# TMC2072 Genlocking Video Digitizer

# Features

- Fully integrated acquisition

- 3-channel video input multiplexer

- Two-stage (analog and digital) video clamp

- Automatic gain adjustment

- Sync detection and separation

- Pixel and subpixel adjustment of video-to-sync output timing

- Genlock to any NTSC or PAL format, including PAL-M and PAL-N

- Pixel clock generation

- 8-bit video A/D conversion

- Standard R-bus serial microprocessor interface

- User-selectable line-locked pixel rates include:

- 12.27 MHz NTSC & PAL-M

- 13.5 MHz NTSC & all PAL

- 14.75 MHz PAL (non-M) TMC2072-1 only

- 15.0 MHz PAL (non-M) TMC2072-1 only

- Direct interface to Fairchild Semiconductor video encoders and decoders

- Built-in circuitry for crystal oscillator

- · No tuning or external voltage reference required

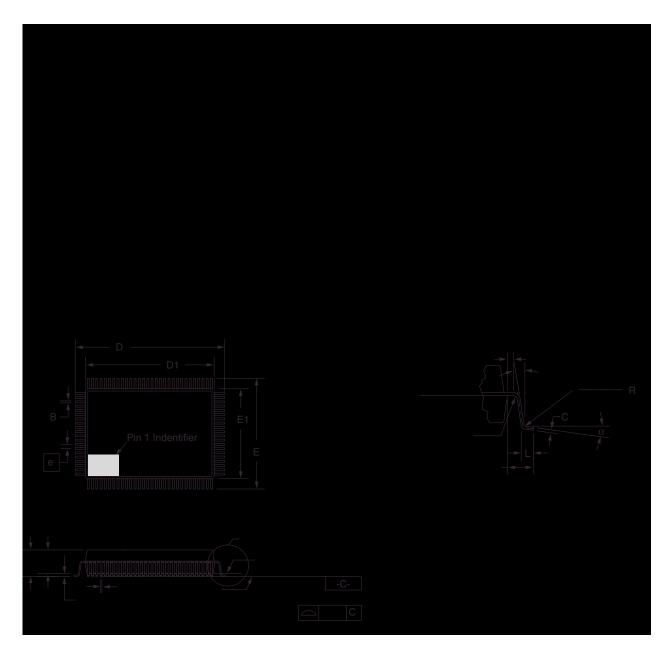

- Space-saving 100-lead MQFP package

### Applications

- Frame grabber

- · Digital videotape recorders

- Desktop video

# Description

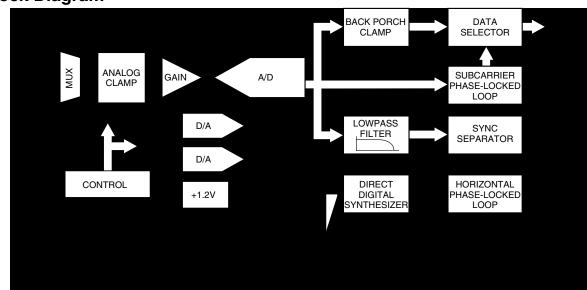

The TMC2072 Genlocking Video Digitizer samples and quantizes standard analog baseband composite NTSC or PAL video into its 8-bit digital equivalent. It extracts horizontal and vertical sync signals, from which an on-chip PLL generates a line-locked pixel clock for the on-chip 8-bit A/D converter and a double-speed register clock to transfer data to a subsequent video processing subsystem. A second PLL generates a chroma subcarrier locked to the incoming chroma burst. The chip reports each line's color burst phase and frequency during the next horizontal sync pulse.

The TMC2072 includes a three-channel video input multiplexer, analog clamp, variable gain amplifier, and digital back porch clamp. The user may provide either an external 20MHz clock or a 20MHz crystal. No external component changes or tuning are required for PAL or NTSC operation at either D1 or square pixel VGA pixel rates.

The TMC2072 is fabricated in a submicron CMOS process and is packaged in a 100-lead MQFP. Its performance is guaranteed from 0 to 70°C.

# **Block Diagram**

# **Functional Description**

The TMC2072, a fully integrated self-genlocking video A/D converter, digitizes NTSC or PAL baseband composite signals. It accepts video on one of three input channels, adjusts the gain, clamps to the back porch and digitizes the video at a user-selectable multiple of the horizontal line frequency. It extracts horizontal and vertical sync, measures the subcarrier frequency and phase, and provides these data with the digitized composite data over an 8-bit digital video port. Horizontal and vertical sync outputs are provided, along with pixel clock (LDV) and twice pixel clock (PXCK).

Operating parameters are set up via a standard two-wire microprocessor port. The chip can work with either an internal or an external voltage reference.

Fabricated in an advanced CMOS process, the TMC2072 is housed in a 100 lead metric quad flat package. Its performance is guaranteed from 0 to 70°C and from 4.75 to 5.25 supply volts.

### Timing

The TMC2072's A/D converter and digital signal path operate from alternate cycles of an internally-synthesized clock, PXCK. This 24.5 to 30 MHz clock is derived from the incoming 20 MHz reference clock and phase-locked to the horizontal sync tips of the incoming analog video stream. The frequency of PXCK may be set as 1560 (NTSC VGA square pixel), 1716 (NTSC D1), 1732 (PAL D1), or 1888 or 1920 (PAL VGA) times the incoming video line rate.

Timing of the serial microprocessor interface bus is independent of the pixel clock and is described under the Microprocessor Interface section that follows Functional Description.

### Video Input

Via the microprocessor interface, the user can enable one of the chip's three analog video input ports. Although each port normally anticipates a standard video signal level with 286 to 300 mV between sync tip and blank, another control register bit allows it to be used with half-power (approximately 70% amplitude) signals. Good crosstalk isolation accommodates active video on all three inputs simultaneously. The user must provide antialias filtering and proper line termination externally.

### **Analog Clamp**

The front-end analog clamp ensures that the input video falls within the active range of the A/D converter. The digitized composite video output can be clamped to the back porch by a secondary digital clamp.

#### **Automatic Gain Adjustment**

To accommodate approximately a  $\pm 15\%$  range in video signal amplitudes, the TMC2072's on-chip AGC circuit

engages for one video frame following either: 1) initial lock after reset; 2) loss and recovery of lock while operating; or 3) setting of control bit AGCEN high by the host microprocessor. The AGC operation adjusts the A/D converter's onchip reference voltages until video blank causes it to output approximately 1/4 of its full range. The chip then holds this gain adjustment constant until a new AGC sequence is initiated by AGCEN going high or by loss and recovery of video lock. The one-frame timeout prevents the gain control from riding gain and trying to track noise or minor variations in signal strength.

To handle doubly-terminated and other weak video signals, the user should set the VGAIN control bit high, thereby boosting video gain 50% above nominal.

#### Analog-to-Digital Converter

The TMC2072 contains a high-performance 8-bit A/D converter. Its gain and offset are automatically set as a part of the automatic gain adjustment process during initial signal acquisition, and require no user attention.

The reference voltages to the A/D converter are set up by internal D/A converters under automatic control during genlock acquisition. These voltages determine the gain and offset of the A/D converter with respect to the video level presented at its input.

#### Low-Pass Filter

The digitized composite video stream is digitally low-pass filtered to remove chrominance components from the sync separator. Filtering provides robust operation by optimizing the signal-to-noise ratio of the synchronizing/blanking portion of the video, improving the accuracy of the back porch blanking level detector.

A digital sync separator provides the output sync signals, GHSYNC and GVSYNC, and times internal operations.

#### Horizontal Phase-Locked Loop

A phase-locked loop generates PXCK, at twice the pixel rate. The reference signal for the horizontal phase-locked loop is generated by the Direct Digital Synthesizer (DDS). The DDS output is constructed with an internal D/A converter and is output from the TMC2072 via the DDS OUT pin. This signal is passed through an external LC filter and input to the horizontal phase-comparator.

The frequency of the DDS output is one ninth of that of PXCK.

A 20MHz clock is required to drive the DDS. Preferably, this may be input to the TMC2072 via CMOS levels on the CLK IN pin. Alternately, a 20MHz crystal may be directly connected between CLK IN and CLK OUT with tuning capacitors to activate the internal crystal oscillator circuitry.

If incoming video is lost or disconnected after the TMC2072 has locked to it, PXCK and GRS data will continue, but  $\overline{\text{GVSYNC}}$  and every eighth  $\overline{\text{GHSYNC}}$  will cease until lock is reestablished. The GRS will report the initial subcarrier frequency set by the Format select bits of the Control Register. The TMC2072 will relock to incoming video within two frames after it is restored.

#### Subcarrier Phase-Locked Loop

A fully-digital phase-locked loop is used to extract the phase and frequency of the incoming color burst. These frequency and phase values are output over the CVBS bus during the horizontal sync period. Fairchild's video decoder and genlockable encoder chips will accept these data directly.

#### **Back Porch Digital Clamp**

A digital back-porch clamp is employed to ensure a constant blanking level. It digitally offsets the data from the A/D converter to set the back porch level to precisely  $3C_h$  for NTSC and  $40_h$  for PAL. When the digital clamp is enabled, the CVBS video output data is the A/D conversion result minus the back porch level plus  $3C_h$  ( $40_h$  for PAL). The back-porch level is low-pass filtered to minimize streaking artifacts from subtle line-to-line variations.

### **Digitized Video Output**

The digitized 8-bit video output is provided over an 8-bit wide CVBS data port, synchronous with PXCK and LDV. Subcarrier frequency, subcarrier phase, and Field ID data (GRS) are transmitted in 4-bit nibbles over CVBS3-0 during the horizontal sync tip period at the PXCK rate.

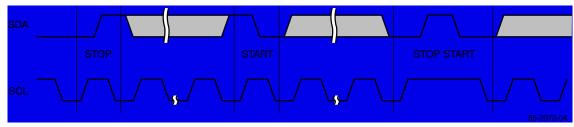

### **Microprocessor Interface**

The TMC2072 is controlled by a standard 2-wire bus. Up to eight TMC2072 devices may be connected to the 2-wire serial interface with each device having a unique address.

The 2-wire interface comprises a clock input (SCL) and a bi-directional data (SDA) pin. The TMC2072 acts as a slave

for receiving and transmitting data over the serial interface. When the serial interface is not active, the logic levels on SCL and SDA are pulled HIGH by external pull-up resistors.

Data received or transmitted on the SDA line must be stable for the duration of the positive-going SCL pulse. Data on SDA must change only when SCL is LOW. If SDA changes state while SCL is HIGH, the serial interface interprets that action as a start or stop sequence.

There are five components to serial bus operation:

- Start signal

- Slave address byte

- Base register address byte

- Data byte to read or write

- Stop signal

When the serial interface is inactive (SCL and SDA are HIGH) communications are initiated by sending a start signal. The start signal is a HIGH-to-LOW transition on SDA while SCL is HIGH. This signal alerts all slaved devices that a data transfer sequence is coming.

The first eight bits of data transferred after a start signal comprise a seven bit slave address and a single R/W bit. The R/W bit indicates the direction of data transfer, read from or write to the slave device. If the transmitted slave address matches the address of the device (set by the state of the SA2:0 input pins.), the TMC2072 acknowledges by bringing SDA LOW on the 9th SCL pulse. If the addresses do not match, the TMC2072 does not acknowledge.

#### **Table 1. Serial Port Addresses**

| A6 | A5 | <b>A</b> 4 | A3 | A <sub>2</sub><br>(SA <sub>2</sub> ) | A <sub>1</sub><br>(SA <sub>1</sub> ) | A <sub>0</sub><br>(SA <sub>0</sub> ) |

|----|----|------------|----|--------------------------------------|--------------------------------------|--------------------------------------|

| 1  | 0  | 0          | 0  | 1/0                                  | 1/0                                  | 1/0                                  |

The address is 1000 SA<sub>2</sub> SA<sub>1</sub> SA<sub>0</sub>.

Figure 1. Microprocessor Parallel Port – Read Timing

#### Data Transfer via Serial Interface

For each byte of data read or written, the MSB is the first bit of the sequence.

If the TMC2072 does not acknowledge the master device during a write sequence, the SDA remains HIGH so the master can generate a stop signal. If the master device does not acknowledge the TMC2072 during a read sequence, the TMC2072 interprets this as "end of data." The SDA remains HIGH so the master can generate a stop signal.

Writing data to specific control registers of the TMC2072 requires that the 8-bit address of the control register of interest be written after the slave address has been established. This control register address is the base address for subsequent write operations. The base address autoincrements by one for each byte of data written after the data byte intended for the base address. If more bytes are transferred than there are available addresses, the address will not increment and remain at its maximum value of 10h. Any base address higher than 10h will not produce an ACKnowledge signal. If no ACKnowledge is received from the master, the encoder will automatically stop sending data.

Data are read from the control registers of the TMC2072 in a similar manner. Reading requires two data transfer operations:

The base address must be written with the R/W bit of the slave address byte LOW to set up a sequential read operation.

Reading (the R/W bit of the slave address byte HIGH) begins at the previously established base address. The address of the read register autoincrements after each byte is transferred.

To terminate a read/write sequence to the TMC2072, a stop signal must be sent. A stop signal comprises a LOW-to-HIGH transition of SDA while SCL is HIGH.

A repeated start signal occurs when the master device driving the serial interface generates a start signal without first generating a stop signal to terminate the current communication. This is used to change the mode of communication (read, write) between the slave and master without releasing the serial interface lines.

#### Serial Interface Read/Write Examples

Write to one control register

$\downarrow$  Start signal

- $\downarrow$  Slave Address byte (R/W bit = LOW)

- $\downarrow$  Base Address byte

- $\downarrow$  Data byte to base address

- $\downarrow$  Stop signal

Write to four consecutive control registers

- $\downarrow$  Start signal

- $\downarrow$  Slave Address byte (R/W bit = LOW)

- $\downarrow$  Base Address byte

- $\downarrow$  Data byte to base address

- $\downarrow$  Data byte to (base address + 1)

- $\downarrow$  Data byte to (base address + 2)

- $\downarrow$  Data byte to (base address + 3)

- $\downarrow$  Stop signal

Read from one control register

- $\downarrow$  Start signal

- $\downarrow$  Slave Address byte (R/W bit = LOW)

- $\downarrow$  Base Address byte

Figure 2. Serial Port Read/Write Timing

Figure 3. Serial Interface – Start/Stop Signal

#### PRODUCT SPECIFICATION

- $\downarrow$  Stop signal

- $\downarrow$  Start signal

- $\downarrow$  Slave Address byte (R/W bit = HIGH)

- $\downarrow$  Data byte from base address

- $\downarrow$  Stop signal

Read from four consecutive control registers

- $\downarrow$  Start signal

- $\downarrow$  Slave Address byte (R/W bit = LOW)

- $\downarrow$  Base Address byte

# **Pin Assignments**

- $\downarrow$  Stop signal

- $\downarrow$  Start signal

- $\downarrow$  Slave Address byte (R/W bit = HIGH)

- $\downarrow$  Data byte from base address

- $\downarrow$  Data byte from (base address + 1)

- $\downarrow$  Data byte from (base address + 2)

- $\downarrow$  Data byte from (base address + 3)

- $\downarrow$  Stop signal

# **Pin Definitions**

| Pin Name    | Pin Number | Pin Type | Function                                                                                                                                      |

|-------------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Video Input |            |          |                                                                                                                                               |

| VIN1-3      | 65, 61, 58 | 1.23Vp-p | <b>Composite Video Input.</b> Video inputs,1.235 Volts peak-to-peak, sync tip to peak color                                                   |

| Clocks      |            | •        |                                                                                                                                               |

| CLK IN      | 91         | CMOS     | <b>20 MHz DDS clock input.</b> 20 MHz CMOS clock input to DDS. This pin may also be used along with CLK OUT for directly connecting crystals. |

| CLK OUT     | 93         | CMOS     | <b>Inverted clock output.</b> Inverted DDS clock output. This pin may also be used along with CLK IN for directly connecting a crystal.       |

| РХСК        | 45         | CMOS     | 2x Pixel clock output. 2x oversampled line-locked clock output.                                                                               |

# Pin Definitions (continued)

| Pin Name       | Pin Number   | Pin Type | e Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |                            |  |  |

|----------------|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|--|--|

| LDV            | 40           | CMOS     | <b>Pixel clock output.</b> Delayed pixel clock output. LDV runs at 1/2 the rate of PXCK and its rising edge is useful for transferring CVBS digital video from the TMC2072 to the TMC22x9x Digital Video Encoders.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |                            |  |  |

| EXT PXCK       | 94           | CMOS     | External PXCK input. Input for external PXCK clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |                            |  |  |

| PXCK SEL       | 86           | CMOS     | <b>PXCK source select.</b><br>When HIGH, the intern<br>When LOW, the extern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nally generated line-lo | cked PXCK is selected.     |  |  |

| Digital Video  | )            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |                            |  |  |

| GHSYNC         | 32           | CMOS     | Horizontal sync output. When the TMC2072 is locked to incomin-<br>video, the GHSYNC pin provides a negative-going pulse after the<br>falling edge of each horizontal sync pulse. When the device is<br>locked to a stable video signal, there is a fixed number of PXCK<br>clock cycles between adjacent falling edges of GHSYNC. If no vide<br>signal is present and LEADLAG is less than 4A(hex), the TMC2072<br>will output normal, evenly-spaced horizontal pulses. If no video<br>signal is present and LEADLAG exceeds 88(hex), the TMC2072 wi<br>omit every eighth Hsync pulse. As LEADLAG is increased from 49<br>to 89h, seven out of every eight Hsyncs will be unaffected, but the<br>eighth will shrink by one clock cycle per LSB step, until it disappear<br>entirely at 89h. |                         |                            |  |  |

| GVSYNC         | 33           | CMOS     | <b>Vertical sync output.</b> When the TMC2072 is locked to incoming video, the GVSYNC pin provides a negative-going edge after the start of the first vertical sync pulse of a vertical blanking interval. If no video signal is present on the selected input pin, GVSYNC will remain continuously at logic high, until a signal is selected and lock is reestablished. A system designer requiring a free-running vertical sync may wish to provide this with an external pixel counter.                                                                                                                                                                                                                                                                                                  |                         |                            |  |  |

| CVBS7-0        | 30-28, 25-21 | CMOS     | <b>Composite output bu</b><br>this bus at 1/2 the PX0<br>subcarrier frequency,<br>bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CK rate. During horizo  |                            |  |  |

| FID[0]         | 35           | CMOS     | Odd/even ("top/botton<br>video frame; HIGH, th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         | otes the first field of a  |  |  |

| FID[1]         | 36           | CMOS     | Bruch blanking flag. In PAL, LOW denotes a frame with burst<br>blanked on line 310, whereas HIGH denotes burst detected on line<br>310. FID[1] is valid only in PAL and only when FID[0] is high and<br>should be interpreted as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                            |  |  |

|                |              |          | FID[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PAL Field Number        |                            |  |  |

|                |              |          | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | II or VI                |                            |  |  |

|                |              |          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IV or VIII              |                            |  |  |

| μ <b>Ρ Ι/Ο</b> |              |          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |                            |  |  |

| SA[2:0]        | 3-1          |          | <b>R-bus chip address,</b><br>SA[1], SA[0]}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 LSBs. Full 7-bit add  | ress = {1, 0, 0, 0, SA[2], |  |  |

| SDA            | 4            | R-bus    | R-bus bidirectional data line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |                            |  |  |

| SCL            | 5            | R-bus    | R-bus clock line (inp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | out/slave only)         |                            |  |  |

# Pin Definitions (continued)

| Pin Name                        | Pin Number                                     | Pin Type     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                           | 7                                              | TTL          | <b>Master reset input.</b> Bringing RESET LOW forces the internal state machines to their starting states, loads the Control Register with default values, and disables outputs. Bringing RESET HIGH restarts the TMC2072 in its default mode.                                                                                                                                                                                                                                                                                                |

| INT                             | 17                                             | TTL          | <b>Interrupt output.</b> This output is LOW if the internal horizontal phase lock loop is unlocked with respect to incoming video for 128 or more lines per field. After lock is established, INT goes HIGH.                                                                                                                                                                                                                                                                                                                                  |

| VALID                           | 34                                             | TTL          | <b>HSYNC locked flag.</b> Hsync locked flag. When high, this output indicates that the most recent incoming horizontal sync has been detected within $\pm 16$ pixels of its expected position. It goes low if no sync is encountered during this $\pm 16$ -pixel window, as during a typical VCR headswitch line. Once the chip has locked to a clean video source, this flag should remain high continuously. If the chip has locked to a VCR, this flag will typically go low for one (or sometimes two) lines at the bottom of each field. |

| BURL                            | 31                                             | TTL/<br>CMOS | <b>Burst lock flag</b> . When high, this output indicates that the chip's internal <i>subcarrier synthesizer is phase-aligned</i> with the current line's incoming chroma burst. The flag goes low when the internal and external phases diverge.                                                                                                                                                                                                                                                                                             |

| Analog Inte                     | erface                                         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VREF                            | 70                                             | +1.23 V      | <b>VREF input/output.</b> +1.23 Volt reference. When the internal voltage reference is used, this pin should be decoupled to $A_{GND}$ with a 0.1 $\mu$ F capacitor. An external +1.2 Volt reference may be connected here, overriding the internal reference source.                                                                                                                                                                                                                                                                         |

| COMP                            | 88                                             | 0.1 μF       | Compensation capacitor. Compensation for DDS D/A converter circuitry. This pin should be decoupled to VDDA with a 0.1 $\mu F$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                      |

| R <sub>B</sub> , R <sub>T</sub> | 57, 68                                         | 0.1 μF       | A/D VREF decoupling. Decoupling points for A/D converter voltage references. These pins should be decoupled to $A_{GND}$ with a 0.1 $\mu F$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                        |

| PLL Filter                      |                                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DDS OUT                         | 82                                             |              | Internal DDS output. Analog output from the internal Direct Digital Synthesizer D/A converter, at 1/9 the PXCK frequency.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PFD IN                          | 77                                             |              | Horizontal PLL input. Analog input to the Phase/Frequency Detector of the horizontal phase-locked loop.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Свүр                            | 75                                             | 1 μF         | <b>Comparator bypass.</b> Decoupling point for the internal comparator reference of the Phase/Frequency Detector. This pin should be decoupled to A <sub>GND</sub> with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                              |

| Power Sup                       | ply                                            |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vdda                            | 49, 51, 52, 60,<br>64, 73, 87                  | +5 V         | <b>Analog power supply.</b> Positive power supply to analog section.<br>All pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD                             | 6, 18, 26, 42, 44,<br>48, 92, 98, 100          | +5 V         | <b>Digital power supply.</b> Positive power supply to digital section.<br>All pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ground                          |                                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Agnd                            | 50, 55, 63, 67,<br>69, 72, 74, 81, 89          | 0.0 V        | <b>Analog ground.</b> Ground for analog section. All pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DGND                            | 8, 16, 27, 38, 39,<br>41, 46, 47, 90,<br>95-97 | 0.0 V        | <b>Digital ground.</b> Ground for digital section. All pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Control and Status Register Bit Functions**

# Summary

| Register | Function                                 |                   |

|----------|------------------------------------------|-------------------|

| Reg 00   | 97h (year of revision)                   | read only         |

| Reg 01   | 20h (part #)                             | read only         |

| Reg 02   | 72h (part #)                             | read only         |

| Reg 03   | 01h (silicon revision #)                 | read only         |

| Reg 04   | Reserved                                 |                   |

| Reg 05   | Lock flags; sync tip                     | read only         |

| Reg 06   | Blank level                              | read only         |

| Reg 07   | Reserved                                 |                   |

| Reg 08   | Format; clock rate; freerun; clamp; rese | t                 |

| Reg 09   | HSync lead/lag                           |                   |

| Reg 0A   | Gain; loop filter bandwidth; subpixel sy | nc & clk position |

| Reg 0B   | Video source select                      |                   |

| Reg 0C   | Vsync delay                              |                   |

| Reg 0D   | Sync tip set                             |                   |

| Reg 0E   | Output timing, tristate                  |                   |

| Reg 0F   | Reserved                                 |                   |

### Details

| Bit      | Name                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                              |  |  |  |  |

|----------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| Reg 00 9 | Reg 00 97h (year of revision)Read Only |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |  |  |  |  |

| Reg 01 2 | 0h (part #)                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Read Only                                                    |  |  |  |  |

| Reg 02 7 | 2h (part #)                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Read Only                                                    |  |  |  |  |

| Reg 03 0 | 1h (silicon revisior                   | n #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Read Only                                                    |  |  |  |  |

| Reg 04 R | eserved                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |  |  |  |  |

| Reg 05 L | ock Flags & Sync I                     | leight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Read Only                                                    |  |  |  |  |

| 7        | BURST_DET                              | Each time a high-frequency signal is detected during a video lir<br>expected burst interval, this flag goes high until the next line's e<br>period. If no high-frequency signal is present during the expect<br>this flag goes low. With a standard color television signal input, t<br>during vertical field groups and, in PAL, Bruch-blanked lines. [The section of the | expected burst<br>ed burst interval,<br>his flag will be low |  |  |  |  |

| 6        | BURST LOCK                             | If the subcarrier loop is unlocked on the current video line, i.e., phase error measured during burst exceeds the lock threshold, until the next burst interval. If the phase error is less than the thr reset high. This flag is meaningful only if $\overline{\text{HLOCK}}$ is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | this flag goes low                                           |  |  |  |  |

| 5        | HLOCK                                  | During each video field, if most horizontal sync pulses arrive me<br>before or after their expected positions, this flag will go high. If<br>incoming horizontal syncs fall within 15 pixels of their expected<br>will go low. [TMC22071A bit 56.]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | most of the field's                                          |  |  |  |  |

| 4:0      | ST                                     | These bits report the each line's average sync tip level out of th (as observed over CVBS). For a clean signal, the reported valu sync tip set in Reg 0D, below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |  |  |  |  |

| Bit      | Name              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reg 06 B | lank level        | Read Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7:0      | BP                | Blank level, as measured at the low-pass-filtered A/D output during each line's color back porch. For a standard video input, its decimal value will be approximately 60 (NTSC) or 64 (PAL). [TMC22071A bits 55:48.]                                                                                                                                                                                                                                                         |

| Reg 07 R | eserved           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Reg 08 S | tandard and Clocl | < Rate Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7:6      | V_STD             | Video Standard. These two control bits select the incoming video standard, viz:                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                   | 00 NTSC, NTSC-EIAJ (power-on default)<br>01 PALM (Brazil)<br>10 PALB,G,H,I<br>11 PALN (Argentina)                                                                                                                                                                                                                                                                                                                                                                            |

|          |                   | [With bits 5:4, these bits cover all functions of TMC22071A bits 3:1.]                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5:4      | CK_RATE           | Pixel Clock/Sample Rate. Pixel (sample) rate selector, as follows:                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |                   | 00 12.27 MHz (power-on default; 525-line VGA)<br>01 13.5 MHz (D1 television rate)<br>10 14.75 MHz (625-line square-pixel VGA) TMC2072-1 only<br>11 15.0 MHz TMC2072-1 only                                                                                                                                                                                                                                                                                                   |

|          |                   | Note: The 12.27 MHz pixel rate is reserved for 525-line television standards (NTSC, PAL-M), whereas the 14.75 and 15.0 MHz rates are for 625-line standards (all other PAL) only. Bit combinations 0x1x and 1x00 may yield stable composite data samples, sync pulses, and pixel clock, but no useful color subcarrier information.                                                                                                                                          |

| 3        | FREERUN           | <b>Freerun vs. Genlock Operation</b> . LOW (power-on default): Standard genlock mode, in which the PXCK, GHSYNC, and GVSYNC lock to the incoming video's observed sync pattern. HIGH: GHSYNC is counted down from a free-running PXCK, which is unrelated to the incoming video. [TMC22071A bit 26.]                                                                                                                                                                         |

| 2        | BPFOUT            | <b>Genlock Reference Signal Enable</b> . LOW (power-on default): Loop-predicted subcarrier phase and frequency data (GRS) are sent over CVBS during each horizontal sync pulse. HIGH: GRS data suppressed, such that the CVBS datastream is just the digitized incoming video signal. [TMC22071A bit 33.]                                                                                                                                                                    |

| 1        | DC_CLAMP          | HIGH (power-on default): vertically low-pass filtered digital porch clamp enabled.<br>LOW: digital clamp disabled [TMC22071A bit 34, except that the TMC22071A clamp has no vertical filter.]                                                                                                                                                                                                                                                                                |