ISL99202

#### September 14, 2011

## FN6758.1

## 60mW, Capfree, Stereo Headphone Amplifier

intercil

The ISL99202 is a stereo, capfree headphone amplifier. The wide operating voltage of 2.4V to 5.5V makes it versatile enough to be used in mobile battery powered applications powered by 2 AA or Single cell Li-Ion batteries as well as 3.3/5V power supply available notebook computers.

The ISL99202 has robust RF immunity, which makes it ideally suited for today's mobile applications.

It has audiophile quality SNR and THD specifications and Click/Pop suppression.

The ISL99202 comes with Comprehensive Protection features, which include undervoltage and short-circuit protection and thermal shutdown.

The ISL99202 lowest power consumption in the industry is achieved by low  ${\rm I}_{\rm QQ}$  and current shutdown.

The product is available in 12 Ld TQFN and 0.4mm pitch 12 ball WLCSP.

Ordering Information

#### Features

- Supports  $16\Omega$  to  $600\Omega$  Speaker Impedance

- · Ground Referenced: No Output Coupling Capacitors

- Audiophile Quality Sound THD of 0.01%, SNR of 102dB

- PSRR < -90dB, No Need for LDO

- Wide Operating Voltage of 2.4V to 5.5V

- < 3mA Quiesent Current and 0.1µA Shutdown Current</li>

- · State of the Art Pop and Click Suppression

- Pb-Free (RoHS Compliant)

#### **Applications**

- Mobile Phones

- MP3 Players

| PART NUMBER                    | PART MARKING | GAIN SETTING<br>(dB) | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free)    | PKG. DWG. # |

|--------------------------------|--------------|----------------------|---------------------|-------------------------|-------------|

| ISL99202IIAZ-T* (Notes 1, 3)   | 202A         | -1.5V/V              | -40 to +85          | 12 Ball 3x4 WLCSP Array | W3x4.12     |

| ISL99202IIBZ-T* (Notes 1, 3)   | 202B         | Adjustable           | -40 to +85          | 12 Ball 3x4 WLCSP Array | W3x4.12     |

| ISL99202IRTAZ (Notes 2, 3)     | 202A         | -1.5V/V              | -40 to +85          | 12 Ld TQFN              | L12.3x3Z    |

| ISL99202IRTAZ-T* (Notes 2, 3)  | 202A         | -1.5V/V              | -40 to +85          | 12 Ld TQFN              | L12.3x3Z    |

| ISL99202IRTAZ-TK* (Notes 2, 3) | 202A         | -1.5V/V              | -40 to +85          | 12 Ld TQFN              | L12.3x3Z    |

| ISL99202IRTBZ (Notes 2, 3)     | 202B         | Adjustable           | -40 to +85          | 12 Ld TQFN              | L12.3x3Z    |

| ISL99202IRTBZ-T* (Notes 2, 3)  | 202B         | Adjustable           | -40 to +85          | 12 Ld TQFN              | L12.3x3Z    |

| ISL99202IRTBZ-TK* (Notes 2, 3) | 202B         | Adjustable           | -40 to +85          | 12 Ld TQFN              | L12.3x3Z    |

\*Please refer to TB347 for details on reel specifications. NOTES:

1. These Intersil Pb-free WLCSP and BGA packaged products products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free WLCSP and BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. Contact factory for ordering details.

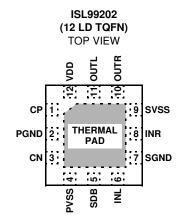

## Pinouts

## **Pin Descriptions**

| PIN  | NUMBER |          |                               |

|------|--------|----------|-------------------------------|

| TQFN | WLCSP  | PIN NAME | DESCRIPTION                   |

| 1    | B3     | CP       | Charge pump positive terminal |

| 2    | C3     | PGND     | Charge pump Ground            |

| 3    | D3     | CN       | Charge pump negative terminal |

| 4    | D2     | PVSS     | Charge pump output            |

| 5    | C2     | SDB      | Active low shutdown input     |

| 6    | D1     | INL      | Left channel input            |

| 7    | C1     | SGND     | Analog ground                 |

| 8    | B2     | INR      | Right channel input           |

| 9    | B1     | SVSS     | Amplifier negative supply     |

| 10   | A1     | OUTR     | Right channel output          |

| 11   | A2     | OUTL     | Left channel output           |

| 12   | A3     | VDD      | Positive power supply         |

NOTE: Exposed Pad is connected to PGND and SGND

| <b>Absolute Maximum Ratings</b> | (Reference to GND) |

|---------------------------------|--------------------|

|---------------------------------|--------------------|

| Supply Voltage   |

|------------------|

| ESD Rating       |

| Human Body Model |

| All pins         |

| OUTL, OUTR       |

| Machine Model    |

|                  |

#### **Operating Conditions**

| Ambient Temperature Range          | 40°C to +85°C |

|------------------------------------|---------------|

| Maximum Supply Voltage (VDD Pin)   | 5.5V          |

| Operating Supply Voltage (VDD Pin) | 2.4V to 5V    |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 4, 5) $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W)TQFN Package548 |

|---------------------------------------------------------------------------------------------------|

| WLCSP Package                                                                                     |

| Maximum Junction Temperature (Plastic Package) -65°C to +150°C                                    |

| Maximum Storage Temperature Range65°C to +150°C                                                   |

| Dissipation Ratings                                                                               |

| Derating Factor                                                                                   |

| 12 LD 3x3 TQFN14.7mW/°C                                                                           |

| 12 Ball 3x4 Array WLCSP10.1mW/°C                                                                  |

| Power Rating T <sub>A</sub>                                                                       |

| 12 Ld 3x3 TQFN                                                                                    |

| +25°C                                                                                             |

| +70°C                                                                                             |

| +85°C                                                                                             |

| 12 Ball 3x4 Array WLCSP                                                                           |

| +25°C                                                                                             |

| +70°C                                                                                             |

| +85°C0.18W                                                                                        |

| Pb-Free Reflow Profilesee link below                                                              |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp                                                  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For theta  $\theta_{JC}$  the "case temp." location is the center of the exposed metal pad on the package underside.

| Electrical Specifications | Typical Values are Tested at V <sub>DD</sub> = 5V, T <sub>A</sub> = +25°C and R <sub>L</sub> = 32 $\Omega$ . All Maximum and Minimum Values are |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Established Under the Recommended Operating Supply Voltage Range and +25°C, Unless Otherwise Noted.                                             |

| PARAMETER                         | SYMBOL           | TEST CONDITIONS                                      | MIN | ТҮР   | MAX | UNITS |

|-----------------------------------|------------------|------------------------------------------------------|-----|-------|-----|-------|

| OUTPUT POWER                      |                  |                                                      |     |       |     |       |

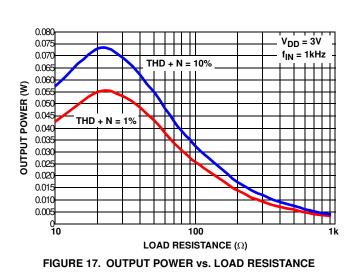

| Output Power (QFN)                | P <sub>OUT</sub> | R <sub>L</sub> = 32Ω, THD = 1%                       | 30  | 63    |     | mW    |

|                                   |                  | R <sub>L</sub> = 16Ω                                 |     | 70    |     | mW    |

| Output Power (CSP)                | P <sub>OUT</sub> | $R_L=32\Omega$                                       | 25  | 63    |     | mW    |

|                                   |                  | $R_L=16\Omega$                                       |     | 70    |     | mW    |

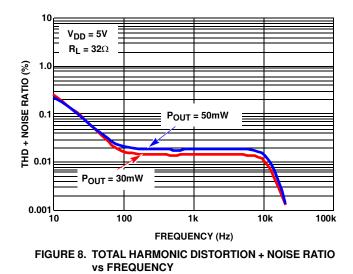

| Total Harmonic Distortion + Ratio | THD+N            | $R_L = 1k\Omega$ , $V_{OUT} = 1.5V_{RMS}$ , f = 1kHz |     | 0.003 |     | %     |

|                                   |                  | $R_L = 32\Omega$ , $P_{OUT} = 50$ mW, f = 1kHz       |     | 0.01  |     | %     |

|                                   |                  | $R_L = 16\Omega, P_{OUT} = 35mW, f = 1kHz$           |     | 0.02  |     | %     |

| PROTECTION                        |                  |                                                      |     |       |     |       |

| Thermal Shutdown                  | OTP              |                                                      |     | 160   |     | °C    |

| Thermal Shutdown Hysteresis       |                  |                                                      |     | 15    |     | °C    |

| Overcurrent Protection            | OCP              |                                                      |     | 200   |     | mA    |

| Undervoltage Shutdown             |                  |                                                      |     |       | 2.4 | V     |

| LOGIC INPUTS (SDB)                |                  |                                                      |     |       |     |       |

| Input Voltage High                | V <sub>INH</sub> |                                                      | 1.4 |       |     | V     |

| Input Voltage Low                 | V <sub>INL</sub> |                                                      |     |       | 0.9 | V     |

| POWER SUPPLY                      |                  | 1                                                    | ł   |       |     |       |

| Supply Voltage Range              | V <sub>DD</sub>  |                                                      | 2.4 |       | 5.5 | V     |

# **Electrical Specifications** Typical Values are Tested at $V_{DD} = 5V$ , $T_A = +25^{\circ}C$ and $R_L = 32\Omega$ . All Maximum and Minimum Values are Established Under the Recommended Operating Supply Voltage Range and +25°C, Unless Otherwise Noted. (Continued)

| (Continued)                             |                  |                                                                                               |       |       |       |       |

|-----------------------------------------|------------------|-----------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| PARAMETER                               | SYMBOL           | TEST CONDITIONS                                                                               | MIN   | ТҮР   | MAX   | UNITS |

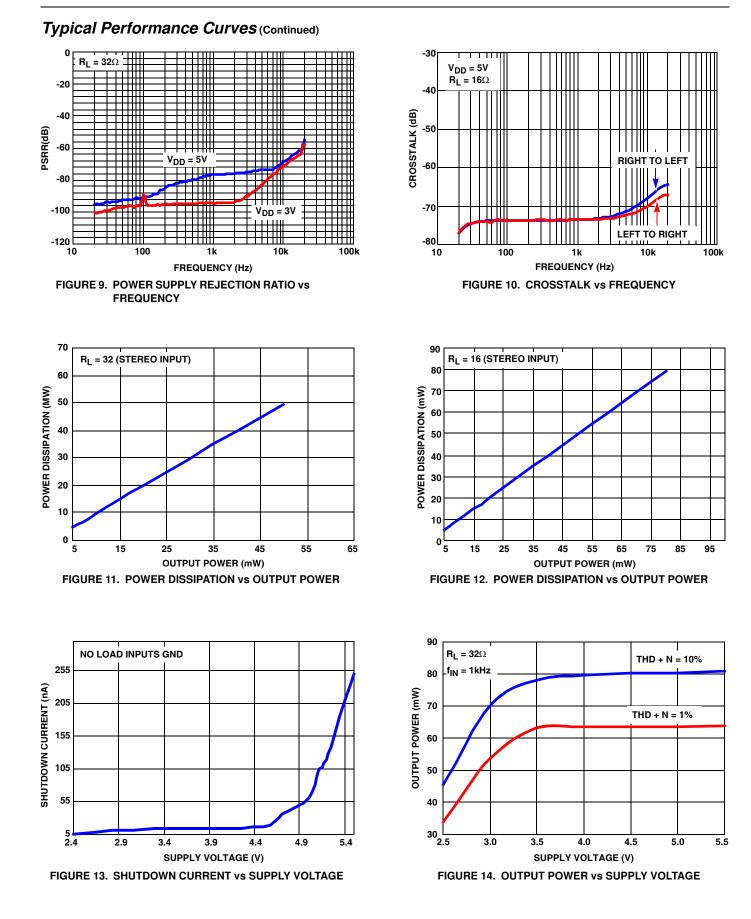

| Power Supply Rejection Ratio            | PSRR             | V <sub>DD</sub> = 2.5V to 5.0V at 217Hz                                                       |       | 96    |       | dB    |

|                                         |                  | V <sub>DD</sub> = 2.5V to 5.0V at 1kHz                                                        |       | 88    |       | dB    |

|                                         |                  | V <sub>DD</sub> = 2.5V to 5.0V at 20kHz                                                       |       | 76    |       | dB    |

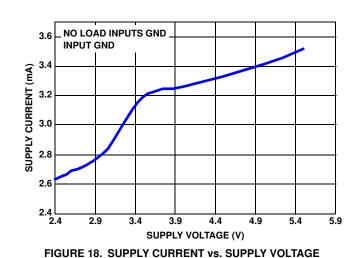

| Quiescent Current                       | l <sub>qq</sub>  | V <sub>DD</sub> = 5.0V                                                                        |       | 3     | 4.6   | mA    |

| Shutdown Current                        | I <sub>SDB</sub> | SDB = GND , V <sub>DD</sub> = 5.0V                                                            |       | 0.1   | 1.1   | μA    |

| GAIN CONTROL                            | 1                |                                                                                               | 1     | r     |       |       |

| Voltage Gain                            | A <sub>V</sub>   |                                                                                               | -1.55 | -1.50 | -1.45 | V/V   |

| Ch to Ch Gain Tracking                  | -                |                                                                                               |       | ±0.15 |       | %     |

| Total Harmonic Distortion + Ratio       | THD+N            | R <sub>L</sub> = 1kΩ, V <sub>OUT</sub> = 1.5V <sub>RMS</sub> , f = 1kHz                       |       | 0.005 |       | %     |

|                                         |                  | $R_L = 32\Omega$ , $P_{OUT} = 50$ mW, f = 1kHz                                                |       | 0.01  |       | %     |

|                                         |                  | $R_L = 16\Omega, P_{OUT} = 35mW, f = 1kHz$                                                    |       | 0.04  |       | %     |

| NOISE PERFORMANCE                       |                  | 1                                                                                             | 1     |       |       |       |

| Signal to Noise Ratio                   | SNR              | $R_L$ = 1k $\Omega$ , V <sub>OUT</sub> = 1.5V <sub>RMS</sub> , BW = 22Hz to 20kHz             |       | 102   |       | dB    |

|                                         |                  | $R_L$ = 1k $\Omega$ , V <sub>OUT</sub> = 1.5V <sub>RMS</sub> , BW = 22Hz to 20kHz, A-weighted |       | 105   |       | dB    |

|                                         |                  | $R_L$ = 32 $\Omega$ , $P_{OUT}$ = 35mW, BW = 22Hz to 20kHz                                    |       | 100   |       | dB    |

|                                         |                  | $R_L$ = 32 $\Omega$ , $P_{OUT}$ = 35mW, BW = 22Hz to 20kHz, A-weighted                        |       | 113   |       | dB    |

| Slew Rate                               | SR               |                                                                                               |       | 0.5   |       | VµS   |

| Capacitve Drive                         | CL               |                                                                                               |       | 100   |       | pF    |

| Crosstalk (QFN, CSP)                    | xtalk            | R <sub>L</sub> = 16Ω, P <sub>OUT</sub> = 15mW, f = 10kHz                                      |       | -76   |       | dB    |

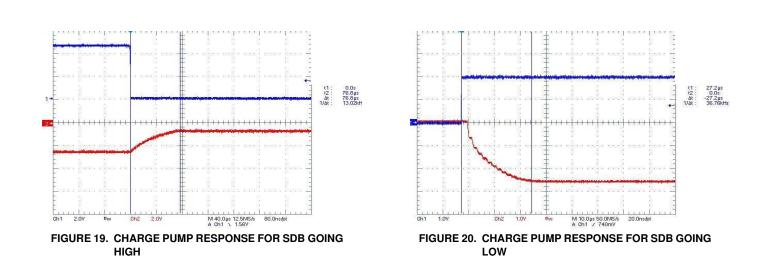

| Charge Pump Oscillation Frequency       | f <sub>soc</sub> |                                                                                               | 400   | 500   | 600   | kHz   |

| Click and Pop Level                     | K <sub>CP</sub>  | $R_L = 32\Omega$ , Peak voltage, Awtg. 32 sam/sec                                             |       | -67   |       | dB    |

| V <sub>DD</sub> = 3.0V                  |                  |                                                                                               |       |       |       |       |

| Power Supply Rejection Ratio            | PSRR             | 217Hz                                                                                         |       | 96    |       | dB    |

|                                         |                  | 1kHz                                                                                          |       | 88    |       | dB    |

|                                         |                  | 20kHz                                                                                         |       | 76    |       | dB    |

| Quiescent Current                       | l <sub>qq</sub>  |                                                                                               |       | 2.4   | 3.6   | mA    |

| Shutdown Current                        | I <sub>SDB</sub> | SDB = GND                                                                                     |       | 0.1   | 1.1   | μA    |

| Output Offset Voltage                   | VOS              |                                                                                               | -1    | 0.05  | 1     | mV    |

| Output Power at $32\Omega$ Load         |                  | R <sub>L</sub> = 32Ω, THD = 1%                                                                | 1     | 54    |       | mW    |

| Output Power at 16Ω Load                |                  | R <sub>L</sub> = 16Ω, THD = 1%                                                                |       | 56    |       | mW    |

| Total Harmonic Distortion + Noise Ratio | THD+N            | $R_L = 1k\Omega$ , $V_{OUT} = 1.5V_{RMS}$ , f = 1kHz                                          |       | 0.005 |       | %     |

|                                         |                  | $R_{L} = 32\Omega, P_{OUT} = 50$ mW, f = 1kHz                                                 |       | 0.01  |       | %     |

|                                         |                  | $R_L = 16\Omega, P_{OUT} = 35mW, f = 1kHz$                                                    |       | 0.02  |       | %     |

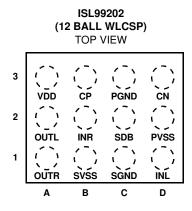

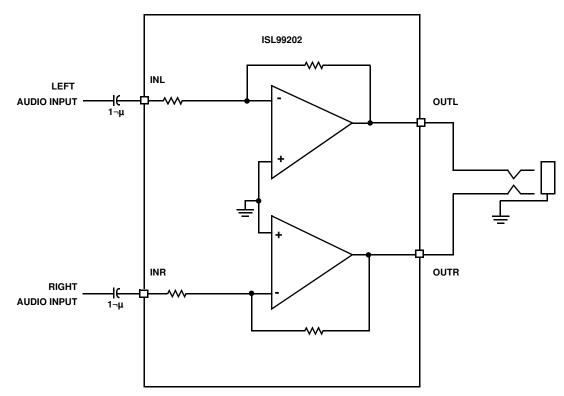

#### Block Diagram

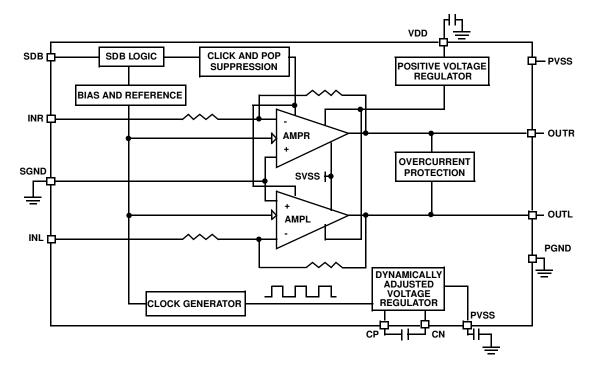

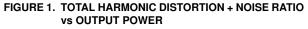

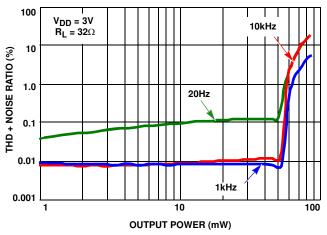

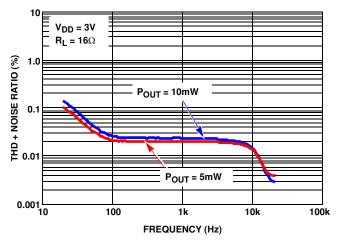

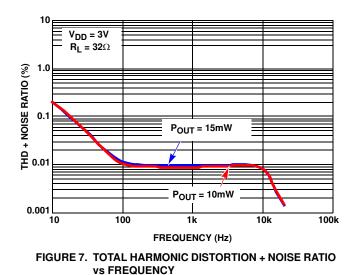

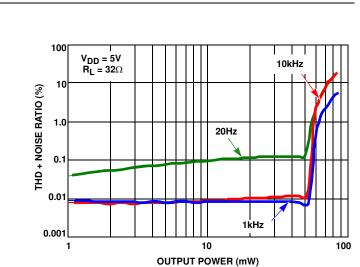

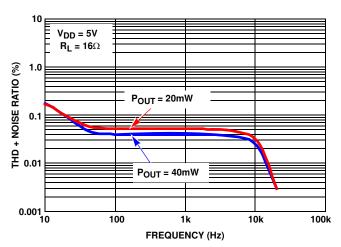

Typical Performance Curves

FIGURE 2. TOTAL HARMONIC DISTORTION + NOISE RATIO vs OUTPUT POWER

#### Typical Performance Curves (Continued)

FIGURE 5. TOTAL HARMONIC DISTORTION + NOISE RATIO vs FREQUENCY

FIGURE 4. TOTAL HARMONIC DISTORTION + NOISE RATIO

FIGURE 6. TOTAL HARMONIC DISTORTION + NOISE RATIO vs FREQUENCY

8

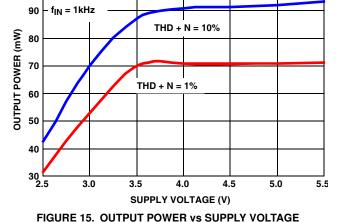

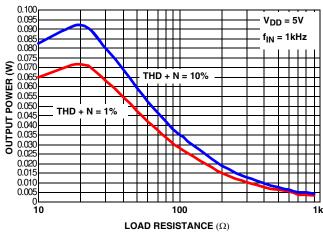

FIGURE 16. OUTPUT POWER vs LOAD RESISTANCE

## **Typical Application Circuit**

## **Detailed Description**

The ISL99202 incorporates a novel proprietary architecture to eliminate the large output capacitors associated with single supply headphone amplifiers. Traditional charge pump based architectures that eliminated the output capacitors required additional power to operate the charge pump, which made them ill-suited for portable battery powered applications. The ISL99202 architecture eliminates the need for large output capacitors while consuming industry's lowest quiescent and shutdown currents.

#### Capfree Architecture

At the core of the Capfree architecture is a dynamically adjusted negative voltage regulator. By continuously monitoring the output power requirements, it adjusts the energy delivery circuitry. The feedback system ensures that overhead power required to deliver audio at the headphone speaker is always optimized for lower power dissipation.

## Integrated LDO

A high precision LDO integrated into the power path of the amplifier accounts for a 92dB PSRR. This eliminates the need for a dedicated LDO used in some systems resulting in BOM/cost savings.

## Offset Cancellation Circuitry

The DC offset is a very important parameter. It is a principal contributor to Click and Pop. In the cast Capfree architecture, the DC offset can also be a source of DC

current in quiescent state. The ISL99202 is tested and trimmed to have very low offset voltages (typically 50µV).

## RF Immunity

Most portable applications for ISL99202 are subject to RF radiation from a myriad of sources, like Wi-Fi networks or cellular phone networks. Though these signals are not in the audio band, they can interfere with the audio signals through complex non-linear mechanisms, aliasing or demodulations to create audio band noise. The ISL99202 architecture prevents this coupling into audio band to achieve superior audio performance.

#### **Protection Circuitry**

The ISL99202 has comprehensive protection circuitry, which protects the part due to undervoltage, over-temperature and overcurrent. There is hysteresis built into over-temperature and undervoltage, while the overcurrent is designed to limit the output current in case of accidental short circuit or low impedance headphone load connection.

## References

Intersil Technical Brief 451: "PCB Assembly Guidelines for Intersil Wafer Level Chip Scale Package Devices" http://www.intersil.com/data/tb/TB451.pdf

Intersil Technical Brief 389: "PCB Land Pattern Design and Surface Mount Guidelines for QFN Packages" http://www.intersil.com/data/tb/tb389.pdf

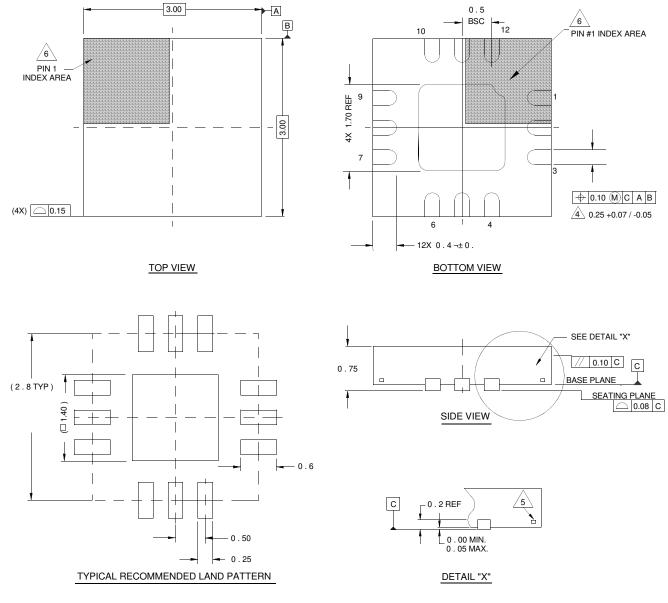

## Package Outline Drawing

L12.3x3Z 12 LEAD THIN QUAD FLAT NO LEAD PLASTIC PACKAGE FOR ISL99202 USE ONLY WITH REDUCED e-PAD SIZE TO 1.4mm ON LAND PATTERN Rev 0, 10/08

#### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to JEDEC STD MO-229.

- 3. Unless otherwise specified, tolerance : Decimal  $\neg \pm 0.0$

- 4. Dimension b applies to the metallized terminal and is measured between 0.20mm and 0.32mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

## ISL99202

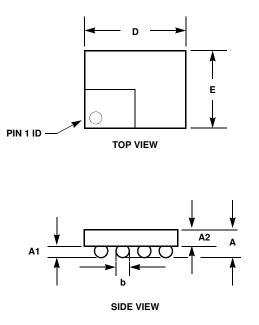

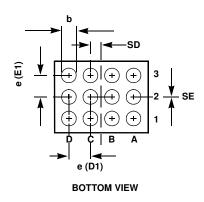

## Wafer Level Chip Scale Package (WLCSP 0.4mm Ball Pitch)

W3x4.12

3x4 ARRAY 12 BALL WAFER LEVEL CHIP SCALE PACKAGE

| SYMBOL | MILLIMETERS                   |

|--------|-------------------------------|

| A      | 0.445 Min 0.495 Nom 0.545 Max |

| A1     | 0.190 ±0.025                  |

| A2     | 0.305 ±0.025                  |

| b      | 0.270 ±0.030                  |

| D      | 1.695 ±0.020                  |

| D1     | 0.400 BASIC                   |

| E      | 1.295 ±0.020                  |

| E1     | 0.400 BASIC                   |

| e      | 0.400 BASIC                   |

| SD     | 0.200 BASIC                   |

| SE     | 0 BASIC                       |

|        | NUMBER OF BUMPS: 12           |

NOTES:

1. All Dimensions are in Millimeters.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Rev. 0 12/08