## Load-Dump/Reverse-Voltage Protection Circuits

#### **General Description**

The MAX16126/MAX16127 load-dump/reverse-voltage protection circuits protect power supplies from damaging input voltage conditions, including overvoltage, reverse-voltage, and high-voltage transient pulses. Using a built-in charge pump, the devices control two external back-to-back n-channel MOSFETs that turn off and isolate downstream power supplies during damaging input conditions, such as an automotive load-dump pulse or a reverse-battery condition. Operation is guaranteed down to 3V to ensure proper operation during automotive cold-crank conditions. These devices feature a flag output (FLAG) that asserts during fault conditions.

For reverse-voltage protection, external back-to-back MOSFETs outperform the traditional reverse-battery diode, minimizing the voltage drop and power dissipation during normal operation.

The MAX16126/MAX16127 use external resistors to adjust the overvoltage and undervoltage comparator thresholds for maximum flexibility.

The MAX16127 provides limiter-mode fault management for overvoltage and thermal shutdown conditions; whereas the MAX16126 provides switch-mode fault management for overvoltage and thermal shutdown conditions. In the limiter mode, the output voltage is limited and  $\overline{FLAG}$  is asserted low during a fault. In the switch mode, the external MOSFETs are switched off and  $\overline{FLAG}$  is asserted low after a fault. The switch mode is available in four options: latch mode, 1 autoretry mode, 3 autoretry mode, and always autoretry mode.

The MAX16126/MAX16127 are available in 12-pin TQFN packages. These devices operate over the automotive temperature range (-40°C to +125°C).

#### **Benefits and Features**

- Increases Protection of Sensitive Electronic Components in Harsh Environments

- -36V to +90V Wide Input-Voltage Protection Range

- Fast Gate Shutoff During Fault Conditions with Complete Load Isolation

- Thermal-Shutdown Protection

- Active-Low FLAG Output Identifies Fault Condition

- AEC-Q100 Automotive Qualified

- Operates Down to +3V, Riding Out Cold-Crank

Conditions

- -40°C to +125°C Operating Temperature Range

- Integration Reduces Solution Size

- Internal Charge-Pump Circuit Enhances External n-Channel MOSFET

- Adjustable Undervoltage/Overvoltage Thresholds

- 3mm x 3mm, 12-Pin TQFN Package

- Reduced Power Dissipation Compared to Discrete

Solutions

- Minimal Operating Voltage Drop for Reverse-Voltage Protection

- 350µÅ (max) Supply Current and 100µÅ (max) Shutdown Current at 30V Input

#### **Applications**

- Automotive

- Industrial

- Avionics

- Telecom/Server/Networking

Ordering Information appears at end of data sheet.

## Load-Dump/Reverse-Voltage Protection Circuits

## **Absolute Maximum Ratings**

| (All pins referenced to GND.) |                                          |

|-------------------------------|------------------------------------------|

| IN                            | 36V to +90V                              |

| SHDN                          | 0.3V to max (0V, V <sub>IN</sub> + 0.3V) |

| TERM                          | 0.3V to max (0V, V <sub>IN</sub> + 0.3V) |

| SRC, GATE                     | 36V to +45V                              |

| SRC to GATE                   | 36V to +36V                              |

| OUT                           | 0.3V to +45V                             |

| FLAG                          | 0.3V to +45V                             |

| OVSET, UVSET                  | 0.3V to +6V                              |

| Continuous Sink/Source (all pins)                     | ±100mA             |

|-------------------------------------------------------|--------------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | (multilayer board) |

| TQFN (derate 14.7mW/°C above +70°C)                   | 1176.5mW           |

| Operating Temperature Range                           | -40°C to +125°C    |

| Junction Temperature                                  | +150°C             |

| Storage Temperature Range                             | -60°C to +150°C    |

| Lead Temperature (soldering, 10s)                     | +300°C             |

| Soldering Temperature (reflow)                        | +260°C             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Thermal Characteristics (Note 1)

TQFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).....46.91°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )...........5.27°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

$(V_{IN} = 12V, C_{GATE-SOURCE} = 1nF, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                        | SYMBOL              | CONE                                    | DITIONS                                                        | MIN | ТҮР                       | MAX  | UNITS |

|----------------------------------|---------------------|-----------------------------------------|----------------------------------------------------------------|-----|---------------------------|------|-------|

|                                  | N                   | Operating range                         |                                                                | 3   |                           | 30   | V     |

| Input Voltage Range              | V <sub>IN</sub>     | Protection range                        |                                                                | -36 |                           | +90  | V     |

|                                  |                     |                                         | V <sub>IN</sub> = V <sub>SRC</sub> =<br>V <sub>OUT</sub> = 12V |     | 224                       | 360  |       |

| Input Supply Current             | I <sub>IN</sub>     | SHDN = high                             | V <sub>IN</sub> = V <sub>SRC</sub> =<br>V <sub>OUT</sub> = 30V |     | 260                       | 400  | μA    |

|                                  |                     |                                         | V <sub>IN</sub> = 12V                                          |     | 34                        | 60   |       |

|                                  |                     | SHDN = low                              | V <sub>IN</sub> = 30V                                          |     | 64                        | 100  |       |

| SPC Input Current                |                     | V <sub>SRC</sub> = V <sub>IN</sub> = 12 |                                                                |     | 136                       | 200  |       |

| SRC Input Current                | I <sub>SRC</sub>    | $V_{SRC} = V_{IN} = 30$                 | V, SHDN = high                                                 |     | 240                       | 350  | μA    |

| IN Undervoltage Lockout          | V <sub>UVLO</sub>   | V <sub>IN</sub> rising                  |                                                                |     |                           | 2.92 | V     |

| OVSET/UVSET Input Current        | IUVSET/OVSET        |                                         |                                                                |     |                           | 100  | nA    |

| OVSET/UVSET Threshold (Rising)   | V <sub>TH</sub>     | V <sub>IN</sub> rising                  |                                                                | 1.2 | 1.225                     | 1.25 | V     |

| OVSET/UVSET Threshold Hysteresis | V <sub>TH-HYS</sub> |                                         |                                                                |     | 0.05 x<br>V <sub>TH</sub> |      | V     |

| POK Threshold Rising             | V <sub>POK+</sub>   |                                         |                                                                |     | 0.9 x<br>V <sub>IN</sub>  |      | V     |

| POK Threshold Falling            | V <sub>POK-</sub>   |                                         |                                                                |     | 0.87 x<br>V <sub>IN</sub> |      | V     |

| TERM On-Resistance               | R <sub>TERM</sub>   |                                         |                                                                |     | 0.7                       | 1.2  | kΩ    |

# Load-Dump/Reverse-Voltage Protection Circuits

## **Electrical Characteristics (continued)**

$(V_{IN} = 12V, C_{GATE-SOURCE} = 1nF, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 2)

| PARAMETER                                          | SYMBOL             | CONDITIONS                                                                               | MIN  | TYP  | MAX  | UNITS |  |

|----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Startup Response Time                              | t <sub>START</sub> | (Note 3)                                                                                 |      | 150  |      | μs    |  |

| Autoretry Timeout                                  | <sup>t</sup> RETRY |                                                                                          |      | 150  |      | ms    |  |

| GATE Rise Time                                     | t <sub>RISE</sub>  | V <sub>GATE</sub> rising (GND to V <sub>SRC</sub> + 8V)                                  |      | 1    |      | ms    |  |

| OVSET-to-GATE Propagation Delay                    | t <sub>OVG</sub>   | V <sub>OVSET</sub> rising (V <sub>TH</sub> - 100mV to<br>V <sub>TH</sub> + 100mV)        |      |      | 0.55 | μs    |  |

| UVSET-to-GATE Propagation Delay                    | t <sub>UVG</sub>   | V <sub>UVSET</sub> falling (V <sub>TH</sub> + 100mV to<br>V <sub>TH</sub> - 100mV)       |      | 20   |      | μs    |  |

|                                                    |                    | MAX16126                                                                                 |      | 4    |      | ΜΩ    |  |

| Output Input Resistance to GND                     | R <sub>OUT</sub>   | MAX16127                                                                                 |      | 2    |      |       |  |

| OVSET-to-FLAG Propagation Delay                    | t <sub>OV</sub>    | V <sub>OVSET</sub> rising (V <sub>TH</sub> - 100mV to<br>V <sub>TH</sub> + 100mV)        |      | 0.3  |      | μs    |  |

| GATE Output Voltage High Above<br>V <sub>SRC</sub> | V <sub>GS</sub>    | $V_{IN} = V_{SRC} = V_{OUT} = 3V,$<br>$I_{GATE} = -1\mu A$                               | 4.25 | 5    | 5.5  | V     |  |

|                                                    |                    | $V_{IN} = V_{SRC} = V_{OUT} = 12V,$<br>$I_{GATE} = -1\mu A$                              | 8    | 9    | 10   |       |  |

|                                                    |                    | V <sub>IN</sub> = V <sub>SRC</sub> = V <sub>OUT</sub> = 24V,<br>I <sub>GATE</sub> = -1μA | 7    | 8.5  | 10   |       |  |

|                                                    |                    | $V_{IN} = V_{SRC} = V_{OUT} = 30V,$<br>$I_{GATE} = -1\mu A$                              | 6.25 | 8    | 9.5  |       |  |

| GATE Pulldown Current                              | I <sub>PD</sub>    | V <sub>GATE</sub> = 12V                                                                  | 8.8  |      |      | mA    |  |

| GATE Charge-Pump Current                           | IGATE              | $V_{IN} = V_{GATE} = V_{SRC} = 12V$                                                      |      | 180  |      | μA    |  |

| Thermal Shutdown                                   | T+                 |                                                                                          |      | +145 |      | °C    |  |

| Thermal-Shutdown Hysteresis                        | ΔΤ                 |                                                                                          |      | 15   |      | °C    |  |

| SHDN Logic-High Input Voltage                      | VIH                |                                                                                          | 1.4  |      |      | V     |  |

| SHDN Logic-Low Input Voltage                       | VIL                |                                                                                          |      |      | 0.4  | V     |  |

| SHDN Input Pulse Width                             | t <sub>PW</sub>    |                                                                                          | 6    |      |      | μs    |  |

| SHDN Input Pulldown Current                        | I <sub>SPD</sub>   |                                                                                          |      | 0.8  | 1.2  | μA    |  |

| FLAG Output Voltage Low                            | V <sub>OL</sub>    | FLAG sinking 1mA                                                                         |      |      | 0.4  | V     |  |

| FLAG Leakage Current                               | IIL                | V <sub>FLAG</sub> = 12V                                                                  |      |      | 0.5  | μA    |  |

Note 2: All parameters are production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

Note 3: The MAX16126/MAX16127 power up with the external MOSFETs in off mode (V<sub>GATE</sub> = V<sub>SRC</sub>). The external MOSFETs turn on t<sub>START</sub> after the IC is powered up and all input conditions are valid.

# Load-Dump/Reverse-Voltage Protection Circuits

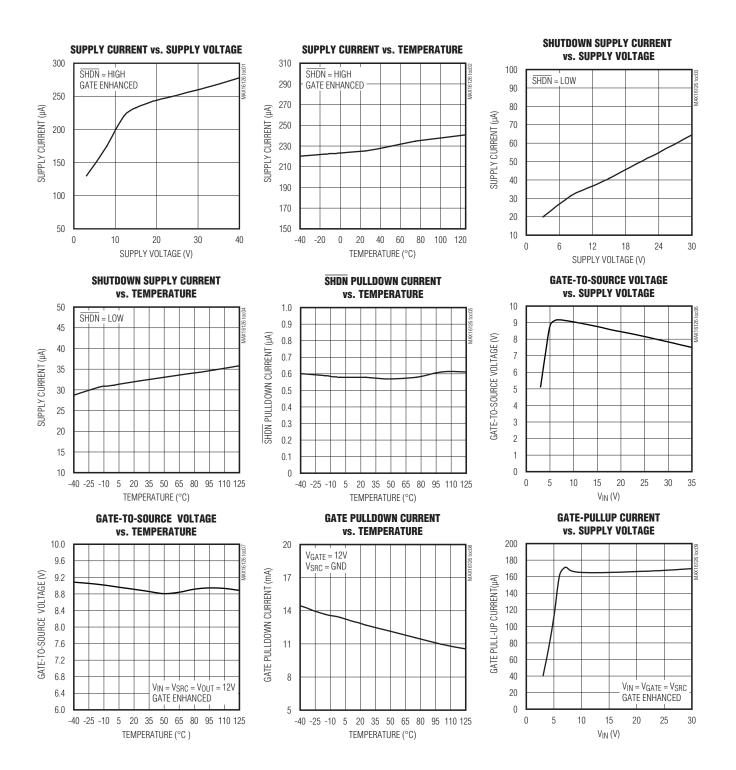

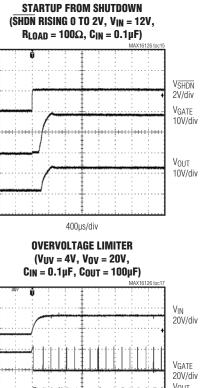

## **Typical Operating Characteristics**

(V<sub>IN</sub> = 12V, T<sub>A</sub> = +25°C, unless otherwise noted.)

# Load-Dump/Reverse-Voltage Protection Circuits

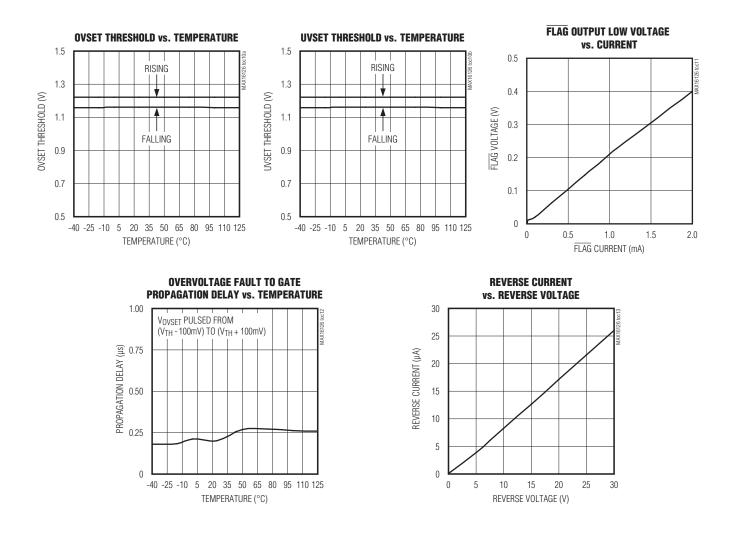

## **Typical Operating Characteristics (continued)**

( $V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.)

Load-Dump/Reverse-Voltage Protection Circuits

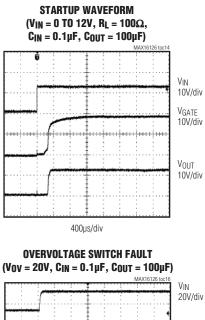

## **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 12V,  $T_A$  = +25°C, unless otherwise noted.)

100ms/div

V<sub>OUT</sub> 10V/div

20ms/div

# Load-Dump/Reverse-Voltage Protection Circuits

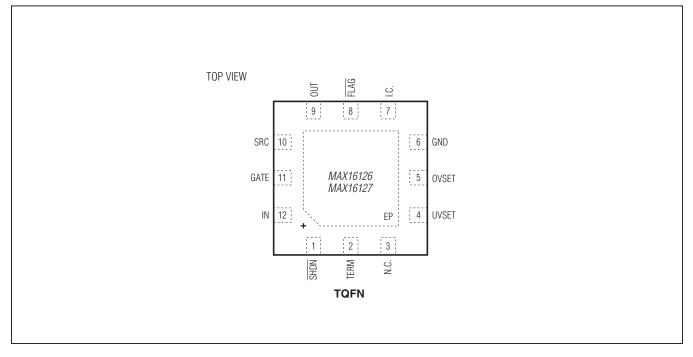

# **Pin Configuration**

## Load-Dump/Reverse-Voltage Protection Circuits

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SHDN  | Shutdown Input. Drive $\overline{SHDN}$ low to force GATE and $\overline{FLAG}$ low and turn off the external n-channel MOSFETs. Connect a 100k $\Omega$ resistor from $\overline{SHDN}$ to IN for normal operation.                                                                                                                              |

| 2   | TERM  | Voltage-Divider Termination Output. TERM is internally connected to IN. TERM is high impedance when SHDN is low, forcing the current to zero in the resistive-divider connected to TERM.                                                                                                                                                          |

| 3   | N.C.  | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                          |

| 4   | UVSET | Undervoltage Threshold Adjustment Input. Connect UVSET to the external resistive voltage-divider network to adjust the desired input undervoltage threshold. Connect the resistive divider to TERM.                                                                                                                                               |

| 5   | OVSET | Overvoltage Threshold Adjustment Input. Connect OVSET to an external resistive voltage-divider network to adjust the desired overvoltage disable or overvoltage limit threshold. Connect the resistive divider to TERM for overvoltage switch-mode applications or to OUT for overvoltage limiting applications.                                  |

| 6   | GND   | Ground                                                                                                                                                                                                                                                                                                                                            |

| 7   | I.C.  | Internally Connected. Connect to GND.                                                                                                                                                                                                                                                                                                             |

| 8   | FLAG  | $\overline{\text{FLAG}}$ Output. During startup, $\overline{\text{FLAG}}$ is low as long as V <sub>OUT</sub> is lower than 90% of V <sub>IN</sub> and after that it is high impedance. It asserts low during shutdown mode, an overvoltage, thermal shutdown, or undervoltage fault or when V <sub>OUT</sub> falls below 90% of V <sub>IN</sub> . |

| 9   | OUT   | Output Voltage-Sense Input. Connect OUT to the load with a $100\Omega$ series resistor. Bypass the load with a minimum $10\mu$ F capacitor to GND.                                                                                                                                                                                                |

| 10  | SRC   | Source Input. Connect SRC to the common source connection of the external MOSFETs. When the MOSFETs are turned off, this connection is clamped to GND. An external zener diode between SRC and GATE protects the gates of the external MOSFETs.                                                                                                   |

| 11  | GATE  | Gate-Driver Output. Connect GATE to the gates of the external n-channel MOSFETs. GATE is the charge-pump output during normal operation. GATE is quickly pulled low during a fault condition or when SHDN is pulled low.                                                                                                                          |

| 12  | IN    | Positive Supply Input Voltage. Connect IN to the positive side of the input voltage. Bypass IN with a 0.1µF ceramic capacitor to GND.                                                                                                                                                                                                             |

|     | EP    | Exposed Pad. Can be connected to GND or left unconnected.                                                                                                                                                                                                                                                                                         |

|     |       |                                                                                                                                                                                                                                                                                                                                                   |

### **Detailed Description**

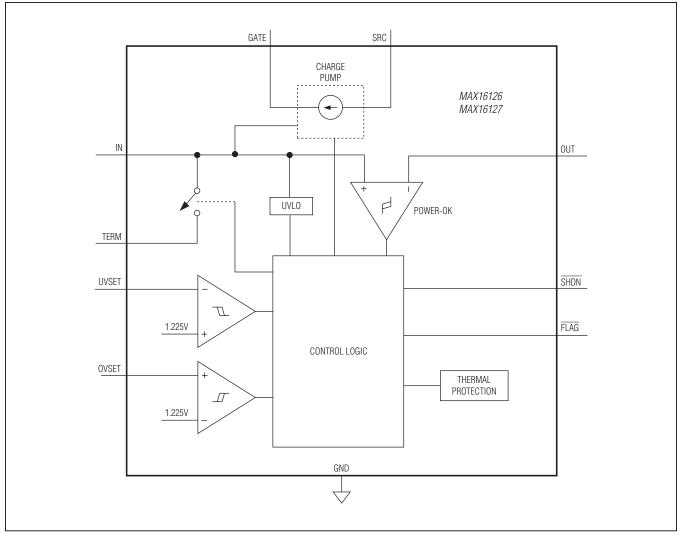

The MAX16126/MAX16127 transient protection circuits are suitable for automotive and industrial applications where high-voltage transients are commonly present on supply voltage inputs. The devices monitor the input voltage and control two external common-source n-channel MOSFETs to protect downstream voltage regulators during load-dump events or other automotive pulse conditions.

The devices feature an overvoltage and an undervoltage comparator for voltage window detection. A flag output  $(\overline{FLAG})$  asserts when a fault event occurs.

Two external back-to-back n-channel MOSFETs provide reverse-voltage protection and also prevent reverse current during a fault condition. Compared to a traditional reverse-battery diode, this approach minimizes power dissipation and voltage drop, and allows the circuit to operate at very low cold-crank voltages (3V minimum).

The MAX16127 provides a limiter-mode fault management for overvoltage and thermal shutdown conditions, whereas the MAX16126 provides switch-mode fault management for overvoltage and thermal shutdown conditions. In the limiter mode, the MOSFETs cycle on and off so the output voltage is limited. In the switch mode, the external MOSFETs are switched off, disconnecting the load from the input. In both cases, FLAG asserts to indicate a fault.

#### Gate Charge Pump

The MAX16126/MAX16127 use a charge pump to generate the GATE to SRC voltage and enhance the external MOSFETs. After the input voltage exceeds the input

## Load-Dump/Reverse-Voltage Protection Circuits

undervoltage threshold, the charge pump turns on after a 150 $\mu s$  delay.

During a fault condition, GATE is pulled to ground with a 8.8mA (min) pulldown current. Note that an external zener diode is required to be connected between the gate and source of the external MOSFETs. See the <u>Applications</u> <u>Information</u> section.

#### **Overvoltage Protection**

The MAX16126/MAX16127 detect overvoltage conditions using a comparator that is connected through an external resistive divider to the input or output voltage. An overvoltage condition causes the GATE output to go low, turning off the external MOSFETs. FLAG also asserts to indicate the fault condition.

#### **Overvoltage Limiter (MAX16127)**

In overvoltage limiter mode, the output voltage is regulated at the overvoltage threshold voltage and continues to supply power to downstream devices. In this mode, the device operates like a voltage regulator.

During normal operation, GATE is enhanced 9V above SRC. The output voltage is monitored through a resistive divider between OUT and OVSET. When OUT rises above the overvoltage threshold, GATE goes low and the MOSFETs turn off. As the voltage on OUT falls below the overvoltage threshold minus the threshold hysteresis, GATE goes high and the MOSFETs turn back on again, regulating OUT in a switched-linear mode at the overvoltage threshold.

The switching frequency depends on the gate charge of the MOSFETs, the charge-pump current, the output load current, and the output capacitance.

Caution must be exercised when operating the MAX16127 in voltage-limiting mode for long durations. Since MOSFETs can dissipate power continuously during this interval, proper heat sinking should be implemented to prevent damage to them.

#### **Overvoltage Switch (MAX16126)**

In the overvoltage switch mode, the internal overvoltage comparator monitors the input voltage and the load is completely disconnected from the input during an overvoltage event. When the input voltage exceeds the overvoltage threshold, GATE goes low and the MOSFETs turn off, disconnecting the input from the load. After that, for the autoretry mode version, the autoretry timer starts, while for the latched mode version a power cycle to IN or a cycle on SHDN is needed to turn the external MOSFETs back on. The MAX16126 can be configured to latch off (suffix **D**) even after the overvoltage condition ends. The latch is cleared by cycling IN below the undervoltage threshold or by toggling  $\overline{SHDN}$ .

The devices can also be configured to retry:

- One time, then latch off (suffix B)

- Three times, then latch off (suffix C)

- Always retry and never latch off (suffix A)

There is a fixed 150ms (typ) delay between each retry attempt. If the overvoltage fault condition is gone when a retry is attempted, GATE goes high and power is restored to the downstream circuitry.

#### **Undervoltage Protection**

The MAX16126/MAX16127 monitor the input voltage for undervoltage conditions. If the input voltage is below the undervoltage threshold ( $V_{IN} < V_{TH} - V_{TH-HYS}$ ), GATE goes low, turning off the external MOSFETs and FLAG asserts. When the input voltage exceeds the undervoltage threshold ( $V_{IN} > V_{TH}$ ), GATE goes high after a 150µs delay (typ).

For the MAX16126/MAX16127, an external resistive divider connected between TERM, UVSET, and GND sets the undervoltage threshold (TERM is connected to IN when  $\overline{SHDN}$  is high).

#### **Thermal Shutdown**

The MAX16126/MAX16127 thermal shutdown feature turns off the MOSFETs if the internal die temperature exceeds +145°C (T<sub>J</sub>). By ensuring good thermal coupling between the MOSFETs and the MAX16126/MAX16127, the thermal shutdown can turn off the MOSFETs if they overheat.

When the junction temperature exceeds  $T_J = +145^{\circ}C$  (typ), the internal thermal sensor signals the shutdown logic, pulling the GATE voltage low and allowing the device to cool. When  $T_J$  drops by 15°C (typ), GATE goes high and the MOSFETs turn back on. Do not exceed the absolute maximum junction-temperature rating of  $T_J = +150^{\circ}C$ .

#### Flag Output (FLAG)

An open-drain  $\overline{FLAG}$  output indicates fault conditions. During startup,  $\overline{FLAG}$  is initially low and goes high impedance when V<sub>OUT</sub> is greater than 90% of V<sub>IN</sub> if no fault conditions are present.  $\overline{FLAG}$  asserts low during shutdown mode, an overvoltage, thermal shutdown, or undervoltage fault, or when V<sub>OUT</sub> falls below 90% of V<sub>IN</sub>.

#### **TERM Connection**

The TERM connection has an internal switch to IN. In shutdown ( $\overline{SHDN} = GND$ ), this switch is open. By connecting the voltage threshold resistive divider to TERM instead of directly to IN, power dissipation in the resistive divider can be eliminated and the shutdown supply current reduced.

#### **Reverse-Voltage Protection**

The MAX16126/MAX16127 integrate reverse-voltage protection, preventing damage to the downstream circuitry caused by battery reversal or negative transients. The devices can withstand reverse voltage to -36V without damage to themselves or the load. During a reverse-voltage condition, the two external n-channel MOSFETs are turned off, protecting the load. Connect a  $0.1\mu$ F ceramic capacitor from IN to GND, connect  $10\mu$ F from the load to GND, and minimize the parasitic capacitance from GATE to GND to have a fast reserve-battery voltage-transient protection. During normal operation, both MOSFETs are turned on and have a minimal forward voltage drop, providing lower power dissipation and a much lower voltage drop than a reverse-battery protection diode.

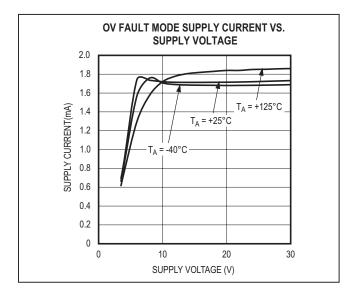

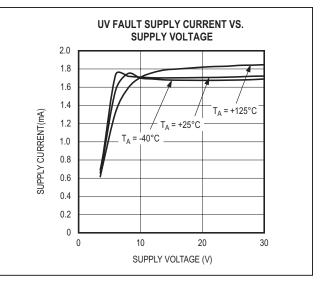

#### **Supply Current During Fault Conditions**

During fault conditions, the MAX16126/MAX16127 supply current is higher than normal operation. When a fault condition occurs, the MAX16126/MAX16127 pulls the gate low but keeps the charge pump active. This results in increased supply because the charge pump tries hard to bring up the gate. See Figures below for supply current during overvoltage and undervotlage fault conditions.

### **Applications Information**

# Automotive Electrical Transients (Load Dump)

Automotive circuits generally require supply voltage protection from various transient conditions that occur in automotive systems. Several standards define various pulses that can occur. Table 1 summarizes the pulses from the ISO 7637-2 and ISO 16750-2 specification.

Most of the pulses can be mitigated with capacitors and zener clamp diodes (see the Typical Operating Characteristics and also the Increasing the Input Voltage Protection Range section). The load dump (pulse 5a and 5b) occurs when the alternator is charging the battery and a battery terminal gets disconnected. Due to the sudden change in load, the alternator goes out of regulation and the bus voltage spikes. The pulse has a rise time of about 10ms and a fall time of about 400ms, but can extend out to 1s or more depending on the characteristics of the charging system. The magnitude of the pulse depends on the bus voltage and whether the system is unsuppressed or uses central load-dump suppression (generally implemented using very large clamp diodes built into the alternator). Table 1 lists the worst-case values from the ISO 7637-2 specification.

Cold crank (pulse 4) occurs when activating the starter motor in cold weather with a marginal battery. Due to the large load imposed by the starter motor, the bus voltage sags. Since the MAX16126/MAX16127 can operate down to 3V, the downstream circuitry can continue to operate through a cold-crank condition. If desired, the undervoltage threshold can be increased so that the MOSFETs turn

## Load-Dump/Reverse-Voltage Protection Circuits

| Table 1. Summary of 150 7037 and 150 10730-2 Pulses |                                |                                  |                 |  |  |

|-----------------------------------------------------|--------------------------------|----------------------------------|-----------------|--|--|

| NAME                                                | DESCRIPTION                    | PEAK VOLTAGE (V) (max)*          | DURATION        |  |  |

|                                                     | DESCRIPTION                    | 12V SYSTEM                       | DURATION        |  |  |

| Pulse 1                                             | Inductive load disconnection   | -100                             | 1ms to 2ms      |  |  |

| Pulse 2a                                            | Inductive wiring disconnection | 50                               | 0.05ms          |  |  |

| Pulse 3a                                            | Switching transients           | -150                             | 0.200           |  |  |

| Pulse 3b                                            | Switching transients           | 100                              | — 0.2µs         |  |  |

| Pulse 4                                             | Cold crank                     | -7                               | 100ms (initial) |  |  |

| Puise 4                                             |                                | -6                               | Up to 20s       |  |  |

| Pulse 5a                                            | Load dump (unsuppressed)       | 87                               | 400ma (single)  |  |  |

| Pulse 5b                                            | Load dump (suppressed)         | (Varies, but less than pulse 5a) | 400ms (single)  |  |  |

#### Table 1. Summary of ISO 7637 and ISO 16750-2 Pulses

\*Relative to system voltage.

off during a cold crank, disconnecting the downstream circuitry. An output reservoir capacitor can be connected from OUT to GND to provide energy to the circuit during the cold-crank condition.

Refer to the ISO 7637-2 specification for details on pulse waveforms, test conditions, and test fixtures.

# Setting Overvoltage and Undervoltage Thresholds (MAX16126)

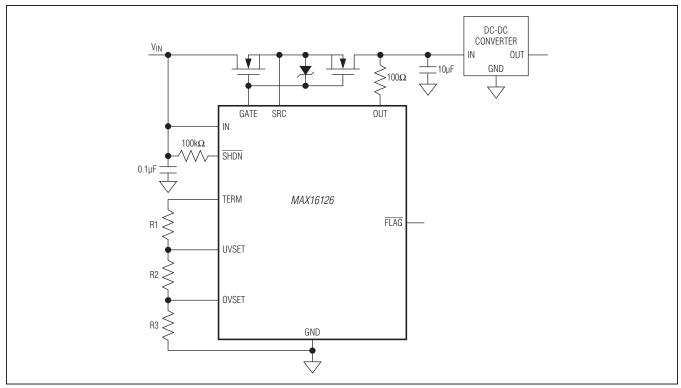

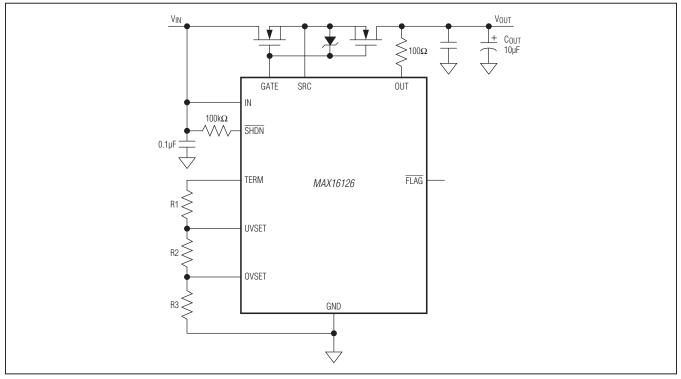

The MAX16126 uses an external resistive divider to set the overvoltage and undervoltage thresholds. The MAX16126 operates in switch mode in which the internal overvoltage comparator monitors the input voltage. It uses three resistors in a single resistive divider to set the undervoltage and overvoltage thresholds. The top of the resistive divider connects to TERM (see Figure 1).

The MAX16126 includes internal undervoltage and overvoltage comparators for window detection. GATE is enhanced and the n-channel MOSFETs are on when the IN voltage is within the selected window. When the monitored voltage falls below the lower limit ( $V_{TRIPLOW}$ ) or exceeds the upper limit ( $V_{TRIPHIGH}$ ) of the window, the GATE voltage goes to GND, turning off the MOSFETs. The circuit in Figure 1 shows the MAX16126 enabling the DC-DC converter when the monitored voltage is in the selected window.

The resistor values R1, R2, and R3 can be calculated as follows:

$$V_{\text{TRIPLOW}} = (V_{\text{TH}} - V_{\text{TH-HYS}}) \left(\frac{R_{\text{TOTAL}}}{R2 + R3}\right)$$

$$V_{\text{TRIPHIGH}} = V_{\text{TH}} \left(\frac{R_{\text{TOTAL}}}{R3}\right)$$

where  $R_{TOTAL}$  = R1 + R2 + R3,  $V_{TH}$  is the 1.225V OVSET/UVSET threshold, and  $V_{TH-HYS}$  is the hysteresis.

Use the following steps to determine the values for R1, R2, and R3:

- 1) Choose a value for R<sub>TOTAL</sub>, the sum of R1, R2, and R3.

- 2) Calculate R3 based on R<sub>TOTAL</sub> and the desired upper trip point:

$$R3 = \frac{V_{TH} \times R_{TOTAL}}{V_{TRIPHIGH}}$$

3) Calculate R2 based on R<sub>TOTAL</sub>, R3, and the desired lower trip point:

$$R2 = \frac{(V_{TH} - V_{TH-HYS}) \times R_{TOTAL}}{V_{TRIPLOW}} - R3$$

4) Calculate R1 based on RTOTAL, R2, and R3:

## Load-Dump/Reverse-Voltage Protection Circuits

Figure 1. Overvoltage and Undervoltage Window Detector Circuit (MAX16126)

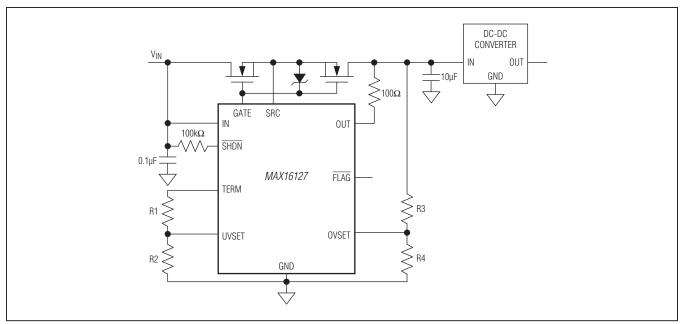

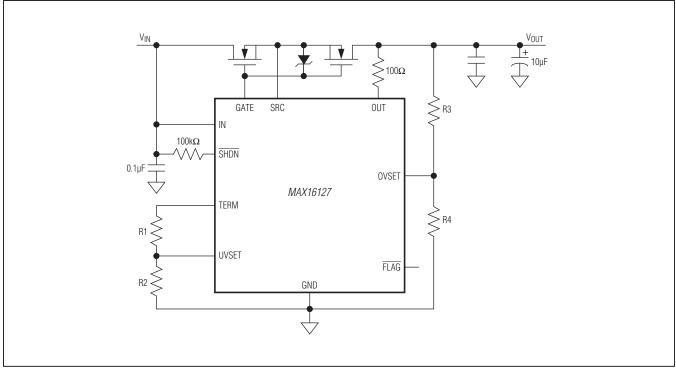

# Setting Overvoltage and Undervoltage Thresholds (MAX16127)

The MAX16127 operates in limiter mode and uses separate resistive dividers to set the undervoltage and overvoltage thresholds. The top of the overvoltage divider connects to OUT and the top of the undervoltage divider connects to TERM (see Figure 2).

Use the following formula to calculate R4:

$$R4 = V_{TH} \times \frac{R_{TOTAL} OV}{V_{OV}}$$

where  $R_{TOTAL OV} = R3 + R4$ ,  $V_{TH}$  is the 1.225V OVSET rising threshold, and  $V_{OV}$  is the desired overvoltage threshold. The falling threshold of  $V_{TH}$  is 5% below the rising threshold.

Similarly, to calculate the values of R1 and R2:

$$R2 = (V_{TH} - V_{TH-HYS}) \times \frac{R_{TOTAL_UV}}{V_{UV}}$$

where  $R_{TOTAL\_UV} = R1 + R2$ ,  $V_{TH}$  is the 1.225V UVSET rising threshold,  $V_{TH-HYS}$  is the hysteresis, and  $V_{UV}$  is the desired undervoltage threshold.

Use the nearest standard-value resistor that is less than the calculated value. A lower value for total resistance dissipates more power, but provides slightly better accuracy.

#### **MOSFET Selection**

MOSFET selection is critical to design a proper protection circuit. Several factors must be taken into account: the gate capacitance, the drain-to-source voltage rating, the on-resistance ( $R_{DS(ON)}$ ), the peak power dissipation capability, and the average power dissipation limit. In general, both MOSFETs should have the same part number. For size-constrained applications, a dual MOSFET can save board area. Select the drain-to-source voltage so that the MOSFETs can handle the highest voltage that might be applied to the circuit. Gate capacitance is not as critical, but it does determine the maximum turn-on and turn-off time. MOSFETs with more gate capacitance tend to respond more slowly.

## Load-Dump/Reverse-Voltage Protection Circuits

Figure 2. Overvoltage and Undervoltage Limiter Protection Configuration (MAX16127)

#### **MOSFET Power Dissipation**

The  $R_{DS(ON)}$  must be low enough to limit the MOSFET power dissipation during normal operation. Power dissipation (per MOSFET) during normal operation can be calculated using this formula:

#### $P = I_{LOAD}^2 \times R_{DS(ON)}$

where P is the power dissipated in each MOSFET and  $I_{\mbox{LOAD}}$  is the average load current.

During a fault condition in switch mode, the MOSFETs turn off and do not dissipate power. Limiter mode imposes the worst-case power dissipation. The average power can be computed using the following formula:

#### $P = I_{LOAD} \times (V_{IN} - V_{OUT})$

where P is the average power dissipated in both MOSFETs, I<sub>LOAD</sub> is the average load current, V<sub>IN</sub> is the input voltage, and V<sub>OUT</sub> is the average limited voltage on the output. In limiter mode, the output voltage is a sawtooth wave with characteristics determined by the R<sub>DS(ON)</sub> of the MOSFETs, the output load current, the output capacitance, the gate charge of the MOSFETs, and the GATE charge-pump current.

Since limiter mode can involve high switching currents when the GATE is turning on at the start of a limiting cycle (especially when the output capacitance is high), it is important to ensure the circuit does not violate the peak power rating of the MOSFETs. Check the pulse power ratings in the MOSFET data sheet.

#### **MOSFET Gate Protection**

To protect the gate of the MOSFETs, connect a zener clamp diode from the gate to the source. The cathode connects to the gate, and the anode connects to the source. Choose the zener clamp voltage to be above 10V and below the MOSFET V<sub>GS</sub> maximum rating.

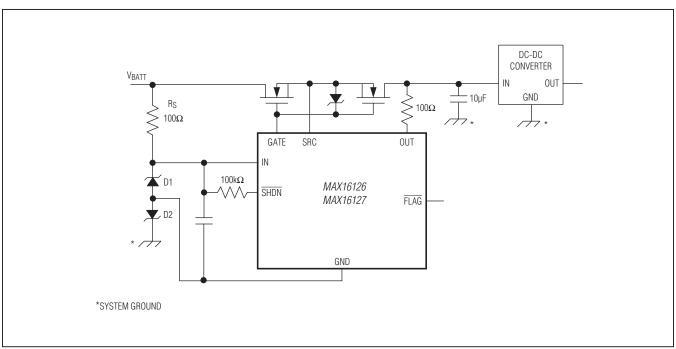

#### Increasing the Input Voltage Protection Range

The MAX16126/MAX16127 can tolerate -36V to +90V. To increase the positive input voltage range protection, connect two back-to-back zener diodes from IN to system ground, and connect a resistor in series with IN and the power-supply input to limit the current drawn by the zener diodes (see Figure 3).

Zener diode D1 clamps positive voltage excursions and D2 clamps negative voltage excursions. Set the zener voltages so the worst-case voltages do not exceed the ratings of the part. Also ensure that the zener diode power ratings are not exceeded. The combination of the series resistor and the zener diodes also help snub pulses on the supply voltage input and can aid in clamping the low-energy ISO 7637-2 pulses.

## Load-Dump/Reverse-Voltage Protection Circuits

It is important to compute the peak power dissipation in the series resistor. Most standard surface-mount resistors cannot withstand the peak power dissipation during certain pulse events. Check the resistor data sheets for pulse power derating curves. If necessary, connect multiple resistors in parallel or use automotiverated resistors.

The shutdown input needs a series resistor to limit the current if  $V_{IN}$  exceeds the clamped voltage on IN. A good starting point is  $100 k\Omega$

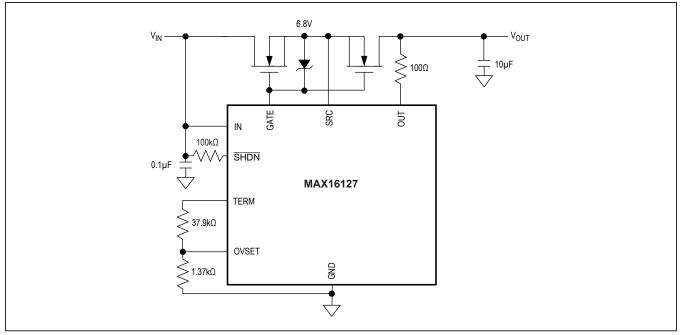

#### Increasing the Input Voltage Operating Range

With proper external component selection, the MAX16126/ MAX16127's input voltage operating range can be extended beyond 30V. Normally the input voltage can swing up to 90V in protection mode, but normal operation is listed in the electrical characteristics table to 30V. Higher voltage operation is permissible so long as the resulting GATE bias voltage does not exceed 45V with respect to GND.

To enable operating voltages above 30V, a 6.8V Zener diode clamp can be added GATE-to-SRC to the external switches to limit the maximum GATE voltage.

The circuit in Figure 4 shows the recommended arrangement. When V<sub>IN</sub> = 35V, V<sub>GATE</sub> = 35V + 6.8V or 41.8V. When V<sub>IN</sub> > 35V, the MAX16126/MAX16127 detects the input over voltage condition by sensing the voltage at the OVSET pin and turns off the charge pump. The resistive voltage divider on OVSET must be selected to disable the circuit before the gate voltage reaches 45V. The MAX16126TCA/MAX16127TCA automatically reenable GATE drive when the input voltage drops 5% below the overvoltage threshold. For the MAX16126TCD, the latch-mode option, GATE drive is enabled by either power cycling the IN voltage below UVLO threshold or by toggling SHDN. See the <u>Ordering Information</u> section for other available options.

#### **Output Reservoir Capacitor**

The output capacitor can be used as a reservoir capacitor to allow downstream circuitry to ride out fault transient conditions. Since the voltage at the output is protected from input voltage transients, the capacitor voltage rating can be less than the expected maximum input voltage.

Figure 3. Circuit to Increase Input Voltage Protection Range

# Load-Dump/Reverse-Voltage Protection Circuits

Figure 4. Use of a 6.8V Zener Clamp to Enable Operation with  $V_{IN}$  Up to 35V

Figure 5. MAX16126 Typical Operating Circuit

# Load-Dump/Reverse-Voltage Protection Circuits

Figure 6. MAX16127 Typical Operating Circuit

Load-Dump/Reverse-Voltage Protection Circuits

Figure 7. MAX16126/MAX16127 Functional Diagram

# Load-Dump/Reverse-Voltage Protection Circuits

## **Ordering Information**

| PART            | PIN-PACKAGE | TOP MARK | PACKAGE CODE |              | FUNCTION                  |  |

|-----------------|-------------|----------|--------------|--------------|---------------------------|--|

| MAX16126TCA+    | 12 TQFN-EP  | +ABV     | T1233+4      |              | Alwaya autoratry          |  |

| MAX16126TCA/V+  | 12 TQFN-EP  | +ACR     | T1233+4      |              | Always autoretry          |  |

| MAX16126TCA/VY+ | 12 TQFN-EP  | +AGV     | T1233Y+5     |              |                           |  |

| MAX16126TCB+    | 12 TQFN-EP  | +ABX     | T1233+4      |              |                           |  |

| MAX16126TCB/V+  | 12 TQFN-EP  | +ADT     | T1233+4      | Switch mode  | One retry, then latch     |  |

| MAX16126TCC+    | 12 TQFN-EP  | +ABY     | T1233+4      | -            | <b>T</b> 1                |  |

| MAX16126TCC/V+  | 12 TQFN-EP  | +ADU     | T1233+4      |              | Three retries, then latch |  |

| MAX16126TCD+    | 12 TQFN-EP  | +ABZ     | T1233+4      |              | l stels wesde             |  |

| MAX16126TCD/V+* | 12 TQFN-EP  | +ADH     | T1233+4      |              | Latch mode                |  |

| MAX16127TC+     | 12 TQFN-EP  | +ABW     | T1233+4      | Limiter mode |                           |  |

| MAX16127TC/V+   | 12 TQFN-EP  | +AGC     | T1233+5      | Limiter mode |                           |  |

Note: All devices are specified over the -40°C to +125°C temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

N denotes an automotive qualified part.

\*Future product—contact factory for availability. EP = Exposed pad.

### **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO.   | LAND<br>PATTERN NO. |

|-----------------|-----------------|------------------|---------------------|

| 12 TQFN-EP      | T1233+4         | <u>21-0136</u>   | <u>90-0019</u>      |

| 12 TQFN-EP      | T1233Y+4        | <u>21-100171</u> | <u>90-100060</u>    |

| 12 TQFN-EP      | T1233+5         | <u>21-100319</u> | <u>90-0019</u>      |

# Load-Dump/Reverse-Voltage Protection Circuits

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                             | PAGES<br>CHANGED     |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 0                  | 11/11            | Initial release                                                                                                                                                                                                         | —                    |

| 1                  | 6/12             | Revised the Electrical Characteristics, Typical Operating Characteristics, the Overvoltage Limiter (MAX16127), Reverse-Voltage Protection, and the Increasing the Input Voltage Protection Range sections and Figure 3. | 1–3, 4, 9, 10,<br>14 |

| 2                  | 12/12            | Updated Input Supply Current, SRC Input Current, and GATE Output Voltage High Above V <sub>SRC</sub> conditions in the <i>Electrical Characteristics</i> and updated Figure 3                                           | 2, 3, 14             |

| 3                  | 12/13            | Updated Figure 3                                                                                                                                                                                                        | 12                   |

| 4                  | 1/14             | Added /V automotive OPNs to Ordering Information                                                                                                                                                                        | 18                   |

| 5                  | 10/14            | Added Increasing the Input Voltage Operating Range section and new Figure 4                                                                                                                                             | 14–17                |

| 6                  | 3/15             | Updated Benefits and Features section                                                                                                                                                                                   | 1                    |

| 7                  | 8/17             | Corrected Ordering Information table                                                                                                                                                                                    | 18                   |

| 8                  | 4/18             | Added Supply Current During Fault Conditions section                                                                                                                                                                    | 10                   |

| 9                  | 9/18             | Updated the <i>Pin Description</i> table and <i>Reverse-Voltage Protection</i> section. Added MAX16127TC/V+* to <i>Ordering Information</i> and package code T1233+5 to the <i>Package Information</i> .                | 8, 10, 18            |

| 10                 | 12/18            | Updated Electrical Characteristics, Ordering Information, and Package Information                                                                                                                                       | 2, 3, 18             |

| 11                 | 6/19             | Updated Package Thermal Characteristics                                                                                                                                                                                 | 2                    |

| 12                 | 8/19             | Updated Electrical Characteristics, Detailed Description, Applications Information, and Ordering Information                                                                                                            | 2, 3, 9–16, 18       |

| 13                 | 10/19            | Updated Ordering Information                                                                                                                                                                                            | 18                   |

| 14                 | 11/19            | Updated Ordering Information                                                                                                                                                                                            | 18                   |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.