# Processor Power Management Subsystem

#### **DESCRIPTION**

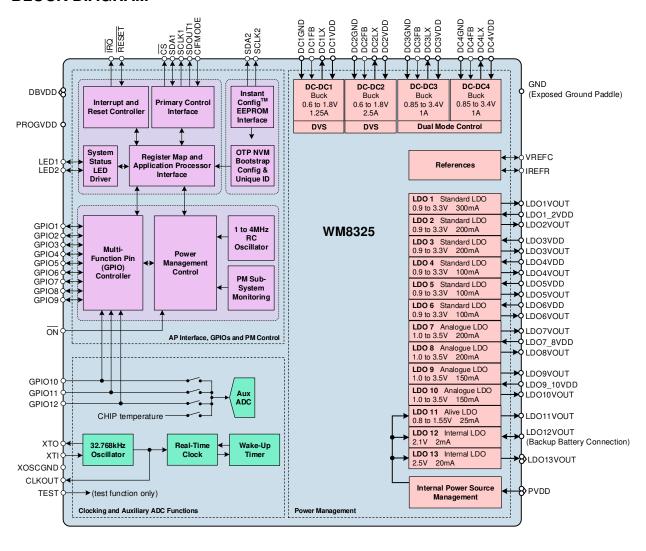

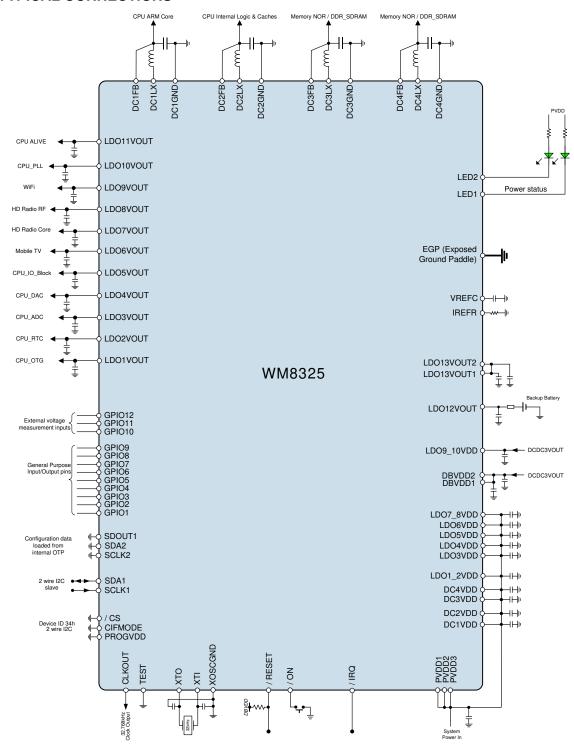

The WM8325 is an integrated power-management subsystem which provides a cost-effective, flexible, single-chip solution for power management. It is specifically targeted at the requirements of a range of low-power portable consumer products, but is suitable to any application with a multimedia processor. The WM8325 is designed to operate as a system PMIC supporting the ARM9™, ARM11™ and ARM Cortex-A™ processors, but is also capable of supporting the majority of application and mobile processors at the heart of a wide range of low-power consumer multimedia applications.

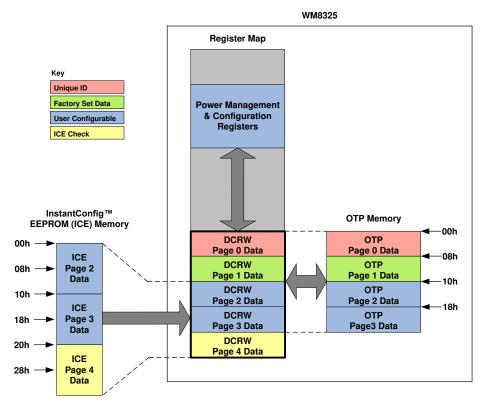

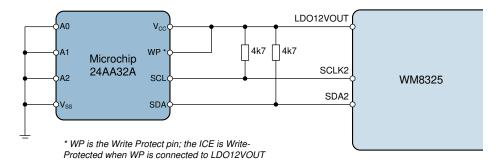

The start-up behaviour and configuration is fully programmable in an integrated OTP non-volatile memory. This highly flexible solution helps reduce time-to-market, as changing application requirements can be very easily accommodated in the OTP. The InstantConfig $^{\text{TM}}$  interface enables an external EEPROM to configure the WM8325.

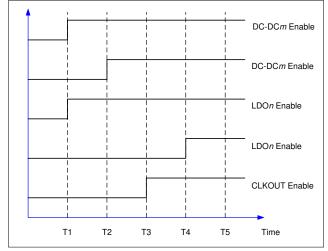

The WM8325 power management subsystem comprises four programmable DC-DC converters and eleven LDO regulators (four of which are low-noise for supplying sensitive analogue subsystems). The integrated OTP bootstrap circuitry controls the start-up sequencing and voltages of the converters and regulators as well as the sequencing of system clocks.

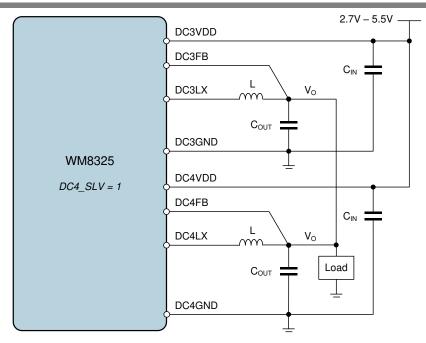

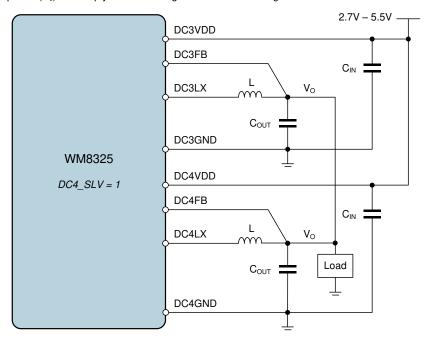

The DC-DC converters deliver high performance and high efficiency across a wide range of operating conditions. They are optimised to support the high load current transients seen in modern processor core domains. DC-DC3 / DC-DC4 can be connected together and operated in 'dual' mode to support an increased current load of up to 1.6A

An on-chip regulator provides power for always-on PMIC functions such as register map and the RTC. The device provides autonomous backup battery switchover. A low-power LDO is included to support 'Alive' processor power domains external to the WM8325.

A 12-bit Auxiliary ADC supports a wide range of applications for internal as well as external analogue sampling, such as voltage detection and temperature measurement.

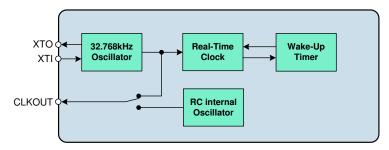

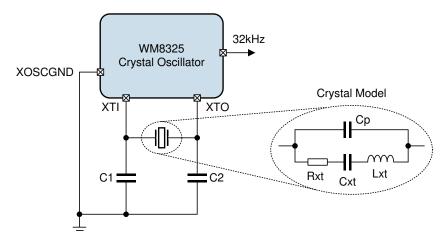

WM8325 includes a crystal oscillator and an internal RC oscillator to generate all clock signals for autonomous system start-up and processor clocking. A Secure Real-time Clock (S-RTC) and alarm function is included, capable of waking up the system from low-power modes. A watchdog function is provided to ensure system integrity.

To maximise battery life, highly-granular power management enables each function in the WM8325 subsystem to be independently powered down through a control interface or alternatively through register and OTP-configurable GPIOs. The device offers a standby power consumption of <7uA, making it particularly suitable for portable applications.

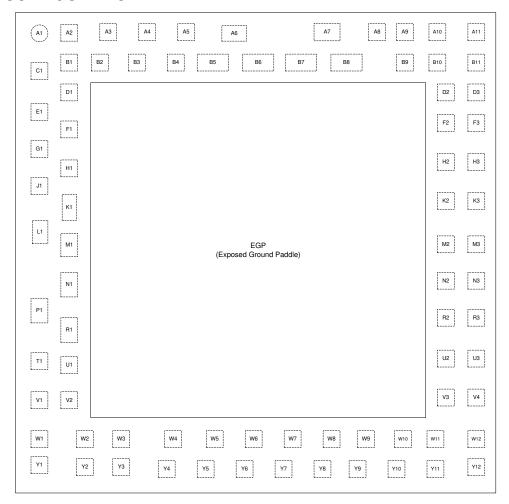

The WM8325 is supplied in an 8x8mm 81-lead QFN package, ideal for use in portable systems. The WM8325 forms part of the Cirrus series of audio and power management solutions, and is widely register compatible with the WM831X devices.

#### **FEATURES**

#### **Power Management**

- 1 x DC-DC synchronous buck converter (0.6V - 1.8V, 2.5A, DVS)

- 1 x DC-DC synchronous buck converter (0.6V - 1.8V, 1.25A, DVS)

- 2 x DC-DC synchronous buck converters (0.85V - 3.4V, 1A)

- 1 x LDO regulator (0.9V 3.3V, 300mA, 1Ω)

- 2 x LDO regulators (0.9V 3.3V, 200mA, 1Ω)

- 3 x LDO regulators (0.9V 3.3V, 100mA, 2Ω)

- 2 x Low-noise LDO regulators (1.0V 3.5V, 200mA, 1Ω)

- 2 x Low-noise LDO regulators (1.0V 3.5V, 150mA, 2Ω)

- 1 x 'Alive' regulator (0.8V 1.55V, up to 25mA)

#### **System Control**

- I<sup>2</sup>C or SPI compatible primary control interface

- Comprehensive interrupt scheme

- Watchdog timer and system reset control

- Autonomous power sequencing and fault detection

- OTP memory bootstrap configuration function

#### **Additional Features**

- Auxiliary ADC for multi-function analogue measurement

- 128-bit pseudo-random unique ID

- Secure Real-Time Clock with wake-up alarm

- 12 x configurable multi-function (GPIO) pins

- Comprehensive clocking scheme: low-power 32kHz RTC crystal oscillator, GPIO clock output and 4MHz RC clock for power management

- System LED outputs indicating device power state, and fault status

#### **Package Options**

• 8 x 8 x 0.85mm, 81-lead QFN package

#### **APPLICATIONS**

- Cellular Handsets

- Smartphones

- Electronic Books

- Portable Media Players

- Mobile Internet Devices

- Electronic Gaming Devices

- Netbooks

- Smartbooks

- Set Top Box

- Digital Picture Frames

#### **BLOCK DIAGRAM**

#### **TYPICAL APPLICATIONS**

The WM8325 is designed as a system PMIC device that generates configurable DC supplies to power processors and associated peripherals within a system. The WM8325 provides four DC-DC synchronous buck (step-down) converters. Two of these can operate in dual mode, providing an increased current capability. Eleven LDO regulators provide a high degree of flexibility to provide power to multiple devices, with the capability to power-up and power-down different circuits independently.

Two of the DC-DC buck converters incorporate BuckWise™ technology specifically designed to handle rapid changes in load current; programmable slew rate DVS is also provided, as required by modern application processors. Selectable operating modes on all of the DC-DC converters allow each converter to be optimally configured for light, heavy or transient load conditions. Flexible operating configurations allow the converters to be tailored for minimum PCB area, maximum performance, or for maximum efficiency. The analogue LDOs provide low-noise outputs suitable for powering sensitive circuits such as RF / Wi-Fi / cellular handset applications.

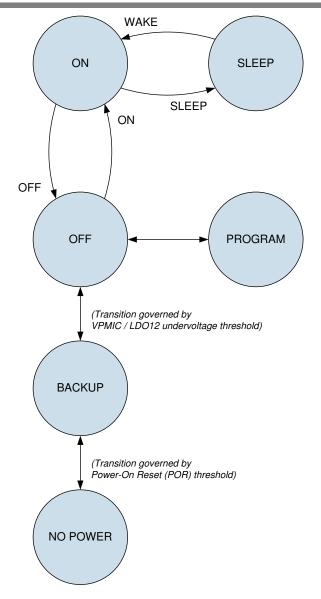

The WM8325 powers up the converters and LDOs according to a programmable sequence. A configurable 'SLEEP' state is also available, providing support for an alternate configuration, typically for low-power / standby operation. The power control sequences and many other parameters can be stored in an integrated user-configurable OTP (One-Time Programmable) memory or may be loaded from an external memory. The WM8325 supports the programming and verification of the integrated OTP memory.

A backup battery supply can be connected to the WM8325 in order to maintain the Real Time Clock (RTC) in the absence of the primary supply.

Programmable GPIO pins may be configured as hardware inputs for general use or for selecting different power management configurations. As outputs, the GPIOs can provide indications of the device status, or may be used as control signals for other power management circuits. The WM8325 also provides two LED drivers, which can be controlled manually or configured as status indicators for the OTP memory programmer or operating power state.

## **TABLE OF CONTENTS**

| DES         | CRIPTION                                    | . 1 |

|-------------|---------------------------------------------|-----|

| <b>FEA</b>  | rures                                       | . 1 |

| APPI        | LICATIONS                                   | . 1 |

| BLO         | CK DIAGRAM                                  | . 2 |

| TYPI        | CAL APPLICATIONS                            | . 3 |

|             | LE OF CONTENTS                              |     |

|             | PIN CONFIGURATION                           |     |

|             | ORDERING INFORMATION                        |     |

|             | PIN DESCRIPTION                             |     |

| 4           | THERMAL CHARACTERISTICS                     | 13  |

| -           | ABSOLUTE MAXIMUM RATINGS                    |     |

| 6           | RECOMMENDED OPERATING CONDITIONS            |     |

| 7           | ELECTRICAL CHARACTERISTICS                  |     |

| 7.1         | DC-DC SYNCHRONOUS BUCK CONVERTERS           | 16  |

| 7.2         | LDO REGULATORS                              |     |

| 7.3         | RESET THRESHOLDS                            |     |

| 7.4         | REFERENCES                                  |     |

| 7.5         | GENERAL PURPOSE INPUTS / OUTPUTS (GPIO)     |     |

| 7.6         | DIGITAL INTERFACES                          |     |

| 7.7         | AUXILIARY ADC                               | 25  |

| 7.8         | SYSTEM STATUS LED DRIVERS                   |     |

|             | RESERVED                                    |     |

|             | RESERVED                                    |     |

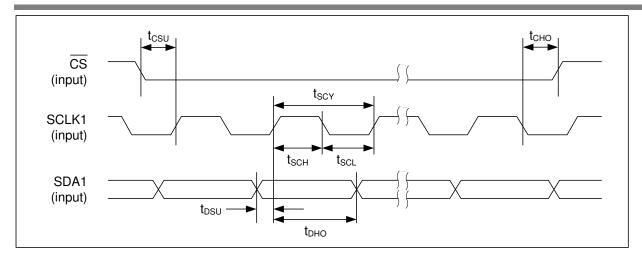

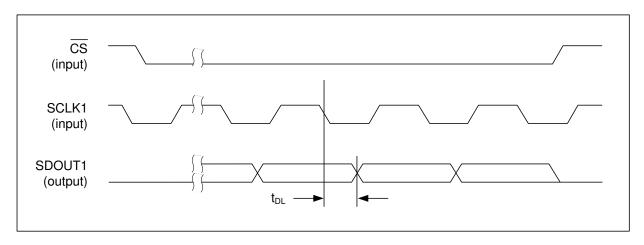

|             | SIGNAL TIMING REQUIREMENTS                  |     |

| 10.         |                                             |     |

|             | DEVICE DESCRIPTION                          |     |

| 11.         |                                             |     |

| 11.2        |                                             |     |

| 11.3        |                                             |     |

| 11.4        |                                             |     |

| 11.!<br>11. |                                             |     |

| 11.         |                                             |     |

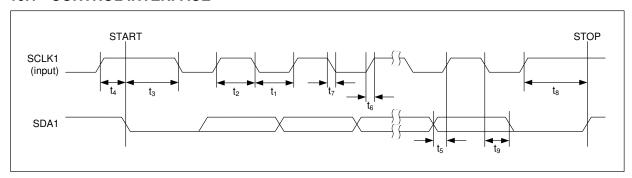

|             | CONTROL INTERFACE                           |     |

| 12.         |                                             |     |

| 12.         |                                             |     |

| 12.         |                                             | 42  |

| 12.4        | 4 REGISTER LOCKING                          | 42  |

| 12.         | SOFTWARE RESET AND CHIP ID                  | 43  |

| 12.0        |                                             |     |

| 13          | CLOCKING AND OSCILLATOR CONTROL             |     |

| 13.         |                                             | 44  |

| 13.2        |                                             |     |

| 13.3        |                                             |     |

|             | INSTANTCONFIG™ (ICE) AND OTP MEMORY CONTROL | 48  |

| 14.         |                                             |     |

| 14.2        | 2 ICE AND OTP MEMORY DEFINITION             | 48  |

| 14.3  | ВО           | OTSTRAP (START-UP) FUNCTION                                   | 49 |

|-------|--------------|---------------------------------------------------------------|----|

| 14    | .3.1         | START-UP FROM OTP MEMORY                                      | 49 |

| 14    | .3.2         | START-UP FROM ICE MEMORY (DEVELOPMENT MODE)                   | 50 |

| 14    | .3.3         | START-UP FROM DCRW REGISTER SETTINGS                          |    |

|       | .3.4         | EXTERNAL ICE MEMORY CONNECTION                                |    |

| 14.4  | OT           | P / ICE MEMORY CONTROL                                        |    |

| 14    | .4.1         | ENTERING / EXITING THE PROGRAM STATE                          |    |

|       | .4.2         | OTP / ICE READ COMMAND                                        |    |

|       | .4.3         | OTP WRITE COMMAND                                             |    |

|       | .4.4         | OTP VERIFY COMMAND                                            |    |

|       | .4.5         | OTP FINALISE COMMAND                                          |    |

| 14.5  | .4.6<br>OT   | OTP CONTROL REGISTERP / ICE INTERRUPTS                        |    |

| 14.5  |              | RW MEMORY CONTENTS                                            |    |

|       | .6.1         | DCRW PAGE 0                                                   |    |

|       | .6.1<br>.6.2 | DCRW PAGE 1                                                   |    |

|       | .6.3         | DCRW PAGE 2                                                   |    |

|       | .6.4         | DCRW PAGE 3                                                   |    |

|       | .6.5         | DCRW PAGE 4                                                   |    |

| 15 PC | OWE          | R MANAGEMENT                                                  |    |

| 15.1  | _            | NERAL DESCRIPTION                                             | _  |

| 15.2  |              | -DC CONVERTER AND LDO REGULATOR ENABLE                        |    |

| 15.3  |              | IESLOT CONTROL AND HARDWARE ENABLE (GPIO) CONTROL             |    |

| 15.4  |              | ERATING MODE CONTROL                                          |    |

| 15    | .4.1         | DC-DC SYNCHRONOUS BUCK CONVERTERS                             |    |

| 15    | .4.2         | LDO REGULATORS                                                |    |

| 15.5  | OU           | TPUT VOLTAGE CONTROL                                          | 63 |

| 15    | .5.1         | DC-DC SYNCHRONOUS BUCK CONVERTERS                             | 63 |

| 15    | .5.2         | LDO REGULATORS 1-10                                           |    |

|       | .5.3         | LDO REGULATOR 11                                              |    |

| 15.6  | DC           | -DC SYNCHRONOUS BUCK CONVERTER CONTROL                        |    |

|       | .6.1         | DC-DC3 / DC-DC4 DUAL MODE                                     |    |

| 15.7  |              | O REGULATOR CONTROL                                           |    |

| 15.8  |              | RDWARE CONTROL (GPIO)                                         |    |

| 15.9  |              | JLT PROTECTION                                                |    |

| 15.10 |              | NITORING AND FAULT REPORTING                                  |    |

| 15.11 | _            | WER MANAGEMENT REGISTER DEFINITIONS                           |    |

|       | .11.1        | DC-DC CONVERTER AND LDO REGULATOR ENABLE                      |    |

|       | .11.2        | DC-DC SYNCHRONOUS BUCK CONVERTER CONTROLLDO REGULATOR CONTROL |    |

|       |              | EXTERNAL POWER ENABLE (EPE) CONTROL                           |    |

|       |              | MONITORING AND FAULT REPORTING                                |    |

| 15.12 |              | WER MANAGEMENT INTERRUPTS                                     |    |

|       |              | WER GOOD INDICATION                                           |    |

| 15.14 |              | -DC SYNCHRONOUS BUCK CONVERTER OPERATION                      |    |

| _     |              | OVERVIEW                                                      |    |

|       |              | DC-DC SYNCHRONOUS BUCK CONVERTERS                             |    |

| _     |              | O REGULATOR OPERATION                                         |    |

|       |              | OVERVIEW                                                      |    |

| 15    |              | LDO REGULATORS                                                |    |

| 16 RI | ESEF         | RVED                                                          | 94 |

|       |              | R SUPPLY CONTROL                                              |    |

| 17.1  | GE           | NERAL DESCRIPTION                                             | 95 |

| 17.2  | PO           | WER PATH MANAGEMENT INTERRUPTS                                | 95 |

| 17. | .3 BA            | ACKUP POWER                                       | 95   |

|-----|------------------|---------------------------------------------------|------|

| 18  |                  | LIARY ADC                                         |      |

| 18. | .1 GI            | ENERAL DESCRIPTION                                | 96   |

| 18. | .2 AL            | JXADC CONTROL                                     | 96   |

| 18. |                  | JXADC READBACK                                    |      |

| 18. | .4 DI            | GITAL COMPARATORS                                 | 99   |

| 18. | .5 AL            | JXADC INTERRUPTS                                  | .101 |

| 19  | <b>RESE</b>      | RVED                                              | 101  |

| 20  | <b>REAL</b>      | -TIME CLOCK (RTC)                                 | 102  |

| 20. |                  | ENERAL DESCRÌPTION                                |      |

| 20. | .2 R1            | TC CONTROL                                        | .102 |

| 20. | .3 R1            | TC INTERRUPTS                                     | .104 |

| 20. | 4 DI             | IGITAL RIGHTS MANAGEMENT                          | .105 |

| 20. | .5 BA            | ACKUP MODE CLOCKING OPTIONS                       | .105 |

| 21  | GENE             | ERAL PURPOSE INPUTS / OUTPUTS (GPIO)              | 106  |

| 21. |                  | ENERAL DESCRIPTION                                |      |

| 21. | .2 GI            | PIO FUNCTIONS                                     | .106 |

| 21. | .3 CC            | ONFIGURING GPIO PINS                              | .108 |

| 21. | .4 GF            | PIO INTERRUPTS                                    | .112 |

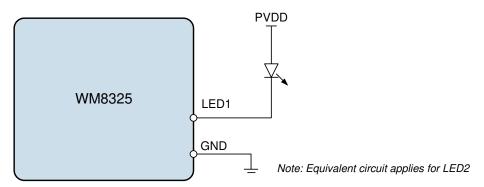

| 22  | SYST             | EM STATUS LED DRIVERS                             | 113  |

| 22. | .1 GI            | ENERAL DESCRIPTION                                | .113 |

| 22. | .2 LE            | ED DRIVER CONTROL                                 | .113 |

|     | 22.2.1           | OTP PROGAM STATUS                                 | 113  |

|     | 22.2.2           | POWER STATE STATUS                                | 114  |

|     | 22.2.3           | MANUAL MODE                                       |      |

|     |                  | ED DRIVER CONNECTIONS                             |      |

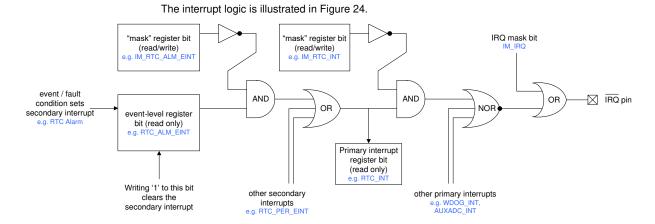

| 23  |                  | RRUPT CONTROLLER                                  |      |

| _   |                  | RIMARY INTERRUPTS                                 |      |

| 23. | .2 SE            | ECONDARY INTERRUPTS                               |      |

|     | 23.2.1           | POWER STATE INTERRUPT                             |      |

|     | 23.2.2           | THERMAL INTERRUPTS                                |      |

|     | 23.2.3           | GPIO INTERRUPTS                                   |      |

|     | 23.2.4           | ON PIN INTERRUPTS                                 |      |

|     | 23.2.5<br>23.2.6 | WATCHDOG INTERRUPTSAUXADC INTERRUPTS              |      |

|     | 23.2.7           | POWER PATH MANAGEMENT INTERRUPTS                  |      |

|     | 23.2.7           | REAL TIME CLOCK AND CRYSTAL OSCILLATOR INTERRUPTS |      |

|     | 23.2.9           | OTP MEMORY INTERRUPTS                             |      |

|     | 23.2.10          |                                                   |      |

|     | 23.2.11          | UNDERVOLTAGE INTERRUPTS                           | 125  |

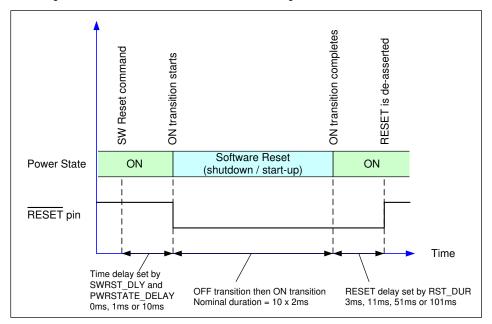

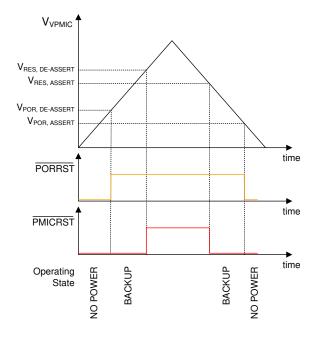

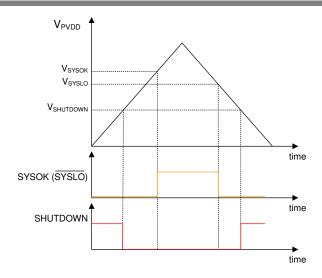

| 24  | RESE             | TS AND SUPPLY VOLTAGE MONITORING                  | 126  |

| 24. |                  | ESETS                                             |      |

| 24. | .2 H             | ARDWARE RESET                                     | .128 |

| 24. |                  | OFTWARE RESET                                     |      |

| 24. | .4 Sl            | JPPLY VOLTAGE MONITORING                          | .130 |

| 25  | WATC             | CHDOG TIMER                                       | 132  |

| 26  | TEMP             | PERATURE SENSING                                  | 134  |

|     |                  | AGE AND CURRENT REFERENCES                        |      |

|     |                  | OLTAGE REFERENCE (VREF)                           |      |

|     |                  | URRENT REFERENCE (IREF)                           |      |

# **WM8325**

7

| 28  | REG    | SISTER       | MAP      | OVERVIEW          |              |                 | <br>136 |

|-----|--------|--------------|----------|-------------------|--------------|-----------------|---------|

| 29  | REG    | SISTER       | BITS     | <b>BY ADDRESS</b> | )            |                 | <br>143 |

| 30  | APP    | PLICAT       | IONS     | INFORMATION       | ١            |                 | <br>242 |

| 30. | 1      | TYPICA       | L CON    | NECTIONS          |              |                 | <br>242 |

| 30. | 2      | VOLTA        | GE AN    | CURRENT RE        | FERENCE COM  | <b>IPONENTS</b> | <br>243 |

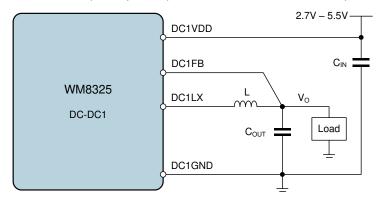

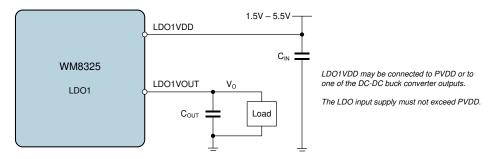

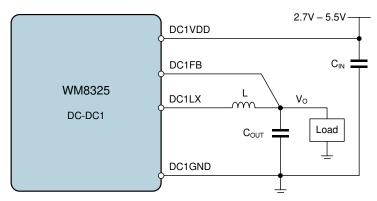

| 30. | 3      | DC-DC        | BUCK     | CONVERTER E       | XTERNAL COM  | PONENTS.        | <br>243 |

|     | 30.3.1 | 1 DC-E       | DC3 / DO | DC4 DUAL MODE     |              |                 | <br>246 |

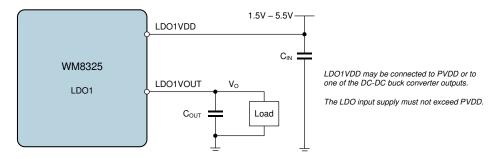

| 30. | 4      | LDO RE       | GULA     | TOR EXTERNAL      | L COMPONENTS | S               | <br>247 |

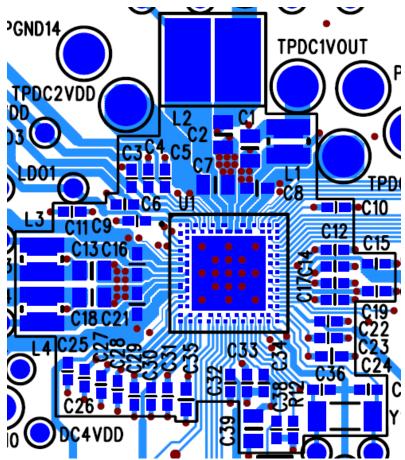

| 30. | 5      | PCB LA       | YOUT     |                   |              |                 | <br>248 |

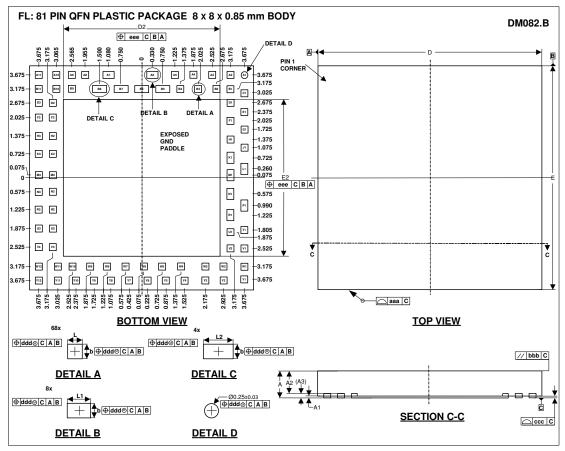

| 31  | PAC    | KAGE         | DIAG     | RAM               |              |                 | <br>249 |

| 32  | IMP    | ORTAN        | IT NO    | TICE              |              |                 | <br>250 |

| 33  | REV    | <b>ISION</b> | HISTO    | RY                |              |                 | <br>251 |

## 1 PIN CONFIGURATION

Top View - WM8325

## 2 ORDERING INFORMATION

| ORDER CODE        | ОТР          | TEMPERATURE<br>RANGE (T <sub>A</sub> ) | PACKAGE                     | MOISTURE<br>SENSITIVITY<br>LEVEL | PEAK<br>SOLDERING<br>TEMPERATURE |

|-------------------|--------------|----------------------------------------|-----------------------------|----------------------------------|----------------------------------|

| WM8325GEFL/V      | Unprogrammed | -40°C to +85°C                         | 81-lead QFN (8 x 8mm)       | MSL3                             | 260°C                            |

|                   |              |                                        | (Pb-free)                   |                                  |                                  |

| WM8325GEFL/RV     | Unprogrammed | -40°C to +85°C                         | 81-lead QFN (8 x 8mm)       | MSL3                             | 260°C                            |

|                   |              |                                        | (Pb-free, tape and reel)    |                                  |                                  |

| WM8325GEFLxxx/RV* | Custom       | -40°C to +85°C                         | 81-lead QFN (8 x 8mm)       | MSL3                             | 260°C                            |

|                   |              |                                        | (Pb-free, tape and reel) ** |                                  |                                  |

### Note:

Reel quantity = 2200

<sup>\*</sup> xxx = Unique OTP part number

$<sup>^{\</sup>star\star}$  Custom OTP minimum order quantity 22,000.

## 3 PIN DESCRIPTION

#### Notes:

- 1. Pins are sorted by functional groups.

- 2. The power domain associated with each pin is noted; VPMIC is the domain powered by LDO12 for the 'always-on' functions internal to the WM8325.

- 3. Note that an external level-shifter may be required when interfacing between different power domains.

| PIN          | NAME               | TYPE                    | POWER<br>DOMAIN | DESCRIPTION                                                                                   |  |

|--------------|--------------------|-------------------------|-----------------|-----------------------------------------------------------------------------------------------|--|

| Clocking and | Real Time Clock    |                         |                 |                                                                                               |  |

| Y12          | XTO                | Analogue Output         | VPMIC           | Crystal Drive Output                                                                          |  |

| Y11          | XTI                | Analogue Input          | VPMIC           | Crystal Drive Input or 32.768kHz CMOS Clock Input                                             |  |

| W11          | XOSCGND            | Supply                  |                 | Crystal Oscillator Ground                                                                     |  |

|              |                    |                         |                 | CMOS Clock Output                                                                             |  |

| H1           | CLKOUT             | Digital Output          | DBVDD           | Configurable Open Drain / CMOS mode. (External 4.7kΩ pull-up recommended in Open Drain mode.) |  |

| General Purp | ose Input / Output | and Auxiliary ADC       |                 |                                                                                               |  |

| D3           | GPIO1              | Digital I/O             |                 | GPIO Pin 1                                                                                    |  |

| D3           | GFIOT              | Digital 1/O             |                 | Selectable pull-up/pull-down.                                                                 |  |

| F2           | GPIO2              | Digital I/O             | DBVDDor         | GPIO Pin 2                                                                                    |  |

| 12           | GI 102             | Digital 1/O             | VPMIC           | Selectable pull-up/pull-down.                                                                 |  |

| F3           | GPIO3              | Digital I/O             |                 | GPIO Pin 3                                                                                    |  |

| 1.0          | GI 100             | Digital I/O             |                 | Selectable pull-up/pull-down.                                                                 |  |

| W4           | GPIO4              | Digital I/O             |                 | GPIO Pin 4                                                                                    |  |

| ***          | GI 104             | Digital I/O             | DBVDDor PVDD    | Selectable pull-up/pull-down.                                                                 |  |

| Y4           | GPIO5              | Digital I/O Digital I/O |                 | GPIO Pin 5                                                                                    |  |

|              | G. 100             |                         |                 | Selectable pull-up/pull-down.                                                                 |  |

| W5           | GPIO6              |                         |                 | GPIO Pin 6                                                                                    |  |

|              |                    | - 1911-11 11            |                 | Selectable pull-up/pull-down.                                                                 |  |

| H2           | GPIO7              | Digital I/O             |                 | GPIO Pin 7                                                                                    |  |

|              |                    | <b>3</b>                |                 | Selectable pull-up/pull-down.                                                                 |  |

| НЗ           | GPIO8              | Digital I/O             | DBVDDor         | GPIO Pin 8                                                                                    |  |

|              |                    | , , ,                   | VPMIC           | Selectable pull-up/pull-down.                                                                 |  |

| K3           | GPIO9              | Digital I/O             |                 | GPIO Pin 9                                                                                    |  |

|              |                    |                         |                 | Selectable pull-up/pull-down.                                                                 |  |

| Y5           | GPIO10             | Digital I/O             |                 | GPIO Pin 10 / Auxiliary ADC input                                                             |  |

|              |                    |                         |                 | Selectable GPIO pull-up/pull-down.                                                            |  |

| Y6           | GPIO11             | Digital I/O             | DBVDDor PVDD    | GPIO Pin 11 / Auxiliary ADC input                                                             |  |

|              |                    |                         | -               | Selectable GPIO pull-up/pull-down.                                                            |  |

| W6           | GPIO12             | Digital I/O             |                 | GPIO Pin 12 / Auxiliary ADC input                                                             |  |

|              |                    |                         |                 | Selectable GPIO pull-up/pull-down.                                                            |  |

| PIN          | NAME                | TYPE           | POWER<br>DOMAIN | DESCRIPTION                                                                                                                                                                                   |                                                                                                                                                                 |  |  |

|--------------|---------------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Processor In | terface and IC Cont | rol            |                 |                                                                                                                                                                                               |                                                                                                                                                                 |  |  |

| W9           | ON                  | Digital Input  | VPMIC           | ON Request Pin<br>(Internal pull-up)                                                                                                                                                          |                                                                                                                                                                 |  |  |

| B10          | RESET               | Digital I/O    | DBVDD           | System Reset Input and Open (Internal pull-up)                                                                                                                                                | Drain Output.                                                                                                                                                   |  |  |

| A11          | IRQ                 | Digital Output | DBVDD           | PMIC Interrupt Flag Output. Configurable Open Drain / CM (Internal pull-up in Open Drain                                                                                                      |                                                                                                                                                                 |  |  |

| E1           | CIFMODE             | Digital Input  | DBVDD           | Primary Control Interface Mode<br>0 = I <sup>2</sup> C Compatible Control Inte<br>1 = SPI Compatible Control Inte                                                                             | erface Mode                                                                                                                                                     |  |  |

|              |                     |                |                 | SPI Compatible Control<br>Interface Mode                                                                                                                                                      | f C Compatible<br>Control Interface<br>Mode                                                                                                                     |  |  |

| D2           | SDOUT1              | Digital Output |                 | Control Interface Serial Data<br>Out.<br>Open Drain output; external<br>4.7kΩ pull-up recommended.                                                                                            | No Function                                                                                                                                                     |  |  |

| В9           | SCLK1               | Digital Input  |                 | Control Interface Serial Clock                                                                                                                                                                | Control Interface<br>Serial Clock                                                                                                                               |  |  |

| А9           | SDA1                | Digital I/O    | DBVDD           | Control Interface Serial Data<br>In                                                                                                                                                           | Control Interface<br>Serial Data Input<br>and Open Drain<br>Output.<br>External 4.7kΩ pull-<br>up recommended.<br>(Output can extend<br>above DBVDD<br>domain.) |  |  |

| A10          | cs                  | Digital Input  |                 | Control Interface Chip Select                                                                                                                                                                 | I <sup>2</sup> C Address Select:<br>0 = 68h<br>1 = 6Ch                                                                                                          |  |  |

| Y10          | SCLK2               | Digital I/O    |                 | Control Interface Serial Clock for external InstantConfig™ EEPROM (ICE) (Internal pull-down)  Control Interface Serial Data to/from external InstantConfig™ EEPROM (ICE) (Internal pull-down) |                                                                                                                                                                 |  |  |

| W10          | SDA2                | Digital I/O    | - VPMIC         |                                                                                                                                                                                               |                                                                                                                                                                 |  |  |

| B11          | DBVDD1              | Supply         |                 | Digital Buffer Supply                                                                                                                                                                         |                                                                                                                                                                 |  |  |

| F1           | DBVDD2              | Supply         |                 | Digital Buffer Supply                                                                                                                                                                         |                                                                                                                                                                 |  |  |

| OTP Memory   |                     |                |                 |                                                                                                                                                                                               |                                                                                                                                                                 |  |  |

| Y3           | PROGVDD             | Supply         |                 | High-voltage input for OTP pro                                                                                                                                                                | gramming.                                                                                                                                                       |  |  |

| PIN        | NAME               | TYPE            | POWER<br>DOMAIN | DESCRIPTION                                                         |

|------------|--------------------|-----------------|-----------------|---------------------------------------------------------------------|

| DC-DC Conv | erters and LDO Reg | julators        |                 |                                                                     |

| B7         | DC1GND             | Supply          |                 | DC-DC1 Power Ground                                                 |

| A8         | DC1FB              | Analogue Input  | 2011/22         | DC-DC1 Feedback Pin                                                 |

| A7         | DC1LX              | Analogue I/O    | DC1VDD          | DC-DC1 Inductor Connection                                          |

| B8         | DC1VDD             | Supply          |                 | DC-DC1 Power Input (connect to PVDD system supply)                  |

| В6         | DC2GND             | Supply          |                 | DC-DC2 Power Ground                                                 |

| A5         | DC2FB              | Analogue Input  | 200/22          | DC-DC2 Feedback Pin                                                 |

| A6         | DC2LX              | Analogue I/O    | DC2VDD          | DC-DC2 Inductor Connection                                          |

| B5         | DC2VDD             | Supply          |                 | DC-DC2 Power Input (connect to PVDD system supply)                  |

| M1         | DC3GND             | Supply          |                 | DC-DC3 Power Ground                                                 |

| J1         | DC3FB              | Analogue Input  | D00/DD          | DC-DC3 Feedback Pin                                                 |

| L1         | DC3LX              | Analogue I/O    | DC3VDD          | DC-DC3 Inductor Connection                                          |

| K1         | DC3VDD             | Supply          |                 | DC-DC3 Power Input (connect to PVDD system supply)                  |

| N1         | DC4GND             | Supply          |                 | DC-DC4 Power Ground                                                 |

| T1         | DC4FB              | Analogue Input  | DO 11/DD        | DC-DC4 Feedback Pin                                                 |

| P1         | DC4LX              | Analogue I/O    | DC4VDD          | DC-DC4 Inductor Connection                                          |

| R1         | DC4VDD             | Supply          |                 | DC-DC4 Power Input (connect to PVDD system supply)                  |

| A3         | LDO1_2VDD          | Supply          |                 | LDO1 & LDO2 Power Input                                             |

| B2         | LDO1VOUT           | Analogue Output | LDO1VDD         | LDO1 Power Output                                                   |

| B3         | LDO2VOUT           | Analogue Output | LDO2VDD         | LDO2 Power Output                                                   |

| B4         | LDO3VDD            | Supply          |                 | LDO3 Power Input                                                    |

| A4         | LDO3VOUT           | Analogue Output | LDO3VDD         | LDO3 Power Output                                                   |

| W3         | LDO4VDD            | Supply          |                 | LDO4 Power Input                                                    |

| Y2         | LDO4VOUT           | Analogue Output | LDO4VDD         | LDO4 Power Output                                                   |

| Y1         | LDO5VDD            | Supply          |                 | LDO5 Power Input                                                    |

| W2         | LDO5VOUT           | Analogue Output | LDO5VDD         | LDO5 Power Output                                                   |

| W1         | LDO6VDD            | Supply          |                 | LDO6 Power Input                                                    |

| V1         | LDO6VOUT           | Analogue Output | LDO6VDD         | LDO6 Power Output                                                   |

| R3         | LDO7_8VDD          | Supply          |                 | LDO7 & LDO8 Power Input                                             |

| N2         | LDO7VOUT           | Analogue Output | LDO7VDD         | LDO7 Power Output                                                   |

| R2         | LDO8VOUT           | Analogue Output | LDO8VDD         | LDO8 Power Output                                                   |

| M2         | LDO9_10VDD         | Supply          |                 | LDO9 Power Input                                                    |

| М3         | LDO9VOUT           | Analogue Output | LDO9VDD         | LDO9 Power Output                                                   |

| N3         | LDO10VOUT          | Analogue Output | LDO10VDD        | LDO10 Power Output                                                  |

| V3         | LDO11VOUT          | Analogue Output | PVDD            | LDO11 (Alive) Power Output                                          |

| Y8         | LDO12VOUT          | Analogue I/O    | PVDD            | LDO12 (Internal VPMIC) Output; Backup battery supply input / output |

| W7         | LDO13VOUT1         | Analogue I/O    | PVDD            | LDO13 (Internal INTVDD) Output; not for general use                 |

| K2         | LDO13VOUT2         | Analogue I/O    | PVDD            | LDO13 - Connect to LDO13VOUT1 (W7)                                  |

| PIN                       | NAME                     | TYPE            | POWER<br>DOMAIN | DESCRIPTION                                  |  |  |

|---------------------------|--------------------------|-----------------|-----------------|----------------------------------------------|--|--|

| Voltage and               | Current References       |                 |                 |                                              |  |  |

| W8                        | VREFC                    | Analogue I/O    | VDMIC           | Voltage Reference capacitor connection point |  |  |

| Y9                        | IREFR                    | Analogue I/O    | VPMIC           | Current Reference resistor connection point  |  |  |

| System LED                | Drivers                  |                 |                 |                                              |  |  |

| U3                        | LED1                     | Digital Output  | DVDD            | Status LED Driver 1. Open Drain Output       |  |  |

| U2                        | LED2                     | Digital Output  | PVDD            | Status LED Driver 2. Open Drain Output       |  |  |

| System Pow                | er                       |                 |                 |                                              |  |  |

| U1                        | PVDD1                    | Supply          |                 | System VDD Supply                            |  |  |

| <b>Y</b> 7                | PVDD2                    | Supply          |                 | System VDD Supply                            |  |  |

| V4                        | PVDD3                    | Supply          |                 | System VDD Supply                            |  |  |

| EGP                       | Exposed Ground<br>Paddle | Analogue Ground |                 | Ground                                       |  |  |

| Miscellaneo               | ıs                       |                 |                 |                                              |  |  |

| A1, A2, B1,<br>C1, D1, V2 | DNC                      |                 |                 | Do Not Connect                               |  |  |

| G1, W12                   | TEST                     |                 |                 | Test function (connect to GND)               |  |  |

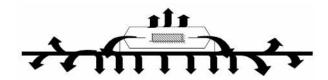

### 4 THERMAL CHARACTERISTICS

Thermal analysis must be performed in the intended application to prevent the WM8325 from exceeding maximum junction temperature. Several contributing factors affect thermal performance most notably the physical properties of the mechanical enclosure, location of the device on the PCB in relation to surrounding components and the number of PCB layers. Connecting the GND balls through thermal vias and into a large ground plane will aid heat extraction.

Three main heat transfer paths exist to surrounding air:

- Package top to air (convection and radiation).

- Package bottom to PCB (convection and radiation).

- Package leads to PCB (conduction).

(Note that radiation is not normally significant at the moderate temperatures experienced in typical applications.)

The temperature rise  $T_R$  is given by  $T_R = P_D * \Theta_{JA}$

- P<sub>D</sub> is the power dissipated by the device.

- O<sub>JA</sub> is the thermal resistance from the junction of the die to the ambient temperature and is therefore a measure of heat transfer from the die to surrounding air.

- For WM8325,  $\Theta_{JA} = 24^{\circ}\text{C/W}$

- The quoted Θ<sub>JA</sub> is based on testing to the EIA/JEDEC-51-2 test environment (ie. 1ft<sup>3</sup> box, still air, with specific PCB stack-up and tracking rules). Note that this is not guaranteed to reflect all typical end applications.

The junction temperature  $T_J$  is given by  $T_J = T_A + T_R$

- T<sub>A</sub>, is the ambient temperature.

The worst case conditions are when the WM8325 is operating in a high ambient temperature, and under conditions which cause high power dissipation, such as the DC-DC converters operating at low supply voltage, high duty cycle and high output current. Under such conditions, it is possible that the heat dissipated could cause the maximum junction temperature of the device to be exceeded. Care must be taken to avoid this situation. An example calculation of the junction temperature is given below.

- $P_D = 500$ mW (example figure)

- OJA = 24°C/W

- $T_R = P_D * \Theta_{JA} = 12^{\circ}C$

- TA = 85°C (example figure)

- $T_J = T_A + T_R = 97^{\circ}C$

The minimum and maximum operating junction temperatures for the WM8325 are quoted in Section 5. The maximum junction temperature is 125°C. Therefore, the junction temperature in the above example is within the operating limits of the WM8325.

## 5 ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Cirrus Logic tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The WM8325 has been classified as MSL3.

| CONDITION                                                  | MIN        | MAX          |  |  |  |

|------------------------------------------------------------|------------|--------------|--|--|--|

| OTP Programming Supply (PROGVDD)                           | -0.3V      | 7.0V         |  |  |  |

| System supply (PVDD1, PVDD2, PVDD3)                        | -0.3V      | 7.0V         |  |  |  |

| Input voltage for LDO regulators                           | -0.3V      | 7.0V         |  |  |  |

| Input voltage for DC-DC converters                         | -0.3V      | 7.0V         |  |  |  |

| Digital buffer supply (DBVDD1, DBVDD2)                     | -0.3V      | 4.5V         |  |  |  |

| Voltage range for digital inputs                           | -0.3V      | DBVDD + 0.3V |  |  |  |

| Operating Temperature Range, T <sub>A</sub>                | -40°C      | +85°C        |  |  |  |

| Junction Temperature, T <sub>J</sub>                       | -40°C      | +125°C       |  |  |  |

| Thermal Impedance Junction to Ambient, $\theta_{JA}$       |            | 24°C/W       |  |  |  |

| Storage temperature prior to soldering                     | 30°C max / | 60% RH max   |  |  |  |

| Storage temperature after soldering                        | -65°C      | +150°C       |  |  |  |

| Soldering temperature (10 seconds)                         |            | +260°C       |  |  |  |

| Note: These ratings assume that all ground pins are at 0V. |            |              |  |  |  |

## 6 RECOMMENDED OPERATING CONDITIONS

| PARAMETER              | SYMBOL                                                                     | MIN  | TYP | MAX  | UNITS |

|------------------------|----------------------------------------------------------------------------|------|-----|------|-------|

| System power source    | PVDD1, PVDD2, PVDD3                                                        | 2.7  |     | 5.5  | V     |

| Digital buffer supply  | DBVDD1, DBVDD2                                                             | 1.71 |     | 3.6  | V     |

| OTP Programming Supply | PROGVDD                                                                    | 6.25 | 6.5 | 6.75 | V     |

| (see note)             | LDO12VOUT                                                                  |      | 3.3 |      | V     |

| Ground                 | Exposed Ground Paddle (EGP),<br>DC1GND, DC2GND, DC3GND,<br>DC4GND, XOSCGND |      | 0   |      | V     |

#### Note:

The OTP Programming Supply PROGVDD should only be present when programming the OTP. At other times, this pin should be left unconnected. The LDO12VOUT must be overdriven by an external supply when programming the OTP. At other times, the voltage at this pin is driven by the internal circuits of the WM8325.

## 7 ELECTRICAL CHARACTERISTICS

## 7.1 DC-DC SYNCHRONOUS BUCK CONVERTERS

#### DC-DC1

Unless otherwise noted:  $V_{IN} = 3.8V$ ,  $V_{OUT} = 1.2V$ , MODE = FCCM<sup>(1)</sup>,  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C; typical values are at  $T_J = 25^{\circ}$ C

| PARAMETER                  | SYMBOL                | TEST CONDITIONS                                                                                                           | MIN  | TYP  | MAX  | UNIT |

|----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage              | V <sub>IN</sub>       |                                                                                                                           | 2.7  |      | 5.5  | V    |

| Programmable               | V <sub>OUT</sub>      | F <sub>SW</sub> = 2MHz                                                                                                    | 0.6  |      | 1.8  | V    |

| Output Voltage             |                       | F <sub>SW</sub> = 4MHz                                                                                                    | 0.6  |      | 1.4  |      |

| V <sub>OUT</sub> Step Size | V <sub>OUT_STEP</sub> |                                                                                                                           |      | 12.5 |      | mV   |

| V <sub>OUT</sub> Accuracy  | $V_{\text{OUT\_ACC}}$ | $V_{IN} = 2.7V \text{ to } 5.5V, I_{OUT} = 0\text{mA to } 1250\text{mA}$                                                  | -2.5 |      | +2.5 | %    |

| Undervoltage               | $V_{UV}$              | $0.6V \le V_{OUT} < 0.9V$                                                                                                 |      | 50   |      | mV   |

| margin                     |                       | 0.9V ≤ V <sub>OUT</sub> < 1.3V                                                                                            |      | 80   |      |      |

|                            |                       | 1.3V ≤ V <sub>OUT</sub> ≤ 1.8V                                                                                            |      | 100  |      |      |

| Overvoltage margin         | V <sub>ov</sub>       | 0.6V ≤ V <sub>OUT</sub> ≤ 1.8V                                                                                            |      | 100  |      | mV   |

| Output Current             | I <sub>OUT</sub>      | FCCM <sup>(1)</sup> and Auto (CCM/DCM with PS <sup>(2)</sup> ) Modes                                                      | 0    |      | 1250 | mA   |

|                            |                       | Hysteretic Mode                                                                                                           | 0    |      | 150  |      |

|                            |                       | LDO Mode                                                                                                                  | 0    |      | 10   |      |

| P-channel                  | I <sub>P_LIM</sub>    | DC1_FREQ = 01 or 10                                                                                                       |      | 1850 |      | mA   |

| Current Limit              |                       | DC1_FREQ = 11                                                                                                             |      | 2050 |      |      |

| Quiescent<br>Current       | lα                    | I <sub>OUT</sub> = 0mA, FCCM <sup>(1)</sup> and Auto (CCM/DCM with PS <sup>(2)</sup> ) Modes (excluding switching losses) |      | 585  |      | μΑ   |

|                            |                       | I <sub>OUT</sub> = 0mA, Hysteretic Mode                                                                                   |      | 100  |      |      |

|                            |                       | I <sub>OUT</sub> = 0mA, LDO Mode                                                                                          |      | 25   |      |      |

| Shutdown<br>Current        | I <sub>SD</sub>       | DC1_ENA = 0                                                                                                               |      | 0.01 |      | μА   |

| P-channel On Resistance    | R <sub>DSP</sub>      | $V_{IN} = V_{GS} = 3.8V, I_{DCmLX} = 100mA$                                                                               |      | 150  |      | mΩ   |

| N-channel                  | R <sub>DSN</sub>      | V V 0.0V L 100 A                                                                                                          |      | 4.40 |      | mΩ   |

| On Resistance              |                       | $V_{IN} = V_{GS} = 3.8V, I_{DCmLX} = -100mA$                                                                              |      | 140  |      |      |

| Switching                  | F <sub>SW</sub>       | DC1_FREQ = 01                                                                                                             |      | 2    |      | MHz  |

| Frequency                  |                       | DC1_FREQ = 1X                                                                                                             |      | 4    |      |      |

#### Notes:

1. Forced Continuous Conduction Mode

2. Continuous / Discontinuous Conduction with Pulse-Skipping Mode

#### DC-DC2

| PARAMETER                  | SYMBOL             | TEST CONDITION                                                                                          | IS                                          | MIN  | TYP  | MAX  | UNIT |

|----------------------------|--------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------|------|------|------|------|

| Input Voltage              | $V_{IN}$           |                                                                                                         |                                             | 2.7  |      | 5.5  | V    |

| Programmable               | $V_{OUT}$          | F <sub>SW</sub> = 2MHz                                                                                  |                                             | 0.6  |      | 1.8  | V    |

| Output Voltage             |                    | F <sub>SW</sub> = 4MHz                                                                                  |                                             | 0.6  |      | 1.4  |      |

| V <sub>OUT</sub> Step Size | $V_{OUT\_STEP}$    |                                                                                                         |                                             |      | 12.5 |      | mV   |

| V <sub>OUT</sub> Accuracy  | $V_{OUT\_ACC}$     | $V_{IN} = 2.7V$ to 5.5V, $I_{OUT} = 0$ mA to                                                            | 2500mA                                      | -2.5 |      | +2.5 | %    |

| Undervoltage               | $V_{UV}$           | $0.6V \le V_{OUT} < 0.9V$                                                                               |                                             |      | 50   |      | mV   |

| margin                     |                    | $0.9V \le V_{OUT} < 1.3V$                                                                               |                                             |      | 80   |      |      |

|                            |                    | 1.3V ≤ V <sub>OUT</sub> ≤ 1.8V                                                                          |                                             |      | 100  |      |      |

| Overvoltage margin         | V <sub>ov</sub>    | 0.6V ≤ V <sub>OUT</sub> ≤ 1.8V                                                                          | ··                                          |      | 100  |      | mV   |

| Output Current             | I <sub>OUT</sub>   | FCCM <sup>(1)</sup> and Auto (CCM/DCM                                                                   | F <sub>SW</sub> = 2MHz                      | 0    |      | 2500 | mA   |

|                            |                    | with PS <sup>(2)</sup> ) Modes                                                                          | F <sub>SW</sub> = 4MHz                      | 0    |      | 1250 |      |

|                            |                    | Hysteretic Mode                                                                                         |                                             | 0    |      | 150  |      |

|                            |                    | LDO Mode                                                                                                | 0                                           |      | 10   |      |      |

| P-channel                  | I <sub>P_LIM</sub> |                                                                                                         |                                             |      | 3650 |      | mA   |

| Current Limit              |                    |                                                                                                         |                                             |      | 3630 |      | MA   |

| Quiescent<br>Current       | ΙQ                 | I <sub>OUT</sub> = 0mA, FCCM <sup>(1)</sup> and Auto (0 PS <sup>(2)</sup> ) Modes (excluding switching) |                                             |      | 585  |      | μΑ   |

|                            |                    | I <sub>OUT</sub> = 0mA, Hysteretic Mode                                                                 |                                             |      | 100  |      |      |

|                            |                    | I <sub>OUT</sub> = 0mA, LDO Mode                                                                        |                                             |      | 25   |      |      |

| Shutdown<br>Current        | I <sub>SD</sub>    | DC2_ENA = 0                                                                                             |                                             |      | 0.01 |      | μΑ   |

| P-channel                  | R <sub>DSP</sub>   | $V_{IN} = V_{GS} = 3.8V$ , $I_{DCml, X} = 100 \text{m/s}$                                               | 1                                           |      | 115  |      | mΩ   |

| On Resistance              |                    | VIN - VGS - 0.0 V, IDCMLX - 1001117                                                                     | $I = V_{GS} = 3.8V$ , $I_{DCmLX} = 100IIIA$ |      |      |      |      |

| N-channel                  | R <sub>DSN</sub>   | $V_{IN} = V_{GS} = 3.8V$ , $I_{DCmI} = -100m$                                                           | Α                                           |      | 105  |      | mΩ   |

| On Resistance              |                    | iii de , beilles                                                                                        |                                             |      |      |      |      |

| Switching                  | F <sub>SW</sub>    | DC2_FREQ = 01                                                                                           |                                             |      | 2    |      | MHz  |

| Frequency                  |                    | DC2_FREQ = 10                                                                                           |                                             |      | 4    |      |      |

#### Notes:

- 1. Forced Continuous Conduction Mode

- 2. Continuous / Discontinuous Conduction with Pulse-Skipping Mode

#### DC-DC3 and DC-DC4

Unless otherwise noted:  $V_{IN} = 3.8V$ ,  $V_{OUT} = 1.8V$ , MODE = FCCM<sup>(1)</sup>,  $T_J = -40$ °C to +125°C; typical values are at  $T_J = 25$ °C

| PARAMETER                       | SYMBOL                    | TEST C                                                                                | ONDITIONS                                   | MIN     | TYP    | MAX    | UNIT |

|---------------------------------|---------------------------|---------------------------------------------------------------------------------------|---------------------------------------------|---------|--------|--------|------|

| Input Voltage                   | $V_{IN}$                  |                                                                                       |                                             | 2.7     |        | 5.5    | V    |

| Programmable<br>Output Voltage  | V <sub>OUT</sub>          |                                                                                       |                                             | 0.85(4) |        | 3.4    | V    |

| V <sub>OUT</sub> Step Size      | $V_{\text{OUT\_STEP}}$    |                                                                                       |                                             |         | 25     |        | mV   |

| V <sub>OUT</sub> Accuracy       | $V_{OUT\_ACC}$            | $V_{IN} = 2.7V \text{ to } 5.5V, I_{OU}$                                              | = 2.7V to 5.5V, $I_{OUT}$ = 0mA to 1000mA   |         |        | +4     | %    |

| Undervoltage margin             | V <sub>UV</sub>           | $0.85V \le V_{OUT} \le 3.4V$                                                          | 85V ≤ V <sub>OUT</sub> ≤ 3.4V               |         | 50     |        | mV   |

| Output Current I <sub>OUT</sub> | I <sub>OUT</sub>          | FCCM <sup>(1)</sup> and Auto<br>(CCM/DCM with                                         | Independent operation (DC4_SLV=0)           | 0       |        | 1000   | mA   |

|                                 | PS <sup>(2)</sup> ) Modes | Dual mode operation (DC4_SLV=1)                                                       | 0                                           |         | 800(5) |        |      |

|                                 |                           | Hysteretic Mode, DCr                                                                  | n_STNBY_LIM=01                              | 0       |        | 100(3) |      |

|                                 |                           | LDO Mode                                                                              |                                             | 0       |        | 10     |      |

| P-channel<br>Current Limit      | I <sub>P_LIM</sub>        |                                                                                       |                                             |         | 1600   |        | mA   |

| Quiescent<br>Current            | lα                        | I <sub>OUT</sub> = 0mA, FCCM <sup>(1)</sup> a<br>PS <sup>(2)</sup> ) Modes (excluding | and Auto (CCM/DCM with ng switching losses) |         | 330    |        | μА   |

|                                 |                           | I <sub>OUT</sub> = 0mA, Hysteretic                                                    | Mode                                        |         | 110    |        |      |

|                                 |                           | I <sub>OUT</sub> = 0mA, LDO Mod                                                       | е                                           |         | 20     |        |      |

| Shutdown<br>Current             | I <sub>SD</sub>           | DC <i>m</i> _ENA = 0                                                                  |                                             |         | 0.01   |        | μА   |

| P-channel On Resistance         | R <sub>DSP</sub>          | $V_{\text{IN}} = V_{\text{GS}} = 3.8V, \ I_{\text{DCmI}}$                             | <sub>LX</sub> = 100mA                       |         | 165    |        | mΩ   |

| N-channel<br>On Resistance      | R <sub>DSN</sub>          | $V_{IN} = V_{GS} = 3.8V$ , $I_{DCml}$                                                 | <sub>LX</sub> = -100mA                      |         | 155    |        | mΩ   |

| Switching<br>Frequency          | F <sub>SW</sub>           |                                                                                       |                                             |         | 2      |        | MHz  |

#### Notes:

- 1. Forced Continuous Conduction Mode

- 2. Continuous / Discontinuous Conduction with Pulse-Skipping Mode

- 3. The maximum output current in Hysteretic mode can be adjusted using the DCm\_STNBY\_LIM registers

- 4. In FCCM mode, the minimum  $V_{\text{OUT}}$  is 1.2V

- 5. In Dual mode operation, the ratings are 'per converter'. The combined maximum output current is 1600mA

## 7.2 LDO REGULATORS

#### LDO1

Unless otherwise noted:  $V_{IN}$  = 3.8V,  $V_{OUT}$  = 1.8V,  $T_J$  = -40°C to +125°C; Typical values are at  $T_J$  = +25°C

| PARAMETER                      | SYMBOL                             | TEST CONDITIONS                                                                                  | MIN                | TYP        | MAX     | UNIT |

|--------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|--------------------|------------|---------|------|

| Input Voltage                  | V <sub>IN</sub>                    |                                                                                                  | 1.5                |            | 5.5     | V    |

| Programmable<br>Output Voltage | V <sub>OUT</sub>                   |                                                                                                  | 0.9                |            | 3.3     | V    |

| $V_{\text{OUT}}$ Step Size     | $V_{\text{OUT\_STEP}}$             | V <sub>OUT</sub> = 0.9V to 1.6V                                                                  |                    | 50         |         | mV   |

|                                |                                    | V <sub>OUT</sub> = 1.7V to 3.3V                                                                  |                    | 100        |         |      |

| Output Current                 | I <sub>OUT</sub>                   | Normal mode                                                                                      | 0                  |            | 300     | mA   |

|                                |                                    | Low power mode, LDOn_LP_MODE=0                                                                   | 0                  |            | 50      |      |

|                                |                                    | Low power mode, LDOn_LP_MODE=1                                                                   | 0                  |            | 20      |      |

| V <sub>OUT</sub> Accuracy      | $V_{\text{OUT\_ACC}}$              | $I_{LOAD} = 1 mA$                                                                                | -3                 |            | +3      | %    |

| Line Regulation                | V <sub>OUT LINE</sub>              | $V_{IN} = (V_{OUT} + 0.5)$ to 5.5V, $I_{LOAD} = 150$ mA<br>Note that $V_{IN}$ must be $>= 1.5$ V |                    | 0.1        |         | %/V  |

| Load Regulation                | V <sub>OUT LOAD</sub>              | I <sub>LOAD</sub> =1mA to 300mA                                                                  |                    | 0.011      |         | %/mA |

| Dropout Voltage                | V <sub>IN</sub> - V <sub>OUT</sub> | $I_{LOAD} = 150 \text{mA}, V_{OUT} > 2.7 \text{V}$                                               |                    | 250        |         | mV   |

|                                |                                    | I <sub>LOAD</sub> =150mA, V <sub>OUT</sub> 1.8V to 2.7V                                          |                    | 300        |         |      |

|                                |                                    | $I_{LOAD} = 150 \text{mA}, V_{OUT} < 1.8 \text{V}$                                               |                    | 500        |         |      |

| Undervoltage<br>level          | V <sub>OUT</sub>                   | V <sub>OUT</sub> Falling                                                                         |                    | 88         |         | %    |

| Quiescent                      | ΙQ                                 | Normal mode, no load                                                                             |                    | 30         |         | μΑ   |

| Current                        |                                    | Low power mode, LDOn_LP_MODE=0, no load                                                          |                    | 10         |         |      |

|                                |                                    | Low power mode, LDOn_LP_MODE=1, no load                                                          |                    | 5          |         |      |

|                                |                                    | $I_{LOAD} = 1 \text{mA to } 300 \text{mA}$                                                       | I <sub>Q</sub> (no | load) + 1% | of load |      |

| Power Supply                   | PSRR                               | I <sub>LOAD</sub> = 150mA, <= 1kHz                                                               |                    | 53         |         | dB   |

| Rejection Ratio                |                                    | I <sub>LOAD</sub> = 150mA, 10kHz                                                                 |                    | 53         |         |      |

|                                |                                    | I <sub>LOAD</sub> = 150mA, 100kHz                                                                |                    | 32         |         |      |

| On Resistance                  | R <sub>DSON</sub>                  | $V_{IN} = 1.5V$ , $I_{LOAD} = 100mA$                                                             |                    | 1.5        |         | Ω    |

| (Switch mode)                  |                                    | $V_{IN} = 1.8V, I_{LOAD} = 100mA$                                                                |                    | 1.2        |         |      |

|                                |                                    | $V_{IN} = 2.5V, I_{LOAD} = 100mA$                                                                |                    | 0.85       |         |      |

|                                |                                    | $V_{IN} = 3.3V, I_{LOAD} = 100mA$                                                                |                    | 0.7        |         |      |

| Current Limit (Switch mode)    | I <sub>CL</sub>                    | $V_{OUT} = 0V$                                                                                   |                    | 600        |         | mA   |

| Start-up time                  | t <sub>start_up</sub>              | No load, Output cap 2.2 μF, 90% of V <sub>OUT</sub>                                              |                    | 10         |         | μS   |

| Shutdown time                  | t <sub>shut_down</sub>             | No load, Output cap 2.2 μF, 10% of V <sub>OUT</sub>                                              |                    |            | 10      | ms   |

#### LDO2, LDO3

Unless otherwise noted:  $V_{IN} = 3.8V$ ,  $V_{OUT} = 1.8V$ ,  $T_{J} = -40$ °C to +125°C; Typical values are at  $T_{J} = +25$ °C

| PARAMETER                      | SYMBOL                | TEST CONDITIONS                                         | MIN | TYP   | MAX | UNIT         |

|--------------------------------|-----------------------|---------------------------------------------------------|-----|-------|-----|--------------|

| Input Voltage                  | $V_{IN}$              |                                                         | 1.5 |       | 5.5 | V            |

| Programmable<br>Output Voltage | V <sub>OUT</sub>      |                                                         | 0.9 |       | 3.3 | V            |

| V <sub>OUT</sub> Step Size     | $V_{OUT\_STEP}$       | $V_{OUT} = 0.9V \text{ to } 1.6V$                       |     | 50    |     | mV           |

|                                |                       | V <sub>OUT</sub> = 1.7V to 3.3V                         |     | 100   |     |              |

| Output Current                 | I <sub>OUT</sub>      | Normal mode                                             | 0   |       | 200 | mA           |

|                                |                       | Low power mode, LDOn_LP_MODE=0                          | 0   |       | 50  |              |

|                                |                       | Low power mode, LDOn_LP_MODE=1                          | 0   |       | 20  |              |

| V <sub>OUT</sub> Accuracy      | V <sub>OUT_ACC</sub>  | $I_{LOAD} = 1 \text{mA}$                                | -3  |       | +3  | %            |

| Line Regulation                | V <sub>OUT LINE</sub> | $V_{IN} = (V_{OUT} + 0.5)$ to 5.5V, $I_{LOAD} = 100$ mA |     | 0.1   |     | %/V          |

|                                |                       | Note that V <sub>IN</sub> must be >= 1.5V               |     | 0.1   |     | 70/ <b>V</b> |

| Load Regulation                | V <sub>OUT LOAD</sub> | I <sub>LOAD</sub> =1mA to 200mA                         |     | 0.011 |     | %/mA         |

| PARAMETER                      | SYMBOL                             | TEST CONDITIONS                                         | MIN                                   | TYP  | MAX | UNIT |