### **General Description**

The MAX541/MAX542 are serial-input, voltage-output, 16-bit digital-to-analog converters (DACs) that operate from a single +5V supply. They provide 16-bit performance (±1LSB INL and DNL) over temperature without any adjustments. The DAC output is unbuffered, resulting in a low supply current of 0.3mA and a low offset error of 1LSB.

The DAC output range is 0V to VREF. For bipolar operation, matched scaling resistors are provided in the MAX542 for use with an external precision op amp (such as the MAX400), generating a ±VREF output swing. The MAX542 also includes Kelvin-sense connections for the reference and analog ground pins to reduce layout sensitivity.

A 16-bit serial word is used to load data into the DAC latch. The 10MHz, 3-wire serial interface is compatible with SPI™/QSPI™/MICROWIRE™, and it also interfaces directly with optocouplers for applications requiring isolation. A power-on reset circuit clears the DAC output to 0V (unipolar mode) when power is initially applied.

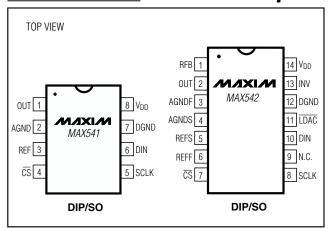

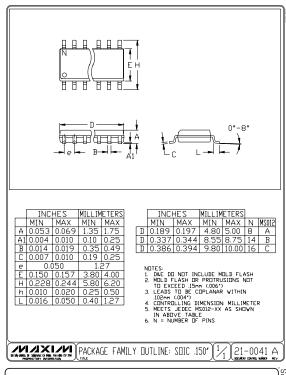

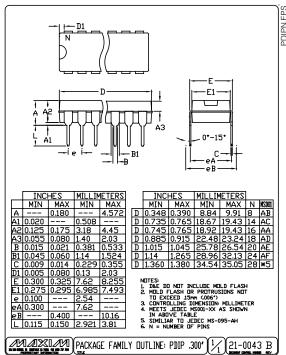

The MAX541 is available in 8-pin plastic DIP and SO packages. The MAX542 is available in 14-pin plastic DIP and SO packages.

### **Applications**

High-Resolution Offset and Gain Adjustment Industrial Process Control Automated Test Equipment **Data-Acquisition Systems**

**Features**

- ♦ Full 16-Bit Performance Without Adjustments

- ♦ +5V Single-Supply Operation

- ♦ Low Power: 1.5mW

- ♦ 1µs Settling Time

- ♦ Unbuffered Voltage Output Directly Drives 60kΩ Loads

- ♦ SPI/QSPI/MICROWIRE-Compatible Serial Interface

- ♦ Power-On Reset Circuit Clears DAC Output to 0V (unipolar mode)

- ♦ Schmitt Trigger Inputs for Direct Optocoupler Interface

### **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE   | INL<br>(LSB) |

|------------|--------------|---------------|--------------|

| MAX541ACPA | 0°C to +70°C | 8 Plastic DIP | ±1           |

| MAX541BCPA | 0°C to +70°C | 8 Plastic DIP | ±2           |

| MAX541CCPA | 0°C to +70°C | 8 Plastic DIP | ±4           |

| MAX541ACSA | 0°C to +70°C | 8 SO          | ±1           |

| MAX541BCSA | 0°C to +70°C | 8 SO          | ±2           |

| MAX541CCSA | 0°C to +70°C | 8 SO          | ±4           |

Ordering Information continued at end of data sheet.

## **General Description**

SPI and QSPI are trademarks of Motorola. Inc. MICROWIRE is a trademark of National Semiconductor Corp.

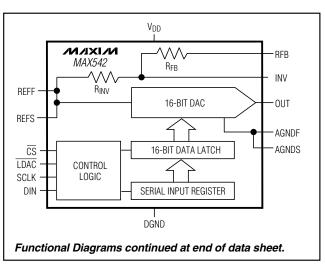

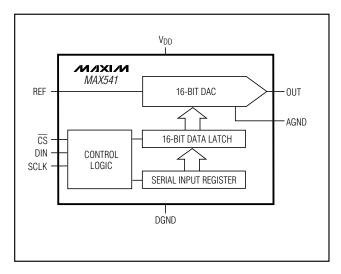

### **Functional Diagrams**

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND                            | 0.3V to +6V               |

|----------------------------------------------------|---------------------------|

| CS, SCLK, DIN, LDAC to DGND                        | 0.3V to +6V               |

| REF, REFF, REFS to AGND                            | 0.3V to $(V_{DD} + 0.3V)$ |

| AGND, AGNDF, AGNDS to DGND                         | 0.3V to +0.3V             |

| OUT, INV to AGND, DGND                             | 0.3V to V <sub>DD</sub>   |

| RFB to AGND, DGND                                  | 6V to +6V                 |

| Maximum Current into Any Pin                       | 50mA                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70 | 0°C)                      |

| 8-Pin Plastic DIP (derate 9.09mW/°C at             | oove +70°C)727mW          |

| 8-Pin SO (derate 5.88mW/°C above +7                | 0°C)471mW                 |

|                                                    |                           |

| 14-Pin Plastic DIP (derate 10.00mW/°C above +70°C)80<br>14-Pin SO (derate 8.33mW/°C above +70°C)60<br>14-Pin Ceramic SB (derate 10.00mW/°C above +70°C80 | 67mW   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Operating Temperature Ranges                                                                                                                             | 301111 |

| MAX541 _C_ A/MAX542_C_D0°C to -                                                                                                                          | +70°C  |

| MAX541_E_ A/MAX542_E_D40°C to -                                                                                                                          |        |

| MAX542CMJD55°C to +                                                                                                                                      | 125°C  |

| Storage Temperature Range65°C to +                                                                                                                       |        |

| Lead Temperature (soldering, 10s)+                                                                                                                       | 300°C  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5V \pm 5\%, V_{REF} = +2.5V, AGND = DGND = 0, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$

| PARAMETER                  | SYMBOL           | CONI                                             | DITIONS                           | MIN | TYP   | MAX    | UNITS  |  |

|----------------------------|------------------|--------------------------------------------------|-----------------------------------|-----|-------|--------|--------|--|

| STATIC PERFORMANCE—AN      | NALOG SECT       | TION (R <sub>L</sub> = ∞)                        |                                   |     |       |        |        |  |

| Resolution                 | N                |                                                  |                                   | 16  |       |        | Bits   |  |

|                            |                  |                                                  | MAX54_A                           |     | ±0.5  | ±1.0   |        |  |

| Integral Nonlinearity      | INL              | $V_{DD} = 5V$                                    | MAX54_B                           |     | ±0.5  | ±2.0   | LSB    |  |

|                            |                  |                                                  | MAX54_C                           |     | ±0.5  | ±4.0   |        |  |

| Differential Nonlinearity  | DNL              | Guaranteed monotoni                              | ic                                |     | ±0.5  | ±1.0   | LSB    |  |

| Zero-Code Offset Error     | ZSE              | T <sub>A</sub> = +25°C                           |                                   |     |       | ±1     | LSB    |  |

| Zero-Code Offset Error     | ZSE              | $T_A = T_{MIN}$ to $T_{MAX}$                     |                                   |     |       | ±2     | LOD    |  |

| Zero-Code Tempco           | ZS <sub>TC</sub> | $T_A = T_{MIN}$ to $T_{MAX}$                     |                                   |     | ±0.05 |        | ppm/°C |  |

| Cain Error (Noto 1)        |                  | T <sub>A</sub> = +25°C                           |                                   |     |       | ±5     | LSB    |  |

| Gain Error (Note 1)        |                  | TA = TMIN to TMAX                                |                                   |     |       | ±10    | LSB    |  |

| Gain-Error Tempco          |                  |                                                  |                                   |     | ±0.1  |        | ppm/°C |  |

| DAC Output Resistance      | Rout             | (Note 2)                                         | (Note 2)                          |     | 6.25  |        | kΩ     |  |

| Bipolar Resistor Matching  |                  | MAX542                                           | R <sub>FB</sub> /R <sub>INV</sub> |     | 1.0   |        |        |  |

| bipolar nesistor Matching  |                  | IVIAA042                                         | Ratio error                       |     |       | ±0.015 | %      |  |

| Dipolar Zaro Offact Error  |                  | MAX542                                           | T <sub>A</sub> = +25°C            |     |       | ±10    | LCD    |  |

| Bipolar Zero Offset Error  |                  | $T_{A} = T_{MIN} \text{ to } T_{MAX}$            |                                   |     |       | ±20    | - LSB  |  |

| Bipolar Zero Tempco        | BZSTC            | MAX542                                           |                                   |     | ±0.5  |        | ppm/°C |  |

| Power-Supply Rejection     | PSR              | $4.75V \le V_{DD} \le 5.25V$                     |                                   |     |       | ±1.0   | LSB    |  |

| REFERENCE INPUT            |                  |                                                  |                                   | •   |       |        | •      |  |

| Reference Input Range      | V <sub>REF</sub> | (Note 3)                                         | (Note 3)                          |     |       | 3.0    | V      |  |

| Reference Input Resistance | Doce             | Unipolar mode                                    | Unipolar mode                     |     |       |        | 1.0    |  |

| (Note 4)                   |                  | MAX542, bipolar mod                              | le                                | 9.0 |       |        | kΩ     |  |

| DYNAMIC PERFORMANCE—       | ANALOG SE        | CTION (R <sub>L</sub> = ∞, unipola               | ar mode)                          | •   |       |        | ,      |  |

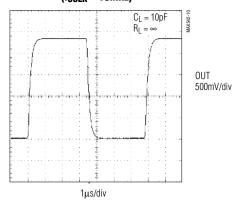

| Voltage-Output Slew Rate   | SR               | C <sub>L</sub> = 10pF (Note 5)                   |                                   |     | 25    |        | V/µs   |  |

| Output Settling Time       |                  | to $\pm \frac{1}{2}$ LSB of FS, C <sub>L</sub> = | : 10pF                            |     | 1     |        | μs     |  |

|                            |                  | ·                                                |                                   | -   |       |        |        |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VDD = +5V ±5%, VREF = +2.5V, AGND = DGND = 0, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                   | SYMBOL          | CONDITIONS                                                                                            | MIN  | TYP  | MAX  | UNITS |  |

|-----------------------------|-----------------|-------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| DAC Glitch Impulse          |                 | Major-carry transition                                                                                |      | 10   |      | nVs   |  |

| Digital Feedthrough         |                 | Code = 0000 hex; $\overline{CS}$ = $V_{DD}$ ; $\overline{LDAC}$ = 0; SCLK, DIN = 0 to $V_{DD}$ levels |      | 10   |      | nVs   |  |

| DYNAMIC PERFORMANCE—R       | EFERENCE        | SECTION                                                                                               | '    |      |      |       |  |

| Reference -3dB Bandwidth    | BW              | Code = FFFF hex                                                                                       |      | 1    |      | MHz   |  |

| Reference Feedthrough       |                 | Code = 0000 hex, VREF = 1Vp-p at 100kHz                                                               |      | 1    |      | mVp-p |  |

| Signal-to-Noise Ratio       | SNR             |                                                                                                       |      | 92   |      | dB    |  |

| Reference Input Capacitance | CIN             | Code = 0000 hex                                                                                       |      | 75   |      | pF    |  |

|                             | CIN             | Code = FFFF hex                                                                                       |      | 120  |      | Pi    |  |

| STATIC PERFORMANCE—DIG      | ITAL INPUT      | S                                                                                                     |      |      |      |       |  |

| Input High Voltage          | VIH             |                                                                                                       | 2.4  |      |      | V     |  |

| Input Low Voltage           | VIL             |                                                                                                       |      |      | 0.8  | V     |  |

| Input Current               | I <sub>IN</sub> | V <sub>IN</sub> = 0                                                                                   |      |      | ±1   | μΑ    |  |

| Input Capacitance           | CIN             | (Note 6)                                                                                              |      |      | 10   | рF    |  |

| Hysteresis Voltage          | VH              |                                                                                                       |      | 0.40 |      | V     |  |

| POWER SUPPLY                |                 |                                                                                                       |      |      |      |       |  |

| Positive Supply Range       | V <sub>DD</sub> |                                                                                                       | 4.75 |      | 5.25 | V     |  |

| Positive Supply Current     | I <sub>DD</sub> |                                                                                                       |      | 0.3  | 1.1  | mA    |  |

| Power Dissipation           | PD              |                                                                                                       |      | 1.5  |      | mW    |  |

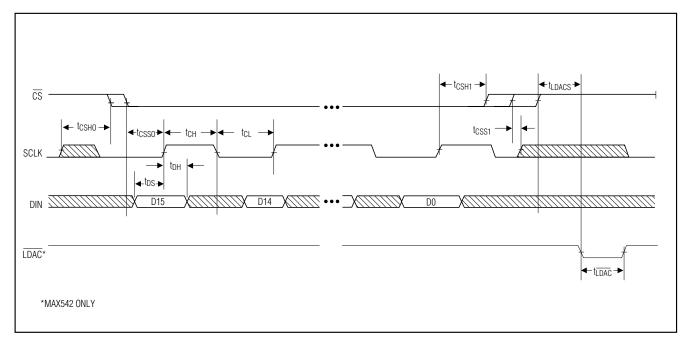

### **TIMING CHARACTERISTICS**

(VDD = +5V ±5%, VREF = +2.5V, AGND = DGND = 0, CMOS inputs, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                                                  | SYMBOL          | CONDITIONS      | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------|-----------------|-----------------|-----|-----|-----|-------|

| SCLK Frequency                                             | fCLK            |                 |     |     | 10  | MHz   |

| SCLK Pulse Width High                                      | tch             |                 | 45  |     |     | ns    |

| SCLK Pulse Width Low                                       | t <sub>CL</sub> |                 | 45  |     |     | ns    |

| CS Low to SCLK High Setup                                  | tcsso           |                 | 45  |     |     | ns    |

| CS High to SCLK High Setup                                 | tcss1           |                 | 45  |     |     | ns    |

| SCLK High to CS Low Hold                                   | tcsH0           | (Note 6)        | 30  |     |     | ns    |

| SCLK High to CS High Hold                                  | tcsH1           |                 | 45  |     |     | ns    |

| DIN to SCLK High Setup                                     | tDS             |                 | 40  |     |     | ns    |

| DIN to SCLK High Hold                                      | tDH             |                 | 0   |     |     | ns    |

| LDAC Pulse Width                                           | tLDAC           | MAX542          | 50  |     |     | ns    |

| CS High to LDAC Low Setup                                  | tLDACS          | MAX542 (Note 6) | 50  |     |     | ns    |

| V <sub>DD</sub> High to <del>CS</del> Low (power-up delay) |                 |                 |     | 20  |     | μs    |

- **Note 1:** Gain Error tested at  $V_{REF} = 2.0V$ , 2.5V, and 3.0V.

- **Note 2:** Rout tolerance is typically ±20%.

- Note 3: Min/max range guaranteed by gain-error test. Operation outside min/max limits will result in degraded performance.

- Note 4: Reference input resistance is code dependent, minimum at 8555 hex.

- Note 5: Slew-rate value is measured from 0% to 63%.

- Note 6: Guaranteed by design. Not production tested.

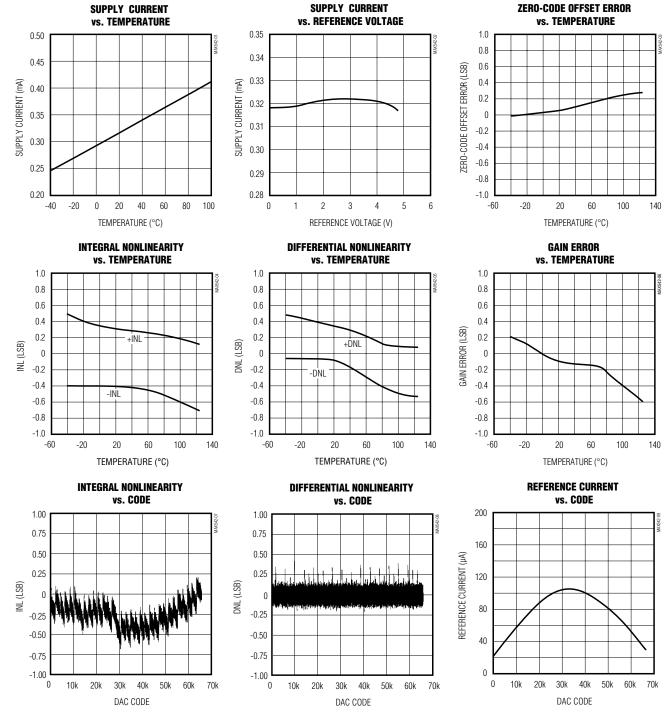

### **Typical Operating Characteristics**

$(V_{DD} = 5V, V_{REF} = +2.5V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +5V, V_{REF} = +2.5V, T_A = +25^{\circ}C, unless otherwise noted.)$

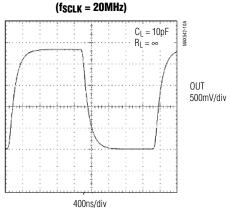

## FULL-SCALE STEP RESPONSE (fSCLK = 10MHz)

## FULL-SCALE STEP RESPONSE (feer v = 20MHz)

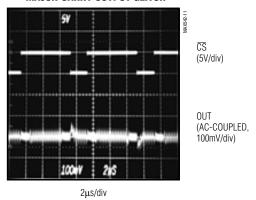

#### **MAJOR-CARRY OUTPUT GLITCH**

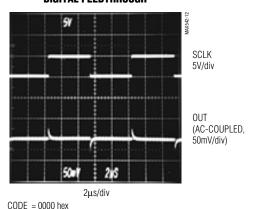

#### **DIGITAL FEEDTHROUGH**

## **Pin Descriptions**

#### **MAX541**

| PIN | NAME            | FUNCTION                                                      |  |

|-----|-----------------|---------------------------------------------------------------|--|

| 1   | OUT             | DAC Output Voltage                                            |  |

| 2   | AGND            | Analog Ground                                                 |  |

| 3   | REF             | Voltage Reference Input. Connect to external +2.5V reference. |  |

| 4   | CS              | Chip-Select Input                                             |  |

| 5   | SCLK            | Serial Clock Input. Duty cycle must be between 40% and 60%.   |  |

| 6   | DIN             | Serial Data Input                                             |  |

| 7   | DGND            | Digital Ground                                                |  |

| 8   | V <sub>DD</sub> | +5V Supply Voltage                                            |  |

## Pin Descriptions (continued)

### **MAX542**

| PIN | NAME            | FUNCTION                                                                                              |  |

|-----|-----------------|-------------------------------------------------------------------------------------------------------|--|

| 1   | RFB             | Feedback Resistor. Connect to external op amp's output in bipolar mode.                               |  |

| 2   | OUT             | DAC Output Voltage                                                                                    |  |

| 3   | AGNDF           | Analog Ground (force)                                                                                 |  |

| 4   | AGNDS           | Analog Ground (sense)                                                                                 |  |

| 5   | REFS            | Voltage Reference Input (sense). Connect REFS to external +2.5V reference.                            |  |

| 6   | REFF            | Voltage Reference Input (force). Connect REFF to external +2.5V reference.                            |  |

| 7   | CS              | Chip-Select Input                                                                                     |  |

| 8   | SCLK            | Serial Clock Input. Duty cycle must be between 40% and 60%.                                           |  |

| 9   | N.C.            | No Connection. Not internally connected.                                                              |  |

| 10  | DIN             | Serial Data Input                                                                                     |  |

| 11  | LDAC            | LDAC Input. A falling edge updates the internal DAC latch.                                            |  |

| 12  | DGND            | Digital Ground                                                                                        |  |

| 13  | INV             | Junction of internal scaling resistors. Connect to external op amp's inverting input in bipolar mode. |  |

| 14  | V <sub>DD</sub> | +5V Supply Voltage                                                                                    |  |

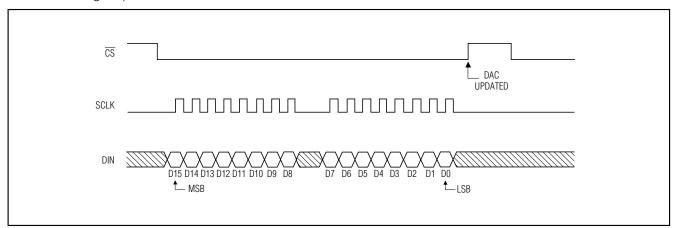

Figure 1. Timing Diagram

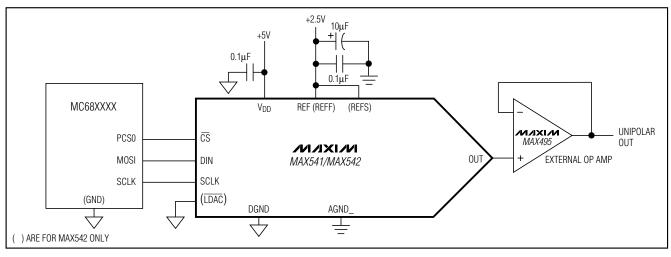

Figure 2a. Typical Operating Circuit—Unipolar Output

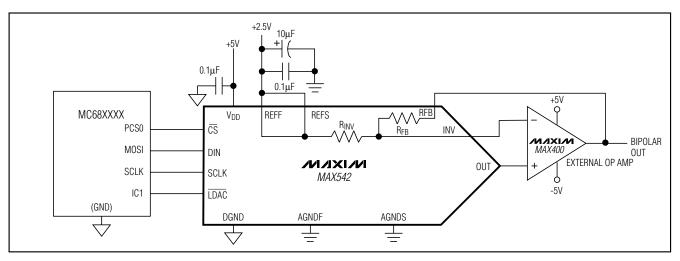

Figure 2b. Typical Operating Circuit—Bipolar Output

### **Detailed Description**

The MAX541/MAX542 voltage-output, 16-bit digital-to-analog converters (DACs) offer full 16-bit performance with less than 1LSB integral linearity error and less than 1LSB differential linearity error, thus ensuring monotonic performance. Serial data transfer minimizes the number of package pins required.

The MAX541/MAX542 are composed of two matched DAC sections, with a 12-bit inverted R-2R DAC forming the 12 LSBs and the 4 MSBs derived from 15 identically matched resistors. This architecture allows the lowest glitch energy to be transferred to the DAC output on

major-carry transitions. It also lowers the DAC output impedance by a factor of eight compared to a standard R-2R ladder, allowing unbuffered operation in medium-load applications.

The MAX542 provides matched bipolar offset resistors, which connect to an external op amp for bipolar output swings (Figure 2b). For optimum performance, the MAX542 also provides a set of Kelvin connections to the voltage-reference and analog-ground inputs.

#### **Digital Interface**

The MAX541/MAX542's digital interface is a standard 3-wire connection compatible with SPI/QSPI/MICROWIRE interfaces. The chip-select input  $\overline{(CS)}$  frames the serial data loading at the data-input pin (DIN). Immediately following  $\overline{CS}$ 's high-to-low transition, the data is shifted synchronously and latched into the input register on the rising edge of the serial clock input (SCLK). After 16 data bits have been loaded into the serial input register, it transfers its contents to the DAC latch on  $\overline{CS}$ 's low-to-high transition (Figure 3a). Note that if  $\overline{CS}$  is not kept low during the entire 16 SCLK cycles, data will be corrupted. In this case, reload the DAC latch with a new 16-bit word.

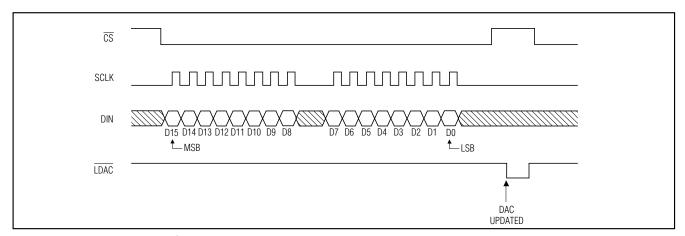

Alternatively, for the MAX542, LDAC allows the DAC latch to update asynchronously by pulling LDAC low after CS goes high (Figure 3b). Hold LDAC high during the data-loading sequence.

#### **External Reference**

The MAX541/MAX542 operate with external voltage references from 2V to 3V. The reference voltage determines the DAC's full-scale output voltage. Kelvin connections are provided with the MAX542 for optimum performance.

#### **Power-On Reset**

The MAX541/MAX542 have a power-on reset circuit to set the DAC's output to 0V in unipolar mode when V<sub>DD</sub> is first applied. This ensures that unwanted DAC output voltages will not occur immediately following a system power-up, such as after a loss of power. In bipolar mode, the DAC output is set to -V<sub>REF</sub>.

Figure 3a. MAX541/MAX542 3-Wire Interface Timing Diagram (LDAC = DGND for MAX542)

Figure 3b. MAX542 4-Wire Interface Timing Diagram

### **Applications Information**

#### **Reference and Analog Ground Inputs**

The MAX541/MAX542 operate with external voltage references from 2V to 3V, and maintain 16-bit performance if certain guidelines are followed when selecting and applying the reference. Ideally, the reference's temperature coefficient should be less than 0.4ppm/°C to maintain 16-bit accuracy to within 1LSB over the 0°C to +70°C commercial temperature range. Since this converter is designed as an inverted R-2R voltage-mode DAC, the input resistance seen by the voltage reference is code-dependent. The worst-case inputresistance variation is from 11.5k $\Omega$  (at code 8555 hex) to  $200k\Omega$  (at code 0000 hex). The maximum change in load current for a 2.5V reference is  $2.5V / 11.5k\Omega = 217\mu A$ ; therefore, the required load regulation is 7ppm/mA for a maximum error of 0.1LSB. This implies a reference output impedance of less than  $18m\Omega$ . In addition, the impedance of the signal path from the voltage reference to the reference input must be kept low because it contributes directly to the load-regulation

The requirement for a low-impedance voltage reference is met with capacitor bypassing at the reference inputs and ground. A 0.1µF ceramic capacitor with short leads between REFF and AGNDF (MAX542), or REF and AGND (MAX541), provides high-frequency bypassing. A surface-mount ceramic chip capacitor is preferred because it has the lowest inductance. An additional 10µF between REFF and AGNDF (MAX542), or REF and AGND (MAX541), provides low-frequency bypassing. A low-ESR tantalum, film, or organic semiconductor capacitor works well. Leaded capacitors are acceptable because impedance is not as critical at lower frequencies. The circuit can benefit from even larger bypassing capacitors, depending on the stability of the external reference with capacitive loading. If separate force and sense lines are not used, tie the appropriate force and sense pins together close to the package.

AGND must also be low impedance, as load-regulation errors will be introduced by excessive AGND resistance. As in all high-resolution, high-accuracy applications, separate analog and digital ground planes yield the best results. Tie DGND to AGND at the AGND pin to form the "star" ground for the DAC system. Always refer remote DAC loads to this system ground for the best possible performance.

#### **Unbuffered Operation**

Unbuffered operation reduces power consumption as well as offset error contributed by the external output buffer. The R-2R DAC output is available directly at OUT, allowing 16-bit performance from +VREF to AGND without degradation at zero scale. The DAC's output impedance is also low enough to drive medium loads (RL > 60k $\Omega$ ) without degradation of INL or DNL; only the gain error is increased by externally loading the DAC output.

#### **External Output Buffer Amplifier**

The requirements on the external output buffer amplifier change whether the DAC is used in the unipolar or bipolar mode of operation. In unipolar mode, the output amplifier is used in a voltage-follower connection. In bipolar mode (MAX542 only), the amplifier operates with the internal scaling resistors (Figure 2b). In each mode, the DAC's output resistance is constant and is independent of input code; however, the output amplifier's input impedance should still be as high as possible to minimize gain errors. The DAC's output capacitance is also independent of input code, thus simplifying stability requirements on the external amplifier.

In bipolar mode, a precision amplifier operating with dual power supplies (such as the MAX400) provides the ±VREF output range. In single-supply applications, precision amplifiers with input common-mode ranges including AGND are available; however, their output swings do not normally include the negative rail (AGND) without significant degradation of performance. A single-supply op amp, such as the MAX495, is suitable if the application does not use codes near zero.

Since the LSBs for a 16-bit DAC are extremely small (38.15µV for VREF = 2.5V), pay close attention to the external amplifier's input specification. The input offset voltage can degrade the zero-scale error and might require an output offset trim to maintain full accuracy if the offset voltage is greater than 1/2LSB. Similarly, the input bias current multiplied by the DAC output resistance (typically 6.25k $\Omega$ ) contributes to the zero-scale error. Temperature effects also must be taken into consideration. Over the 0°C to +70°C commercial temperature range, the offset voltage temperature coefficient (referenced to +25°C) must be less than 0.42µV/°C to add less than 1/2LSB of zero-scale error. The external amplifier's input resistance forms a resistive divider with the DAC output resistance, which results in a gain error.

To contribute less than 1/2LSB of gain error, the input resistance typically must be greater than:

$$6.25k\Omega \div \frac{1}{2} \left[ \frac{1}{2^{16}} \right] = 819M\Omega$$

The settling time is affected by the buffer input capacitance, the DAC's output capacitance, and PC board capacitance. The typical DAC output voltage settling time is 1µs for a full-scale step. Settling time can be significantly less for smaller step changes. Assuming a single time-constant exponential settling response, a full-scale step takes 12 time constants to settle to within 1/2LSB of the final output voltage. The time constant is equal to the DAC output resistance multiplied by the total output capacitance. The DAC output capacitance is typically 10pF. Any additional output capacitance will increase the settling time.

The external buffer amplifier's gain-bandwidth product is important because it increases the settling time by adding another time constant to the output response. The effective time constant of two cascaded systems, each with a single time-constant response, is approximately the root square sum of the two time constants. The DAC output's time constant is 1µs / 12 = 83ns, ignoring the effect of additional capacitance. If the time constant of an external amplifier with 1MHz bandwidth is 1 / 2 $\pi$  (1MHz) = 159ns, then the effective time constant of the combined system is:

$$\sqrt{\left[\left(83\text{ns}\right)^2 + \left(159\text{ns}\right)^2\right]} = 180\text{ns}$$

This suggests that the settling time to within 1/2LSB of the final output voltage, including the external buffer amplifier, will be approximately  $12 \cdot 180$ ns = 2.15µs.

### Digital Inputs and Interface Logic

The digital interface for the 16-bit DAC is based on a 3-wire standard that is compatible with SPI, QSPI, and MICROWIRE interfaces. The three digital inputs ( $\overline{\text{CS}}$ , DIN, and  $\underline{\text{SCLK}}$ ) load the digital input data serially into the DAC.  $\overline{\text{LDAC}}$  (MAX542) updates the DAC output asynchronously.

All of the digital inputs include Schmitt-trigger buffers to accept slow-transition interfaces. This means that optocouplers can interface directly to the MAX541/MAX542 without additional external logic. The digital inputs are compatible with TTL/CMOS-logic levels.

### **Unipolar Configuration**

Figure 2a shows the MAX541/MAX542 configured for unipolar operation with an external op amp. The op amp is set for unity gain, and Table 1 lists the codes for this circuit

#### **Bipolar Configuration**

Figure 2b shows the MAX542 configured for bipolar operation with an external op amp. The op amp is set for unity gain with an offset of -1/2VREF. Table 2 lists the offset binary codes for this circuit.

#### Power-Supply Bypassing and Ground Management

For optimum system performance, use PC boards with separate analog and digital ground planes. Wire-wrap boards are not recommended. Connect the two ground planes together at the low-impedance power-supply source. Connect DGND and AGND together at the IC. The best ground connection can be achieved by connecting the DAC's DGND and AGND pins together and connecting that point to the system analog ground plane. If the DAC's DGND is connected to the system digital ground, digital noise may get through to the DAC's analog portion.

Bypass V<sub>DD</sub> with a 0.1µF ceramic capacitor connected between V<sub>DD</sub> and AGND. Mount it with short leads close to the device. Ferrite beads can also be used to further isolate the analog and digital power supplies.

Table 1. Unipolar Code Table

| DAC LATCH | CONTENTS  | ANALOG OUTPUT, Vout                             |  |  |

|-----------|-----------|-------------------------------------------------|--|--|

| MSB       | LSB       | ANALOG OUTPUT, VOUT                             |  |  |

| 1111 1111 | 1111 1111 | V <sub>REF</sub> • (65,535 / 65,536)            |  |  |

| 1000 0000 | 0000 0000 | $V_{REF} \cdot (32,768 / 65,536) = 1/2 V_{REF}$ |  |  |

| 0000 0000 | 0000 0001 | V <sub>REF</sub> • (1 / 65,536)                 |  |  |

| 0000 0000 | 0000 0000 | OV                                              |  |  |

**Table 2. Bipolar Code Table**

| DAC LATCH CONTENTS |             | ANALOG OUTPUT, V <sub>OUT</sub>                           |

|--------------------|-------------|-----------------------------------------------------------|

| MSB                | LSB         | ANALOG GOTF GT, VOOT                                      |

| 1111 1111          | 1 1111 1111 | +V <sub>REF</sub> • (32,767 / 32,768)                     |

| 1000 0000          | 0000 0001   | +VREF • (1 / 32,768)                                      |

| 1000 0000          | 0000 0000   | OV                                                        |

| 0111 1111          | 1 1111 1111 | -V <sub>REF</sub> • (1 / 32,768)                          |

| 0000 0000          | 0000 0000   | -V <sub>REF</sub> • (32,768 / 32,768) = -V <sub>REF</sub> |

### Ordering Information (continued)

| PART       | TEMP. RANGE     | PIN-PACKAGE     | INL<br>(LSB) |

|------------|-----------------|-----------------|--------------|

| MAX541AEPA | -40°C to +85°C  | 8 Plastic DIP   | ±1           |

| MAX541BEPA | -40°C to +85°C  | 8 Plastic DIP   | ±2           |

| MAX541CEPA | -40°C to +85°C  | 8 Plastic DIP   | ±4           |

| MAX541AESA | -40°C to +85°C  | 8 SO            | ±1           |

| MAX541BESA | -40°C to +85°C  | 8 SO            | ±2           |

| MAX541CESA | -40°C to +85°C  | 8 SO            | ±4           |

| MAX542ACPD | 0°C to +70°C    | 14 Plastic DIP  | ±1           |

| MAX542BCPD | 0°C to +70°C    | 14 Plastic DIP  | ±2           |

| MAX542CCPD | 0°C to +70°C    | 14 Plastic DIP  | ±4           |

| MAX542ACSD | 0°C to +70°C    | 14 SO           | ±1           |

| MAX542BCSD | 0°C to +70°C    | 14 SO           | ±2           |

| MAX542CCSD | 0°C to +70°C    | 14 SO           | ±4           |

| MAX542BC/D | 0°C to +70°C    | Dice*           | ±2           |

| MAX542AEPD | -40°C to +85°C  | 14 Plastic DIP  | ±1           |

| MAX542BEPD | -40°C to +85°C  | 14 Plastic DIP  | ±2           |

| MAX542CEPD | -40°C to +85°C  | 14 Plastic DIP  | ±4           |

| MAX542AESD | -40°C to +85°C  | 14 SO           | ±1           |

| MAX542BESD | -40°C to +85°C  | 14 SO           | ±2           |

| MAX542CESD | -40°C to +85°C  | 14 SO           | ±4           |

| MAX542CMJD | -55°C to +125°C | 14 Ceramic SB** | ±4           |

<sup>\*</sup>Dice are tested at  $T_A = +25$ °C, DC parameters only.

## \_\_Functional Diagrams (continued)

### **Chip Information**

TRANSISTOR COUNT: 2209

SUBSTRATE CONNECTED TO DGND

<sup>\*\*</sup>Contact factory for availability.

### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600