# A5G23H065N

## Airfast RF Power GaN Transistor

Rev. 1 — November 2022 Data Sheet: Technical Data

This 8.8 W asymmetrical Doherty RF power GaN transistor is designed for cellular base station applications requiring very wide instantaneous bandwidth capability covering the frequency range of 2300 to 2400 MHz.

This part is characterized and performance is guaranteed for applications operating in the 2300 to 2400 MHz band. There is no guarantee of performance when this part is used in applications designed outside of these frequencies.

#### 2300 MHz

Typical Doherty Single–Carrier W–CDMA Reference Circuit Performance:

V<sub>DD</sub> = 48 Vdc, I<sub>DQA</sub> = 30 mA, V<sub>GSB</sub> = -4.3 Vdc, P<sub>out</sub> = 8.8 W Avg., Input Signal PAR = 9.9 dB @ 0.01% Probability on CCDF. (1)

| Frequency | G <sub>ps</sub><br>(dB) | η <sub>D</sub><br>(%) | Output PAR<br>(dB) | ACPR<br>(dBc) |

|-----------|-------------------------|-----------------------|--------------------|---------------|

| 2300 MHz  | 17.3                    | 61.7                  | 8.3                | -27.3         |

| 2350 MHz  | 17.3                    | 60.2                  | 8.4                | -28.4         |

| 2400 MHz  | 17.1                    | 58.2                  | 8.4                | -29.4         |

1. All data measured in reference circuit with device soldered to printed circuit board.

#### **Features**

- · High terminal impedances for optimal broadband performance

- Improved linearized error vector magnitude with next generation signal

- Able to withstand extremely high output VSWR and broadband operating conditions

- Designed for low complexity linearization systems

- Optimized for massive MIMO active antenna systems for 5G base stations

### A5G23H065N

#### 2300-2400 MHz, 8.8 W Avg., 48 V AIRFAST RF POWER GaN TRANSISTOR

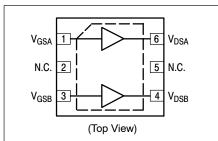

Note: Exposed backside of the package is the source terminal for the transistor.

Figure 1. Pin Connections

#### **Table 1. Maximum Ratings**

| Rating                                                                       | Symbol            | Value       | Unit |

|------------------------------------------------------------------------------|-------------------|-------------|------|

| Drain-Source Voltage                                                         | V <sub>DSS</sub>  | 125         | Vdc  |

| Gate-Source Voltage                                                          | V <sub>GS</sub>   | -16, 0      | Vdc  |

| Operating Voltage                                                            | V <sub>DD</sub>   | 55          | Vdc  |

| Maximum Forward Gate Current, I <sub>G (A+B)</sub> , @ T <sub>C</sub> = 25°C | I <sub>GMAX</sub> | 7.5         | mA   |

| Storage Temperature Range                                                    | T <sub>stg</sub>  | -65 to +150 | °C   |

| Case Operating Temperature Range                                             | T <sub>C</sub>    | -55 to +150 | °C   |

| Maximum Channel Temperature                                                  | T <sub>CH</sub>   | 225         | °C   |

#### **Table 2. Recommended Operating Conditions**

| Characteristic    | Symbol   | Value | Unit |

|-------------------|----------|-------|------|

| Operating Voltage | $V_{DD}$ | 48    | Vdc  |

#### **Table 3. Thermal Characteristics**

| Characteristic                                                                                                        | Symbol                     | Value               | Unit |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|------|

| Thermal Resistance by Infrared Measurement, Active Die Surface-to-Case Case Temperature 119°C, P <sub>D</sub> = 8.1 W | R <sub>θJC</sub> (IR)      | 3.9 (1)             | °C/W |

| Thermal Resistance by Finite Element Analysis, Channel-to-Case Case Temperature 119°C, P <sub>D</sub> = 8.1 W         | R <sub>θCHC</sub><br>(FEA) | 11.5 <sup>(2)</sup> | °C/W |

#### **Table 4. ESD Protection Characteristics**

| Test Methodology                      | Class |

|---------------------------------------|-------|

| Human Body Model (per JS-001-2017)    | 1A    |

| Charge Device Model (per JS-002-2014) | СЗ    |

#### **Table 5. Moisture Sensitivity Level**

| Test Methodology                     | Rating | Package Peak Temperature | Unit |

|--------------------------------------|--------|--------------------------|------|

| Per JESD22-A113, IPC/JEDEC J-STD-020 | 3      | 260                      | °C   |

### Table 6. Electrical Characteristics ( $T_A = 25^{\circ}C$ unless otherwise noted)

| , ,                                                                                                                                              |                     |              |      |            |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|------|------------|------|

| Characteristic                                                                                                                                   | Symbol              | Min          | Тур  | Max        | Unit |

| Off Characteristics (3)                                                                                                                          |                     |              |      |            |      |

|                                                                                                                                                  | I <sub>D(BR)</sub>  | _<br>_       |      | 1.1<br>2.4 | mAdc |

| Off-State Gate Leakage $(V_{DS} = 48 \text{ Vdc}, V_{GS} = -8 \text{ Vdc})$ Carrier $(V_{DS} = 48 \text{ Vdc}, V_{GS} = -8 \text{ Vdc})$ Peaking | I <sub>GLK</sub>    | -1.0<br>-1.0 |      |            | mAdc |

| On Characteristics — Side A, Carrier  Gate Threshold Voltage (V <sub>DS</sub> = 10 Vdc, I <sub>D</sub> = 2.3 mAdc)                               | V <sub>GS(th)</sub> | -4.6         | -2.5 | -1.9       | Vdc  |

| Gate Quiescent Voltage<br>(V <sub>DD</sub> = 48 Vdc, I <sub>DA</sub> = 30 mAdc, Measured in Functional Test)                                     | V <sub>GSA(Q)</sub> | -2.9         | -2.5 | -1.9       | Vdc  |

| Gate-Source Leakage Current<br>(V <sub>DS</sub> = 150 Vdc, V <sub>GS</sub> = -8 Vdc)                                                             | I <sub>GSS</sub>    | -1.1         | _    | _          | mAdc |

| On Characteristics — Side B, Peaking                                                                                                             |                     |              |      |            |      |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 Vdc, I <sub>D</sub> = 5.2 mAdc)                                                                  | V <sub>GS(th)</sub> | -4.6         | -2.5 | -1.9       | Vdc  |

| Gate-Source Leakage Current<br>(V <sub>DS</sub> = 150 Vdc, V <sub>GS</sub> = -8 Vdc)                                                             | I <sub>GSS</sub>    | -2.4         | _    | _          | mAdc |

- 1. Refer to AN1955, Thermal Measurement Methodology of RF Power Amplifiers. Go to <a href="http://www.nxp.com/RF">http://www.nxp.com/RF</a> and search for AN1955.

- 2.  $R_{\theta CHC}$  (FEA) must be used for purposes related to reliability and limitations on maximum channel temperature. MTTF may be estimated by the expression MTTF (hours) =  $10^{[A+B/(T+273)]}$ , where T is the channel temperature in degrees Celsius, A = -11.6 and B = 9129.

3. Each side of device measured separately.

(continued)

2 / 11

A5G23H065N Airfast RF Power GaN Transistor, Rev. 1, November 2022

#### Table 6. Electrical Characteristics (T<sub>A</sub> = 25°C unless otherwise noted) (continued)

| Characteristic                                                                                                                                       | Symbol | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|

| Functional Tests (1) (In NXP Doherty Production Test Fixture, 50 ohm system) $V_{DD}$ = 48 Vdc, $I_{DQA}$ = 30 mA, $V_{GSB}$ = ( $V_t - 1.22$ ) Vdc, |        |     |     |     |      |

| Post = 8.8 W Avg. f = 2300 MHz. 1-tone CW                                                                                                            |        |     |     |     |      |

| Power Gain                    | G <sub>ps</sub> | 14.0 | 15.5 | 18.5 | dB  |

|-------------------------------|-----------------|------|------|------|-----|

| Drain Efficiency              | $\eta_{D}$      | 48.0 | 53.3 | _    | %   |

| Pout @ 6 dB Compression Point | P6dB            | 45.2 | 46.1 | _    | dBm |

Wideband Ruggedness  $^{(2)}$  (In NXP Doherty Reference Circuit, 50 ohm system)  $I_{DQA} = 30$  mA,  $V_{GSB} = -4.3$  Vdc, f = 2350 MHz, Additive White Gaussian Noise (AWGN) with 10 dB PAR

|  |  | ISBW of 400 MHz at 55 Vdc, 17.6 W Avg. Modulated Output Power (3 dB Input Overdrive from 8.8 W Avg. Modulated Output Power) | No Device Degradation |

|--|--|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|

|--|--|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|

Typical Performance (2) (In NXP Doherty Reference Circuit, 50 ohm system)  $V_{DD} = 48 \text{ Vdc}$ ,  $I_{DQA} = 30 \text{ mA}$ ,  $V_{GSB} = -4.3 \text{ Vdc}$ , 2300–2400 MHz Bandwidth

| 2400 Will 2 Ballawiati                                                                          |                    |   |       |   |       |

|-------------------------------------------------------------------------------------------------|--------------------|---|-------|---|-------|

| VBW Resonance Point<br>(IMD Third Order Intermodulation Inflection Point)                       | VBW <sub>res</sub> | _ | 310   | _ | MHz   |

| Gain Flatness in 100 MHz Bandwidth @ Pout = 8.8 W Avg.                                          | G <sub>F</sub>     | _ | 0.2   | _ | dB    |

| Fast CW, 27 ms Sweep                                                                            |                    |   |       |   |       |

| P <sub>out</sub> @ 6 dB Compression Point                                                       | P6dB               | _ | 63.1  | _ | W     |

| AM/PM (Maximum value measured at the P6dB compression point across the 2300–2400 MHz bandwidth) | Φ                  | _ | -18   | _ | ٥     |

| Gain Variation over Temperature (–40°C to +85°C)                                                | ΔG                 | _ | 0.016 | _ | dB/°C |

| Output Power Variation over Temperature (–40°C to +85°C)                                        | ∆P6dB              | _ | 0.002 | _ | dB/°C |

#### **Table 7. Ordering Information**

| Device       | Tape and Reel Information                               | Package     |

|--------------|---------------------------------------------------------|-------------|

| A5G23H065NT4 | T4 Suffix = 2,500 Units, 16 mm Tape Width, 13-inch Reel | DFN 7 × 6.5 |

- 1. Part internally input matched.

- 2. All data measured in reference circuit with device soldered to printed circuit board.

#### Correct Biasing Sequence for GaN Depletion Mode Transistors in a Doherty Configuration

#### Bias ON the device

- 1. Set gate voltage  $V_{\mbox{\footnotesize GSA}}$  and  $V_{\mbox{\footnotesize GSB}}$  to -5 V.

- 2. Set drain voltage  $V_{\mbox{\footnotesize{DSA}}}$  and  $V_{\mbox{\footnotesize{DSB}}}$  to nominal supply voltage (+48 V).

- 3. Increase V<sub>GSA</sub> (carrier side) until I<sub>DQA</sub> current is attained.

- 4. Increase V<sub>GSB</sub> (peaking side) to target bias voltage.

- 5. Apply RF input power to desired level.

#### Bias OFF the device

- 1. Disable RF input power.

- 2. Adjust gate voltage  $V_{\mbox{\footnotesize GSA}}$  and  $V_{\mbox{\footnotesize GSB}}$  to -5 V.

- 3. Adjust drain voltage  $V_{DSA}$  and  $V_{DSB}$  to 0 V. Allow adequate time for drain voltage to reduce to 0 V from external drain capacitors.

- 4. Disable V<sub>GSA</sub> and V<sub>GSB</sub>.

Data Sheet: Technical Data 3 / 11

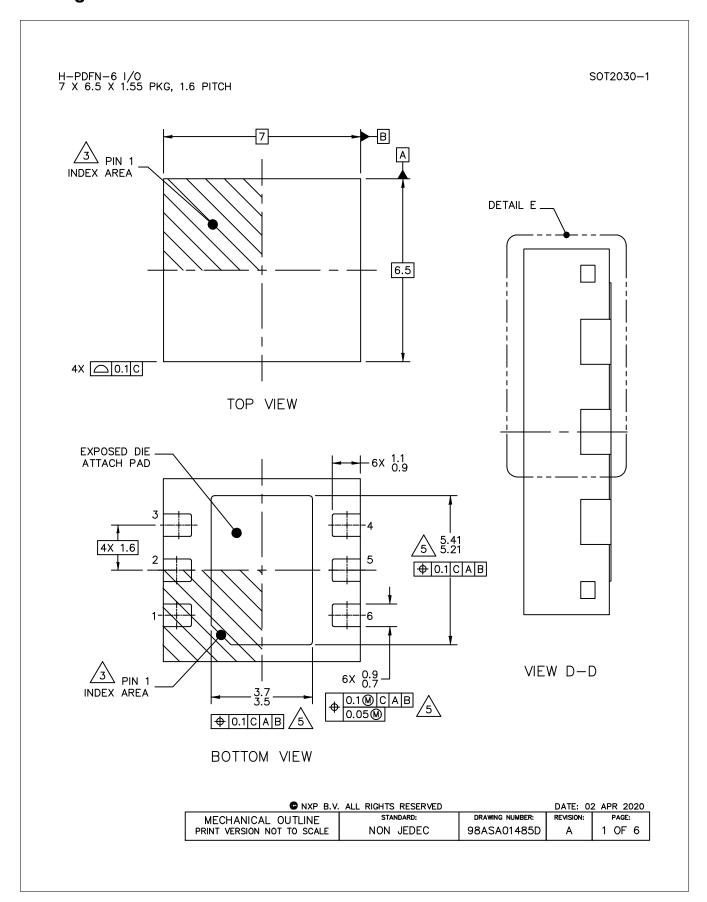

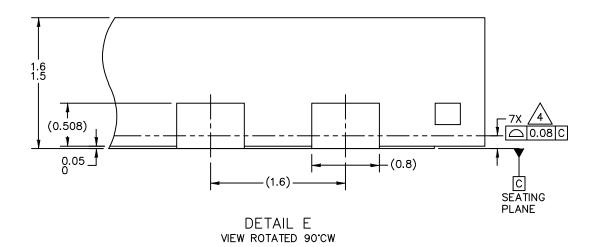

## **Package Information**

Data Sheet: Technical Data 4 / 11

S0T2030-1

MECHANICAL OUTLINE

STANDARD:

DRAWING NUMBER:

REVISION:

PAGE:

PRINT VERSION NOT TO SCALE

NON JEDEC

98ASA01485D

A

2

Data Sheet: Technical Data 5 / 11

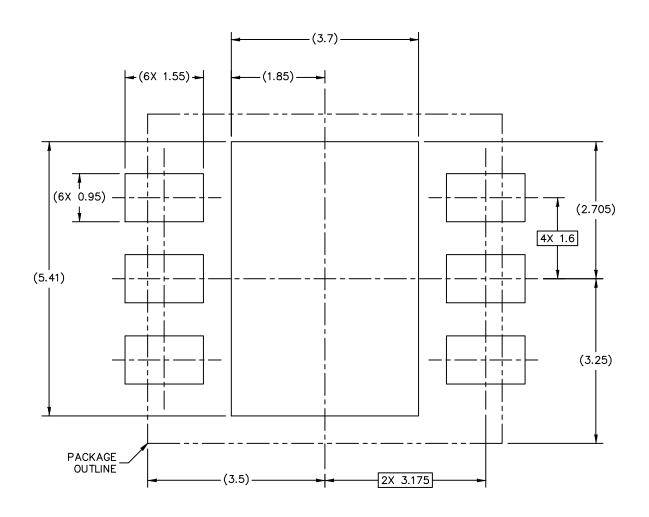

SOT2030-1

### PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| ● NXP B.V. ALL RIGHTS RESERVED DATE: 02 APR 202 |           |                 | 2 APR 2020 |       |

|-------------------------------------------------|-----------|-----------------|------------|-------|

| MECHANICAL OUTLINE                              | STANDARD: | DRAWING NUMBER: | REVISION:  | PAGE: |

| PRINT VERSION NOT TO SCALE                      | NON JEDEC | 98ASA01485D     | Α          | 3     |

Data Sheet: Technical Data 6 / 11

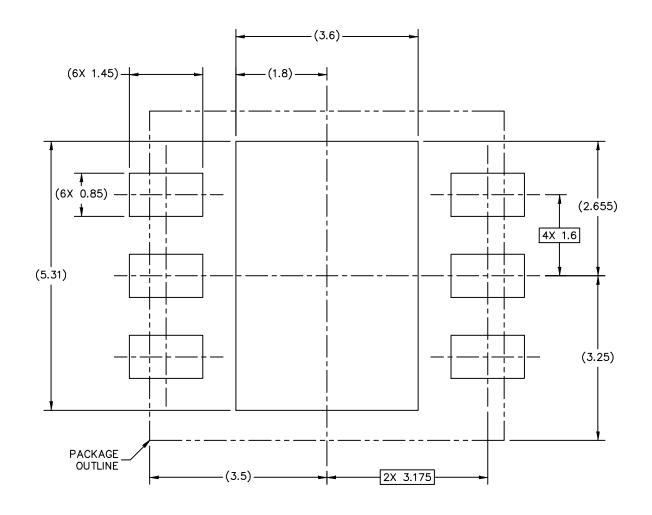

SOT2030-1

## PCB DESIGN GUIDELINES - I/O PADS AND SOLDERABLE AREA

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| ■ NXP B.V. ALL RIGHTS RESERVED DATE: 02 APR 2020 |                            |           | 2 APR 2020      |           |       |

|--------------------------------------------------|----------------------------|-----------|-----------------|-----------|-------|

|                                                  | MECHANICAL OUTLINE         | STANDARD: | DRAWING NUMBER: | REVISION: | PAGE: |

|                                                  | PRINT VERSION NOT TO SCALE | NON JEDEC | 98ASA01485D     | Α         | 4     |

Data Sheet: Technical Data 7 / 11

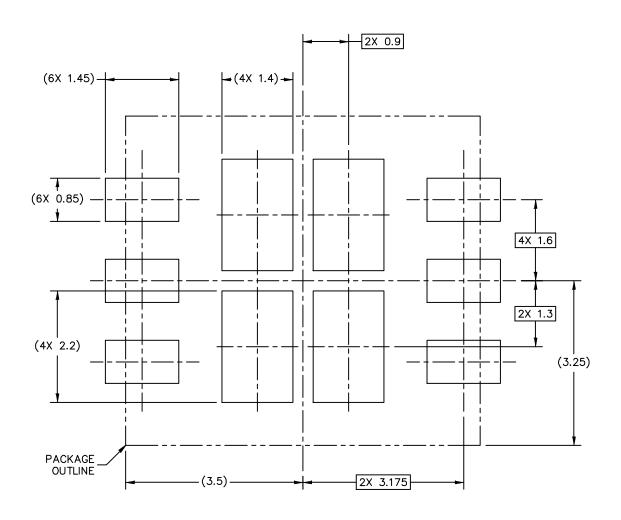

SOT2030-1

8 / 11

STENCIL THICKNESS 0.125 OR 0.15

### PCB DESIGN GUIDELINES - SOLDER PASTE STENCIL

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| NXP B.V. ALL RIGHTS RESERVED     DATE: 02 APR 203 |           |                 | 2 APR 2020 |       |

|---------------------------------------------------|-----------|-----------------|------------|-------|

| MECHANICAL OUTLINE                                | STANDARD: | DRAWING NUMBER: | REVISION:  | PAGE: |

| PRINT VERSION NOT TO SCALE                        | NON JEDEC | 98ASA01485D     | Α          | 5     |

A5G23H065N Airfast RF Power GaN Transistor, Rev. 1, November 2022

Data Sheet: Technical Data

SOT2030-1

9 / 11

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\sqrt{3}$ . PIN 1 FEATURE SHAPE, SIZE AND LOCATION MAY VARY.

COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

RADIUS ON LEAD AND DIE ATTACH FLAG IS OPTIONAL.

| NXP B.V. ALL RIGHTS RESERVED     DATE: 02 APR 20 |           |                 | 2 APR 2020 |       |

|--------------------------------------------------|-----------|-----------------|------------|-------|

| MECHANICAL OUTLINE                               | STANDARD: | DRAWING NUMBER: | REVISION:  | PAGE: |

| PRINT VERSION NOT TO SCALE                       | NON JEDEC | 98ASA01485D     | Α          | 6     |

A5G23H065N Airfast RF Power GaN Transistor, Rev. 1, November 2022

Data Sheet: Technical Data

### **Product Documentation and Software**

Refer to the following resources to aid your design process.

#### **Application Notes**

- AN1907: Solder Reflow Attach Method for High Power RF Devices in Plastic Packages

- AN1955: Thermal Measurement Methodology of RF Power Amplifiers

#### Software

.s2p File

## **Revision History**

The following table summarizes revisions to this document.

| Revision | Date      | Description                                                                                                                                                                                                                                                                       |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | Nov. 2021 | Initial release of data sheet                                                                                                                                                                                                                                                     |

| 1        | Nov. 2022 | <ul> <li>Table 1, Maximum Ratings: Gate-Source Voltage: updated -8, 0 to -16, 0 Vdc, p. 2</li> <li>Table 4, ESD Protection Characteristics, Human Body Model: updated to reflect test data, p. 2</li> <li>General updates made to align data sheet to current standard</li> </ul> |

Data Sheet: Technical Data 10 / 11

### How to Reach Us

Home Page: nxp.com

Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo and Airfast are trademarks of NXP B.V. All other product or service names are the property of their respective owners.

© NXP B.V. 2021–2022

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: November 2022 Document identifier: A5G23H065N