# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

## MICROCIRCUIT DATA SHEET

Original Creation Date: 2/21/00 Last Update Date: 11/10/03 Last Major Revision Date: 2/21/00

# Low Voltage LVDS Quad CMOS Differential Line Receiver

#### General Description

MNDS90LV032A-X REV 0D0

The DS90LV032A is a quad differential line receiver designed for applications requiring low power dissipation and high data rates.

The DS90LV032A accepts low voltage differential input signals and translates them to 3V CMOS output levels. The receiver supports a TRI-STATE function that may be used to multiplex outputs.

The DS90LV032A and companion LVDS line driver (DS90LV031A) provide a new alternative to high power pseudo-ECL devices for high speed point to point interface applications.

In addition, the DS90LV032A provides power-off high impedance LVDS inputs. This feature assures minimal loading effect on the LVDS bus lines when VCC is not present.

#### Industry Part Number

DS90LV032A

Prime Die

DS90LV032A

## Controlling Document

SEE FEATURES SECTION

#### NS Part Numbers

DS90LV032AW-MLS DS90LV032AW-QML DS90LV032AWGMLS DS90LV032AWGQML

| Processing                      | Subgrp | Description         | Temp ( $^{\circ}$ C) |

|---------------------------------|--------|---------------------|----------------------|

| MIL-STD-883, Method 5004        | 1      | Static tests at     | +25                  |

|                                 | 2      | Static tests at     | +85                  |

|                                 | 3      | Static tests at     | -55                  |

| Quality Conformance Inspection  | 4      | Dynamic tests at    | +25                  |

| guarro, compormance improvement | 5      | Dynamic tests at    | +85                  |

| MIL-STD-883, Method 5005        | 6      | Dynamic tests at    | -55                  |

| MIL-SID-003, Method 3003        | 7      | Functional tests at | +25                  |

|                                 | 8A     | Functional tests at | +85                  |

|                                 | 8B     | Functional tests at | -55                  |

|                                 | 9      | Switching tests at  | +25                  |

|                                 | 10     | Switching tests at  | +85                  |

|                                 | 11     | Switching tests at  | -55                  |

#### **Features**

- High impedance LVDS inputs with power-off

- Accepts small swing (330 mV) differential signal levels.

- Low power dissipation.

- Low differential skew.

- Low chip to chip skew

- +85C thru -55C operating temperature range

- Pin compatible with DS90C032A and DS26C32A.

- Compatible with ANSI/TIA/EIA-644

- Typical Rise/Fall time is 350 ps

### CONTROLLING DOCUMENT:

DS90LV032AW-QML 5962-9865201QFA DS90LV032AWGQML 5962-9865201QXA

## (Absolute Maximum Ratings)

(Note 1)

Supply Voltage (Vcc) -0.3 to +4VInput Voltage (RIN+, RIN-) -0.3 to 3.9V Enable Input Voltage (EN, EN\*) -0.3 to (Vcc+0.3V) Output Voltage (ROUT) -0.3 to (Vcc+0.3V) Storage Temperature Range (Tstg) -65C to + 150C Lead Temperature Soldering 4 seconds 260 C Maximum Package Power Dissipation @ +25C (Note 2) 16 PIN CERPAK (W Pkg) 845mW 16 PIN CERAMIC SOIC (WG Pkg) 845mW Thermal Resistance. (Theta JA) 16 PIN CERPAK (W Pkg) 148 C/W 16 PIN CERAMIC SOIC (WG Pkg) 148 C/W Thermal Resistance. (Theta JC) 16 PIN CERPAK (W Pkg) 21 C/W 16 PIN CERAMIC SOIC (WG Pkg) 21 C/W ESD Rating. 4500 Volts.

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Derate (W & WG Pkgs) @ 6.8 mW/C above +25C.

## Recommended Operating Conditions

Operating Voltage (Vcc)

Maximum Junction Temperature

3.15V to 3.45V

+150C

Operating Temperature Range (Ta)

-55C to +85C

Receiver Input Voltage

GND to 3.0V

## Electrical Characteristics

## DC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.)

DC: Over supply voltage range of 3.15V to 3.45V and operating temperature of -55C to +85C unless otherwise specified.

| SYMBOL | PARAMETER                                       | CONDITIONS                          | NOTES       | PIN-<br>NAME  | MIN   | MAX         | UNIT  | SUB-<br>GROUPS |

|--------|-------------------------------------------------|-------------------------------------|-------------|---------------|-------|-------------|-------|----------------|

| VTL    | Differential<br>Input Low<br>Threshold          | Vcm = +1.2V                         | 1           | RIN+,<br>RIN- | -100  |             | mV    | 1, 2,          |

| VTH    | Differential<br>Input High<br>Threshold         | Vcm = +1.2V                         |             | RIN+,<br>RIN- |       | 100         | mV    | 1, 2,          |

| VCMR   | Common Mode<br>Voltage Range                    | VID = 200mV peak to peak            | 1, 4        | RIN+,<br>RIN- | 0.1   | 2.3         | V     | 1, 2,          |

| IIN    | Input Current                                   | Vcc = 3.45V or 0V, Vin = 2.8V or 0V |             | RIN+,<br>RIN- |       | <u>+</u> 10 | uA    | 1, 2,          |

|        |                                                 | Vcc = 0V, Vin = 3.45V               |             | RIN+,<br>RIN- |       | <u>+</u> 20 | uA    | 1, 2,          |

| VOH    | Output High<br>Voltage                          | Ioh = -0.4 mA, Vid = 200mV          |             | ROUT          | 2.7   |             | V     | 1, 2,          |

|        |                                                 | Ioh = -0.4 mA, Inputs Open          |             | ROUT          | 2.7   |             | V     | 1, 2,          |

| VOL    | Output Low<br>Voltage                           | Iol = 2 mA, Vid = -200mV            |             | ROUT          |       | 0.25        | V     | 1, 2,          |

| IOS    | Output Short<br>Circuit Current                 | Enabled, Vout = 0V                  | 5           | ROUT          | -15   | -120        | mA    | 1, 2,          |

| IOZ    | Output TRI-STATE<br>Current                     | Disabled, Vout = 0V or Vcc          |             | ROUT          |       | <u>+</u> 10 | uA    | 1, 2,          |

| VIH    | Input High<br>Voltage                           |                                     | 6           | EN, EN*       | 2.0   | Vcc         | V     | 1, 2,          |

| VIL    | Input Low Voltage                               |                                     | 6           | EN, EN*       | GND   | 0.8         | V     | 1, 2,          |

| II     | Input Current                                   |                                     | <u>+</u> 10 | uA            | 1, 2, |             |       |                |

| VCL    | Input Clamp Icl = -18mA EN, Voltage             |                                     | EN, EN*     |               | -1.5  | V           | 1, 2, |                |

| Icc    | No Load Supply<br>Current Receivers<br>Enabled  | EN, EN* = Vcc or GND, Inputs Open   |             | Vcc           |       | 15          | mA    | 1, 2,          |

|        | Filabled                                        | EN, EN* = 2.4 or 0.5, Inputs Open   |             | Vcc           |       | 15          | mA    | 1, 2,          |

| IccZ   | No Load Supply<br>Current Receivers<br>Disabled | Current Receivers                   |             |               |       | 5           | mA    | 1, 2,          |

## Electrical Characteristics

#### AC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) AC: VCC = 3.15/3.30/3.45V, CL = 20pF

| SYMBOL | PARAMETER                                        | CONDITIONS                                                                                    |   | PIN-<br>NAME | MIN | MAX  | UNIT | SUB-<br>GROUPS |

|--------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|---|--------------|-----|------|------|----------------|

| tPHLD  | Differential<br>Propagation Delay<br>High to Low | Vid = 200mV, Input pulse = 1.1V to<br>1.3V, Vin = 1.2V (0 differential) to<br>Vout = 1/2 Vcc  |   |              | 0.5 | 3.5  | ns   | 9, 10,<br>11   |

| tPLHD  | Differential<br>Propagation Delay<br>Low to High | Vid = 200mV, Input pulse = 1.1V to<br>1.3V, Vin = 1.2V (0V differential) to<br>Vout = 1/2 Vcc |   |              | 0.5 | 3.5  | ns   | 9, 10,<br>11   |

| tSKD   | Differential Skew   tPHLD-tPLHD                  | CL = 20pF, Vid = 200mV                                                                        |   |              |     | 1.5  | ns   | 9, 10,<br>11   |

| tSK1   | Channel to<br>Channel Skew                       | CL = 20pF, Vid = 200mV                                                                        | 2 |              |     | 1.75 | ns   | 9, 10,<br>11   |

| tSK2   | Chip to Chip Skew                                | CL = 20pF, Vid = 200mV                                                                        | 3 |              |     | 3.0  | ns   | 9, 10,<br>11   |

| tPLZ   | Disable Time Low to Z                            | Input pulse = 0V to 3.0V, Vin = 1.5V, Vout = Vol+0.5V, RL= 1K Ohm.                            |   |              |     | 12   | ns   | 9, 10,<br>11   |

| tPHZ   | Disable Time High to Z                           | Input pulse = 0V to 3.0V, Vin = 1.5V, Vout = Voh-0.5V, RL = 1K Ohm.                           |   |              |     | 12   | ns   | 9, 10,<br>11   |

| tPZH   | Enable Time Z to<br>High                         | Input pulse = 0V to 3.0V, Vin = 1.5V, Vout = 50%, RL = 1K Ohm.                                |   |              |     | 20   | ns   | 9, 10,<br>11   |

| tPZL   | Enable Time Z to Low                             | Input pulse = 0V to 3.0V, Vin = 1.5V, Vout = 50%, RL = 1K Ohm.                                |   |              |     | 20   | ns   | 9, 10,<br>11   |

- Note 1: Tested during VOH/VOL tests by applying appropriate voltage levels to the input pins of the device under test.

- Note 2: Channel to Channel Skew is defined as the difference between the propagation delay of one channel and that of the others on the same chip with any event on the inputs.

- Note 3: Chip to Chip Skew is defined as the difference between the minimum and maximum specified differential propagation delays.

- Note 4: The VCMR range is reduced for larger input differential voltage (VID). Example: If VID = 400mV, the VCMR is 0.2V to 2.2V. A VID up to Vcc- 0V may be applied to the Rin+/Rin- inputs with the Common-Mode voltage set to Vcc/2.

- Note 5: Output short circuit current (Ios) is specified as magnitude only, minus sign indicates direction of current. Only one output should be shorted at a time, do not exceed maximum junction temperature.

- Note 6: Tested during IOZ tests by applying appropriate threshold voltage levels to the EN and EN\* pins.

# Graphics and Diagrams

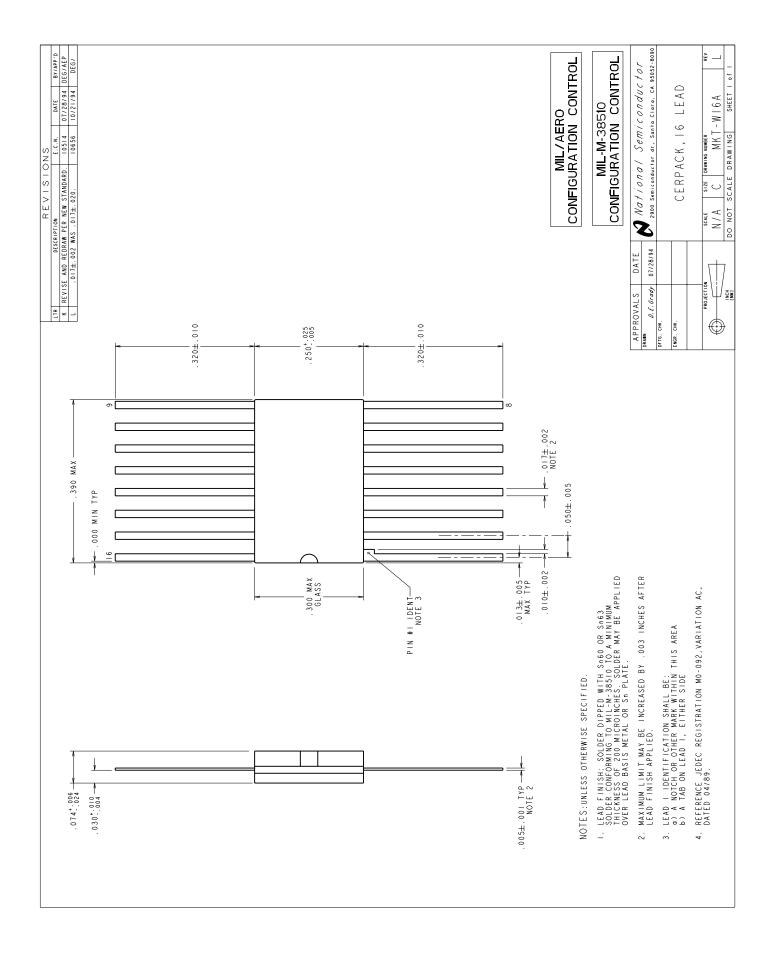

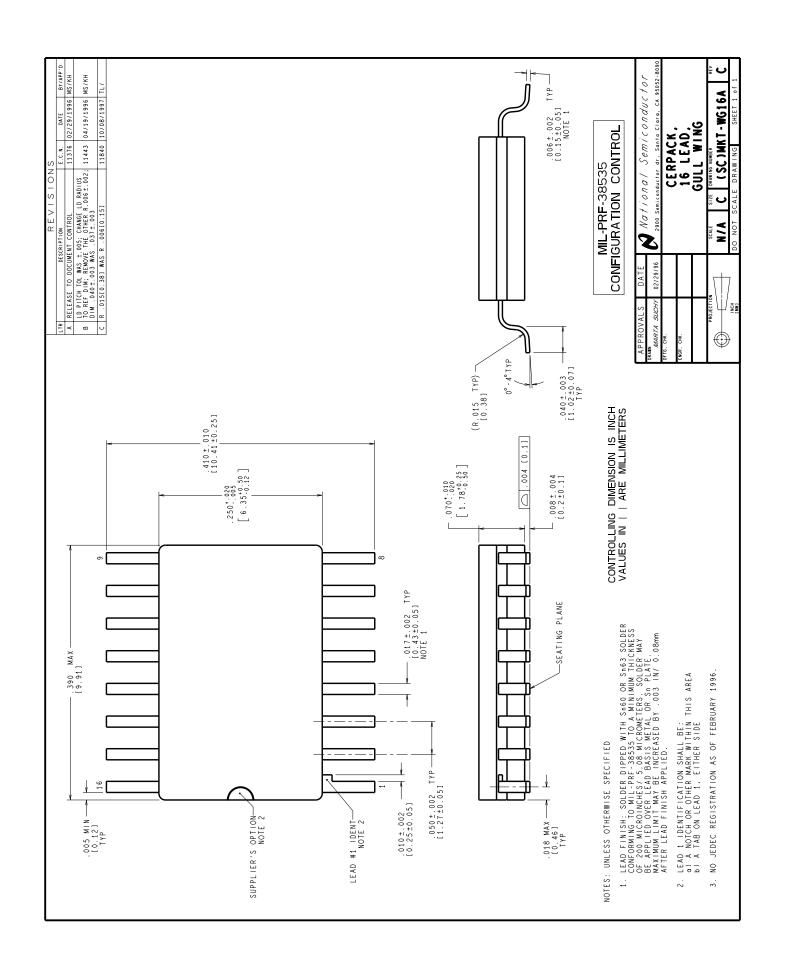

| GRAPHICS# | DESCRIPTION                          |

|-----------|--------------------------------------|

| W16ARL    | CERPACK (W), 16 LEAD (P/P DWG)       |

| WG16ARC   | CERAMIC SOIC (WG), 16 LEAD (P/P DWG) |

See attached graphics following this page.

## Revision History

| Rev | ECN #    | Rel Date | Originator      | Changes                                                                                                                                                                                 |

|-----|----------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A0 | M0003631 | 08/16/02 | Mike Fitzgerald | Initial MDS Release                                                                                                                                                                     |

| 0B0 | M0004035 | 08/15/03 | Rose Malone     | Update MDS: MNDS90LV032A-X, Rev. 0A0 to MNDS90LV031A-X, Rev. 0B0. Added to Main Table NS Par Number DS90LV032AW-MLS. Moved reference to SMD number from Main Table to Features Section. |

| 0C0 | M0004184 | 11/10/03 | Rose Malone     | Update MDS: MNDS90LV032A-X, Rev. 0B0 to 0C0. MDS enhancements: Additional verbage to the general discription, Main Table and Added new bullet to the Features Section.                  |

| 0D0 | M0004345 | 11/10/03 | Rose Malone     | Update MDS: MNDS90LV032A-X, Rev. 0C0 to MNDS90LV032A-X, Rev. 0D0. Updated Features Section Typical Rise/Fall time.                                                                      |