LDC1612-Q1, LDC1614-Q1

SNOSCZ8 - APRIL 2016

# LDC1612-Q1, LDC1614-Q1 Multi-Channel 28-Bit Inductance to Digital Converter (LDC) for **Inductive Sensing**

#### **Features**

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1:–40°C to +125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C5

- Easy-to-use Minimal Configuration Required

- Measure up to 4 Sensors with One IC

- Multiple Channels Support Environmental and Aging Compensation

- Multi-Channel Remote Sensing Provides Lowest System Cost

- Pin-Compatible Medium and High-resolution **Options**

- LDC1312-Q1/LDC1314-Q1: 2/4-ch 12-bit LDC

- LDC1612-Q1/LDC1614-Q1: 2/4-ch 28-bit LDC

- Sensing range beyond two coil diameters

- Supports Wide Sensor Frequency Range of 1kHz to 10MHz

- Power Consumption:

- 35 µA Low Power Sleep Mode

- 200 nA Shutdown Mode

- 3.3V Operation

- Support Internal or External Reference Clock

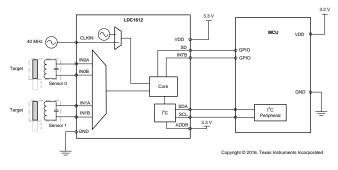

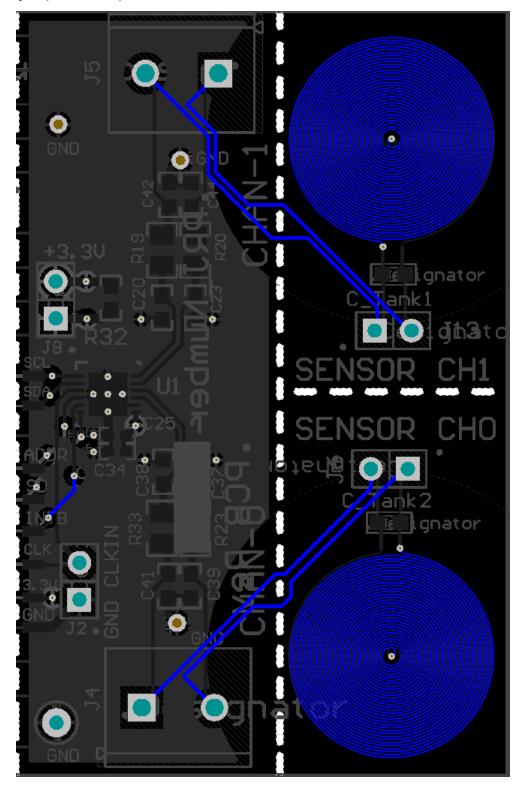

## Simplified Schematic

Immune to DC Magnetic Fields and Magnets

### **Applications**

- Automotive Buttons and Knobs

- Linear and Rotational Encoders

- Slider Buttons

- Metal Detection in Industrial and Automotive

- Flow Meters

### Description

The LDC1612-Q1 and LDC1614-Q1 are 2- and 4channel, 28-bit inductance to digital converters (LDCs) for inductive sensing solutions. With multiple channels and support for remote sensing, the LDC1612-Q1 and LDC1614-Q1 enable performance and reliability benefits of inductive sensing to be realized at minimal cost and power. The products are easy to use, only requiring that the sensor frequency be within 1 kHz and 10 MHz to begin sensing. The wide 1 kHz to 10 MHz sensor frequency range also enables use of very small PCB coils, further reducing sensing solution cost and size.

#### Device Information<sup>(1)</sup>

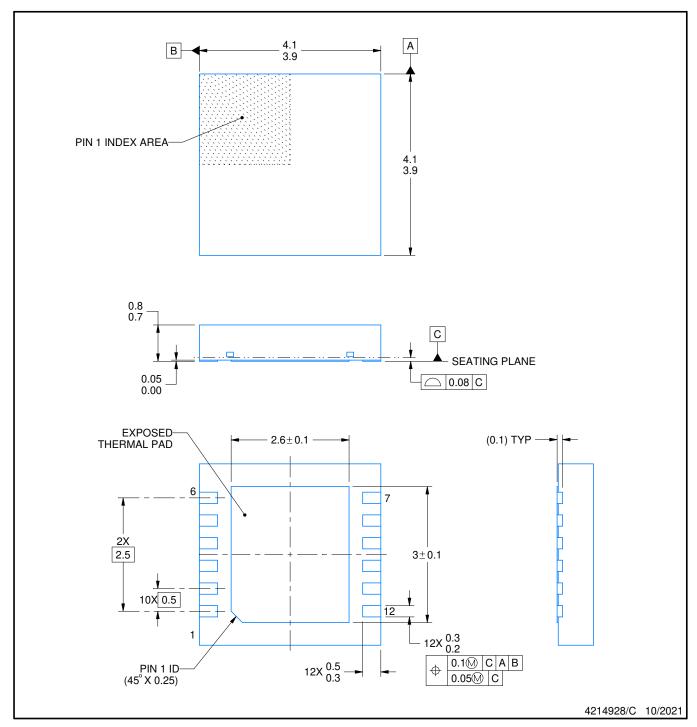

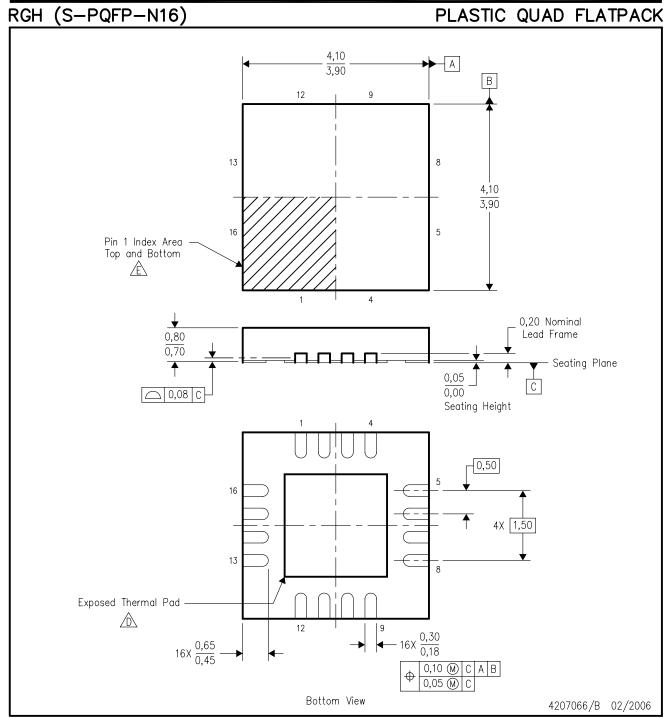

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LDC1612-Q1  | WSON (12) | 4.00 mm × 4.00 mm |

| LDC1614-Q1  | WQFN (16) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

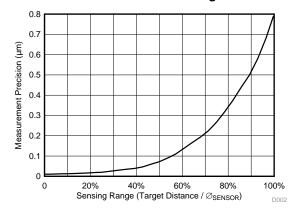

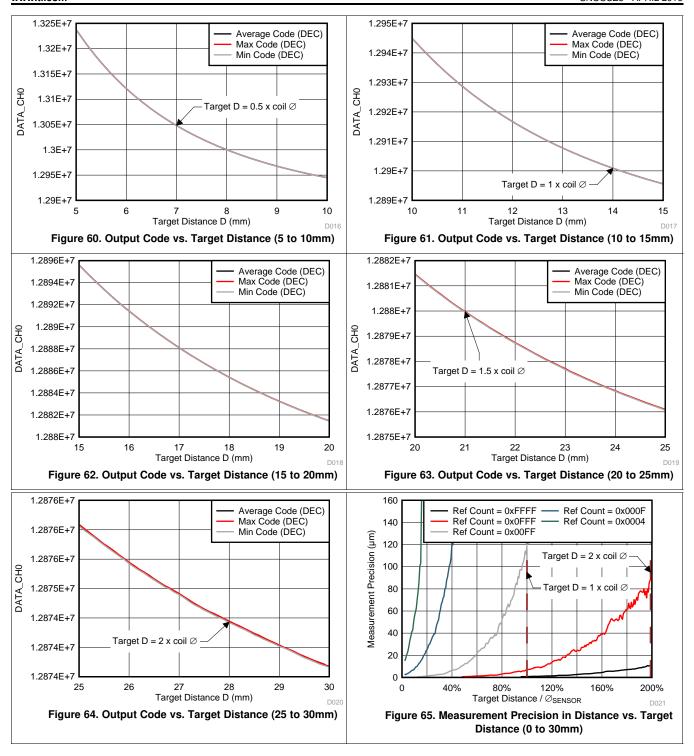

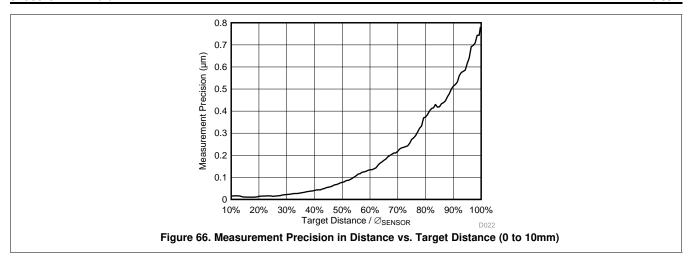

#### Measurement Precision vs. Target Distance

# **Table of Contents**

| 1 | Features 1                          | 8.4 Device Functional Modes                            |

|---|-------------------------------------|--------------------------------------------------------|

| 2 | Applications 1                      | 8.5 Programming                                        |

| 3 | Description 1                       | 8.6 Register Maps21                                    |

| 4 | Revision History2                   | 9 Application and Implementation 40                    |

| 5 | Description Continued 3             | 9.1 Application Information                            |

| 6 | Pin Configuration and Functions 4   | 9.2 Typical Application43                              |

| 7 | _                                   | 10 Power Supply Recommendations 48                     |

| ′ | Specifications                      | 11 Layout                                              |

|   | •                                   | 11.1 Layout Guidelines                                 |

|   | 7.2 ESD Ratings                     | 11.2 Layout Example48                                  |

|   | 7.4 Thermal Information             | 12 Device and Documentation Support 53                 |

|   | 7.5 Electrical Characteristics      | 12.1 Device Support                                    |

|   | 7.6 Timing Characteristics          | 12.2 Documentation Support 53                          |

|   | 7.7 Switching Characteristics - I2C | 12.3 Community Resources 53                            |

|   | 7.8 Typical Characteristics 8       | 12.4 Related Links 53                                  |

| 8 | Detailed Description                | 12.5 Trademarks                                        |

| ٠ | 8.1 Overview                        | 12.6 Electrostatic Discharge Caution 53                |

|   | 8.2 Functional Block Diagram        | 12.7 Glossary53                                        |

|   | 8.3 Feature Description             | 13 Mechanical, Packaging, and Orderable Information 53 |

# 4 Revision History

| DATE       | REVISION | NOTES            |

|------------|----------|------------------|

| April 2016 | *        | Initial release. |

www.ti.com

#### 5 Description Continued

The high resolution channels allow for a much larger sensing range, maintaining good performance beyond two coil diameters. Well-matched channels allow for differential and ratiometric measurements, which enable designers to use one channel to compensate their sensing for environmental and aging conditions such as temperature, humidity, and mechanical drift.

Given their ease of use, low power, and low system cost these products enable designers to greatly improve performance, reliability, and flexibility over existing sensing solutions and to introduce brand new sensing capabilities to products in all markets, especially consumer and industrial applications.

These devices are easily configured via an I2C interface. The two-channel LDC1612-Q1 is available in a WSON-12 package and the four-channel LDC1614-Q1 is available in a WQFN-16 package.

# TEXAS INSTRUMENTS

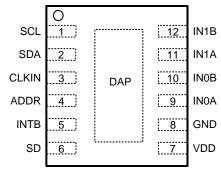

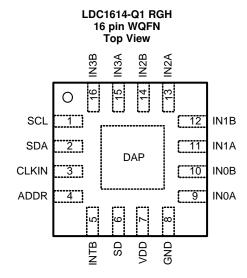

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN |                    | TYPE <sup>(1)</sup> | DECORIDATION                                                                                 |

|-----|--------------------|---------------------|----------------------------------------------------------------------------------------------|

| NO. | NAME               | IYPE                | DESCRIPTION                                                                                  |

| 1   | SCL                | 1                   | I2C Clock input                                                                              |

| 2   | SDA                | I/O                 | I2C Data input/output                                                                        |

| 3   | CLKIN              | I                   | Master Clock input. Tie this pin to GND if internal oscillator is selected                   |

| 4   | ADDR               | 1                   | I2C Address selection pin: when ADDR=L, I2C address = 0x2A, when ADDR=H, I2C address = 0x2B. |

| 5   | INTB               | 0                   | Configurable Interrupt output pin                                                            |

| 6   | SD                 | I                   | Shutdown input                                                                               |

| 7   | VDD                | Р                   | Power Supply                                                                                 |

| 8   | GND                | G                   | Ground                                                                                       |

| 9   | IN0A               | Α                   | External LC sensor 0 connection                                                              |

| 10  | IN0B               | Α                   | External LC sensor 0 connection                                                              |

| 11  | IN1A               | Α                   | External LC sensor 1 connection                                                              |

| 12  | IN1B               | Α                   | External LC sensor 1 connection                                                              |

| 13  | IN2A               | Α                   | External LC sensor 2 connection (LDC1614 only)                                               |

| 14  | IN2B               | Α                   | External LC sensor 2 connection (LDC1614 only)                                               |

| 15  | IN3A               | Α                   | External LC sensor 3 connection (LDC1614 only)                                               |

| 16  | IN3B               | Α                   | External LC sensor 3 connection (LDC1614 only)                                               |

| DAP | DAP <sup>(2)</sup> | N/A                 | Connect to Ground                                                                            |

<sup>(1)</sup> I = Input, O = Output, P=Power, G=Ground, A=Analog

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

<sup>(2)</sup> There is an internal electrical connection between the exposed Die Attach Pad (DAP) and the GND pin of the device. Although the DAP can be left floating, for best performance the DAP should be connected to the same potential as the device's GND pin. Do not use the DAP as the primary ground for the device. The device GND pin must always be connected to ground.

# 7 Specifications

#### 7.1 Absolute Maximum Ratings

|                  |                                  | MIN  | MAX     | UNIT |

|------------------|----------------------------------|------|---------|------|

| $V_{DD}$         | Supply Voltage                   |      | 5       | V    |

| Vi               | Voltage on any pin               | -0.3 | VDD+0.3 | V    |

| IA               | Input current on any INx pin     | -8   | 8       | mA   |

| ID               | Input current on any Digital pin | -5   | 5       | mA   |

| Tj               | Junction Temperature             | -55  | 150     | °C   |

| T <sub>stg</sub> | Storage temperature range        | -65  | 150     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                       |                         |                                                         | VALUE | UNIT |

|-----------------------|-------------------------|---------------------------------------------------------|-------|------|

| M                     |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 |      |

| V <sub>(ESD)</sub> EI | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            | ±750  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 7.3 Recommended Operating Conditions

Unless otherwise specified, all limits ensured for  $T_A = 25$ °C, VDD = 3.3 V

|                |                       | MIN | NOM MAX | UNIT |

|----------------|-----------------------|-----|---------|------|

| VDD            | Supply Voltage        | 2.7 | 3.6     | V    |

| T <sub>A</sub> | Operating Temperature | -40 | 125     | °C   |

#### 7.4 Thermal Information

|                      |                                              | LDC1612    | LDC1614    |      |

|----------------------|----------------------------------------------|------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DNT (WSON) | RGH (WQFN) | UNIT |

|                      |                                              | 12 PINS    | 16 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 36.7       | 35.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 36.2       | 36.2       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 14         | 13.4       | °C/W |

| $\psi_{JT}$          | Junction-to-top characterization parameter   | 0.4        | 0.4        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 14.2       | 13.4       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.5        | 3.5        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# TEXAS INSTRUMENTS

# 7.5 Electrical Characteristics (1)

Unless otherwise specified, all limits ensured for  $T_A = 25$ °C, VDD = 3.3 V

|                           | PARAMETER                                                   | TEST CONDITIONS <sup>(2)</sup>                          | MIN <sup>(3)</sup> | TYP <sup>(4)</sup> | MAX <sup>(3)</sup> | UNIT   |

|---------------------------|-------------------------------------------------------------|---------------------------------------------------------|--------------------|--------------------|--------------------|--------|

| POWER                     |                                                             |                                                         |                    |                    |                    |        |

| $V_{DD}$                  | Supply Voltage                                              | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$    | 2.7                |                    | 3.6                | V      |

| I <sub>DD</sub>           | Supply Current (not including sensor current) (5)           | CLKIN = 10MHz (6)                                       |                    | 2.1                |                    | mA     |

| I <sub>DDSL</sub>         | Sleep Mode Supply Current <sup>(5)</sup>                    |                                                         |                    | 35                 | 60                 | μΑ     |

| I <sub>SD</sub>           | Shutdown Mode Supply<br>Current <sup>(5)</sup>              |                                                         |                    | 0.2                | 1                  | μΑ     |

| SENSOR                    |                                                             |                                                         |                    |                    |                    |        |

| I <sub>SENSORMAX</sub>    | Sensor Maximum Current drive                                | HIGH_CURRENT_DRV = b0                                   |                    | 1.5                |                    | mA     |

| $R_P$                     | Sensor R <sub>P</sub>                                       | DRIVE_CURRENT_CHx = 0xF800                              | 1                  |                    | 100                | kΩ     |

| IHD <sub>SENSORMAX</sub>  | High current sensor drive mode:<br>Sensor Maximum Current   | HIGH_CURRENT_DRV = b1<br>DRIVE_CURRENT_CH0 = 0xF800     |                    | 6                  |                    | mA     |

| R <sub>P_HD_MIN</sub>     | Minimum sensor R <sub>P</sub>                               | Channel 0 only                                          |                    | 250                |                    | Ω      |

| f <sub>SENSOR</sub>       | Sensor Resonance Frequency                                  | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$          | 0.001              |                    | 10                 | MHz    |

| $V_{SENSORMAX}$           | Maximum oscillation amplitude (peak)                        |                                                         |                    | 1.8                |                    | V      |

| N <sub>BITS</sub>         | Number of bits                                              |                                                         |                    |                    | 28                 | bits   |

| f <sub>CS</sub>           | Maximum Channel Sample Rate                                 | single active channel continuous conversion, SCL=400kHz |                    |                    | 4.08               | kSPS   |

| C <sub>IN</sub>           | Sensor Pin input capacitance                                |                                                         |                    | 4                  |                    | pF     |

| MASTER CLOCK              | <b>X</b>                                                    |                                                         |                    |                    |                    |        |

| f <sub>CLKIN</sub>        | External Master Clock Input<br>Frequency (CLKIN)            | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$    | 2                  |                    | 40                 | MHz    |

| CLKIN <sub>DUTY_MIN</sub> | External Master Clock minimum acceptable duty cycle (CLKIN) |                                                         |                    | 40%                |                    |        |

| CLKIN <sub>DUTY_MAX</sub> | External Master Clock maximum acceptable duty cycle (CLKIN) |                                                         |                    | 60%                |                    |        |

| V <sub>CLKIN_LO</sub>     | CLKIN low voltage threshold                                 |                                                         |                    |                    | 0.3×VDD            | V      |

| V <sub>CLKIN_HI</sub>     | CLKIN high voltage threshold                                |                                                         | 0.7×VD<br>D        |                    |                    | V      |

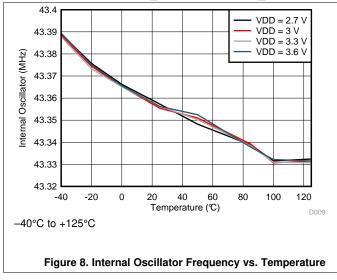

| fINTCLK                   | Internal Master Clock Frequency range                       |                                                         | 35                 | 43.4               | 55                 | MHz    |

| T <sub>Cf_int_µ</sub>     | Internal Master Clock<br>Temperature Coefficient mean       |                                                         |                    | -13                |                    | ppm/°C |

- (1) Electrical Characteristics Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that TJ = TA. Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

- (2) Register values are represented as either binary (b is the prefix to the digits), or hexadecimal (0x is the prefix to the digits). Decimal values have no prefix.

- (3) Limits are ensured by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (4) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- 5) I2C read/write communication and pullup resistors current through SCL, SDA not included.

- (6) Sensor inductor: 2 layer, 32 turns/layer, 14mm diameter, PCB inductor with L=19.4 μH, R<sub>P</sub>=5.7 kΩ at 2MHz Sensor capacitor: 330 pF 1% COG/NP0 Target: Aluminum, 1.5mm thickness Channel = Channel 0 (continuous mode) CLKIN = 40 MHz, CHx\_FIN\_DIVIDER = b0000, CHx\_FREF\_DIVIDER = b00 0000 0001 CH0\_RCOUNT = 0xFFFF, SETTLECOUNT\_CH0 = 0x0100 RP\_OVERRIDE = b1, AUTO\_AMP\_DIS = b1, DRIVE\_CURRENT\_CH0 = 0x9800

#### 7.6 Timing Characteristics

|                         |                                                          | MIN | NOM | MAX | UNIT |

|-------------------------|----------------------------------------------------------|-----|-----|-----|------|

| twakeup                 | Wake-up Time from SD high-low transition to I2C readback |     |     | 2   | ms   |

| t <sub>WD-TIMEOUT</sub> | Sensor recovery time (after watchdog timeout)            |     | 5.2 |     | ms   |

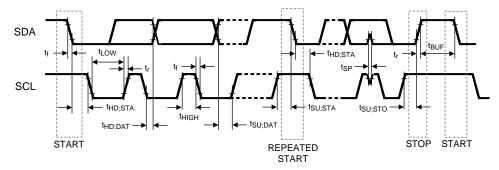

# 7.7 Switching Characteristics - I2C

Unless otherwise specified, all limits ensured for  $T_A$  = 25°C, VDD = 3.3 V

|                     | PARAMETER                                                                        | TEST CONDITIONS                                       | MIN                 | TYP                 | MAX                 | UNIT |

|---------------------|----------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|---------------------|---------------------|------|

| VOLTAGE L           | EVELS                                                                            |                                                       | •                   |                     |                     |      |

| V <sub>IH</sub>     | Input High Voltage                                                               |                                                       | 0.7×V <sub>DD</sub> |                     |                     | V    |

| V <sub>IL</sub>     | Input Low Voltage                                                                |                                                       |                     |                     | 0.3×V <sub>DD</sub> | V    |

| V <sub>OL</sub>     | Output Low Voltage (3mA sink current)                                            |                                                       |                     |                     | 0.4                 | V    |

| HYS                 | Hysteresis                                                                       |                                                       |                     | 0.1×V <sub>DD</sub> |                     | V    |

| 12C TIMING          | CHARACTERISTICS                                                                  |                                                       |                     |                     | ·                   |      |

| f <sub>SCL</sub>    | Clock Frequency                                                                  |                                                       | 10                  |                     | 400                 | kHz  |

| t <sub>LOW</sub>    | Clock Low Time                                                                   |                                                       | 1.3                 |                     |                     | μs   |

| t <sub>HIGH</sub>   | Clock High Time                                                                  |                                                       | 0.6                 |                     |                     | μs   |

| t <sub>HD;STA</sub> | Hold Time (repeated) START condition                                             | After this period, the first clock pulse is generated | 0.6                 |                     |                     | μs   |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition                                       |                                                       | 0.6                 |                     |                     | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                   |                                                       | 0                   |                     |                     | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                  |                                                       | 100                 |                     |                     | ns   |

| t <sub>SU;STO</sub> | Set-up time for STOP condition                                                   |                                                       | 0.6                 |                     |                     | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                 |                                                       | 1.3                 |                     |                     | μs   |

| t <sub>VD;DAT</sub> | Data valid time                                                                  |                                                       |                     |                     | 0.9                 | μs   |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                                                      |                                                       |                     |                     | 0.9                 | μs   |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by the input filter <sup>(1)</sup> |                                                       |                     |                     | 50                  | ns   |

(1) This parameter is specified by design and/or characterization and is not tested in production.

Figure 1. I2C Timing

# TEXAS INSTRUMENTS

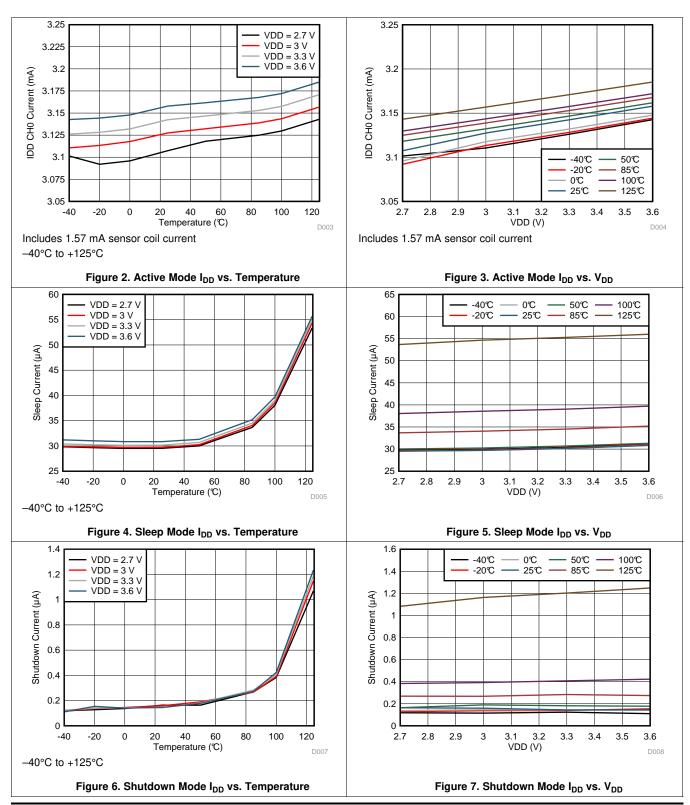

#### 7.8 Typical Characteristics

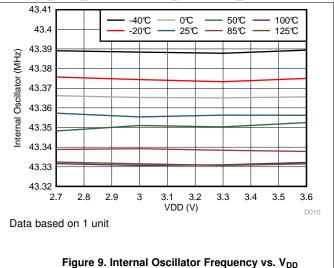

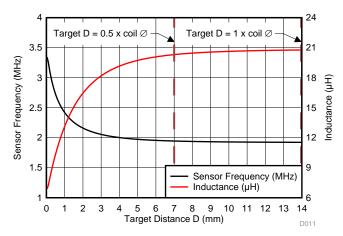

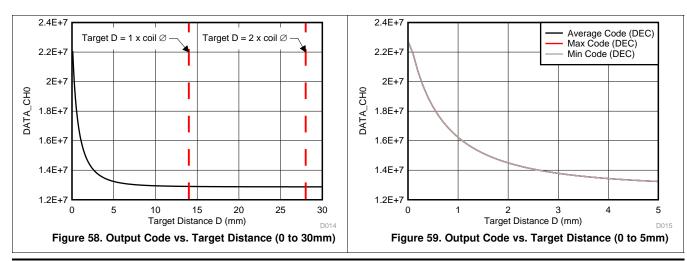

Common test conditions (unless specified otherwise): Sensor inductor: 2 layer, 32 turns/layer, 14 mm diameter, PCB inductor with L=19.4  $\mu$ H, R<sub>P</sub>=5.7 k $\Omega$  at 2 MHz; Sensor capacitor: 330 pF 1% COG/NP0; Target: Aluminum, 1.5mm thickness; Channel = Channel 0 (continuous mode); CLKIN = 40 MHz, CHx\_FIN\_DIVIDER = 0x1, CHx\_FREF\_DIVIDER = 0x001, CH0\_RCOUNT = 0xFFFF, SETTLECOUNT\_CH0 = 0x0100, RP\_OVERRIDE = 1, AUTO\_AMP\_DIS = 1, DRIVE\_CURRENT\_CH0 = 0x9800

www.ti.com

# **Typical Characteristics (continued)**

Common test conditions (unless specified otherwise): Sensor inductor: 2 layer, 32 turns/layer, 14 mm diameter, PCB inductor with L=19.4  $\mu$ H, R<sub>P</sub>=5.7 k $\Omega$  at 2 MHz; Sensor capacitor: 330 pF 1% COG/NP0; Target: Aluminum, 1.5mm thickness; Channel = Channel 0 (continuous mode); CLKIN = 40 MHz, CHx\_FIN\_DIVIDER = 0x1, CHx\_FREF\_DIVIDER = 0x001, CH0\_RCOUNT = 0xFFFF, SETTLECOUNT\_CH0 = 0x0100, RP\_OVERRIDE = 1, AUTO\_AMP\_DIS = 1, DRIVE\_CURRENT\_CH0 = 0x9800

# TEXAS INSTRUMENTS

#### 8 Detailed Description

#### 8.1 Overview

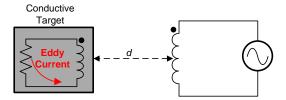

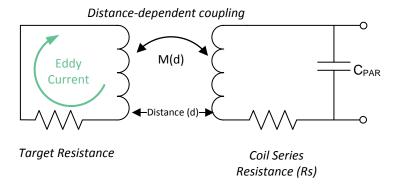

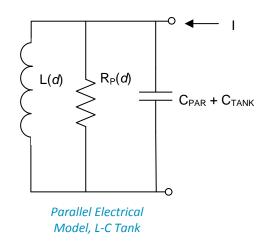

Conductive objects brought in contact with an AC electromagnetic (EM) field will induce field changes that can be detected using a sensor such as an inductor. Conveniently, an inductor, along with a capacitor, can be used to construct an L-C resonator, also known as an L-C tank, which can be used to produce an EM field. In the case of an L-C tank, the effect of the field disturbance is an apparent shift in the inductance of the sensor, which can be observed as a shift in the resonant frequency. Using this principle, the LDC1612/1614 is an inductance-to-digital converter (LDC) that measures the oscillation frequency of an LC resonator. The device outputs a digital value that is proportional to frequency. This frequency measurement can be converted to an equivalent inductance.

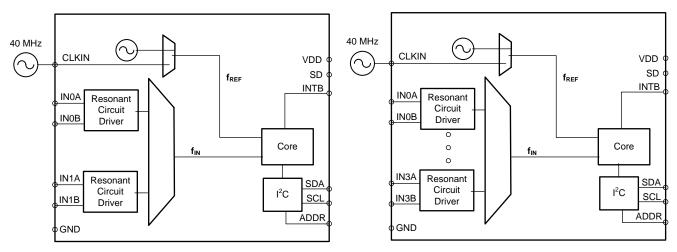

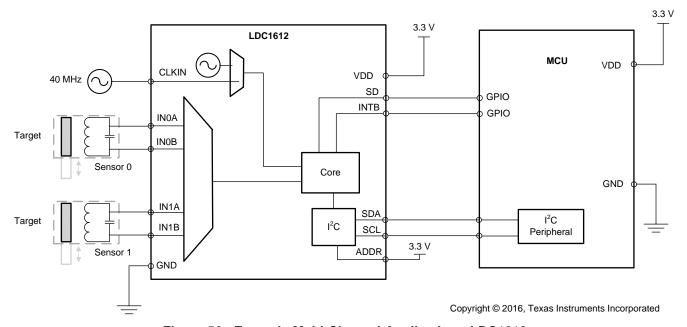

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 10. Block Diagrams for the LDC1612 (Left) and LDC1614 (Right)

The LDC1612/LDC1614 is composed of front-end resonant circuit drivers, followed by a multiplexer that sequences through the active channels, connecting them to the core that measures and digitizes the sensor frequency (f<sub>SENSOR</sub>). The core uses a reference frequency (f<sub>REF</sub>) to measure the sensor frequency. f<sub>REF</sub> is derived from either an internal reference clock (oscillator), or an externally supplied clock. The digitized output for each channel is proportional to the ratio of f<sub>SENSOR</sub>/f<sub>REF</sub>. The I2C interface is used to support device configuration and to transmit the digitized frequency values to a host processor. The LDC can be placed in shutdown mode, saving current, using the SD pin. The INTB pin may be configured to notify the host of changes in system status.

#### 8.3 Feature Description

#### 8.3.1 Clocking Architecture

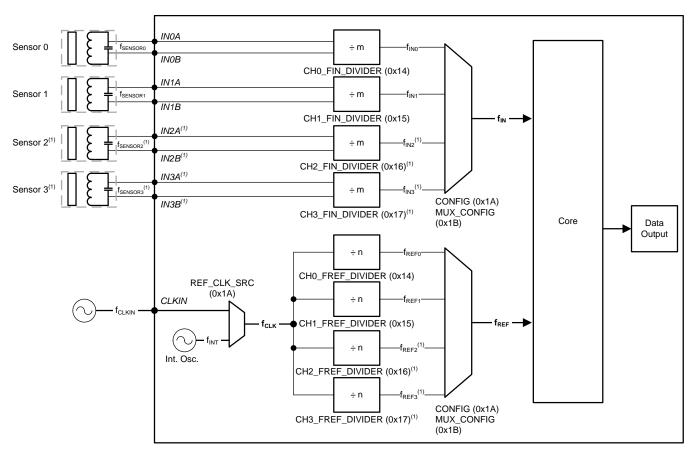

Figure 11 shows the clock dividers and multiplexers of the LDC.

#### **Feature Description (continued)**

Copyright © 2016, Texas Instruments Incorporated

Figure 11. Clocking Diagram

#### (1) LDC1614 only

In Figure 11, the key clocks are  $f_{IN}$ ,  $f_{REF}$ , and  $f_{CLK}$ .  $f_{CLK}$  is selected from either the internal clock source or external clock source (CLKIN). The frequency measurement reference clock,  $f_{REF}$ , is derived from the  $f_{CLK}$  source. TI recommends that precision applications use an external master clock that offers the stability and accuracy requirements needed for the application. The internal oscillator may be used in applications that require low cost and do not require high precision. The  $f_{INx}$  clock is derived from sensor frequency for a channel x,  $f_{SENSORx}$ .  $f_{REFx}$  and  $f_{INx}$  must meet the requirements listed in Table 1, depending on whether  $f_{CLK}$  (master clock) is the internal or external clock.

**Table 1. Clock Configuration Requirements**

| MODE <sup>(1)</sup> | CLKIN SOURCE                | VALID f <sub>REFx</sub><br>RANGE (MHz) | VALID f <sub>INx</sub><br>RANGE | SET<br>CHx_FIN_DIVIDE<br>R to | SET<br>CHx_SETTLECO<br>UNT to | SET<br>CHx_RCOUNT to |

|---------------------|-----------------------------|----------------------------------------|---------------------------------|-------------------------------|-------------------------------|----------------------|

| Multi-Channel       | Internal                    | $f_{REFx} < 55$                        |                                 |                               |                               |                      |

|                     | External                    | $f_{REFx} < 40$                        | < f <sub>BEFx</sub> /4          | ≥ b0001 <sup>(2)</sup>        | > 3                           | > 8                  |

| Single-Channel      | Either external or internal | $f_{REFx} < 35$                        | \ 'REFX''                       | _ 50001                       | 7 0                           | 7 0                  |

(1) Channels 2 and 3 are only available for LDC1614

(2) If  $f_{SENSOR} \ge 8.75$  MHz, then CHx\_FIN\_DIVIDER must be  $\ge 2$

SNOSCZ8 – APRIL 2016 www.ti.com

Table 2 shows the clock configuration registers for all channels.

**Table 2. Clock Configuration Registers**

| CHANNEL <sup>(1)</sup> | CLOCK                                     | REGISTER                          | FIELD [ BIT(S) ]        | VALUE                                                                                                       |

|------------------------|-------------------------------------------|-----------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------|

| All                    | f <sub>CLK</sub> = Master<br>Clock Source | CONFIG, addr<br>0x1A              | REF_CLK_SRC [9]         | b0 = internal oscillator is used as the master clock b1 = external clock source is used as the master clock |

| 0                      | f <sub>REF0</sub>                         | CLOCK_DIVIDER<br>S_CH0, addr 0x14 | CH0_FREF_DIVIDER [9:0]  | f <sub>REF0</sub> = f <sub>CLK</sub> / CH0_FREF_DIVIDER                                                     |

| 1                      | f <sub>REF1</sub>                         | CLOCK_DIVIDER<br>S_CH1, addr 0x15 | CH1_FREF_DIVIDER [9:0]  | f <sub>REF1</sub> = f <sub>CLK</sub> / CH1_FREF_DIVIDER                                                     |

| 2                      | f <sub>REF2</sub>                         | CLOCK_DIVIDER<br>S_CH2, addr 0x16 | CH2_FREF_DIVIDER [9:0]  | f <sub>REF2</sub> = f <sub>CLK</sub> / CH2_FREF_DIVIDER                                                     |

| 3                      | f <sub>REF3</sub>                         | CLOCK_DIVIDER<br>S_CH3, addr 0x17 | CH3_FREF_DIVIDER [9:0]  | f <sub>REF3</sub> = f <sub>CLK</sub> / CH3_FREF_DIVIDER                                                     |

| 0                      | f <sub>INO</sub>                          | CLOCK_DIVIDER<br>S_CH0, addr 0x14 | CH0_FIN_DIVIDER [15:12] | f <sub>IN0</sub> = f <sub>SENSOR0</sub> / CH0_FIN_DIVIDER                                                   |

| 1                      | f <sub>IN1</sub>                          | CLOCK_DIVIDER<br>S_CH1, addr 0x15 | CH1_FIN_DIVIDER [15:12] | f <sub>IN1</sub> = f <sub>SENSOR1</sub> / CH1_FIN_DIVIDER                                                   |

| 2                      | f <sub>IN2</sub>                          | CLOCK_DIVIDER<br>S_CH2, addr 0x16 | CH2_FIN_DIVIDER [15:12] | f <sub>IN2</sub> = f <sub>SENSOR2</sub> / CH2_FIN_DIVIDER                                                   |

| 3                      | f <sub>IN3</sub>                          | CLOCK_DIVIDER<br>S_CH3, addr 0x17 | CH3_FIN_DIVIDER [15:12] | f <sub>IN3</sub> = f <sub>SENSOR3</sub> / CH3_FIN_DIVIDER                                                   |

<sup>(1)</sup> Channels 2 and 3 are only available for LDC1614

#### 8.3.2 Multi-Channel and Single Channel Operation

The multi-channel package of the LDC enables the user to save board space and support flexible system design. For example, temperature drift can often cause a shift in component values, resulting in a shift in resonant frequency of the sensor. Using a 2nd sensor as a reference provides the capability to cancel out a temperature shift. When operated in multi-channel mode, the LDC sequentially samples the active channels. In single channel mode, the LDC samples a single channel, which is selectable. Table 3 shows the registers and values that are used to configure either multi-channel or single channel modes.

**Table 3. Single and Multi-Channel Configuration Registers**

| MODE           | REGISTER             | FIELD [ BIT(S) ]     | VALUE <sup>(1)</sup>                                    |

|----------------|----------------------|----------------------|---------------------------------------------------------|

|                | CONFIG. adds 0.44    |                      | 00 = chan 0                                             |

|                |                      | ACTIVE CHAN [15:14]  | 01 = chan 1                                             |

| Single channel | CONFIG, addr 0x1A    | ACTIVE_CHAIN [15.14] | 10 = chan 2                                             |

|                |                      |                      | 11 = chan 3                                             |

|                | MUX_CONFIG addr 0x1B | AUTOSCAN_EN [15]     | 0 = continuous conversion on a single channel (default) |

|                | MUX_CONFIG addr 0x1B | AUTOSCAN_EN [15]     | 1 = continuous conversion on multiple channels          |

| Multi-channel  |                      |                      | 00 = Ch0, Ch 1                                          |

|                | MUX_CONFIG addr 0x1B | RR_SEQUENCE [14:13]  | 01 = Ch0, Ch 1, Ch 2                                    |

|                |                      |                      | 10 = Ch0, CH1, Ch2, Ch3                                 |

<sup>(1)</sup> Channels 2 and 3 are only available for LDC1614

The digitized sensor measurement for each channel (DATAx) represents the ratio of the sensor frequency to the reference frequency:

$$DATAx/2^{28} = f_{SENSORx}/f_{REFx}$$

(1)

The sensor frequency can be calculated from:

$$f_{\text{sensor}} = \frac{\text{DATAx} * f_{\text{REFx}}}{2^{28}}$$

(2)

Table 4 shows the registers that contain the fixed point sample values for each channel.

#### Table 4. LDC1614/1314 Sample Data Registers

| CHANNEL <sup>(1)</sup> | REGISTER <sup>(2)</sup> | FIELD NAME [ BITS(S) ] | VALUE <sup>(3)(4)</sup>                 |

|------------------------|-------------------------|------------------------|-----------------------------------------|

| 0                      | DATA_MSB_CH0, addr 0x00 | DATA0 [11:0]           | 12 MSBs of the 28 bit result            |

|                        | DATA_LSB_CH0, addr 0x01 | DATA0 [15:0]           | 16 LSBs of the 28 bit conversion result |

| 1                      | DATA_MSB_CH1, addr 0x02 | DATA1 [11:0]           | 12 MSBs of the 28 bit result            |

|                        | DATA_LSB_CH1, addr 0x03 | DATA1 [15:0]           | 16 LSBs of the 28 bit conversion result |

| 2                      | DATA_MSB_CH2, addr 0x04 | DATA2 [11:0]           | 12 MSBs of the 28 bit result            |

|                        | DATA_LSB_CH2, addr 0x05 | DATA2 [15:0]           | 16 LSBs of the 28 bit conversion result |

| 3                      | DATA_MSB_CH3, addr 0x06 | DATA3 [11:0]           | 12 MSBs of the 28 bit result            |

|                        | DATA_LSB_CH3, addr 0x07 | DATA3 [15:0]           | 16 LSBs of the 28 bit conversion result |

- Channels 2 and 3 available only in LDC1614.

- (2) The DATA\_MSB\_ CHx.DATAx register must always be read first, followed by the DATA\_LSB\_ CHx.DATAx register of the same channel to ensure data coherency.

- (3) A DATA value of 0x0000000 = under range for LDC1612/LDC1614

- (4) A DATA value of 0xFFFFFFF = over range for LDC1612/LDC1614

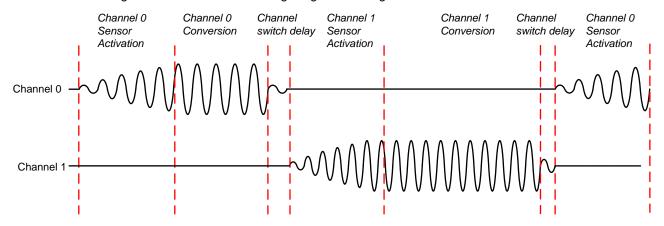

When the LDC sequences through the channels in multi-channel mode, the dwell time interval for each channel is the sum of 3 parts: sensor activation time + conversion time + channel switch delay.

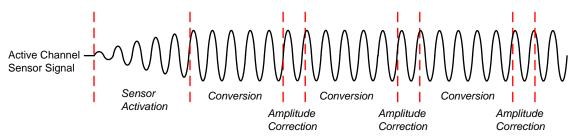

The sensor activation time is the amount of settling time required for the sensor oscillation to stabilize, as shown in Figure 12. The settling wait time is programmable and should be set to a value that is long enough to allow stable oscillation. The settling wait time for channel x is given by:

$$t_{Sx} = (CHX\_SETTLECOUNT \times 16)/f_{REFx}$$

(3)

Table 5 shows the registers and values for configuring the settling time for each channel.

Figure 12. Multi-channel Mode Sequencing

Figure 13. Single-channel Mode Sequencing

#### **Table 5. Settling Time Register Configuration**

| CHANNEL <sup>(1)</sup> | REGISTER                   | FIELD                  | CONVERSION TIME <sup>(2)</sup>         |

|------------------------|----------------------------|------------------------|----------------------------------------|

| 0                      | SETTLECOUNT_CH0, addr 0x10 | CH0_SETTLECOUNT (15:0) | (CH0_SETTLECOUNT*16)/f <sub>REF0</sub> |

| 1                      | SETTLECOUNT_CH1, addr 0x11 | CH1_SETTLECOUNT (15:0) | (CH1_SETTLECOUNT*16)/f <sub>REF1</sub> |

| 2                      | SETTLECOUNT_CH2, addr 0x12 | CH2_SETTLECOUNT (15:0) | (CH2_SETTLECOUNT*16)/f <sub>REF2</sub> |

| 3                      | SETTLECOUNT_CH3, addr 0x13 | CH3_SETTLECOUNT (15:0) | (CH3_SETTLECOUNT*16)/f <sub>REF3</sub> |

- (1) Channels 2 and 3 are available only in the LDC1614.

- (2) f<sub>REFx</sub> is the reference frequency configured for the channel.

#### The SETTLECOUNT for any channel x must satisfy:

CHx\_SETTLECOUNT ≥ Q<sub>SENSORx</sub> × f<sub>REFx</sub> / (16 × f<sub>SENSORx</sub>)

#### where

- $f_{SENSORx}$  = Frequency of the Sensor on Channel x

- f<sub>REFx</sub> = Reference frequency for Channel x

- Q<sub>SENSOBx</sub> = Quality factor of the sensor on Channel x, where Q can be calculated by:

$$Q = R_{P} \sqrt{\frac{C}{L}}$$

(5)

Round the result to the next highest integer (for example, if Equation 4 recommends a minimum value of 6.08, program the register to 7 or higher).

L, R<sub>P</sub> and C values can be obtained by using Texas Instrument's WEBENCH® for the coil design.

The conversion time represents the number of reference clock cycles used to measure the sensor frequency. It is set by the CHx RCOUNT register for the channel. The conversion time for any channel x is:

$$t_{Cx} = (CHx RCOUNT \times 16 + 4) / f_{RFFx}$$

(6)

The reference count value must be chosen to support the required number of effective bits (ENOB). For details, refer to the application note Optimizing L Measurement Resolution for the LDC161x and LDC1101.

Table 6. Conversion Time Configuration Registers, Channels 0 - 3(1)

| CHANNEL | REGISTER              | FIELD [ BIT(S) ]  | CONVERSION TIME                   |

|---------|-----------------------|-------------------|-----------------------------------|

| 0       | RCOUNT_CH0, addr 0x08 | CH0_RCOUNT (15:0) | (CH0_RCOUNT*16)/f <sub>REF0</sub> |

| 1       | RCOUNT_CH1, addr 0x09 | CH1_RCOUNT (15:0) | (CH1_RCOUNT*16)/f <sub>REF1</sub> |

| 2       | RCOUNT_CH2, addr 0x0A | CH2_RCOUNT (15:0) | (CH2_RCOUNT*16)/f <sub>REF2</sub> |

| 3       | RCOUNT_CH3, addr 0x0B | CH3_RCOUNT (15:0) | (CH3_RCOUNT*16)/f <sub>REF3</sub> |

<sup>(1)</sup> Channels 2 and 3 are available only for LDC1614.

The typical channel switch delay time between the end of conversion and the beginning of sensor activation of the subsequent channel is:

Channel Switch Delay =

$$692 \text{ ns} + 5 / f_{\text{ref}}$$

(7)

The deterministic conversion time of the LDC allows data polling at a fixed interval. A data ready flag (DRDY) is also available for interrupt driven system designs (see the STATUS register description in *Register Maps*).

An offset value may be subtracted from each DATA value to compensate for a frequency offset or maximize the dynamic range of the sample data. The offset values should be  $< f_{SENSORx\_MIN} / f_{REFx}$ . Otherwise, the offset might be so large that it masks the LSBs which are changing.

Submit Documentation Feedback

**STRUMENTS**

(8)

#### **Table 7. Frequency Offset Registers**

| CHANNEL | REGISTER              | FIELD [ BIT(S) ]    | VALUE                                                                     |

|---------|-----------------------|---------------------|---------------------------------------------------------------------------|

| 0       | OFFSET_CH0, addr 0x0C | CH0_OFFSET [ 15:0 ] | f <sub>OFFSET0</sub> = CH0_OFFSET * (f <sub>REF0</sub> /2 <sup>16</sup> ) |

| 1       | OFFSET_CH1, addr 0x0D | CH1_OFFSET [ 15:0 ] | f <sub>OFFSET1</sub> = CH1_OFFSET * (f <sub>REF1</sub> /2 <sup>16</sup> ) |

| 2       | OFFSET_CH2, addr 0x0E | CH2_OFFSET [ 15:0 ] | f <sub>OFFSET2</sub> = CH2_OFFSET * (f <sub>REF2</sub> /2 <sup>16</sup> ) |

| 3       | OFFSET_CH3, addr 0x0F | CH3_OFFSET [ 15:0 ] | f <sub>OFFSET3</sub> = CH3_OFFSET * (f <sub>REF3</sub> /2 <sup>16</sup> ) |

The sensor frequency can be determined by:

$$f_{\mathsf{SENSORx}} = \mathsf{CHx\_FIN\_DIVIDER} * f_{\mathsf{REFx}} \bigg( \frac{\mathsf{DATAx}}{2^{28}} + \frac{\mathsf{CHx\_OFFSET}}{2^{16}} \bigg)$$

#### where

- DATAx = Conversion result from the DATA CHx register

- CHx OFFSET = Offset value set in the OFFSET CHx register

#### 8.3.3 Current Drive Control Registers

The registers listed in Table 8 are used to control the sensor drive current. The recommendations listed in the last column of Table 8 should be followed.

Auto-calibration mode is used to determine the optimal sensor drive current for a fixed sensor design. This mode should only be used during system prototyping.

The auto-amplitude correction attempts to maintain the sensor oscillation amplitude between 1.2V and 1.8V by adjusting the sensor drive current between conversions. When auto-amplitude correction is enabled, the output data may show non-monotonic behavior due to an adjustment in drive current. Auto-amplitude correction is only recommended for low-precision applications.

A high sensor current drive mode can be enabled to drive sensor coils with > 1.5mA on channel 0, only in single channel mode. This feature can be used when the sensor  $R_P$  is lower than  $1k\Omega$ . Set the HIGH\_CURRENT\_DRV register bit to b1 to enable this mode.

**Table 8. Current Drive Control Registers**

| CHANNEL <sup>(1)</sup> | REGISTER                     | FIELD [ BIT(S) ]         | VALUE                                                                                                                                                           |

|------------------------|------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | CONFIG, addr 0x1A            | SENSOR_ACTIVATE_SEL [11] | Sets current drive for sensor activation.<br>Recommended value is b0 (Full Current<br>mode).                                                                    |

| All                    |                              | RP_OVERRIDE_EN [12]      | Set to b1 for normal operation (RP over ride enabled)                                                                                                           |

|                        |                              | AUTO_AMP_DIS [10]        | Disables Automatic amplitude correction.<br>Set to b1 for normal operation (disabled)                                                                           |

| 0                      | CONFIG, addr 0x1A            | HIGH_CURRENT_DRV [6]     | b0 = normal current drive (1.5 mA)<br>b1 = Increased current drive (> 1.5 mA)<br>for Ch 0 in single channel mode only.<br>Cannot be used in multi-channel mode. |

| 0                      | DRIVE_CURRENT_CH0, addr 0x1E | CH0_IDRIVE [15:11]       | Drive current used during the settling and conversion time for Ch. 0 (auto-amplitude correction must be disabled and RP over ride=1)                            |

|                        |                              | CH0_INIT_IDRIVE [10:6]   | Initial drive current stored during auto-<br>calibration. Not used for normal operation.                                                                        |

| 1                      | DRIVE_CURRENT_CH1, addr 0x1F | CH1_IDRIVE [15:11]       | Drive current used during the settling and conversion time for Ch. 1 (auto-amplitude correction must be disabled and RP over ride=1)                            |

|                        |                              | CH1_INIT_IDRIVE [10:6]   | Initial drive current stored during auto-<br>calibration. Not used for normal operation.                                                                        |

(1) Channels 2 and 3 are available for LDC1614 only.

**Table 8. Current Drive Control Registers (continued)**

| CHANNEL <sup>(1)</sup> | REGISTER                     | FIELD [ BIT(S) ]       | VALUE                                                                                                                                |

|------------------------|------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 2                      | DRIVE_CURRENT_CH2, addr 0x20 | CH2_IDRIVE [15:11]     | Drive current used during the settling and conversion time for Ch. 2 (auto-amplitude correction must be disabled and RP over ride=1) |

|                        |                              | CH2_INIT_IDRIVE [10:6] | Initial drive current stored during auto-<br>calibration. Not used for normal operation.                                             |

| 3                      | DRIVE_CURRENT_CH3, addr 0x21 | CH3_IDRIVE [15:11]     | Drive current used during the settling and conversion time for Ch. 3 (auto-amplitude correction must be disabled and RP over ride=1) |

|                        |                              | CH3_INIT_IDRIVE [10:6] | Initial drive current stored during auto-<br>calibration. Not used for normal operation.                                             |

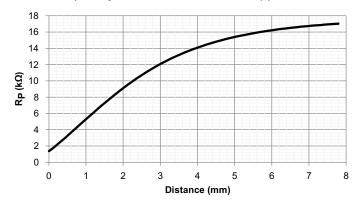

If the  $R_P$  value of the sensor attached to channel x is known, Table 9 can be used to select the 5-bit value to be programmed into the CHx\_IDRIVE field for the channel. If the measured  $R_P$  (at maximum spacing between the sensor and the target) falls between two of the table values, use the current drive value associated with the lower  $R_P$  from Table 9. All channels that use an identical sensor/target configuration should use the same IDRIVE value.

Table 9. CHx\_IDRIVE Values for Maximum Measured Rp.

| MEASURED R <sub>P</sub> (kΩ) | CHx_IDRIVE REGISTER FIELD VALUE,<br>BINARY (BITS [15:11] ) | NOMINAL CURRENT (μA) |

|------------------------------|------------------------------------------------------------|----------------------|

| 90.0                         | b00000                                                     | 16                   |

| 77.6                         | b00001                                                     | 18                   |

| 66.9                         | b00010                                                     | 20                   |

| 57.6                         | b00011                                                     | 23                   |

| 49.7                         | b00100                                                     | 28                   |

| 42.8                         | b00101                                                     | 32                   |

| 36.9                         | b00110                                                     | 40                   |

| 31.8                         | b00111                                                     | 46                   |

| 27.4                         | b01000                                                     | 52                   |

| 23.3                         | b01001                                                     | 59                   |

| 20.4                         | b01010                                                     | 72                   |

| 17.6                         | b01011                                                     | 82                   |

| 15.1                         | b01100                                                     | 95                   |

| 13.0                         | b01101                                                     | 110                  |

| 11.2                         | b01110                                                     | 127                  |

| 9.7                          | b01111                                                     | 146                  |

| 8.4                          | b10000                                                     | 169                  |

| 7.2                          | b10001                                                     | 195                  |

| 6.2                          | b10010                                                     | 212                  |

| 5.4                          | b10011                                                     | 244                  |

| 4.6                          | b10100                                                     | 297                  |

| 4.0                          | b10101                                                     | 342                  |

| 3.4                          | b10110                                                     | 424                  |

| 3.0                          | b10111                                                     | 489                  |

| 2.5                          | b11000                                                     | 551                  |

| 2.2                          | b11001                                                     | 635                  |

| 1.9                          | b11010                                                     | 763                  |

| 1.6                          | b11011                                                     | 880                  |

| 1.4                          | b11100                                                     | 1017                 |

#### Table 9. CHx IDRIVE Values for Maximum Measured Rp. (continued)

| MEASURED R <sub>P</sub> (kΩ) | CHx_IDRIVE REGISTER FIELD VALUE,<br>BINARY (BITS [15:11] ) | NOMINAL CURRENT (μA) |

|------------------------------|------------------------------------------------------------|----------------------|

| 1.2                          | b11101                                                     | 1173                 |

| 1.0                          | b11110                                                     | 1355                 |

| 0.9                          | b11111                                                     | 1563                 |

If the  $R_P$  is not known, the following steps for auto-calibration can be used to configure the needed drive current, either during system prototyping, or during normal startup if feasible:

- 1. Set target at the maximum planned operating distance from the sensor.

- 2. Place the device into SLEEP mode by setting CONFIG.SLEEP MODE EN to b0.

- 3. Program the desired values of SETTLECOUNT and RCOUNT values for the channel.

- 4. Enable auto-calibration by setting RP\_OVERDRIVE\_EN to b0.

- 5. Take the device out of SLEEP mode by setting CONFIG.SLEEP MODE EN to b1.

- 6. Allow the device to perform at least one measurement, with the target stable (fixed) at the maximum operating range.

- 7. Read the channel current drive value from the appropriate DRIVE\_CURRENT\_CHx register (addresses 0x1e, 0x1f, 0x20, or 0x21), in the CHx INIT DRIVE field (bits 10:6). Save this value.

- 8. During startup for normal operating mode, write the value saved from the CHx\_INIT\_DRIVE bit field into the Chx\_IDRIVE bit field (bits 15:11).

- 9. During normal operating mode, the RP OVERRIDE EN must set to b1 to force the fixed current drive.

If the current drive results in the oscillation amplitude greater than 1.8V, the internal ESD clamping circuit will become active. This may cause the sensor frequency to shift so that the output values no longer represent a valid system state. If the current drive is set at a lower value, the SNR performance of the system will decrease, and at near zero target range, oscillations may completely stop, and the output sample values will be all zeroes.

www.ti.com

#### 8.3.4 Device Status Registers

The registers listed in Table 10 may be used to read device status.

Table 10. Status Registers

| CHANNEL <sup>(1)</sup> | REGISTER                | FIELDS [ BIT(S) ]                                                           | VALUES                                                                                       |

|------------------------|-------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| All                    | STATUS, addr 0x18       | 12 fields are available that contain various status bits [ 15:0 ]           | Refer to Register Maps section for a description of the individual status bits.              |

| All                    | ERROR_CONFIG, addr 0x19 | 12 fields are available that are used to configure error reporting [ 15:0 ] | Refer to Register Maps section for a description of the individual error configuration bits. |

<sup>(1)</sup> Channels 2 and 3 are available for LDC1614 only.

See the STATUS and ERROR\_CONFIG register description in the Register Map section. These registers can be configured to trigger an interrupt on the INTB pin for certain events. The following conditions must be met:

- 1. The error or status register must be unmasked by enabling the appropriate register bit in the ERROR CONFIG register

- 2. The INTB function must be enabled by setting CONFIG.INTB DIS to 0

When a bit field in the STATUS register is set, the entire STATUS register content is held until read or until the DATA\_MSB\_CHx register is read. Reading also de-asserts INTB.

Interrupts are cleared by one of the following events:

- 1. Entering Sleep Mode

- 2. Power-on reset (POR)

- 3. Device enters Shutdown Mode (SD is asserted)

- 4. S/W reset

- I2C read of the STATUS register: Reading the STATUS register will clear any error status bit set in STATUS along with the ERR\_CHAN field and de-assert INTB

Setting register CONFIG.INTB DIS to b1 disables the INTB function and holds the INTB pin high.

#### 8.3.5 Input Deglitch Filter

The input deglitch filter suppresses EMI and ringing above the sensor frequency. It does not impact the conversion result as long as its bandwidth is configured to be above the maximum sensor frequency. The input deglitch filter can be configured in MUX\_CONFIG.DEGLITCH register field as shown in Table 11. For optimal performance, TI recommends to select the lowest setting that exceeds the sensor oscillation frequency. For example, if the maximum sensor frequency is 2.0 MHz, choose MUX\_CONFIG.DEGLITCH = b100 (3.3 MHz).

Table 11. Input deglitch filter register

| CHANNEL <sup>(1)</sup> | MUX_CONFIG.DEGLITCH REGISTER VALUE | DEGLITCH FREQEUNCY |

|------------------------|------------------------------------|--------------------|

| ALL                    | 001                                | 1 MHz              |

| ALL                    | 100                                | 3.3 MHz            |

| ALL                    | 101                                | 10 MHz             |

| ALL                    | 011                                | 33 MHz             |

(1) Channels 2 and 3 are available for LDC1614 only.

#### 8.4 Device Functional Modes

#### 8.4.1 Startup Mode

When the LDC powers up, it enters into Sleep Mode and will wait for configuration. Once the device is configured, exit Sleep Mode by setting CONFIG.SLEEP MODE EN to b0.

TI recommends to configure the LDC while in Sleep Mode. If a setting on the LDC needs to be changed, return the device to Sleep Mode, change the appropriate register, and then exit Sleep Mode.

#### 8.4.2 Normal (Conversion) Mode

When operating in the normal (conversion) mode, the LDC is periodically sampling the frequency of the sensor(s) and generating sample outputs for the active channel(s).

#### 8.4.3 Sleep Mode

Sleep Mode is entered by setting the CONFIG.SLEEP\_MODE\_EN register field to 1. While in this mode, the device configuration is maintained. To exit Sleep Mode, set the CONFIG.SLEEP\_MODE\_EN register field to 0. After setting CONFIG.SLEEP\_MODE\_EN to b0, sensor activation for the first conversion will begin after 16,384 f<sub>INT</sub> clock cycles. While in Sleep Mode the I2C interface is functional so that register reads and writes can be performed. While in Sleep Mode, no conversions are performed. In addition, entering Sleep Mode will clear conversion results, any error condition and de-assert the INTB pin.

#### 8.4.4 Shutdown Mode

When the SD pin is set to high, the LDC will enter Shutdown Mode. Shutdown Mode is the lowest power state. To exit Shutdown Mode, set the SD pin to low. Entering Shutdown Mode will return all registers to their default state.

While in Shutdown Mode, no conversions are performed. In addition, entering Shutdown Mode will clear any error condition and de-assert the INTB pin. While the device is in Shutdown Mode, is not possible to read to or write from the device via the I2C interface.

#### 8.4.4.1 Reset

The LDC can be reset by writing to RESET\_DEV.RESET\_DEV. Any active conversion will stop and all register values will return to their default value. This register bit will always return 0b when read.

#### 8.5 Programming

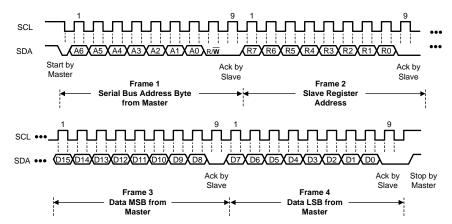

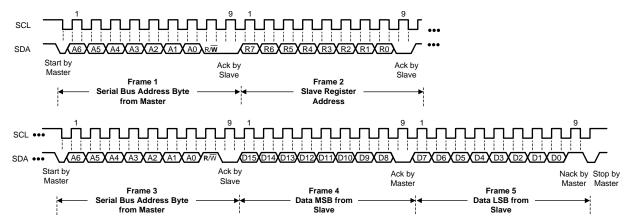

The LDC device uses an I2C interface to access control and data registers.

#### 8.5.1 I2C Interface Specifications

The LDC uses an extended start sequence with I2C for register access. The maximum speed of the I2C interface is 400kbit/s. This sequence follows the standard I2C 7bit slave address followed by an 8bit pointer register byte to set the register address. When the ADDR pin is set low, the LDC I2C address is 0x2A; when the ADDR pin is set high, the LDC I2C address is 0x2B. The ADDR pin must not change state after the LDC exits Shutdown Mode.

Copyright © 2016, Texas Instruments Incorporated

#### **Programming (continued)**

Figure 14. I2C Write Register Sequence

Figure 15. I2C Read Register Sequence

20

### 8.6 Register Maps

### 8.6.1 Register List

Fields indicated with Reserved must be written only with indicated values, otherwise improper device operation may occur. The R/W column indicates the Read-Write status of the corresponding field. A 'R/W' entry indicates read and write capability, a 'R' indicates read-only, and a 'W' indicates write-only.

Figure 16. Register List

| ADDRESS | NAME                   | DEFAULT VALUE | DESCRIPTION                                                                               |

|---------|------------------------|---------------|-------------------------------------------------------------------------------------------|

| 0x00    | DATA_MSB_CH0           | 0x0000        | Channel 0 MSB Conversion Result and Error Status                                          |

| 0x01    | DATA_LSB_CH0           | 0x0000        | Channel 0 LSB Conversion Result. Must be read after Register address 0x00.                |

| 0x02    | DATA_MSB_CH1           | 0x0000        | Channel 1 MSB Conversion Result and Error Status.                                         |

| 0x03    | DATA_LSB_CH1           | 0x0000        | Channel 1 LSB Conversion Result. Must be read after Register address 0x02.                |

| 0x04    | DATA_MSB_CH2           | 0x0000        | Channel 2 MSB Conversion Result and Error Status. (LDC1614 only)                          |

| 0x05    | DATA_LSB_CH2           | 0x0000        | Channel 2 LSB Conversion Result. Must be read after Register address 0x04.(LDC1614 only)  |

| 0x06    | DATA_MSB_CH3           | 0x0000        | Channel 3 MSB Conversion Result and Error Status. (LDC1614 only)                          |

| 0x07    | DATA_LSB_CH3           | 0x0000        | Channel 3 LSB Conversion Result. Must be read after Register address 0x06. (LDC1614 only) |

| 80x0    | RCOUNT_CH0             | 0x0080        | Reference Count setting for Channel 0                                                     |

| 0x09    | RCOUNT_CH1             | 0x0080        | Reference Count setting for Channel 1                                                     |

| 0x0A    | RCOUNT_CH2             | 0x0080        | Reference Count setting for Channel 2. (LDC1614 only)                                     |

| 0x0B    | RCOUNT_CH3             | 0x0080        | Reference Count setting for Channel 3.(LDC1614 only)                                      |

| 0x0C    | OFFSET_CH0             | 0x0000        | Offset value for Channel 0                                                                |

| 0x0D    | OFFSET_CH1             | 0x0000        | Offset value for Channel 1                                                                |

| 0x0E    | OFFSET_CH2             | 0x0000        | Offset value for Channel 2 (LDC1614 only)                                                 |

| 0x0F    | OFFSET_CH3             | 0x0000        | Offset value for Channel 3 (LDC1614 only)                                                 |

| 0x10    | SETTLECOUNT_CH0        | 0x0000        | Channel 0 Settling Reference Count                                                        |

| 0x11    | SETTLECOUNT_CH1        | 0x0000        | Channel 1 Settling Reference Count                                                        |

| 0x12    | SETTLECOUNT_CH2        | 0x0000        | Channel 2 Settling Reference Count (LDC1614 only)                                         |

| 0x13    | SETTLECOUNT_CH3        | 0x0000        | Channel 3 Settling Reference Count (LDC1614 only)                                         |

| 0x14    | CLOCK_DIVIDERS_C<br>H0 | 0x0000        | Reference and Sensor Divider settings for Channel 0                                       |

| 0x15    | CLOCK_DIVIDERS_C<br>H1 | 0x0000        | Reference and Sensor Divider settings for Channel 1                                       |

| 0x16    | CLOCK_DIVIDERS_C<br>H2 | 0x0000        | Reference and Sensor Divider settings for Channel 2 (LDC1614 only)                        |

| 0x17    | CLOCK_DIVIDERS_C<br>H3 | 0x0000        | Reference and Sensor Divider settings for Channel 3 (LDC1614 only)                        |

| 0x18    | STATUS                 | 0x0000        | Device Status Report                                                                      |

| 0x19    | ERROR_CONFIG           | 0x0000        | Error Reporting Configuration                                                             |

| 0x1A    | CONFIG                 | 0x2801        | Conversion Configuration                                                                  |

| 0x1B    | MUX_CONFIG             | 0x020F        | Channel Multiplexing Configuration                                                        |

| 0x1C    | RESET_DEV              | 0x0000        | Reset Device                                                                              |

| 0x1E    | DRIVE_CURRENT_CH       | 0x0000        | Channel 0 sensor current drive configuration                                              |

| 0x1F    | DRIVE_CURRENT_CH       | 0x0000        | Channel 1 sensor current drive configuration                                              |

| 0x20    | DRIVE_CURRENT_CH 2     | 0x0000        | Channel 2 sensor current drive configuration (LDC1614 only)                               |

| 0x21    | DRIVE_CURRENT_CH       | 0x0000        | Channel 3 sensor current drive configuration (LDC1614 only)                               |

| 0x7E    | MANUFACTURER_ID        | 0x5449        | Manufacturer ID                                                                           |

| 0x7F    | DEVICE_ID              | 0x3055        | Device ID                                                                                 |

# SNOSCZ8 – APRIL 2016 www.ti.com

#### 8.6.2 Address 0x00, DATA MSB CH0

#### Figure 17. Address 0x00, DATA\_MSB\_CH0

| 15         | 14           | 13         | 12         | 11 | 10     | 9      | 8 |  |  |

|------------|--------------|------------|------------|----|--------|--------|---|--|--|

| CH0_ERR_UR | CH0_ERR_OR   | CH0_ERR_WD | CH0_ERR_AE |    | DATA0[ | 27:16] |   |  |  |

| 7          | 6            | 5          | 4          | 3  | 2      | 1      | 0 |  |  |

|            | DATA0[27:16] |            |            |    |        |        |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 12. Address 0x00, DATA\_MSB\_CH0 Field Descriptions

| Bit  | Field        | Туре | Reset             | Description                                                                   |

|------|--------------|------|-------------------|-------------------------------------------------------------------------------|

| 15   | CH0_ERR_UR   | R    | 0                 | Channel 0 Conversion Under-range Error Flag. Cleared by reading the bit.      |

| 14   | CH0_ERR_OR   | R    | 0                 | Channel 0 Conversion Over-range Error Flag. Cleared by reading the bit.       |

| 13   | CH0_ERR_WD   | R    | 0                 | Channel 0 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12   | CH0_ERR_AE   | R    | 0                 | Channel 0 Conversion Amplitude Error Flag. Cleared by reading the bit.        |

| 11:0 | DATA0[27:16] | R    | 0000 0000<br>0000 | Channel 0 MSB Conversion Result (MSB)                                         |

# 8.6.3 Address 0x01, DATA\_LSB\_CH0

#### Figure 18. Address 0x01, DATA\_LSB\_CH0

| 15              | 14             | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|-----------------|----------------|----|----|----|----|---|---|--|--|--|

| DATA_CH0[15:0]  |                |    |    |    |    |   |   |  |  |  |

| 7 6 5 4 3 2 1 0 |                |    |    |    |    |   |   |  |  |  |

|                 | DATA_CH0[15:0] |    |    |    |    |   |   |  |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Table 13. Address 0x01 DATA\_LSB\_CH0 Field Descriptions

| Bit  | Field       | Туре | Reset     | Description                                                                                                    |

|------|-------------|------|-----------|----------------------------------------------------------------------------------------------------------------|

| 15:0 | DATA0[15:0] | R    | 0000 0000 | Channel 0 LSB Conversion Result (LSB). This register must be read after DATA_MSB_CH0 to ensure data coherency. |

#### 8.6.4 Address 0x02, DATA\_MSB\_CH1

## Figure 19. Address 0x02, DATA\_MSB\_CH1

| 15         | 14           | 13         | 12         | 11 | 10     | 9      | 8 |  |  |

|------------|--------------|------------|------------|----|--------|--------|---|--|--|

| CH1_ERR_UR | CH1_ERR_OR   | CH1_ERR_WD | CH1_ERR_AE |    | DATA1[ | 27:16] |   |  |  |

| 7          | 6            | 5          | 4          | 3  | 2      | 1      | 0 |  |  |

|            | DATA1[27:16] |            |            |    |        |        |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 14. Address 0x02, DATA\_MSB\_CH1 Field Descriptions

| Bit  | Field        | Туре | Reset             | Description                                                                   |

|------|--------------|------|-------------------|-------------------------------------------------------------------------------|

| 15   | CH1_ERR_UR   | R    | 0                 | Channel 1 Conversion Under-range Error Flag. Cleared by reading the bit.      |

| 14   | CH1_ERR_OR   | R    | 0                 | Channel 1 Conversion Over-range Error Flag. Cleared by reading the bit.       |

| 13   | CH1_ERR_WD   | R    | 0                 | Channel 1 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12   | CH1_ERR_AE   | R    | 0                 | Channel 1 Conversion Amplitude Error Flag. Cleared by reading the bit.        |

| 11:0 | DATA1[27:16] | R    | 0000 0000<br>0000 | Channel 1 MSB Conversion Result (MSB)                                         |

# 8.6.5 Address 0x03, DATA\_LSB\_CH1

#### Figure 20. Address 0x03, DATA\_LSB\_CH1

| 15              | 14             | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|-----------------|----------------|----|----|----|----|---|---|--|--|--|

| DATA_CH1[15:0]  |                |    |    |    |    |   |   |  |  |  |

| 7 0 5 4 0 0     |                |    |    |    |    |   |   |  |  |  |

| / 6 5 4 3 2 1 0 |                |    |    |    |    |   |   |  |  |  |

|                 | DATA_CH1[15:0] |    |    |    |    |   |   |  |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 15. Address 0x03, DATA\_LSB\_CH1 Field Descriptions

| Bit  | Field       | Туре | Reset                  | Description                                                                                                    |

|------|-------------|------|------------------------|----------------------------------------------------------------------------------------------------------------|

| 15:0 | DATA1[15:0] | R    | 0000 0000<br>0000 0000 | Channel 1 LSB Conversion Result (LSB). This register must be read after DATA_MSB_CH1 to ensure data coherency. |

SNOSCZ8 – APRIL 2016 www.ti.com

#### 8.6.6 Address 0x04, DATA\_MSB\_CH2 (LDC1614 only)

#### Figure 21. Address 0x04, DATA\_MSB\_CH2

| 15         | 14           | 13         | 12         | 11 | 10     | 9      | 8 |  |  |

|------------|--------------|------------|------------|----|--------|--------|---|--|--|

| CH2_ERR_UR | CH2_ERR_OR   | CH2_ERR_WD | CH2_ERR_AE |    | DATA2[ | 27:16] |   |  |  |

| 7          | 6            | 5          | 4          | 3  | 2      | 1      | 0 |  |  |

|            | DATA2[27:16] |            |            |    |        |        |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 16. Address 0x04, DATA\_MSB\_CH2 Field Descriptions

| Bit  | Field        | Туре | Reset             | Description                                                                   |

|------|--------------|------|-------------------|-------------------------------------------------------------------------------|

| 15   | CH2_ERR_UR   | R    | 0                 | Channel 2 Conversion Under-range Error Flag. Cleared by reading the bit.      |

| 14   | CH2_ERR_OR   | R    | 0                 | Channel 2 Conversion Over-range Error Flag. Cleared by reading the bit.       |

| 13   | CH2_ERR_WD   | R    | 0                 | Channel 2 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12   | CH2_ERR_AE   | R    | 0                 | Channel 2 Conversion Amplitude Error Flag. Cleared by reading the bit.        |

| 11:0 | DATA2[27:16] | R    | 0000 0000<br>0000 | Channel 2 MSB Conversion Result (MSB)                                         |

# 8.6.7 Address 0x05, DATA\_LSB\_CH2 (LDC1614 only)

#### Figure 22. Address 0x05, DATA\_LSB\_CH2

| 15              | 14       | 13 | 12     | 11        | 10          | 9              | 8 |  |  |  |  |  |  |  |  |

|-----------------|----------|----|--------|-----------|-------------|----------------|---|--|--|--|--|--|--|--|--|

| DATA_CH2[15:0]  |          |    |        |           |             |                |   |  |  |  |  |  |  |  |  |

| 7 6 5 4 3 2 1 0 |          |    |        |           |             |                |   |  |  |  |  |  |  |  |  |

|                 | <u> </u> |    | DATA_C | :H2[15:0] | <del></del> | DATA_CH2[15:0] |   |  |  |  |  |  |  |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Table 17. Address 0x05 DATA\_LSB\_CH2 Field Descriptions

| Bit  | Field       | Туре | Reset     | Description                                                                                                    |

|------|-------------|------|-----------|----------------------------------------------------------------------------------------------------------------|

| 15:0 | DATA2[15:0] | R    | 0000 0000 | Channel 2 LSB Conversion Result (LSB). This register must be read after DATA_MSB_CH2 to ensure data coherency. |

#### 8.6.8 Address 0x06, DATA\_MSB\_CH3 (LDC1614 only)

## Figure 23. Address 0x06, DATA\_MSB\_CH3

| 15         | 14           | 13         | 12         | 11 | 10     | 9      | 8 |  |  |

|------------|--------------|------------|------------|----|--------|--------|---|--|--|

| CH3_ERR_UR | CH3_ERR_OR   | CH3_ERR_WD | CH3_ERR_AE |    | DATA3[ | 27:16] |   |  |  |

| 7          | 6            | 5          | 4          | 3  | 2      | 1      | 0 |  |  |

|            | DATA3[27:16] |            |            |    |        |        |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 18. Address 0x06, DATA\_MSB\_CH3 Field Descriptions

| Bit  | Field        | Туре | Reset             | Description                                                                   |

|------|--------------|------|-------------------|-------------------------------------------------------------------------------|

| 15   | CH3_ERR_UR   | R    | 0                 | Channel 3 Conversion Under-range Error Flag. Cleared by reading the bit.      |

| 14   | CH3_ERR_OR   | R    | 0                 | Channel 3 Conversion Over-range Error Flag. Cleared by reading the bit.       |

| 13   | CH3_ERR_WD   | R    | 0                 | Channel 3 Conversion Watchdog Timeout Error Flag. Cleared by reading the bit. |

| 12   | CH3_ERR_AE   | R    | 0                 | Channel 3 Conversion Amplitude Error Flag. Cleared by reading the bit.        |

| 11:0 | DATA3[27:16] | R    | 0000 0000<br>0000 | Channel 3 MSB Conversion Result (MSB)                                         |

# 8.6.9 Address 0x07, DATA\_LSB\_CH3 (LDC1614 only)

#### Figure 24. Address 0x07, DATA\_LSB\_CH3

| 15             | 14             | 13 | 12 | 11 | 10 | 9 | 8 |  |  |

|----------------|----------------|----|----|----|----|---|---|--|--|

| DATA_CH3[15:0] |                |    |    |    |    |   |   |  |  |

| 7              | 6              | 5  | 4  | 3  | 2  | 1 | 0 |  |  |

| ,              | DATA_CH3[15:0] |    |    |    |    |   |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 19. Address 0x07 DATA\_LSB\_CH3 Field Descriptions

| Bit  | Field       | Туре | Reset     | Description                                                                                                    |

|------|-------------|------|-----------|----------------------------------------------------------------------------------------------------------------|

| 15:0 | DATA3[15:0] | R    | 0000 0000 | Channel 3 LSB Conversion Result (LSB). This register must be read after DATA_MSB_CH3 to ensure data coherency. |

#### 8.6.10 Address 0x08, RCOUNT CH0