# **General Description**

The MAX115/MAX116 are high-speed, multichannel, 12-bit data-acquisition systems (DAS) with simultaneous track/holds (T/Hs). These devices contain a 12-bit, 2µs, successive-approximation analog-to-digital converter (ADC), a +2.5V reference, a buffered reference input, and a bank of four simultaneous-sampling T/H amplifiers that preserve the relative phase information of the sampled inputs. The MAX115/MAX116 have two multiplexed inputs for each T/H, allowing a total of eight inputs. In addition, the converter is overvoltage tolerant to  $\pm$ 17V. A fault condition on any channel will not damage the IC. Available input ranges are  $\pm$ 5V (MAX115) and  $\pm$ 2.5V (MAX116).

The parallel interface's data access and bus release timing specifications are compatible with most popular digital signal processors and 16-bit/32-bit microprocessors. The MAX115/MAX116 conversion results can be accessed without resorting to wait-states.

**Applications**

Multiphase Motor Control Power-Grid Synchronization Power-Factor Monitoring Digital Signal Processing Vibration and Waveform Analysis

#

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# \_\_Features

- Four Simultaneous-Sampling T/H Amplifiers with Two Multiplexed Inputs (Eight Single-Ended Inputs Total)

- ♦ 2µs Conversion Time per Channel

- Throughput: 390ksps (1 Channel) 218ksps (2 Channels) 152ksps (3 Channels) 116ksps (4 Channels)

- Input Range: ± 5V (MAX115)

± 2.5V (MAX116)

- Fault-Protected Input Multiplexer (±17V)

- ♦ Internal +2.5V or External Reference Operation

- Programmable On-Board Sequencer

- High-Speed Parallel DSP Interface

- Internal 10MHz Clock

# **Ordering Information**

| PART      | TEMP. RANGE    | PIN-PACKAGE |

|-----------|----------------|-------------|

| MAX115CAX | 0°C to +70°C   | 36 SSOP     |

| MAX115EAX | -40°C to +85°C | 36 SSOP     |

| MAX116CAX | 0°C to +70°C   | 36 SSOP     |

| MAX116EAX | -40°C to +85°C | 36 SSOP     |

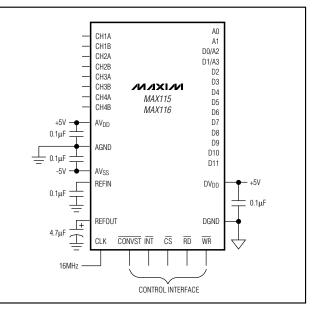

# **Typical Operating Circuit**

Maxim Integrated Products

# **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND        | 0.3V to 6V                        |

|---------------------------------|-----------------------------------|

| AV <sub>SS</sub> to AGND        | 0.3V to -6V                       |

| DV <sub>DD</sub> to DGND        | 0.3V to 6V                        |

| AGND to DGND                    | 0.3V to 0.3V                      |

| CH to AGND                      | ±17V                              |

| REFIN, REFOUT to AGND           | 0.3V to 6V                        |

| Digital Inputs/Outputs to DGND. | 0.3V to (DV <sub>DD</sub> + 0.3V) |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>36-Pin SSOP (derate 11.8mW/°C above +70°C)941mW |   |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| Operating Temperature Ranges                                                                             |   |  |  |  |  |

| MAX115_CAX/MAX116_CAX0°C to +70°C                                                                        | С |  |  |  |  |

| MAX115_EAX/MAX116_EAX40°C to +85°C                                                                       | С |  |  |  |  |

| Junction Temperature+150°C                                                                               | С |  |  |  |  |

| Storage Temperature Range65°C to +150°C                                                                  | С |  |  |  |  |

| _ead Temperature (soldering, 10s)                                                                        | 2 |  |  |  |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = +5V \pm 5\%, AV_{SS} = -5V \pm 5\%, DV_{DD} = +5V \pm 5\%, V_{REFIN} = +2.5V$  (external reference), AGND = DGND = 0, 4.7µF capacitor from REFOUT to AGND, 0.1µF capacitor from REFIN to AGND, f<sub>CLK</sub> = 16MHz, external clock, 50% duty cycle. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                           | SYMBOL                  |                               | CONDITIONS                   | MIN | TYP | MAX  | UNITS   |  |

|-------------------------------------|-------------------------|-------------------------------|------------------------------|-----|-----|------|---------|--|

| DC ACCURACY (Note 1)                |                         |                               |                              |     |     |      |         |  |

| Resolution                          | N                       | All channels                  |                              | 12  |     |      | Bits    |  |

| Integral Nonlinearity (Note 2)      | INL                     |                               |                              |     | 0.6 | ±1   | LSB     |  |

| Differential Nonlinearity           | DNL                     |                               |                              |     | 0.6 | ±1   | LSB     |  |

|                                     |                         |                               | $T_A = +25^{\circ}C$         |     | ±5  | ±15  |         |  |

| Disalar Zara Errar                  |                         | MAX115                        | $T_A = T_{MIN}$ to $T_{MAX}$ |     |     | ±30  |         |  |

| Bipolar Zero Error                  |                         |                               | T <sub>A</sub> = +25°C       |     | ±5  | ±10  | mV      |  |

|                                     |                         | MAX116                        | $T_A = T_{MIN}$ to $T_{MAX}$ |     |     | ±18  | -       |  |

| Bipolar Zero-Error Match            |                         | Between all cha               | nnels                        |     | 2   | 5    | mV      |  |

| Zene Oede Teneres                   |                         | MAX115                        |                              |     | 180 |      |         |  |

| Zero-Code Tempco                    |                         | MAX116                        |                              |     | 90  |      | - μV/°C |  |

|                                     |                         |                               | $T_A = +25^{\circ}C$         |     | ±5  | ±15  | _       |  |

|                                     |                         | MAX115                        | $T_A = T_{MIN}$ to $T_{MAX}$ |     |     | ±25  |         |  |

| Gain Error                          |                         |                               | T <sub>A</sub> = +25°C       |     | ±5  | ±10  | mV      |  |

|                                     |                         | MAX116                        | $T_A = T_{MIN}$ to $T_{MAX}$ |     |     | ±18  | -       |  |

| Gain Error Match                    |                         |                               |                              |     | 2   | 5    | mV      |  |

|                                     |                         | MAX115<br>MAX116              |                              |     | 120 |      | 2//20   |  |

| Gain Error Tempco                   |                         |                               |                              |     | 60  | μV/° |         |  |

| DYNAMIC PERFORMANCE (f <sub>C</sub> | _ <sub>K</sub> = 16MHz, | f <sub>IN</sub> = 10.06kHz) ( | Notes 1, 3)                  |     |     |      | 1       |  |

| Signal-to-Noise Ratio               | SNR                     | (Note 4)                      |                              | 69  |     |      | dB      |  |

| Total Harmonic Distortion           | THD                     | (Notes 4, 5)                  |                              |     |     | -80  | dB      |  |

| Spurious-Free Dynamic Range         | SFDR                    | (Note 4)                      |                              | 80  |     |      | dB      |  |

| Channel-to-Channel Isolation        |                         | (Note 6)                      |                              |     | 80  |      | dB      |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V \pm 5\%, AV_{SS} = -5V \pm 5\%, DV_{DD} = +5V \pm 5\%, V_{REFIN} = +2.5V$  (external reference), AGND = DGND = 0, 4.7µF capacitor from REFOUT to AGND, 0.1µF capacitor from REFIN to AGND, f<sub>CLK</sub> = 16MHz, external clock, 50% duty cycle. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                               | SYMBOL        | CONDITIONS                    | MIN   | ТҮР  | MAX   | UNITS  |

|-----------------------------------------|---------------|-------------------------------|-------|------|-------|--------|

| ANALOG INPUT                            |               |                               |       |      |       |        |

|                                         |               | MAX115                        |       |      | ±5    |        |

| Input Voltage Range                     | VIN           | MAX116                        |       |      | ±2.5  | V      |

|                                         |               | MAX115 (-5V to +5V range)     |       |      | ±625  |        |

| Input Current                           | lin           | MAX116 (-2.5V to +2.5V range) |       |      | ±15   | μA     |

| Input Capacitance                       | CIN           |                               |       | 16   |       | pF     |

| TRACK/HOLD                              | ·             |                               |       |      |       |        |

| Acquisition Time                        | tacq          |                               | 600   |      |       | ns     |

| Small-Signal Bandwidth                  |               |                               |       | 10   |       | MHz    |

| Full-Power Bandwidth                    |               |                               |       | 1.3  |       | MHz    |

| Drop Rate                               |               |                               |       | 2    |       | mV/ms  |

| Aperture Delay                          |               |                               |       | 10   |       | ns     |

| Aperture Jitter                         |               |                               |       | 30   |       | ps     |

| Aperture-Delay Matching                 |               |                               |       | 500  |       | ps     |

| REFERENCE OUTPUT (Note 7                | 7)            |                               |       |      |       |        |

| Output Voltage                          | VREFOUT       | $T_A = +25^{\circ}C$          | 2.462 | 2.5  | 2.532 | V      |

| External Load Regulation                |               | 0 < I <sub>REF</sub> < 1mA    |       | 0.5  |       | mV/m/  |

| REFOUT Tempco                           |               | (Note 8)                      |       | 30   |       | ppm/°C |

| External Capacitive Bypass at REFIN     |               |                               | 0.1   |      |       | μF     |

| External Capacitive Bypass<br>at REFOUT |               |                               | 4.7   |      | 22    | μF     |

| REFERENCE INPUT                         |               |                               |       |      |       |        |

| Input Voltage Range                     |               |                               | 2.40  | 2.50 | 2.60  | V      |

| Input Current                           |               |                               |       |      | ±50   | μA     |

| Input Resistance (Note 9)               |               |                               |       | 10   |       | kΩ     |

| Input Capacitance                       |               |                               |       | 10   |       | pF     |

| EXTERNAL CLOCK                          |               |                               |       |      |       |        |

| External Clock Frequency                |               |                               |       |      | 16    | MHz    |

| INTERNAL CLOCK                          |               |                               |       |      |       |        |

| Internal Clock Frequency                |               |                               | 5.6   | 10   | 14.8  | MHz    |

| DIGITAL INPUTS (CONVST, F               | RD, WR, CS, C | CLK, A0–A3) (Note 1)          | ·     |      |       |        |

| Input High Voltage                      | VIH           |                               | 2.4   |      |       | V      |

| Input Low Voltage                       | VIL           |                               |       |      | 0.8   | V      |

| Input Current                           | lisi          | CONVST, RD, WR, CS, CLK       |       |      | ±1    | — иА   |

|                                         | lin           | A0-A3                         |       |      | ±10   |        |

| Input Capacitance                       | CIN           |                               |       | 15   |       | pF     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V \pm 5\%, AV_{SS} = -5V \pm 5\%, DV_{DD} = +5V \pm 5\%, V_{REFIN} = +2.5V$  (external reference), AGND = DGND = 0, 4.7µF capacitor from REFOUT to AGND, 0.1µF capacitor from REFIN to AGND, f<sub>CLK</sub> = 16MHz, external clock, 50% duty cycle. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                         | SYMBOL           | CONDITIONS                | MIN   | ТҮР | MAX   | UNITS |

|-----------------------------------|------------------|---------------------------|-------|-----|-------|-------|

| DIGITAL OUTPUTS (D0-D11,          | INT)             | 1                         | 1     |     |       | 1     |

| Output High Voltage               | V <sub>OH</sub>  | I <sub>OUT</sub> = 1mA    | 4     |     |       | V     |

| Output Low Voltage                | Vol              | I <sub>OUT</sub> = -1.6mA |       |     | 0.4   | V     |

| Three-State Leakage Current       |                  | D0-D11                    |       |     | ±10   | μA    |

| Three-State Output<br>Capacitance |                  |                           |       | 10  |       | pF    |

| POWER REQUIREMENTS                | -                |                           | 1     |     |       | •     |

| Positive Supply Voltage           | AV <sub>DD</sub> |                           | 4.75  | 5   | 5.25  | V     |

| Negative Supply Voltage           | AVSS             |                           | -5.25 | -5  | -4.75 | V     |

| Digital Supply Voltage            | DV <sub>DD</sub> |                           | 4.75  | 5   | 5.25  | V     |

| Positive Supply Current           | IAVDD            |                           |       | 17  | 25    | mA    |

| Negative Supply Current           | IAVSS            |                           | -20   | -15 |       | mA    |

| Digital Supply Current            |                  |                           |       | 3   | 6     | mA    |

| Shutdown Positive Current         |                  |                           |       | 1   |       | μA    |

| Shutdown Negative Current         |                  |                           |       | -1  |       | μA    |

| Shutdown Digital Current          |                  |                           |       | 13  |       | μA    |

| Positive Supply Rejection         | PSRR+            | (Note 10)                 |       |     | ±1    | LSB   |

| Negative Supply Rejection         | PSRR-            | (Note 10)                 |       |     | ±1    | LSB   |

| Power Dissipation                 |                  | (Note 11)                 |       | 175 |       | mW    |

# TIMING CHARACTERISTICS

(See Figure 4,  $AV_{DD} = +5V$ ,  $AV_{SS} = -5V$ ,  $DV_{DD} = +5V$ , AGND = DGND = 0,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                | SYMBOL          | CONDITIONS           | MIN | TYP | MAX | UNITS |

|--------------------------|-----------------|----------------------|-----|-----|-----|-------|

| CONVST Pulse Width       | tcw             |                      | 30  |     |     | ns    |

| CS to WR Setup Time      | tcws            | Guaranteed by design | 0   |     |     | ns    |

| CS to WR Hold Time       | tCMH            | Guaranteed by design | 0   |     |     | ns    |

| WR Low Pulse Width       | twr             |                      | 30  |     |     | ns    |

| Address Setup Time       | tas             |                      | 30  |     |     | ns    |

| Address Hold Time        | tah             |                      | 0   |     |     | ns    |

| RD to INT Delay          | tiD             | 25pF load            |     |     | 55  | ns    |

| Delay Time Between Reads | t <sub>RD</sub> |                      | 45  |     |     | ns    |

| CS to RD Setup Time      | tCRS            | Guaranteed by design | 0   |     |     | ns    |

| CS to RD Hold Time       | tCRH            | Guaranteed by design | 0   |     |     | ns    |

| RD Low Pulse Width       | trd             |                      | 30  |     |     | ns    |

| Data-Access Time         | tDA             | 25pF load (Note 12)  |     |     | 40  | ns    |

| Bus-Relinquish Time      | tDH             | 25pF load (Note 13)  | 5   |     | 45  | ns    |

# TIMING CHARACTERISTICS (continued)

(See Figure 4,  $AV_{DD} = +5V$ ,  $AV_{SS} = -5V$ ,  $DV_{DD} = +5V$ , AGND = DGND = 0,  $T_A = T_{MIN}$  to  $T_{MAX}$ , Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER       | SYMBOL | CONDITIONS        | MIN | TYP | MAX | UNITS |

|-----------------|--------|-------------------|-----|-----|-----|-------|

|                 |        | Mode 1, channel 1 |     |     | 2   |       |

|                 | taavuu | Mode 2, channel 2 |     |     | 4   |       |

| Conversion Time | tCONV  | Mode 3, channel 3 |     |     | 6   | μs    |

|                 |        | Mode 4, channel 4 |     |     | 8   |       |

|                 |        | Mode 1, channel 1 |     |     | 390 | liene |

| Conversion Rate |        | Mode 2, channel 2 |     |     | 218 |       |

|                 |        | Mode 3, channel 3 |     |     | 152 | ksps  |

|                 |        | Mode 4, channel 4 |     |     | 116 |       |

| Startup Time    |        | Exiting shutdown  |     | 20  |     | ms    |

**Note 1:**  $AV_{DD} = +5V$ ,  $AV_{SS} = -5V$ ,  $DV_{DD} = +5V$ ,  $V_{REFIN} = 2.500V$  (external),  $V_{IN} = \pm 5V$  (MAX115) or  $\pm 2.5V$  (MAX116).

**Note 2:** Integral nonlinearity is the analog value's deviation at any code from its theoretical value after the full-scale range and offset have been calibrated.

Note 3: CLK synchronized with CONVST.

Note 4:  $f_{IN} = 10.06 \text{kHz}$ ,  $V_{IN} = \pm 5 \text{V}$  (MAX115) or  $\pm 2.5 \text{V}$  (MAX116).

Note 5: First five harmonics.

Note 6: All inputs except CH1A driven with ±5V (MAX115) or ±2.5V (MAX116) 10.06kHz signal, CH1A connected to AGND and digitized.

Note 7:  $AV_{DD} = DV_{DD} = +5V$ ,  $AV_{SS} = -5V$ ,  $V_{IN} = 0V$  (all channels).

**Note 8:** Temperature drift is defined as the change in output voltage from +25°C to  $T_{MIN}$  or  $T_{MAX}$ . It is calculated as TC = [ $\Delta$ REFOUT/REFOUT] /  $\Delta$ T.

Note 9: See Figure 2.

Note 10: Defined as the change in positive full scale caused by a  $\pm 5\%$  variation in the nominal supply voltage. Tested with one input at full scale and all others at AGND. V<sub>REFIN</sub> =  $\pm 2.5V$  (internal).

Note 11: Tested with all inputs connected to AGND. VREFIN = +2.5V (internal).

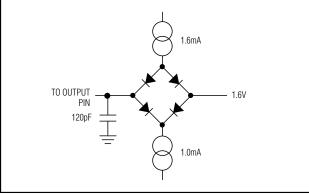

**Note 12:** The data access time is defined as the time required for an output to cross +0.8V or +2.0V. It is measured using the circuit of Figure 1. The measured number is then extrapolated back to determine the value with a 25pF load.

Note 13: The bus relinquish time is derived from the measured time taken for the data outputs to change +0.5V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging and discharging the 120pF capacitor. The time given is the part's true bus relinquish time, which is independent of the external bus loading capacitance.

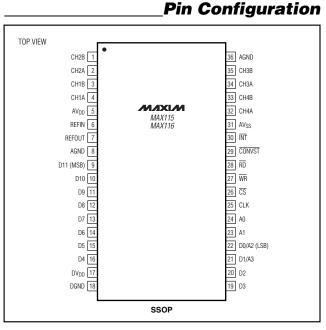

**Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                 |

|--------|------------------|----------------------------------------------------------------------------------------------------------|

| 1, 2   | CH2B, CH2A       | Channel 2 Multiplexed Inputs (single-ended)                                                              |

| 3, 4   | CH1B, CH1A       | Channel 1 Multiplexed Inputs (single-ended)                                                              |

| 5      | AV <sub>DD</sub> | Analog Supply Voltage                                                                                    |

| 6      | REFIN            | External reference input/internal reference output. Bypass with a 0.1µF capacitor to AGND.               |

| 7      | REFOUT           | Reference-Buffer output. Bypass with a 4.7µF capacitor to AGND.                                          |

| 8, 36  | AGND             | Analog ground. Both pins must be connected to ground.                                                    |

| 9–16   | D11-D4           | Data Bits. D11 = MSB.                                                                                    |

| 17     | DV <sub>DD</sub> | Digital Supply Voltage                                                                                   |

| 18     | DGND             | Digital Ground                                                                                           |

| 19, 20 | D3, D2           | Data Bits                                                                                                |

| 21, 22 | D1/A3, D0/A2     | Bidirectional Data Bits/Address Bits                                                                     |

| 23, 24 | A1, A0           | Address Bits                                                                                             |

| 25     | CLK              | Clock Input (duty cycle must be 30% to 70%). Connect CLK to DV <sub>DD</sub> to activate internal clock. |

| 26     | CS               | Chip-Select Input (active-low)                                                                           |

| 27     | WR               | Write Input (active-low)                                                                                 |

| 28     | RD               | Read Input (active-low)                                                                                  |

| 29     | CONVST           | Conversion-Start input. Rising edge initiates sampling and conversion sequence.                          |

| 30     | ĪNT              | Interrupt output. Falling edge indicates the end of a conversion sequence.                               |

| 31     | AV <sub>SS</sub> | Analog Supply Voltage                                                                                    |

| 32, 33 | CH4A, CH4B       | Channel 4 Multiplexed Inputs (single-ended)                                                              |

| 34, 35 | СНЗА, СНЗВ       | Channel 3 Multiplexed Inputs (single-ended)                                                              |

# **Detailed Description**

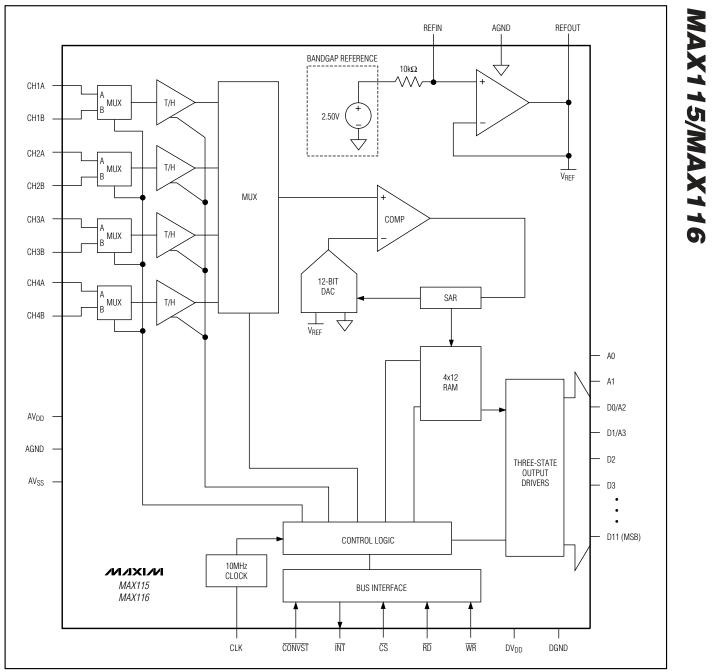

The MAX115/MAX116 use a successive-approximation conversion technique and four simultaneous-sampling track/hold (T/H) amplifiers to convert analog signals into 12-bit digital outputs. Each T/H has two multiplexed inputs, allowing a total of eight inputs. Each T/H output is converted and stored in memory to be accessed sequentially by the parallel interface with successive read cycles. The MAX115/MAX116 internal microsequencer can be programmed to digitize one, two, three, or four inputs sampled simultaneously from either of the two banks of four inputs (Figure 2). The MAX115/MAX116 can operate with either an external or internal clock. For internal operation, connect CLK to DV<sub>DD</sub>.

Figure 2. Functional Diagram

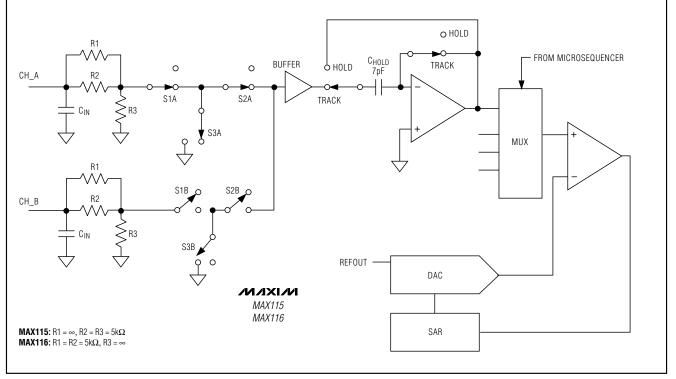

Figure 3. Equivalent Input Circuit

The conversion timing and control sequences are derived from either an internal clock or an external clock, the CONVST signal, and the programmed mode. The T/H amplifiers hold the input voltages at the CONVST rising edge. Additional CONVST pulses are ignored until the last conversion for the sample is complete. An on-board sequencer converts one to four channels per CONVST pulse. In the default mode, one T/H output (CH1A) is converted. An interrupt signal (INT) is provided after the last conversion is complete. Convert two to four channels by reprogramming the MAX115/MAX116 through the bidirectional parallel interface. Once programmed, the MAX115/MAX116 continues to convert the specified number of channels per CONVST pulse until they are reprogrammed. The channels are converted sequentially, beginning with CH1. The INT signal always follows the end of the last conversion in a conversion sequence. The ADC converts each assigned channel in 2µs and stores the result in an internal 4 x 12-bit memory.

At the end of the last conversion, INT goes low and the T/H amplifiers begin to track the inputs again. The data can be accessed by applying successive pulses to the RD pin. Successive reads access data words sequen-

tially. The memory is not random-access and data from CH1 is always read first. After performing four consecutive reads or initiating a new conversion, the address pointer selects CH1 again. Additional read pulses cycle through the data words.  $\overline{\text{CS}}$  can be held low during successive reads.

### **Input Bandwidth**

The T/H's input tracking circuitry has a 10MHz smallsignal bandwidth, so it is possible to digitize highspeed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. To avoid highfrequency signals being aliased into the frequency band of interest, anti-alias filtering is recommended.

### **Analog Input Range and Input Protection** The MAX115's input range is ±5V, and the MAX116's input range is ±2.5V. The input resistance for the MAX115 is 10k $\Omega$ (typ), and the input resistance for the MAX116 is 1M $\Omega$ (typ). An input protection structure allows input voltages to ±17V without harming the IC. This protection is also active in shutdown mode.

## CONVST tACQ INT tcwn. $\overline{CS}$ teres RD tRD WR tn∆ • tрн DATA CH2 СНЗ DATA IN сн1

2x4-Channel, Simultaneous-Sampling

Figure 4. Timing Diagram

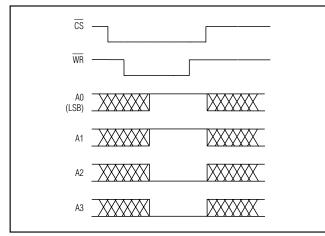

Figure 5. Programming a Four-Channel Conversion, Input Mux A

# Track/Holds

The MAX115/MAX116 feature four simultaneous T/Hs. Each T/H has two multiplexed inputs. A T-switch input configuration provides excellent hold-mode isolation. Allow 600ns acquisition time for 12-bit accuracy.

The T/H aperture delay is typically 10ns. The 500ps aperture-delay mismatch between the T/Hs allows the relative phase information of up to four different inputs to be preserved. Figure 3 shows the equivalent input circuit, illustrating the ADC's sampling architecture. Only one of four T/H stages with its two multiplexed inputs (CH\_A and CH\_B) is shown. All switches are in track configuration for channel A. An internal buffer charges the hold capacitor to minimize the required

acquisition time between conversions. The analog input appears as a 10k $\Omega$  resistor in parallel with a 16pF capacitor for the MAX115 and as a 1M $\Omega$  resistor in parallel with a 16pF capacitor for the MAX116.

Between conversions, the buffer input is connected to channel 1 of the selected track/hold bank. When a channel is not selected, switches S1, S2, and S3 are placed in hold mode to improve channel-to-channel isolation.

# **Digital Interface**

12-Bit ADCs

Input data (A0–A3) and output data ( $\overline{D0}$ –D11) are multiplexed on a three-state bidirectional interface. This parallel I/O can easily be interfaced with a microprocessor ( $\mu$ P) or DSP.  $\overline{CS}$ , WR, and RD control the write and read operations.  $\overline{CS}$  is the standard chip-select signal, which enables the controller to address the MAX115/MAX116 as an I/O port. When  $\overline{CS}$  is high, it disables the WR and RD inputs and forces the interface into a high-Z state. Figure 4 details the interface timing.

# **Programming Modes**

The MAX115/MAX116 have eight conversion modes plus power-down, which are programmed through a bidirectional parallel interface. At power-up, the devices default to the Input Mux A/Single-Channel Conversion mode. The user can select between two banks (mux inputs A or mux inputs B) of four simultaneous-sampled input channels, as illustrated in Figure 2. An internal microsequencer can be programmed to convert one to four channels of the selected bank per sample. For a single-channel conversion, CH1 is digitized, and then INT goes low to indicate completion of the conversion.

# MAX115/MAX116

CONVERSION

TIME (µs)

2

4

6

8

2

4

6

8

# Table 1. Modes of Operation

A1

0

0

1

1

0

0

1

1

Х

A0

0

1

0

1

0

1

0

1

Х

A2

0

0

0

0

1

1

1

1

Х

1 *X* = Don't care

A3

0

0

0

0

0

0

0

0

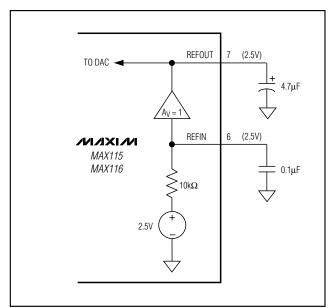

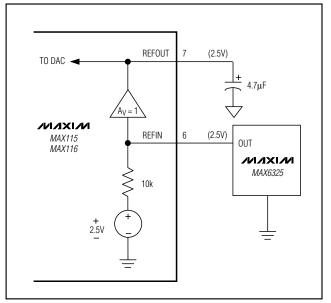

Figure 6. Internal Reference

For multichannel conversions, INT goes low after the last channel has been digitized.

To input data into the MAX115/MAX116, pull  $\overline{CS}$  low, program the bidirectional pins A0–A3 (Table 1), and pulse  $\overline{WR}$  low. Data is latched into the devices on the WR or  $\overline{CS}$  rising edge. The ADC is now ready to convert. Once programmed, the ADC continues operating in the same mode until reprogrammed or until power is removed. Figure 5 shows an example of programming a four-channel conversion using Input Mux A.

### Starting a Conversion

After programming the MAX115/MAX116 as outlined in the *Programming Modes* section, pulse CONVST low to initiate a conversion sequence. The analog inputs are sampled at the CONVST rising edge. Do not start a new conversion while the conversion is in progress. Monitor the INT output. A falling edge indicates the end of a conversion sequence.

MODE

Input Mux A/Single-Channel Conversion (default at power-up)

Input Mux A/Two-Channel Conversion

Input Mux A/Three-Channel Conversion

Input Mux B/Single-Channel Conversion

Input Mux A/Four-Channel Conversion

Input Mux B/Two-Channel Conversion

Input Mux B/Three-Channel Conversion

Input Mux B/Four-Channel Conversion

Power-Down

### Reading a Conversion

Digitized data from up to four channels is stored in memory to be read out through the parallel interface. After receiving an INT signal, the user can access up to four conversion results by performing up to four read operations.

With  $\overline{\text{CS}}$  low, the conversion results from CH1\_ are accessed, and  $\overline{\text{INT}}$  is reset high on the first  $\overline{\text{RD}}$  falling edge. On the  $\overline{\text{RD}}$  rising edge, the internal address pointer is advanced. If a single conversion is programmed, only one  $\overline{\text{RD}}$  pulse is required. For multichannel conversions, up to four  $\overline{\text{RD}}$  falling edges sequentially access the data for channels 1 through 4. For any number of channels converted, the address pointer is reset to CH1\_ after four  $\overline{\text{RD}}$  pulses. The address pointer also resets after receiving a  $\overline{\text{CNVST}}$  pulse. Do not perform a read operation during conversion; it will corrupt the conversion's accuracy.

# **Applications Information**

# Clock

The MAX115/MAX116 have an internal 10MHz (typ) clock, which is activated by connecting CLK to  $DV_{DD}$  (internal clock startup time is 165µs typ). The CLK input also accepts an external clock with duty cycle between 30% and 70%.

Figure 7. External Reference

### **Internal and External Reference**

The MAX115/MAX116 can be used with an internal or external reference voltage. An external +2.5 reference can be connected directly at REFIN. An internal buffer with a gain of +1 provides +2.5V at REFOUT.

### Internal Reference

The full-scale range with the internal reference is  $\pm 5V$  for the MAX115 and  $\pm 2.5V$  for the MAX116. Bypass REFIN with a 0.1µF capacitor to AGND, and bypass the REFOUT pin with a 4.7µF (min) capacitor to AGND (Figure 6). The maximum value to compensate the reference buffer is 22µF. Larger values are acceptable if low-ESR capacitors are used.

### **External Reference**

For operation over a wide temperature range, an external +2.5V reference with tighter specifications improves accuracy. The MAX6325 is an excellent choice to match the MAX115/MAX116 accuracy over the commercial and extended temperature ranges with a 1ppm/°C (max) temperature drift. Connect an external reference at REFIN as shown in Figure 7. The minimum impedance is  $7k\Omega$  for DC currents in both normal operation and shutdown. Bypass REFOUT with a 4.7µF low-ESR capacitor.

## **Power-On Reset**

When power is first applied, the internal power-on reset (POR) circuitry activates the MAX115/MAX116 with  $\overline{INT}$  = high, ready to convert. The default conversion mode

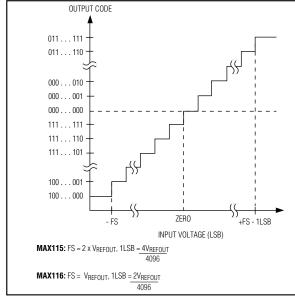

Figure 8. Bipolar Transfer Function

is Input Mux A/Single Channel Conversion. See the *Programming Modes* section if other configurations are desired.

After the power supplies have been stabilized, the reset time is  $5\mu s$ . No conversions should be performed during this phase. At power-up, data-in memory is undefined.

### Software Power-Down

Software power-down is activated by setting bit A3 of the control word high (Table 1). It is asserted after the WR or CS rising edge, at which point the ADC immediately powers down to a low quiescent-current state. IAVDD and IAVSS drop to less than 1µA (typ), and IDVDD drops to 13µA (typ). The ADC circuitry and reference buffer are turned off, but the digital interface and the reference remain active for fast power-up recovery. Wake up the MAX115/MAX116 by writing a control word (A0-A3, Table 1). The bidirectional interface interprets a logic zero at A3 as the start signal, and powers up in the mode selected by A0, A1, and A2. The reference buffer's settling time and the bypass capacitor's value dominate the power-up delay. With the recommended 4.7µF at REFOUT, the power-up delay is typically 20ms.

### **Transfer Function**

The MAX115/MAX116 have bipolar input ranges. Figure 8 shows the bipolar/output transfer function. Code transitions occur at successive-integer least significant bit

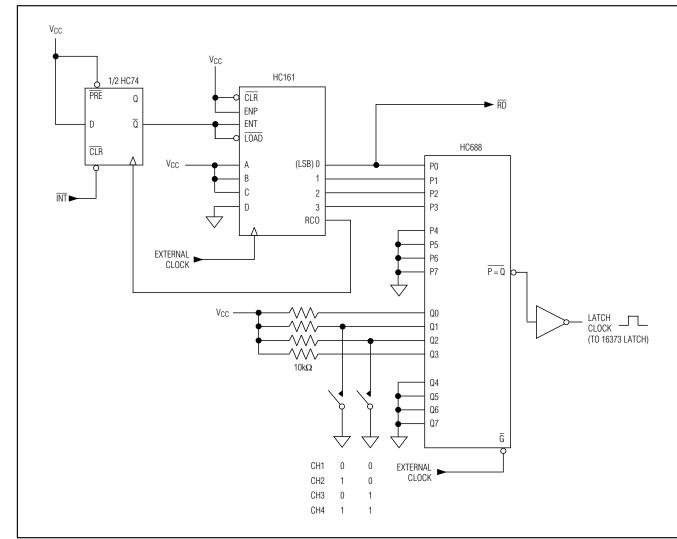

Figure 9. Output Demultiplexer Circuit

(LSB) values. Output coding is two-complement binary with 1LSB = 2.44mV for the MAX115 and 1LSB = 1.22mV for the MAX116.

# **Output Demultiplexer**

An output demultiplexer circuit is useful for isolating data from one channel in a four-channel conversion sequence. Figure 9's circuit uses the external 16MHz clock and the INT signal to generate four RD pulses and a latch clock to save data from the desired channel. CS must be low during the four RD pulses. The channel is selected with the binary coding of two switches. A 16-bit 16373 latch simplifies layout.

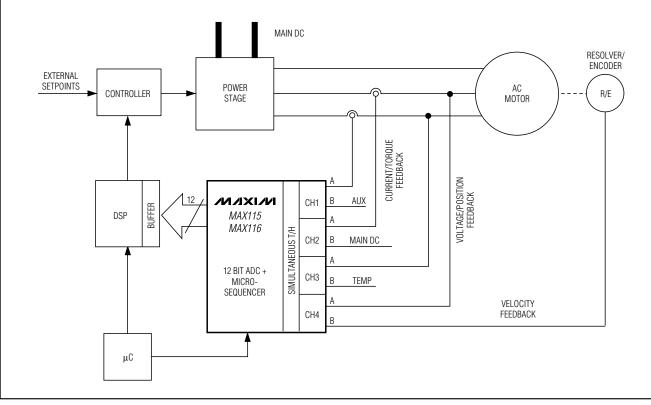

# **Motor-Control Applications**

Vector motor control requires monitoring of the individual phase currents. In their most basic application, the MAX115/MAX116 simultaneously sample two currents (CH1A and CH2A, Figure 10) and preserve the necessary relative phase information. Only two of the three phase currents have to be digitized because the third component can be mathematically derived with a coordinate transformation.

The circuit of Figure 10 shows a typical vector motorcontrol application using all available inputs of the MAX115/MAX116. CH1A and CH2A are connected to two isolated Hall-effect current sensors and are a

Figure 10. Vector Motor Control

part of the current (torque) feedback loop. The MAX115/MAX116 digitize the currents and deliver raw data to the following DSP and controller stages, where the vector processing takes place. Sensorless vector control uses a computer model for the motor and an algorithm to split each output current into its magnetizing (stator current) and torque-producing (rotor current) components.

If a two-to-three phase conversion is not practical, three currents can be sampled simultaneously with the addition of a third sensor (not shown). Optional voltage (position) feedback can be derived by measuring two phase voltages (CH3A, CH4A). Typically, an isolated differential amplifier is used between the motor and the MAX115/MAX116. Again, the third phase voltage can be derived from the magnitude (phase voltage) and its relative phase.

For optimum speed control and good load regulation close to zero speed, additional velocity and position feedback are derived from an encoder or resolver and brought to the MAX115/MAX116 at CH4B. The addi-

tional channels can be used to evaluate slower analog inputs, such as the main DC bus voltage (CH2B), temperature sensors (CH3B), or other analog inputs (AUX, CH1B).

### **Power-Supply Bypassing and Ground Management**

For optimum system performance, use printed circuit boards with separate analog and digital ground planes. Wire-wrapped boards are not recommended. Connect the two ground planes together at the low-impedance power-supply source. For the best ground connection, connect the DGND and AGND pins together and connect that point to the system analog ground plane to avoid interference from other digital noise sources. If DGND is connected to the system digital ground, digital noise may get through to the ADC's analog portion.

The AGND pins must be connected directly to a lowimpedance ground plane. Extra impedance between the pins and the ground plane increases crosstalk and degrades INL.

#

MAX115/MAX116

Bypass AV<sub>DD</sub> and AV<sub>SS</sub> with  $0.1\mu$ F ceramic capacitors to AGND. Mount them with short leads close to the device. Ferrite beads may also be used to further isolate the analog and digital power supplies. Bypass DV<sub>DD</sub> with a  $0.1\mu$ F ceramic capacitor to DGND.

# **Chip Information**

TRANSISTOR COUNT: 4116 SUBSTRATE CONNECTED TO AV<sub>SS</sub> PROCESS: BiCMOS

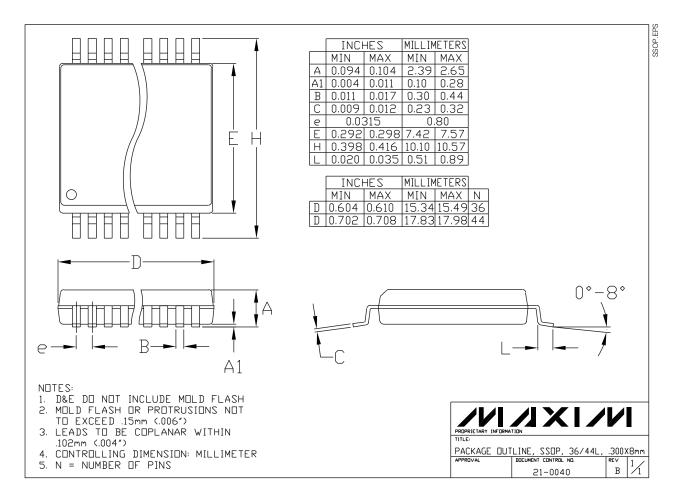

# **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### 14

MAX115/MAX11

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products Printed USA

is a registered trademark of Maxim Integrated Products.