## HDC 9234 PRELIMINARY

## **Universal Disk Controller**

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PIN CONFIGURATION                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Programmable Disk Drive Interface and Formats  IBM® PC-AT® ST506/412 or user definable hard disk formats  IBM® PC-AT® compatible ECC algorithm  IBM Compatible Single or Double Density Floppy Disk Formats  Controls 8", 5.25", and 3.5" drives  Controls tape drives for tape backup of disks  Full CRC generation and checking  Internal or External Error detection  Programmable user-transparent Error correction  Programmable automatic retry option  Programmable internal write precompensation logic  Read/Write commands with automatic seek  Multiple sector read/write transfers  Sector interleave capability  Internal address mark generation and detection  Programmable track step rates  Supports both buffered and unbuffered seeks  Polling command allows overlapping seeks  Powerful, high level command set  Controls up to 4 drives with  up to 16 heads per drive  up to 2048 cylinders per drive  up to 256 sectors per track | S   S   S   S   S   S   S   S   S   S          |

| Flexible System Interface  ☐ Built-in DMA controller capable of addressing up to 16 MBytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ☐ Programmable Interrupt Mask ☐ TTL compatible |

#### GENERAL DESCRIPTION

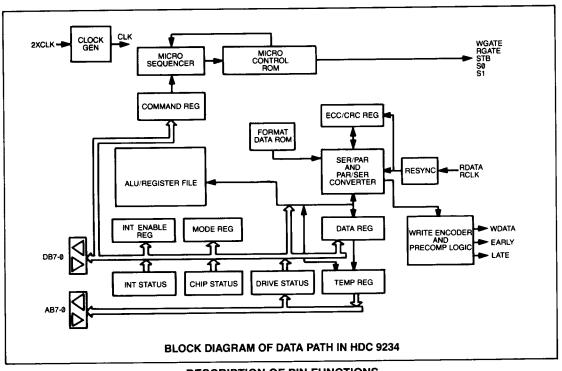

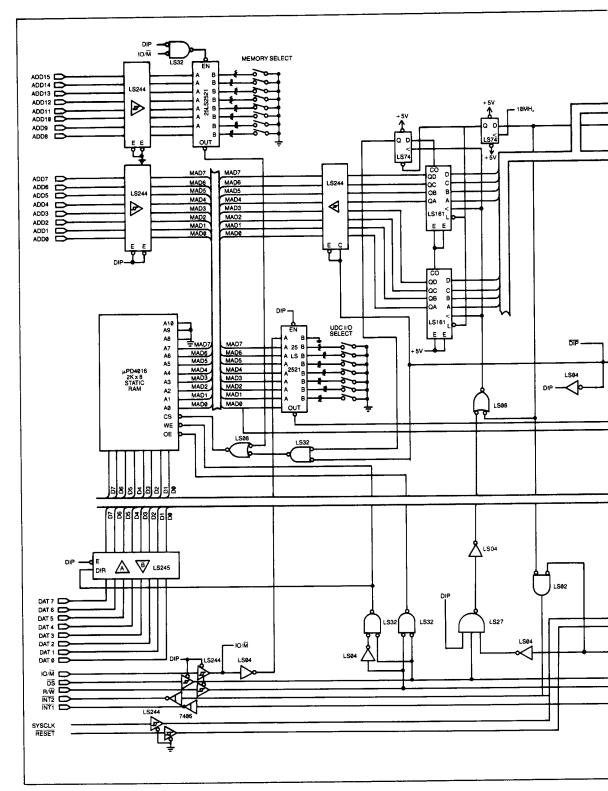

The HDC 9234 Universal Disk Controller (UDC) is a 40 pin, n-channel MOS/LSI device capable of interfacing up to 4 Winchester-type hard disks and/or industry standard floppy disks to a processor. The chip is programmable to support IBM® PC-AT® ST506/412 and user defined hard disk formats, as well as IBM compatible 8", 5.25" and 3.5" single and double density formats.

☐ User readable Interrupt, Chip Status, and Drive Status

☐ Supports either private or virtual buffer memory

addressing schemes

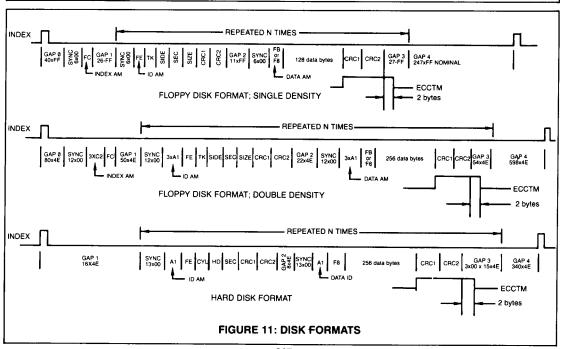

registers

A powerful and sophisticated command set reduces the software overhead required to implement a combined hard disk/floppy disk controller. These commands include:

**Drive Select** Seek to cylinder and read ID Step out 1 cylinder Step in 1 cylinder Restore Drive Read Logical Sectors Read Physical Sectors Read Entire Track Write Logical Sectors Write Physical Sectors Chip Reset Deselect Drive Poll Drives for Ready Set Register Pointer Tape Back-up Format current track

The HDC 9234 can use both private memory or shared memory buffers with the chip's internal DMA controller pro-

viding up to 24 bit addresses over an 8 bit data bus. This enables the HDC 9234 to address up to 16 megabytes of memory, and allows the hardware designer tremendous flexibility in system design.

Standard 40 pin DIP package

☐ Single +5 volt supply

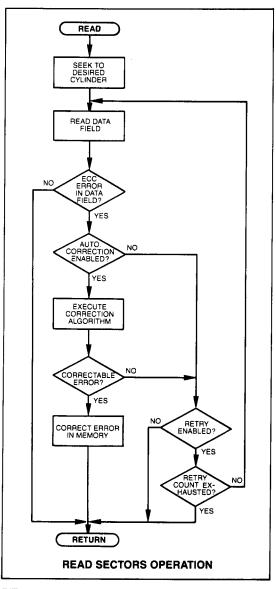

Several techniques of error detection and correction are implemented on the HDC 9234. One user selected method allows the chip to detect and transparently correct a read error in the data-stream, without external logic. Another technique allows the designer complete control over the ECC algorithm, by using external logic or system software to detect and correct the error. As a further aid in error handling, the HDC 9234 allows the user to specify the number of read retries to be attempted before an error is reported to the host processor by the HDC 9234.

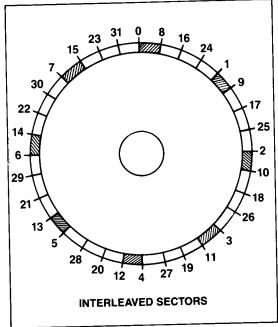

The HDC 9234 features a versatile track format command which allows formatting with interleaved sectors. The chip needs only 4 or 5 bytes of external memory space per sector (depending on format selected). This feature allows the designer to optimize sector interleaving for optimum throughput.

#### **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO.                          | NAME         | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                                                                                                      |  |

|----------------------------------|--------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                | Power        | V <sub>cc</sub> | + 5 volt power supply pin                                                                                                                                                                                                                                                                                        |  |

| 22                               | Ground       | V <sub>ss</sub> | System ground                                                                                                                                                                                                                                                                                                    |  |

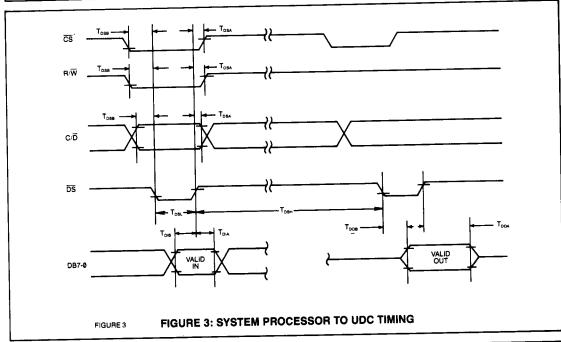

| 16                               | Chip Select  | CS              | This signal (when active) selects the HDC 9234 for communications with the host processor. This signal is normally derived by decoding the high order address bits. It is active low.                                                                                                                            |  |

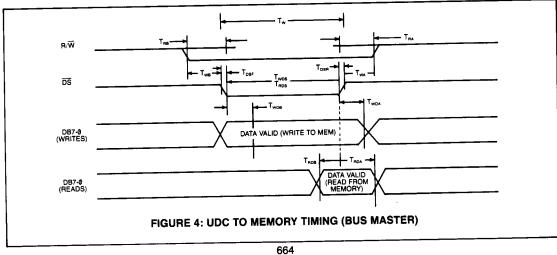

| 17,18<br>19,20<br>21,23<br>24,25 | Data Bus 7-0 | DB7-0           | All system processor reads and writes, (including status reads, initialization, disk parameters, and commands) are 8 bit transfers which utilize these lines.  When the UDC is accessing memory, data is input or output on these lines.  Data on these lines is valid only when DATA STROBE (DS) is active low. |  |

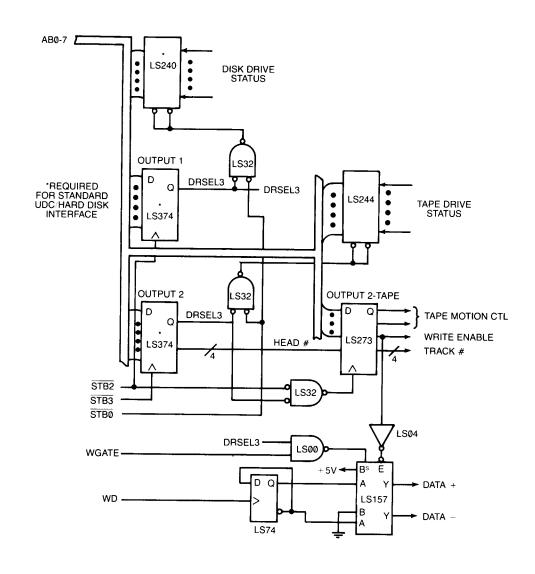

| 8-15                             | Aux Bus 7-0  | AB7-0           | These 8 pins are used to output drive control signals and DMA Address information.  Additionally, these pins are used to input drive status information.                                                                                                                                                         |  |

| 4                                | Command/Data | C/D             | During processor to UDC communications, this input is used to indicate whether a command or data transfer will follow.  If this pin is low, data may be written to, or read from, the internal data registers. If this pin is high, the processor may write commands or read command results from the UDC.       |  |

| 7                                | Read/Write   | R/W             | When the processor is communicating to the UDC, a high on this input line indicates a (processor) request for a UDC read operation, and a low indicates a (processor) request for a write operation.                                                                                                             |  |

|                                  |              |                 | R/W C/D Operation                                                                                                                                                                                                                                                                                                |  |

|                                  |              |                 | 0         0         Write to register file           0         1         Write to command reg.           1         0         Read from register file           1         1         Read Interrupt Status Register                                                                                                |  |

|                                  |              |                 | During UDC initiated operations, this pin becomes an output, and is used to indicate a read operation (logic 1) or write operation (logic 0) to external memories.                                                                                                                                               |  |

| PIN NO. | NAME            | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6       | Data Strobe     | DS     | This active low pin functions as both an input and output. When the processor is writing to the UDC, the trailing edge of an active (low) signal applied to this pin ind cates that the data on DB7-0 is valid, and the data is latched into the appropriate UDC register on the rising edge.  When the processor is reading from the UDC, the trailing edge of an active (low) signal applied to this pin is used to clock out the desired UDC register on to DB7-0 During UDC initiated DMA operations, the UDC drives this pin low to either read o write data from memory. On DMA read cycles, data is clocked in on the trailing edge. On DMA write operations, the data on DB7-0 is valid anytime this pin is active (low).  When this pin is high (logic 1), DB7-0 return to a high impedance state. |  |

| 2       | Interrupt       | INT    | This active high output is used by the UDC whenever it wants to interrupt the processor. The interrupt pin is reset to its inactive (low) state when the UDC interrupt status register is read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

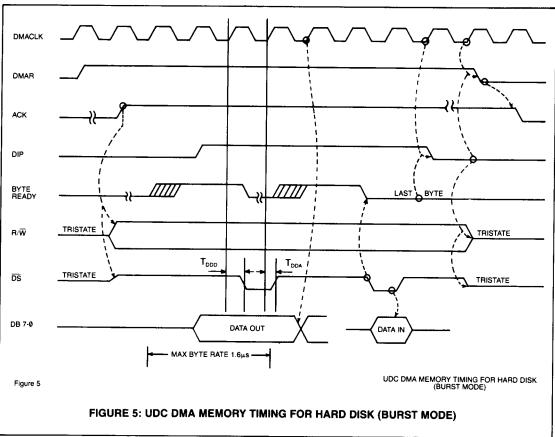

| 30      | DMA In Progress | DIP    | This active high output becomes active whenever the UDC is actually performing a DMA operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

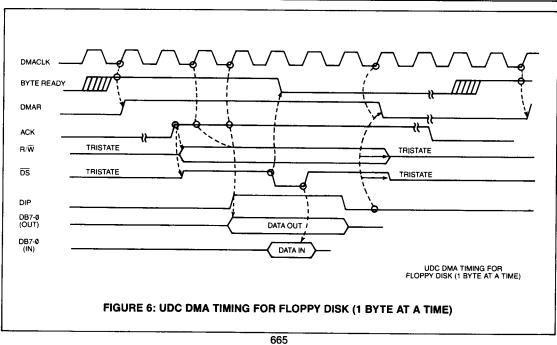

| 28      | DMA Request     | DMAR   | This active high output becomes active whenever the UDC requires the system bus to perform a memory cycle, and ACK is inactive. During hard disk operations, it remains active until the sector transfer is complete.  During floppy disk operations, it is active for 1 byte transfer time.  The UDC shows that it has released the system bus by resetting this signal to its inactive (low) state.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 5       | Acknowledge     | ACK    | This active high signal from the processor tells the UDC that the processor has released the system bus and the UDC may access system memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

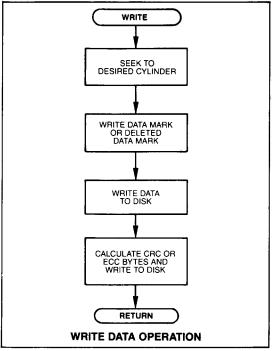

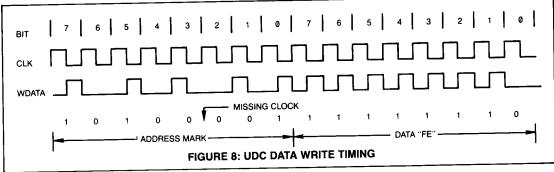

| 37      | Write Data      | WDATA  | This pin is used to output serial data from the UDC to the drive, in either FM or MFM format. In both cases, data is output with the most significant bit first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

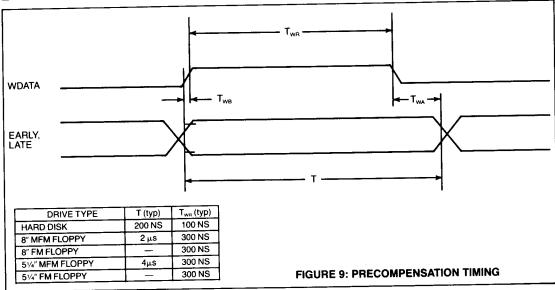

| 38      | Late            | LATE   | This output (when active high) indicates that the current flux transition appearing on WDATA is to be written late.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 39      | Early           | EARLY  | This output (when active high) indicates that the current flux transition appearing on WDATA is to be written early.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

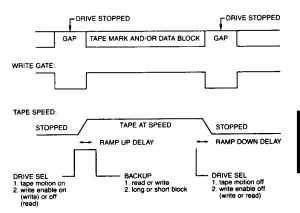

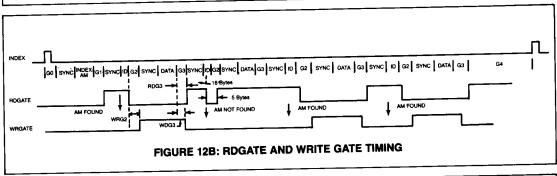

| 27      | Write Gate      | WGATE  | This output (when active high) indicates the drive should allow a write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

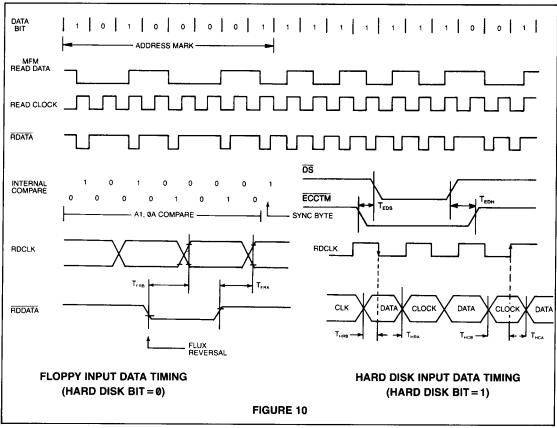

| 40      | Read Data       | RDATA  | This input pin contains the serial bit stream read from the drive, in either FM or MFM format. Media flux reversals are indicated by a negative transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 3       | Read Clock      | RCLK   | This input is generated by the external data separator. Its frequency should self-<br>adjust to the variations in bit width in the data stream from the drive. This clock<br>supplies a window to indicate half-bit-cell boundaries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

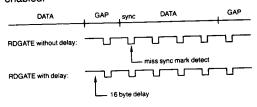

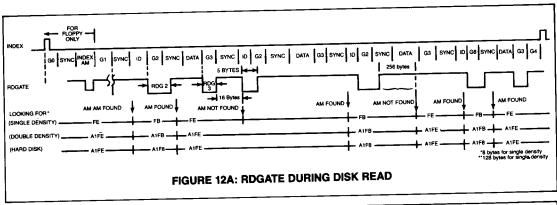

| 26      | Read Gate       | RDGATE | This output pin is used to enable the external data separator, compensate for write to read recovery time of the drive, and filter out the write splice in gaps 2 and 3. The timing of this signal is dependent upon the type of drive (hard or floppy) being used.  RDGATE is inactive at all times except when the UDC is actually performing a read operation or an internal ECC operation.                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 29      | ECC Time        | ECCTM  | When the UDC is used in external ECC mode, this output pin becomes active (low) during the time the UDC is reading the ECC bytes from memory or external ECC chip, when executing a WRITE command.  It is also active during internal ECC correction operations, and for either one (write) or two (read) byte times after DIP (pin 30) becomes inactive following a sector transfer. This shows the system processor when it should service the UDC buffer.                                                                                                                                                                                                                                                                                                                                                |  |

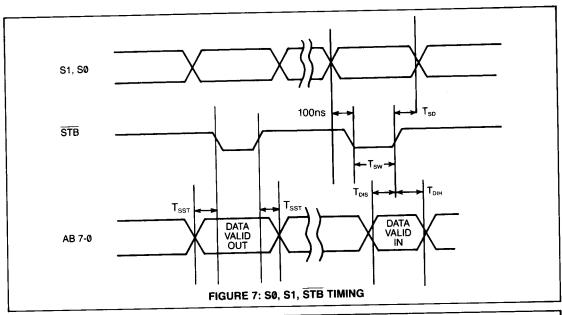

| 32,35   | Select 1,0      | S1,S0  | These active high outputs are used by external logic to select either the source or destination for data transfers occuring via AB7-0. The following table defines the specific transfer being called for by the UDC. (Note that S1-0 are valid only when STB is active low.)  STB S1 S0 AB7-0 Activity  1 X X S1,S0 Invalid 0 0 0 UDC inputs Drive Status Signals 0 0 0 1 UDC outputs DMA address bytes 0 1 0 UDC outputs OUTPUT 1 signals 0 1 1 UDC outputs OUTPUT 2 signals                                                                                                                                                                                                                                                                                                                              |  |

| PIN NO. | NAME         | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 34      | Strobe       | STB    | This active low output indicates when the host processor should read or write to AB7-0, as indicated by S1-0.  When AB7-0 are used as outputs from the UDC, data is valid anytime this signal active (low).  When AB7-0 are used as inputs to the UDC, data is clocked in on the rising edge of this signal.                                                                                                                                                                                                                                                                                                           |  |

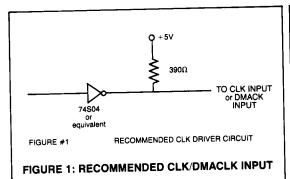

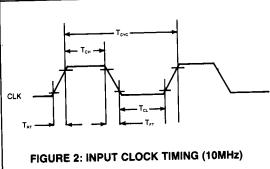

| 36      | DEVICE CLOCK | CLK    | This input is the double frequency clock used by the UDC for all internal timing operations.  Eight inch hard disk drives (with a nominal bit time of 230 ns) require an input of 8.696 MHz (115 ns period).  5.25" hard disks (with a nominal bit time of 200 ns) require a 10 MHz input (100 ns period).  Eight inch, 5.25" and 3.5" floppy drives all require a 10 MHz clock, which is internally prescaled by the UDC to the correct frequency, as determined from the Drive Select command and MODE register.  This input requires an external pull-up resistor, as it is not TTL-level compatible. See figure 2. |  |

| 31      | Reset        | RST    | This active low input will force the UDC into the following known state:  INT-Inactive low WDATA-Inactive low ECCTM-Inactive high DMAR-Inactive low EARLY-Inactive low C/D-Input AB7-0-Input LATE-Inactive low R/W-Input DB7-0-Input WGATE-Inactive low DIP-Inactive low RDGATE-Inactive low RDGATE-Inactive low DS-Input An active low on this pin has the same effect as a RESET Command.                                                                                                                                                                                                                            |  |

| 33      | DMA Clock    | DMACLK | All UDC DMA operations will be synchronized to this clock input. Three DMACLK periods are required for each DMA byte transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

### **OVERVIEW OF UDC REGISTERS**

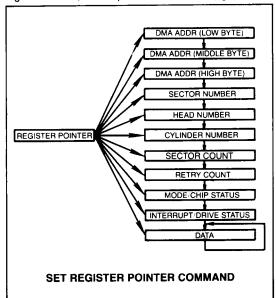

The HDC 9234 has three types of internal, processor addressable registers; Read/Write, Read Only, and Write Only. These registers are addressed by an internal register pointer that is set by the SET REGISTER POINTER command.

All register data is passed to and from the UDC via the data bus (DB7-0).

The internal register pointer is automatically incremented with each register access until it points to the DATA Register. This insures that all subsequent register accesses will address the DATA register.

### PROCESSOR ACESSIBLE REGISTERS

| REGISTER ADDR | WRITE                           | READ              |

|---------------|---------------------------------|-------------------|

| 0             | DMA7-0                          | DMA7-0            |

| i             | DMA15-8                         | DMA15-8           |

| 2             | DMA23-16                        | DMA23-16          |

| 3             | Desired Sector                  | Desired Sector    |

| 4             | Desired Head                    | Current Head      |

| 5             | Desired Cylinder                | Current Cylinder  |

| 6             | Sector Count                    | Temporary Storage |

| 7             | Retry Count                     | Temporary Storage |

| 8             | Mode                            | Chip Status       |

| 9             | Interrupt/Command<br>Terminator | Drive Status      |

| Α             | Data/Delay                      | Data              |

| COMMAND       | Current Command                 | Interrupt Status  |

Three internal registers (OUTPUT 1, OUTPUT 2, and INPUT DRIVE STATUS) which are not directly addressable by the processor are accessed by the UDC. The information contained in these registers is used in disk interfacing and is input or output on UDC Pins AB7-0. The following table describes these registers and the signals they output or input on AB7-0.

#### **UDC ADDRESSABLE REGISTERS**

| DRIVE STATUS REGISTER                                             | (input) Select Pins S1 = 0, S0 = 0                            |

|-------------------------------------------------------------------|---------------------------------------------------------------|

| AB6—Index Pulse AB5—Seek Complete AB1—Drive Ready AB0—Write Fault | AB4—Track 00 AB3—User Defined AB7—ECC Error AB2—Write Protect |

| OUTPUT 1 (Output) AB7—Drive Select 3 AB5—Drive Select 1 AB3—Programmable Outputs (see text) AB1—Programmable Outputs | Select Pins S1 = 1, S0 = 0<br>AB6—Drive Select 2<br>AB4—Drive Select 0<br>AB2—Programmable Outputs<br>AB0—Programmable Outputs |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| AB1—Desired Head (Bit 1) AB0—Desired Head (Bit 0) |

|---------------------------------------------------|

|---------------------------------------------------|

Additionally, several registers (DMA7-0, DMA15-8, DMA23-16, DESIRED SECTOR, DESIRED CYLINDER, SECTOR COUNT, and RETRY COUNT) serve an alternate purpose. These registers are used by the FORMAT TRACK command to hold parameters. This alternate register utilization is described in detail under the FORMAT TRACK command.

#### **DESCRIPTION OF UDC REGISTERS**

#### **DMA 7-0**

(R/W Register; Address 0)

This 8-bit read/write register is loaded with the low order byte (MSB in bit 7) of the DMA buffer memory starting address.

#### **DMA 15-18**

(R/W Register; Address 1)

ster is loaded with the middle

This 8-bit read/write register is loaded with the middle order byte (MSB in bit 7) of the DMA buffer memory starting address.

DMA 23-16 (R/W Register; Address 2)

This 8 bit read/write register is loaded with the high order

byte (MSB in bit 7) of the DMA buffer memory starting

address.

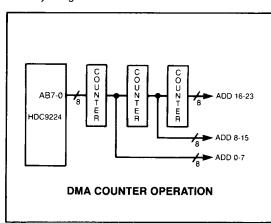

Prior to the data transfer portion of a read or write command, the UDC writes the contents of the DMA registers to an external counter. This transfer (from the registers to the external counter) is accomplished by the UDC with 3 separate outputs on AB7-0, with the contents of DMA 24-16 being transfered first. In memory areas that require less than 24 bit addressing, the higher order bits are overwritten. The external counter must be incremented with the UDC's DS signal after each byte transfer.

If, during read operations, an error is detected during the data transfer, a retry will occur (if so programmed), and the three DMA registers will re-initialize the external counter to the original starting address.

During multiple sector read/write operations, the DMA address contained in the DMA registers will be incremented by the size of the sector selected at each sector boundary. This ensures that during read operations the address contained in the DMA registers always corresponds to the proper memory starting address of the sector currently being read.

#### **DESIRED SECTOR REGISTER**

(R/W Register; Address 3)

This 8-bit read/write register is loaded with the starting sector number of a multiple sector read/write operation. Except for the last sector of the operation, this register is incremented after each sector is written or read without error.

If the UDC terminates a command because of an error, this register will normally contain the bad sector number, and may be read by the processor.

#### **DESIRED HEAD REGISTER**

(Write Register; Address 4)

The contents of this register are compared to the disk sector's ID Field when verifying a seek operation.

For the PC/AT format, this register is loaded with a 2-bit sector size, and 4-bit head number.

BIT 7 Bad Block Mark (always 0) BITS 6.5 Sector Size

| 6   | 5 | SECTOR SIZE |  |

|-----|---|-------------|--|

| 0   | 0 | 256         |  |

| 0   | 1 | 512         |  |

| 1   | 0 | 1024        |  |

| ] 1 | 1 | 128         |  |

BIT 4 Always 0

BIT 3-0 Desired Head Number

For the SMC format, this 8-bit write only register is loaded with the 4-bit head number and the upper 3-bits of the desired cylinder number.

BIT 7 Bad Block Mark (always 0).

BITS 6-4 MSBs of the Desired Cylinder number.

BITS 3-0 Desired Head Number.

The desired head number is output on AB3-0 during OUTPUT 2 times.

#### DESIRED CYLINDER REGISTER (Write Register; Address 5)

This 8-bit write only register is loaded with the 8 low order bits of the desired cylinder (MSB in Bit 7). Combined with the 3 high order bits loaded into the DESIRED HEAD REGISTER, these 11 bits form the desired cylinder number, which is checked by read and write operations during the Check ID portion of the command.

#### SECTOR COUNT REGISTER (Write Register; Address 6)

This 8-bit write only register is loaded with the number of sectors to be operated on by the read or write command. This allows multiple sectors on the same cylinder to be either written or read.

# RETRY COUNT REGISTER (Write Register; Address 7)

This 8-bit write only register is loaded with the number of times the UDC should retry to read a data field before reporting an error. Additionally, this register is loaded with the user programmable output signals that the UDC outputs on AB0-3 during OUTPUT 1 times.

The retry count is loaded (in 1's complement format) into the 4 most significant bits of this register.

The user programmable output signals are loaded into the 4 least significant bits of the register.

BITS 7-4 Desired Retry Count (in 1's complement format)

BITS 3-0 User Programmable Output Signals

MODE REGISTER (Write Register; Address 8)

This 8-bit write only register defines the operating mode of the LIDC as follows:

of the UDC as follows: BIT 7 (DRIVE DATA TYPE)

This bit determines how the UDC decodes data from the drive.

BIT 7 = (1): UDC configured for hard disk use. (Level transitions)

BIT 7 = (0): UDC configured for floppy use. (Pulse inputs)

### STEP RATES FOR DOUBLE DENSITY (MFM) OPERATION

| DRIVE TYPE   |     |     | 5.25" HARD DISK | 8" FLOPPY | 5.25" FLOPPY |

|--------------|-----|-----|-----------------|-----------|--------------|

| DB2          | DB1 | DB0 | STEP RATE       | STEP RATE | STEP RATE    |

| 1            | 1   | 1   | 3.2 ms          | 32 ms     | 64 ms        |

| i            | i   | ò   | 1.6 ms          | 16 ms     | 32 ms        |

| i            | Ó   | ť   | 0.8 ms          | 8 ms      | 16 ms        |

| i            | ŏ   | Ò   | 0.4 ms          | 4 ms      | 8 ms         |

| ń            | ĭ   | ĭ   | 0.2 ms          | 2 ms      | 4 ms         |

| ň            | i   | Ò   | 0.1 ms          | 1 ms      | 2 ms         |

| ŏ            | Ò   | Ĭ   | 0.05 ms         | 0.5 ms    | 1 ms         |

| 0            | 0   | 0   | 21.8 us         | 218 us    | 436 us       |

| Pulse Width: |     |     | 11.2 us         | 112 us    | 224 us       |

### (DOUBLE ALL OF THE ABOVE TIMES FOR SINGLE DENSITY (FM) OPERATIONS.)

### BITS 6,5 (CRC/ECC Enable Code)

These bits determine the error detection/correction code generated and checked by the UDC. In addition, they enable the Write Long command.

| DB6 | DB5 | CODE GENERATED/CHECKED                 |

|-----|-----|----------------------------------------|

| 0   | 0   | CRC                                    |

| 0   | 1   | Enable Write Long                      |

| 1   | 0   | Internal 32 bit ECC without correction |

| 1   | 1   | Internal 32 bit ECC with correction    |

With internal ECC selected the UDC will transfer 4 extra bytes during reads and writes. Normal CRC checking is still done on all ID fields.

If ECC is not selected, then the UDC will perform CRC checks on both data and ID fields.

BIT 4 (Single or Double Density)

This bit determines whether the UDC will perform its operations in either single or double density.

BIT 4 = (1) Single Density (FM) Format

BIT 4 = (0) Double Density (MFM) Format

BIT 3 (ALWAYS 0)

BITS 2,1,0 (Step Rate Select)

These bits are programmed to select the desired drive step rate. Note that all step rates are determined by the type of drive and density selected, and are scaled from the CLK input.

The UDC can output extremely rapid step rate pulses if these bits are set to 000. This is useful when the UDC is controlling drives which support buffered seeks. For other speeds, please refer to the table above.

#### INTERRUPT/COMAND TERMINATION REGISTER (Write Register; Address 9)

This 8-bit write only register allows the programmer to mask out a number of conditions that would cause termination of a command. (Such termination occurs when the DONE bit in the INTERRUPT STATUS register is set.) One bit in this register also controls the generation of interrupts when either the DONE bit or the READY CHANGE bit in the INTERRUPT STATUS register go active.

#### BIT 7 (ALWAYS "1"

Setting this bit to "1" will cause the CRC register to preset to 1 for CRC generation and checking.

In the IBM® PC-AT mode, this bit should always be set to "1". Failure to do so may result in unreliable operation.

ID field CRC and data field CRC or ECC are generated and tested from the first A1 HEX byte in the ID field.

#### BIT 6 (ALWAYS "0")

This bit should always be set to "0" by the user. Failure to do this may result in unreliable operation.

BIT 5 (INT ON DONE)

If this bit is set (to "1"), an interrupt will occur when the DONE bit in the INTERRUPT STATUS register is set. If this bit is reset (to "0"), no interrupt will be generated for this condition.

#### BIT 4 (DELETED DATA MARK)

If this bit is set (to "1"), the DONE bit in the INTERRUPT STATUS register will be set when the DELETED DATA MARK bit in the CHIP STATUS register goes active, and the command will terminate when the current sector operation is completed.

#### BIT 3 (USER DEFINED)

If this bit is set (to "1"), the DONE bit in the INTERRUPT STATUS register will be set when the USER DEFINED status bit in the DRIVE STATUS register goes active, and the command will terminate when the current sector operation is completed.

#### BIT 2 (WRITE PROTECT)

If this bit is set (to "1"), the write or write format command in progress will terminate and the DONE bit in the INTER-RUPT STATUS register will be set when the WRITE PRO-TECT bit in the DRIVE STATUS register goes active.

#### BIT 1 (READY CHANGE)

If this bit is set (to "1"), an interrupt will occur when the READY CHANGE bit in the INTERRUPT STATUS register is set. If this bit is reset (to "0"), no interrupt will be generated for this condition.

The user should note that as a drive is selected or deselected, it is possible for the ready line from the drive to change state, and care should be taken in the design of the interrupt handler.

#### BIT 0 (WRITE FAULT)

If this bit is set (to "1"), the write or write format command in progress will terminate and the DONE bit in the INTER-RUPT STATUS register will be set when the WRITE FAULT status bit in the DRIVE STATUS register is set. The command in progress will terminate when the current sector operation is completed.

#### DATA/DELAY REGISTER (R/W Register; Address OAH)

This 8-bit read/write register serves three purposes. During UDC writes, data is placed in this register for recording to the disk. During UDC reads, recovered data is fetched from this register for storage into memory. All transfers occur via DB7-0, under DMA control.

Additionally, this register is loaded with the HEAD LOAD TIMER COUNT when the Drive Select command is issued. (Note that the actual amount of head load time is this value, times a value predetermined by the UDC, based on the type of drive selected. For more information, please see the Drive Select command description.)

Finally, in the IBM® PC-AT mode, this register is used for a third purpose. If Implied Seek is enabled, this register is used by Seek/Read ID and Read/Write commands to control the UDC seek operation. The data in the Data/ Delay Register and the Current Cylinder Register are used to calculate the direction and step count for a seek.

Please note, the MSB's of the Desired Cylinder Number does not correspond to those written in the Disk ID field.

BITS 7.6 Always 0 BITS 5,4 Actual Sector Size

| 5 | 4 | Sector Size |  |

|---|---|-------------|--|

| 0 | 0 | 128         |  |

| 0 | 1 | 128<br>256  |  |

| 1 | 0 | 512         |  |

| 1 | 1 | 1024        |  |

BITS 3,2 Always 0 BITS 1,0 MSB's of Cylinder Number

| 1 | 0 | Cylinder Number |  |

|---|---|-----------------|--|

| 0 | Ó | 0 - 255         |  |

| 0 | 1 | 256 - 511       |  |

| 1 | 0 | 512 - 767       |  |

| 1 | 1 | 768 - 1023      |  |

#### COMMAND REGISTER (Write Register)

This 8-bit write only register is used to pass commands to the UDC. Valid commands are given to the UDC by setting C/D high and R/W active high, while strobing DS active (low).

#### CURRENT HEAD REGISTER (Read Register)

This 8-bit read only register is updated from the disk when valid ID field sync mark is found while executing a SEEK/ READ ID command.

IBM® PC-AT MODE

BIT 7 = 1 Last Sector read had BAD SECTOR bit set. = 0 Last Sector read had BAD SECTOR bit reset. BIT 6,5 Sector Size

| 6 | 5 | SECTOR SIZE |  |

|---|---|-------------|--|

| 0 | 0 | 256         |  |

| 0 | 1 | 512         |  |

| 1 | 0 | 1024        |  |

| 1 | 1 | 128         |  |

BIT 4 Always 0

BIT 3-0 Current Head Number (MSB in BIT 3)

#### **SMC AND FLOPPY MODES**

BIT 7 = 1 Last sector read had BAD SECTOR bit set.

= 0 Last sector read had BAD SECTOR bit reset.

BITS 6-4 Three most significant bits of the current cylinder. (Most significant bit in BIT 6)

BITS 3-0 Current Head Number (MSB in bit 3).

#### **CURRENT CYLINDER REGISTER** (Read Register: Address 5)

This 8-bit read only register is updated from the disk when a valid ID field sync mark is found while executing a read ID field command sequence. This register will contain the 8 least significant bits of the cylinder ID number, as specified during formatting. (The 3 most significant bits of the 11 bit cylinder ID number are contained as part of the CURRENT HEAD REGISTER.)

#### **CURRENT IDENT BYTE REGISTER** (Read Register: Address 6)

This 8-bit read only register reads the Ident Byte from the disk during the Read ID command sequence. The Current Ident Byte is written to the disk during the format, changing as specified below.

| IDENT BYTE | CYLINDER NUMBERS       |

|------------|------------------------|

| FE         | 0 - 255                |

| FF<br>FC   | 256 - 511<br>512 - 767 |

| FD         | 768 - 1023             |

#### INTERRUPT STATUS REGISTER (Read Register)

This 8-bit read only register contains status information associated with interrupt conditions and errors that occur during disk operation. This register is read by setting C/D high, and R/W high.

When the Interrupt Status register is read, the INT output signal from the UDC will be reset (to an inactive low level).

BIT 7 (INTERRUPT PENDING)

A "1" indicates that either DONE bit or READY CHANGE bit has gone active. The user may disable these interrupts by setting the appropriate bits in the INTERRUPT/COM-MAND TERMINATION, REGISTER. This bit is reset (to "0") by reading the Interrupt Status register.

#### BIT 6 (DMA REQUEST)

A "1" indicates that the UDC requires a data transfer either to or from its data register. This bit is reset (to "0") by the data transfer.

#### BIT 5 (DONE)

A "1" indicates that the current command is completed. This bit is reset (to "0") when a new command is issued.

#### BIT 4,3 (COMMAND TERMINATION CODE-(Valid only when DONE is set)

These two bits indicate the command termination conditions:

| BIT 4 | BIT 3  | CONDITIONS                                                              |

|-------|--------|-------------------------------------------------------------------------|

| 0     | 0<br>1 | Successful command termination<br>Execution error in READ ID            |

| 1 1   | 0      | Sequence Execution error in SEEK Sequence Execution error in DATA field |

More detailed command termination error information is obtained by reading the Chip Status register.

BIT 2 (READY CHANGE)

A "1" indicates that the "ready" signal from the drive has experienced a low-to-high or high-to-low transition. (This shows that the drive has either become ready or become not ready.) This bit is reset (to "0") by reading the Interrupt Status register.

### BIT 1 (OVERRUN/UNDERRUN)

A "1" indicates that a overrun or underrun condition has

occured during a read or write command. These conditions occur when the UDC does not receive an acknowledge (to a DMA request) by the time a byte is ready for transfer to or from the processor.

This bit can only be reset (to "0") with a RESET command or a high on the RESET pin.

#### BIT 0 (BAD SECTOR)

A "1" indicates that a bad sector (as indicated from the MSB of the head ID byte in the ID field) has been encountered. This bit is reset when a new command is issued, or a good sector is read.

#### CHIP STATUS REGISTER (Read Register; Address 8)

This 8-bit read only register supplies additional chip status information. The information in this register is only valid between the time that the DONE bit is set in the INTER-RUPT STATUS register and the time when the next command is issued to the UDC.

#### BIT 7 (RETRY REQUIRED)

If a retry was attempted by the UDC during the execution of any read or write command, this bit is set (to "1").

#### BIT 6 (ECC CORRECTION ATTEMPTED)

If the internal ECC circuitry has attempted to correct a bad sector, this bit is set (to "1").

#### BIT 5 (CRC/ECC ERROR)

If the UDC detects a CRC error or an ECC error this bit is set (to "1").

#### BIT 4 (DELETED DATA MARK)

If the UDC reads a deleted data mark in the ID field, this bit is set (to "1"), otherwise it is reset (to "0").

#### BIT 3 (SYNC ERROR)

If the UDC does not find a sync mark when it is attempting to read either an ID or data field, then this bit is set (to "1"). The command being executed will terminate when this bit is set

### BIT 2 (COMPARE ERROR)

If the information contained in the DESIRED HEAD and DESIRED CYLINDER registers does not match that contained in an ID field on the disk, this bit is set (to "1"). The command being executed will terminate when this bit is set.

#### BIT 1,0 (PRESENT DRIVE SELECTED)

These two binary encoded bits represent the drive currently selected and correspond to the Drive Select bits set in the Output 1 and Output 2 latches.

| BIT 1            | BIT 1 BIT 0 DRIVE SELECTED |                  |

|------------------|----------------------------|------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>0                | 0<br>1<br>2<br>3 |

#### **DRIVE STATUS REGISTER**

#### (Read Register; Address 9)

This 8-bit read only register contains status information generated by the drives, external ECC Chip (if any), and a user definable input to the UDC from the drive.

To save pins on the UDC, the 8 status lines are input on AB7-0 and are latched in this internal register. The UDC will update this register whenever it is not using AB7-0 to output DMA counter values, OUTPUT 1, or OUTPUT 2 data. When configured as described below, the UDC will input drive status signals and interpret them as follows. In all cases, a logic "1" is considered the active input.

#### BIT 7 (ECC ERROR)

This bit is set (to "1") when the ECC ERROR signal is generated by an external ECC chip. This signal is input to the UDC on AB7.

#### BIT 6 (INDEX)

This bit is set (to "1") when the INDEX signal from the selected drive is active. Typically, index pulses from the drives are active for 10us-100us for each disk revolution. This signal is input to the UDC on AB6.

#### **BIT 5 (SEEK COMPLETE)**

This bit is set (to "1") when the SEEK COMPLETE signal from the selected drive is active. This bit will go active when the heads of the selected drive have settled over the desired track (at the completion of a seek).

When a drive supplies this signal, reading and writing should not be attempted until SEEK COMPLETE is set (to "1"). This signal is input on AB5.

For floppy disk operation, where the drives normally do not provide this signal, a retriggerable one shot could be used to generate a SEEK COMPLETE signal (if desired).

#### BIT 4 (TRACK 00)

This bit is set (to "1") when the TRACK 00 signal from the selected drive is active. This indicates that the heads on the selected drive are positioned over track 0. This signal is input on AB4.

#### BIT 3 (USER DEFINED)

This bit is set (to "1") when the USER DEFINED signal is active. This signal is input on AB3.

#### BIT 2 (WRITE PROTECT)

This bit is set (to "1") when the WRITE PROTECT signal from the selected drive is active. When set, this bit indicates that the disk in the selected drive is write protected. This signal is input on AB2.

#### BIT 1 (READY)

This bit is set (to "1") when the READY signal from the selected drive is active. When set, this bit indicates that the drive is ready to execute commands. This signal is input on AB1.

#### BIT 0 (WRITE FAULT)

This bit is set (to "1") when the WRITE FAULT signal from the selected drive is active. This signal, when active, indicates that a condition exists at the drive that would cause improper writing on the disk. This signal is input to the UDC on ABO.

### **TEMPORARY STORAGE REGISTERS**

The UDC contains two temporary storage registers, used by the UDC for internal operations. The host processor should not attempt to read or modify these registers, as unpredictable results may occur.

#### **UDC COMMAND OVERVIEW**

The HDC 9234 has 16 high-level commands that provide the user with a high degree of flexibility and control. All of the commands for the UDC can be thought of as falling into one of two basic groups.

The first group handles the "housekeeping" required by the drives and the UDC itself. These commands are:

RESET STEP IN 1 CYLINDER DRIVE SELECT DESELECT DRIVES

STEP OUT 1 CYLINDER SET REGISTER POINTER RESTORE DRIVE POLL DRIVES

The second group comprises the "READ/WRITE" functions required in a magnetic disk subsystem. These commands are:

SEEK/READ ID FORMAT TRACK READ TRACK

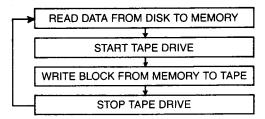

TAPE BACKUP (READ/ WRITE)

READ SECTORS LOGICAL

READ SECTORS PHYSICAL WRITE SECTORS LOGICAL

An internal status byte, which contains the BAD SECTOR, DELETED DATA and OVER/UNDER RUN bits, along with the current state of the READY, WRITE PROTECT, WRITE FAULT, and USER DEFINED lines, is checked at various times during command execution.

This internal status byte is examined before the execution of all READ/WRITE commands, and is also checked just prior to the completion of all commands (except for RESET, where its values would be meaningless.)

This byte is also checked by the UDC between sector operations during the execution of READ LOGICAL, READ PHYSICAL, WRITE LOGICAL and WRITE PHYSICAL commands.

The UDC makes decisions regarding command termination and interrupt generation based on the contents of this status byte, and the state of the bits in the INTERRUPT/COMMAND TERMINATION register. (Note that "write protect" and "write fault" status may cause command termination only during write and format operations.)

All commands (except RESET) terminate with the DONE bit in the INTERRUPT STATUS register being set. This bit may also be considered to be an inverted "busy" line, as the UDC resets it upon receipt of a valid command.

During all READ/WRITE group commands (except FOR-MAT TRACK and BACKUP), the UDC utilizes some common command execution sequences. Prior to entering each sequence the UDC sets the COMMAND TERMINATION bits (in the INTERRUPT STATUS register) to a known state. If a command fails to execute properly, these bits may then be used to determine where the command aborted.

The sequences common to the READ/WRITE group commands are as follows:

READ ID FIELD (Command Termination Code = 0-1)

First, the UDC attempts to find an ID Field Sync mark.

If no sync mark is found within 33,792 byte times (byte time = time to read one byte from the type of drive selected), the SYNC ERROR bit (in the CHIP STATUS register) is set (to "1"), and the command is terminated.

During this phase, the UDC will raise and drop RDGATE up to 256 times (as it attempts to read each sector on the cylinder).

After the ID Field is found, the UDC reads it and updates it CURRENT HEAD and CURRENT CYL-INDER registers. This information was written to the disk during formatting.

Next, the UDC checks the CRC of the ID field which was read. If it is incorrect, the UDC sets (to "1") the CRC ERROR status bit (in the CHIP STATUS register) and terminates the command.

If the CRC is correct, the UDC then calculates the direction and number of step pulses required to move the head from the current cylinder to the cylinder specified in the DESIRED HEAD REGISTER. These pulses, and the direction bit are output during the OUTPUT 2 times.

If a command should terminate while in the sequence, the COMMAND TERMINATION bits will be set to 0-1.

VERIFY (Command Termination Code = 1-0) After the UDC has read the ID Field, it attempts to verify that it has found the correct cylinder. To do this, the UDC tries to find an ID Field sync mark on the selected

disk. If the UDC is unable to find an ID Field sync mark within 33,792 byte times, the SYNC ERROR bit (in the CHIP STATUS register) is set to "1", and the command is terminated.

The UDC, after finding the ID Field sync mark, then reads the ID field and compares the information on the disk to the information contained in the DESIRED CYLINDER, DESIRED HEAD and DESIRED SECTOR registers.

The UDC will hunt for sync marks and read ID fields until the desired sector is found. If the desired sector is not located within 33,792 byte times, then the COMPARE ERROR bit (in the CHIP STATUS register) is set to "1", and the command is terminated.

After the correct sector is found, the UDC checks the CRC for the sector ID Field. If this is found to be incorrect, the UDC sets to "1" the CRC/ECC ERROR bit in the INTERRUPT STATUS register, and the command is terminated.

(When the UDC is executing a READ PHYSICAL or WRITE PHYSICAL command, ID Fields are checked only until the first sector to be transfered is found. No ID Field checking is performed on subsequent sectors, although CRC checking is done.)

If a command should terminate while in this sequence, the COMMAND TERMINATION bits will be set to 1-0.

#### 3. DATA TRANSFER

(Command Termination Code = 1-1)

If a READ PHYSICAL or READ LOGICAL command is being executed, the UDC will try to find a data sync mark (FBhex or F8hex) on the disk. If the sync mark found is F8h, then the UDC will set the DELETED DATA MARK bit in the CHIP STATUS register.

After a data sync mark is found, the UDC then updates its CURRENT HEAD and CURRENT CYLINDER registers from the information found on the disk and initiates a DMA request. If the host processor does not respond to the request within 1 byte time, then the UDC will set to "1" the OVER/UNDERRUN status bit in the INTERRUPT STATUS register, and the command will terminate.

Using DMA, the UDC transfers a sector's worth of data, and then reads the ECC and/or CRC bytes. If a CRC error or uncorrectable ECC error is detected, the UDC will decrement the RETRY REGISTER, set the RETRY REQUIRED status bit (in the CHIP STATUS register), and return to the VERIFY sequence.

If the UDC cannot read the sector, and the count in the ENTRY COUNT register has expired, then the CRC/ECC Error bit (in the CHIP STATUS register) is set, and the command terminates.

During a multi-sector transfer, the UDC updates the DMA registers after all sector operations, including the last one, and the SECTOR COUNT register is decremented. If the SECTOR COUNT register equals 0, then the command is terminated. If the SECTOR COUNT register is not equal to 0, then the UDC will increment the DESIRED SECTOR register, re-initialize the RETRY COUNT register (to its original value) and return to the VERIFY sequence.

If a command should terminate while in this sequence, the command termination bits will be set to 1-1.

#### **COMMAND DESCRIPTION**

#### RESET

(Hex Value = 00)

This command causes the UDC to return to a known state. This command allows the system software to reset the chip, and has the same effect as RST input becoming active.

MULTIPLE SECTOR PERFORM DATA TRANSFER TO/FROM DISK UPDATE EXTERNAL DMA ADDRESS COUNTERS DECREMENT SECT( COUNT YES COUNT EQUAL RETURN NO INCREMENT DESIRED SECTOR NUMBER **MULTIPLE SECTOR READ OPERATIONS**

#### DESELECT DRIVE

(Hex Value = 01)

This command causes all of the drive select bits (Drivé Select 0-3) in the OUTPUT 1 and OUTPUT 2 registers to become inactive.

RESTORE DRIVE (Hex Values = 02, 03)

This command will cause the HDC 9234 to output step pulses to the selected drive, so as to move the head back

pulses to the selected drive, so as to move the head back to Track 00. Before each step pulse, the UDC first checks the TRK00 and READY bits in the DRIVE STATUS register. If TRK00 is active (high) or READY is inactive (low), then the UDC will terminate the command.

The UDC will output up to 4096 step pulses. If the drive does not respond with an active (high) TRK00 signal within this period, the UDC will terminate the command with the DONE bit set (to "1") and the COMMAND TERMINATION CODE

bits set to 1-0. (These bits are contained in the INTER-**RUPT STATUS register.)**

This command takes two forms:

| COMMAND BYTE | RESULT                                                                                                                                                                                        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02           | The command will terminate, and an inter-<br>rupt generated after the UDC has issued the<br>step pulses.                                                                                      |

| 03           | The command will terminate, and an inter-<br>rupt generated after the drive has provided<br>a SEEK COMPLETE signal to the UDC.<br>(This is useful in systems with "buffered<br>seek" drives.) |

This command uses the step rate value loaded into the MODE register.

STEP IN 1 CYLINDER (Hex Values = 04, 05)

This command will cause the HDC 9234 to issue one step pulse towards the inner most track. This command is generally used during track formatting, and takes two forms:

| COMMAND BYTE | RESULT                                                                                                                                                                          |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 04           | The command will terminate, and an inter-<br>rupt generated after the UDC issues the<br>step pulse.                                                                             |  |

| 05           | The command will not terminate until the UDC recognizes the SEEK COMPLETE signal from the selected drive. Upon recognition of SEEK COMPLETE the UDC will generate an interrupt. |  |

This command uses the step rate value programmed into the MODE register.

STEP OUT 1 CYLINDER (Hex Values = 06, 07) This command will cause the HDC 9234 to issue one step pulse towards the outer most track (Track 00). This command is generally used during track formatting, and takes two forms:

| COMMAND BYTE | RESULT                                                                                                                                                                                |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 06           | This command will terminate, and an inter-<br>rupt generated after the UDC issues the<br>step pulse.                                                                                  |  |

| 07           | This command will not terminate until the UDC recognizes the SEEK COMPLETE signal from the selected drive. Upon recognition of the SEEK COMPLETE, the UDC will generate an interrupt. |  |

This command uses the step rate value programmed into the MODE Register.

#### **POLL DRIVES** (Hex Values = 10 thru 1F)

This command polls the drives for a SEEK COMPLETÉ signal allowing the user to perform simultaneous seeks on up to four drives. Polling is enabled by setting (to 1) the appropriate bit in the command word: bit 0 for drive 0 thru to bit 3 for drive 3.

This command executes as follows:

The UDC will output a drive select for the first drive in the polling sequence and look for a SEEK COM-PLETE status input from the polled drive. If the polled drive has not completed a seek, then this line remains low (logic 0), and the UDC selects the next drive in the polling sequence. This continues until the UDC detects a SEEK COMPLETE signal from a drive, which causes the DONE bit in the Interrupt Status register to be set, and the command terminates.

The UDC will continue to select the drive that produced the SEEK COMPLETE signal, allowing the user to read the DRIVE STATUS register to determine which drive caused the command termination.

The POLL DRIVES command must be preceded by SEEK or DESELECT. In normal use, a SEEK command would precede the POLL DRIVES command. In those cases where another command (other than SEEK) has been issued to a drive in the polling sequence, it will be necessary to DESELECT that drive prior to issuing the POLL DRIVES command. This applies even if the selected drive was not included in the polling sequence.

#### **DRIVE SELECT**

(Hex Values = 20 thru 3F) This command will cause one of (up to) four drives to be selected for operation. Any previously selected drive is deselected by this command. Bits 0 and 1 in the command word indicate (in binary form) which of the (up to) four drives has been selected.

| ID WORD | DRIVE<br>SELECTED         |

|---------|---------------------------|

| DB0     |                           |

| 0       | Drive 0                   |

| 1       | Drive 1<br>Drive 2        |

| 1       | Drive 2                   |

|         | DB0<br>DB0<br>0<br>1<br>0 |

Decoded drive select signals are then placed on the data bus (via AB7-AB4) during OUTPUT 1 times and should be latched externally.

Since the HDC 9234 can interface both hard disks and floppy disks to a processor, the Drive Select command needs to also specify the type of drive being selected. Bits 2 and 3 in the command word are used to pass this information to the chip, and take the following form:

| COMMAND WORD |     |                                                                                                                                                                                                                     |  |  |

|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| COMMAND WORD |     | TYPE                                                                                                                                                                                                                |  |  |

| DB3          | DB2 | OF DRIVE                                                                                                                                                                                                            |  |  |

| 0            | 0   | Hard disk with IBM® PC-AT compatible format—512 Byte data field and 4 byte ID field per sector. No internal clock prescaling performed.                                                                             |  |  |

| 0            | 1   | Hard disk with user defineable format. This format allows a data field length of 128, 256, 512, 1024, 2048, 4096, 8192, or 16384 bytes with 5 byte ID field per sector. No internal clock pre-scaling is performed. |  |  |

| 1            | 0   | 8 inch floppy disk, with standard 4<br>byte (FM) or 5 byte (MFM) ID field.<br>An internal divider creates a 1 MHz<br>clock to be compatible with standard<br>disk data rates.                                       |  |  |

| 1            | 1   | 5.25 inch floppy disk, with standard 4<br>byte (FM) or 5 byte (MFM) ID field.<br>An internal divider creates a 500 KHz<br>clock to be compatible with standard<br>disk data rates.                                  |  |  |

NOTE: Microfloppy system designers should determine whether the drive they have chosen to use in the system is compatible with 8" floppy drives or 5.25" floppy drives, and use the appropriate values from the table above.

Note that eight inch Winchester-type drives require an 8.696 MHz system clock. All other drives require a 10 MHz system clock. It is not possible for the UDC to derive internally the clocks required for floppy disk operation from the 8.696 MHz clock required by 8 inch Winchester drives.

To insure compatibility with various drives, the HDC 9234 features a programmable head load timer. Head load delay may be inhibited by resetting the Delay Bit (Bit 4) in the Drive Select command word to 0. If Bit 4 is set (to 1), then the head load delay timer is configured with the value in the

DATA/DELAY register (Register A), multiplied by value shown below:

| DRIVE AND<br>FORMAT SELECTED                        |          | AD TIMER INCREMENT<br>Delay Enabled)                                        |

|-----------------------------------------------------|----------|-----------------------------------------------------------------------------|

| 5.25" HARD DISK<br>(Double Density)                 | 200 usec |                                                                             |

| 5.25" HARD DISK<br>(Single Density)                 | 400 usec |                                                                             |

| 8" FLOPPY                                           | 2 msec   | (The HEAD LOAD TIMER is set to a value                                      |

| (Double Density)<br>8" FLOPPY<br>(Single Density)   | 4 msec   | equal to this increment<br>times the number in the<br>DATA/DELAY register.) |

| 5.25" FLOPPY                                        | 4 msec   | DATA DEEAT TOGISTON                                                         |

| (Double Density)<br>5.25" FLOPPY<br>(Single Density | 8 msec   |                                                                             |

The Drive Select command also optimizes certain characteristics of the HDC 9234 for the type of drive selected.

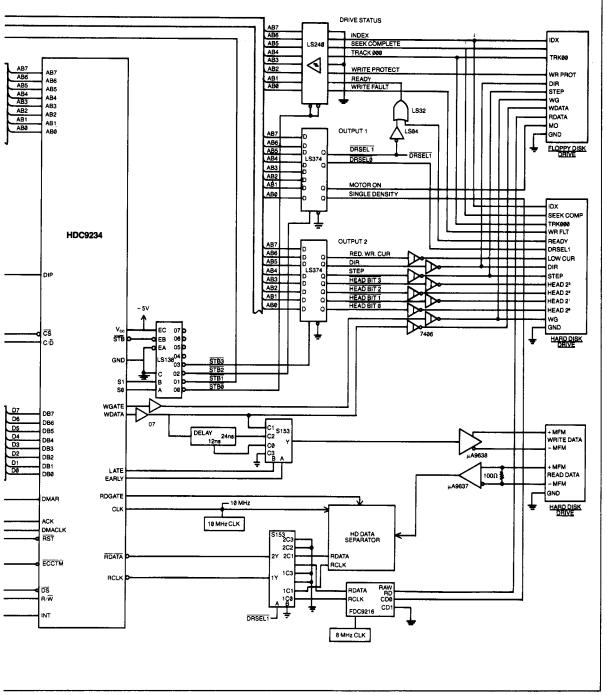

#### IF HARD DISK SELECTED:

- -DMA mechanism works in burst mode and the bus is held for the entire sector transfer.

- -The RDGATE and WRGATE output signals follow the timing relationships shown in Figures 12A and 12B.

- -The GAP lengths are as shown in Table 1.

#### IF FLOPPY DISK SELECTED:

- DMA mechanism transfers an 8-bit byte, and releases the bus.

- -The RDGATE and WRGATE output signals follow the timing relationships shown in Figures 12A and 12B.

- -The GAP lengths are as shown in Table 1.

- The CLK input clock is prescaled (internally) to create an internal clock compatible with the floppy disk data rates.

SET REGISTER POINTER (Hex Values = 40 to 4A) This command causes the register pointer to point to a register. The desired register number is loaded into the 4 least significant bits of the command word. (iMSB in BIT 3).

The register pointer is incremented by the UDC on each register access, until it points to the DATA register. This

reduces the number of times the user must set the register pointer during read and write operation.

Care should be taken to ensure that only valid register values are loaded into the command word. (Valid register numbers are 0 thru OAH.)

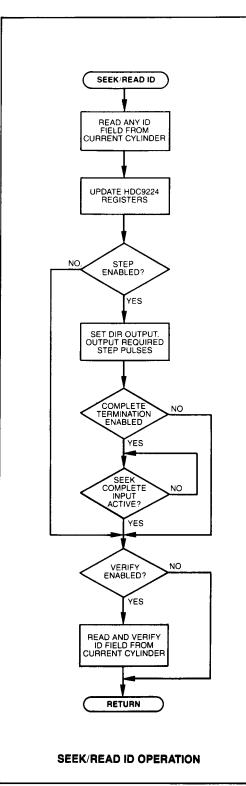

SEEK/READ ID (Hex Values = 50 to 57)

This command will cause the UDC to read the first sector ID field found from the currently selected drive, head, and cylinder. The MODE register should contain the correct value for step rate and density options.

After reading the ID field the UDC will examine the command word and execute the specified options. Bits 2 thru 0 in the command word are used to specify the following options:

- BIT 2 = 1 STEP ENABLE. The UDC will execute the step sequence, and position the head on the track specified by the DESIRED CYLINDER register.

- BIT 2 = 0 STEP DISABLE. No step pulses will be issued by the UDC.

- BIT 1 = 1 WAIT FOR COMPLETE. The UDC will proceed to the verify sequence only after the drive has issued a SEEK COMPLETE signal.

- BIT 1 = 0 DO NOT WAIT FOR COMPLETE. The UDC will proceed to the verify sequence after the last step pulse has been issued.

- BIT 0 = 1 VERIFY ID. The UDC will execute the VERIFY sequence after operations selected by the previous options have finished.

- BIT 0 = 0 DISABLE VERIFY ID. The UDC will not enter the VERIFY sequence. Instead, the command will terminate.

The order in which these options execute is: STEP, COM-PLETE, VERIFY ID. Any combination of these option bits may be specified in the command word.

READ SECTORS PHYSICAL (Hex Values = 58 and 59) This command will cause the UDC to read up to a full track from the disk. The user specifies the MODE, DESIRED CYLINDER, DESIRED HEAD, and DESIRED SECTOR along with the SECTOR COUNT. When using the IBM® PC-AT format, register A must also be initialized. The UDC will find the requested cylinder and sector and set up to begin the data transfer.

(If using drives which support buffered seeks, BITS 2-0 in the MODE SELECT register should be set to 0-0-0. This will cause the UDC to wait for a SEEK COMPLETE signal from the drive prior to entering the verify sequence.)

If a BAD SECTOR bit is read (from the sector ID field) the UDC will set the COMMAND TERMINATION bits (in the INTERRUPT STATUS register) to 1-0, and set the DONE bit (in the INTERRUPT STATUS register) to 1, and terminate the command.

After each sector is successfully read, the SECTOR COUNT register is decremented. If the SECTOR COUNT register is not yet equal to 0 the process is repeated for the next physical sector on the track. This command also will terminate if the Index pulse is received from the drive.

(Note that after the first sector is found, no further comparison is made against sector numbers found on the disk as the DESIRED SECTOR register value may not correspond to the next physical sector on the disk because of sector interleaving.)

This command takes two forms allowing the user to specify the desired transfer option. The options are specified by Bit 0 in the command word, and are:

BIT 0 = 1 TRANSFER ENABLE. The UDC will transfer the data fields to (external) memory, using DMA.

BIT 0 = 0 TRANSFER DISABLE. The UDC will NOT transfer any data to (external) memory, but all error detection circuitry will be enabled and errors reported. This is useful in detecting bad sectors and tracks on the disk.

Before executing this command, the user must set the RETRY COUNT to 0. This is done by loading the high order nybble in the RETRY COUNT register to "1111" (zero in 1's complement format). Failure to do this will result in unpredictable performance because the DESIRED SECTOR register value may not correspond to the next physical sector on the disk.

#### **READ TRACK** (Hex Values = 5A and 5B)

When this command is issued, the UDC will read the data from the entire track on which the selected drive is currently sitting. The UDC will begin reading when it detects the leading edge of an index mark signal from the drive, and terminate reading when it detects the next leading edge of an index mark signal. Sync detect is performed for the ID field, but no error checking is done on the data field.

This command allows the user to specify a data transfer option, using Bit 0 in the command word. These options are:

- BIT 0 = 1 TRANSFER ALL DATA. The UDC will transfer the ID field and data fields to (external) memory.

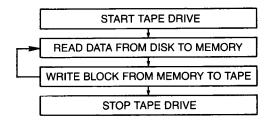

- BIT 0 = 0 TRANSFER ONLY IDs. The UDC will transfer only ID fields to the (external) memory. This is useful during tape backup operations.

#### READ SECTORS LOGICAL (Hex Values = 5C to 5F) When this command is issued, the UDC will read up to a full track from the selected drive. Prior to reading the data from the disk, the UDC will (if enabled in command) use the information in the MODE, DESIRED CYLINDER, DESIRED SECTOR and DESIRED HEAD (and Register A for IBM® PC-AT mode) registers to locate the correct track, sector and drive surface (using the previously described VERIFY

(If using drives which support buffered seeks, BITS 2-0 in the MODE SELECT register should be set to 0-0-0. This will cause the UDC to wait for a SEEK COMPLETE signal from the drive prior to entering the verify sequence.)

sequence).

Before the command is issued, the system processor must also load the desired values into the MODE, SECTOR COUNT, RETRY COUNT and the three DMA registers.

After the desired track and sector is found and verified, the DATA TRANSFER sequence begins. After each successful sector transfer, the UDC increments the DESIRED SECTOR register (except after the last sector is transferred), decrements the SECTOR COUNT register, and reenters the VERIFY sequence. This process continues until the SECTOR COUNT register is equal to 0 (or an error

This command has four options, which are specified by Bit 1 and Bit 0 of the command word. The four options are:

- BIT 1 = 1 IMPLIED SEEK DISABLED. The UDC will not update the CURRENT CYLINDER, CURRENT HEAD OR CURRENT SECTOR register and will not issue step pulses.

- BIT 1 = 0 IMPLIED SEEK ENABLED. The UDC will update the CURRENT CYLINDER, CURRENT HEAD and CURRENT SECTOR register and will issue step pulses if requird.

- BIT 0 = 1 TRANSFER ENABLED. The UDC will transfer data from the disk to the system. The DMA REQUEST status bit (in the INTERRUPT STA-TUS register) will be set when the UDC requires servicing.

BIT 0 = 0 TRANSFER DISABLED. The UDC will not transfer data read from the disk, but all error checking circuitry will be enabled.

FORMAT TRACK (Hex Values 60 to 7F)

This command causes the UDC to format the current cylinder from the leading edge of one index mark to the leading edge of the next index mark. The format chosen is dependent on the Drive Select command.

During execution of the FORMAT TRACK command, the UDC will fetch all required ID field data from external memory, and write it to the disk, along with format constants sup-plied automatically by the UDC. This reduces the number of bytes required to format a sector to 3 or 4, depending on the format chosen.

Before the FORMAT TRACK command can be given, the system processor must:

1. Generate an ID Field Table for the track in UDC memory area. This ID Field Table consists of:

IDENT BYTE (not required for floppy disk FM format)

CYLINDER BYTE

HEAD BYTE

SECTOR NUMBER BYTE

SECTOR SIZE/ECC SIZE BYTE (not required for IBM® PC-AT FORMAT) repeated for each sector on the track.