SN65LVCP114

SLLSEA8A – JANUARY 2012 – REVISED MARCH 2016

# SN65LVCP114 14.2-Gbps Quad 1:2-2:1 Mux, Linear-Redriver With Signal Conditioning

Technical

Documents

Sample &

Buy

# **1** Features

- Quad 2:1 Mux and 1:2 Demux

- Multi-Rate Operation up to 14.2 Gbps Serial Data Rate

- Linear Receiver Equalization Which Increases Margin at System Level of Decision Feedback Equalizer

- Bandwidth: 18 GHz, Typical

- Per-Lane P/N Pair Inversion

- · Port or Single Lane Switching

- Low Power: 150 mW/Channel, Typical

- · Loopback Mode on All Three Ports

- I<sup>2</sup>C Control in Addition to GPIO

- DIAG Mode That Outputs Data of Line Side Port to Both Fabric Side Ports

- 2.5-V or 3.3-V Single Power Supply

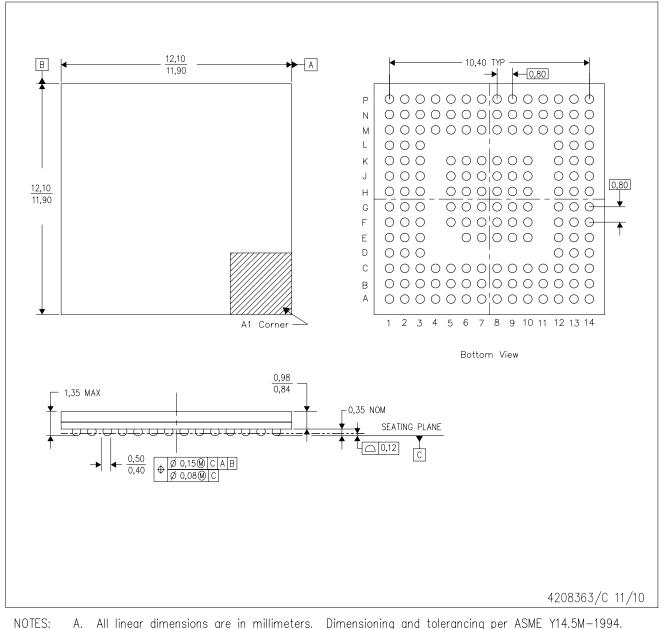

- PBGA Package 12-mm × 12-mm × 1-mm, 0.8-mm Terminal Pitch

- Excellent Impedance Matching to 100-Ω PCB Transmission Lines

- Small Package Size Provides Board Real Estate

Saving

- Adjustable Output Swing Provides Flexible EMI and Crosstalk Control

- Low Power

- Supports 10GBASE-KR Applications With Ability to Transparency for Link Training

# 2 Applications

Tools &

Software

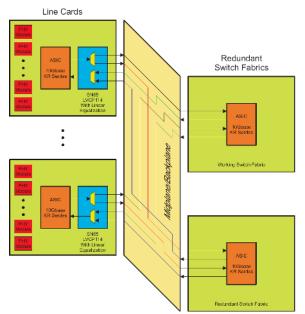

High-Speed Redundancy Switch in Telecom and Data Communication

Support &

Community

**.**...

Backplane Interconnect for 10G-KR, 16GFC

# **3** Description

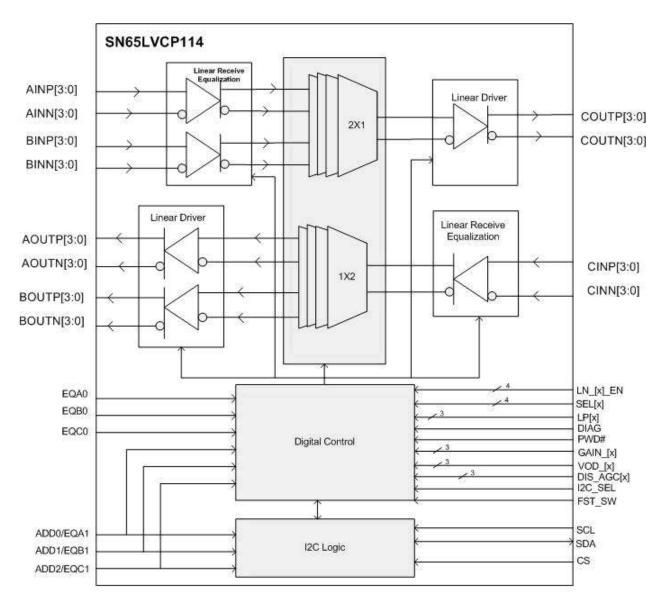

The SN65LVCP114 device is an asynchronous, protocol-agnostic, low-latency QUAD mux, linearredriver optimized for use in systems operating at up to 14.2 Gbps. The device linearly compensates for loss in backplane and channel active-cable applications. The architecture of SN65LVCP114 linear-redriver is designed to work effectively with ASIC or FPGA products implementing digital equalization using decision feedback equalizer (DFE) technology. The SN65LVCP114 mux, linear-redriver preserves the integrity (composition) of the received sianal. ensurina optimum DFE and system performance. The SN65LVCP114 provides a lowpower mux-demux, linear-redriver solution while at the same time extending the effectiveness of DFE.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |

|-------------|-------------|---------------------|

| SN65LVCP114 | NFBGA (167) | 12.00 mm × 12.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# SN65LVCP114 Typical Implementation

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

TEXAS INSTRUMENTS

www.ti.com

# **Table of Contents**

| 1 | Feat | tures 1                                                           |

|---|------|-------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                       |

| 3 | Des  | cription 1                                                        |

| 4 | Rev  | ision History 2                                                   |

| 5 | Des  | cription (continued) 3                                            |

| 6 | Pin  | Configuration and Functions 4                                     |

| 7 | Spe  | cifications7                                                      |

|   | 7.1  | Absolute Maximum Ratings 7                                        |

|   | 7.2  | ESD Ratings7                                                      |

|   | 7.3  | Recommended Operating Conditions7                                 |

|   | 7.4  | Thermal Information 8                                             |

|   | 7.5  | Electrical Characteristics (V <sub>CC</sub> 2.5 V ±5%) 8          |

|   | 7.6  | Electrical Characteristics (V <sub>CC</sub> 3.3 V ±5%) 8          |

|   | 7.7  | Electrical Characteristics (V <sub>CC</sub> 3.3 V $\pm$ 5%, 2.5 V |

|   |      | ±5%)                                                              |

|   | 7.8  | Typical Characteristics 11                                        |

| 8 | Para | ameter Measurement Information 12                                 |

|   | 8.1  | Test Circuits 12                                                  |

|   | 8.2  | Equivalent Input and Output Schematic Diagrams . 13               |

|   | 8.3  | Functional Definitions 13                                         |

| 9 | Deta | ailed Description 17                                              |

|   |      |                                                                   |

|    | 9.1  | Overview                          | 17 |

|----|------|-----------------------------------|----|

|    | 9.2  | Functional Block Diagram          | 17 |

|    | 9.3  | Feature Description               | 18 |

|    | 9.4  | Device Functional Modes           | 20 |

|    | 9.5  | Programming                       | 20 |

|    | 9.6  | Register Maps                     | 22 |

| 10 | Арр  | lication and Implementation       | 29 |

|    | 10.1 | Application Information           | 29 |

|    | 10.2 | Typical Applications              | 29 |

| 11 | Pow  | ver Supply Recommendations        | 33 |

| 12 | Lay  | out                               | 33 |

|    | 12.1 |                                   |    |

|    | 12.2 | Layout Example                    | 34 |

| 13 | Dev  | ice and Documentation Support     | 35 |

|    | 13.1 |                                   |    |

|    | 13.2 | Community Resources               | 35 |

|    | 13.3 | Trademarks                        | 35 |

|    | 13.4 | Electrostatic Discharge Caution   | 35 |

|    | 13.5 | Glossary                          | 35 |

| 14 | Mec  | hanical, Packaging, and Orderable |    |

|    |      | rmation                           | 35 |

|    |      |                                   |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Original (January 2012) to Revision A

#### Page

| • | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation                                                                                        |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | section, <i>Power Supply Recommendations</i> section, <i>Layout</i> section, <i>Device and Documentation Support</i> section, and <i>Mechanical, Packaging, and Orderable Information</i> section. 1 |

| • | Removed Typical Eq Gain Profile Curve graph in Typical Characteristics 11                                                                                                                            |

# 5 Description (continued)

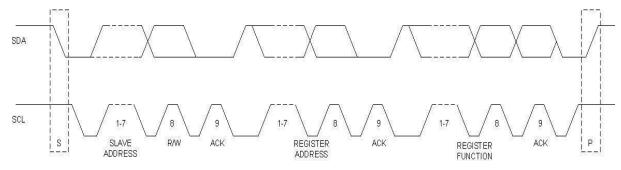

SN65LVCP114 is configurable through GPIO or an I<sup>2</sup>C interface.

A single 2.5-V or 3.3-V power supply supports the operation of the SN65LVCP114.

The SN65LVCP114 is packaged in a 12-mm × 12-mm × 1-mm PBGA package with 0.8-mm pitch.

The SN65LVCP114 has three ports; each port is a quad lane. The switch logic of SN65LVCP114 can be implemented to support a 2:1 MUX per lane, 1:2 DEMUX per lane, and independent lane switching. The receive equalization can be independently programmed for each of the ports. The SN65LVCP114 supports loopback on all three ports.

|        | MAXIMUM BOARD TEMPERATURE <sup>(1)</sup> |        |      |                       |                        |                       |                                |

|--------|------------------------------------------|--------|------|-----------------------|------------------------|-----------------------|--------------------------------|

| LOOP_A | LOOP_B                                   | LOOP_C | DIAG | V <sub>CC</sub> =     | : 2.5 V                |                       | <sub>CC</sub> = 3.3 V          |

|        |                                          | _      |      | V <sub>OD</sub> = LOW | V <sub>OD</sub> = HIGH | V <sub>OD</sub> = LOW | V <sub>OD</sub> = HIGH         |

| LOW    | LOW                                      | LOW    | LOW  | 85°C                  | 85°C                   | 85°C                  | 75°C                           |

| LOW    | LOW                                      | LOW    | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific (2)            |

| LOW    | LOW                                      | HIGH   | LOW  | 85°C                  | 85°C                   | 85°C                  | 75°C                           |

| LOW    | LOW                                      | HIGH   | HIGH | 85°C                  | 85°C                   | 85°C                  | 75°C                           |

| LOW    | HIGH                                     | LOW    | LOW  | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| LOW    | HIGH                                     | LOW    | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| LOW    | HIGH                                     | HIGH   | LOW  | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| LOW    | HIGH                                     | HIGH   | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| HIGH   | LOW                                      | LOW    | LOW  | 85°C                  | 85°C                   | 85°C                  | 75°C                           |

| HIGH   | LOW                                      | LOW    | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| HIGH   | LOW                                      | HIGH   | LOW  | 85°C                  | 85°C                   | 85°C                  | 75°C                           |

| HIGH   | LOW                                      | HIGH   | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| HIGH   | HIGH                                     | LOW    | LOW  | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| HIGH   | HIGH                                     | LOW    | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| HIGH   | HIGH                                     | HIGH   | LOW  | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

| HIGH   | HIGH                                     | HIGH   | HIGH | 85°C                  | 85°C                   | 75°C                  | System Specific <sup>(2)</sup> |

**Table 1. Recommended Maximum Board Temperature**

(1) Maximum board temperature is allowed as long as the device maximum junction temperature is not exceeded.

(2) Texas Instruments recommends a system thermal and device use case power analysis to decide possible use of a heat sink.

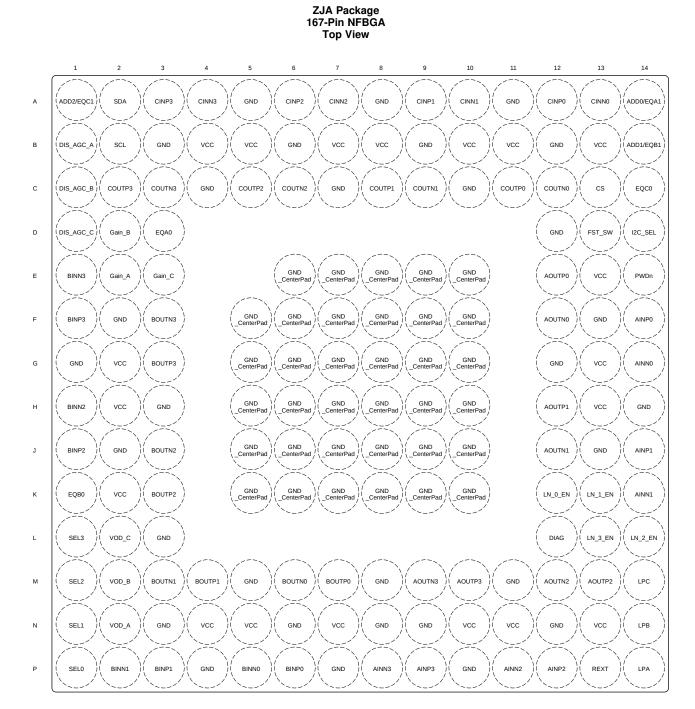

# 6 Pin Configuration and Functions

## **Pin Functions**

| PIN<br>NAME BALLS |                         | DIRECTION TYPE SUPPLY                              | DESCRIPTION                           |  |  |

|-------------------|-------------------------|----------------------------------------------------|---------------------------------------|--|--|

|                   |                         | DIRECTION TIPE SUPPLY                              |                                       |  |  |

| LINE-SIDE HIGH-   | INE-SIDE HIGH-SPEED I/O |                                                    |                                       |  |  |

| CINP0<br>CINN0    | A12<br>A13              | Input (with 50-Ω termination to input common mode) | Differential input, lane 0 line side. |  |  |

| CINP1<br>CINN1    | A9<br>A10               | Input (with 50-Ω termination to input common mode) | Differential input, lane 1 line side  |  |  |

# Pin Functions (continued)

|                                     | PIN               |                                                    | DECODIDION                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                       |  |  |  |

|-------------------------------------|-------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                | BALLS             | DIRECTION TYPE SUPPLY                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                       |  |  |  |

| CINP2<br>CINN2                      | A6<br>A7          | Input (with 50-Ω termination to input common mode) | Differential input, lane 2 line side                                                                                                                                                                                                                                                                                                                  |                                                                                                                                       |  |  |  |

| CINP3<br>CINN3                      | A3<br>A4          | Input (with 50-Ω termination to input common mode) | Differential input, lane 3 line side                                                                                                                                                                                                                                                                                                                  |                                                                                                                                       |  |  |  |

| COUTP0<br>COUTN0                    | C11<br>C12        | Output                                             | Differential output, lane 0 line side                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |  |

| COUTP1<br>COUTN1                    | C8<br>C9          | Output                                             | Differential output, lane 1 line side                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |  |

| COUTP2<br>COUTN2                    | C5<br>C6          | Output                                             | Differential output, lane 2 line side                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |  |

| COUTP3<br>COUTN3                    | C2<br>C3          | Output                                             | Differential output, lane 3 line side                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |  |

| SWITCH-SIDE H                       | IGH-SPEED I/O     |                                                    |                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                       |  |  |  |

| AINP0<br>AINN0                      | F14G14            | Input (with 50-Ω termination to input common mode) | Differential input, lane 0, fabric switch_A_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| AINP1<br>AINN1                      | J14<br>K14        | Input (with 50-Ω termination to input common mode) | Differential input, lane 1, fabric switch_A_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| AINP2<br>AINN2                      | P12<br>P11        | Input (with 50-Ω termination to input common mode) | Differential input, lane 2, fabric switch_A_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| AINP3<br>AINN3                      | P9<br>P8          | Input (with 50-Ω termination to input common mode) | Differential input, lane 3, fabric switch_A_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| BINP0<br>BINN0                      | P6<br>P5          | Input (with 50-Ω termination to input common mode) | Differential input, lane 0, fabric switch_B_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| BINP1<br>BINN1                      | P3<br>P2          | Input (with 50-Ω termination to input common mode) | Differential input, lane 1, fabric switch_B_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| BINP2<br>BINN2                      | J1<br>H1          | Input (with 50-Ω termination to input common mode) | Differential input, lane 2, fabric switch_B_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| BINP3<br>BINN3                      | F1<br>E1          | Input (with 50-Ω termination to input common mode) | Differential input, Iane 3, fabric switch_B_side                                                                                                                                                                                                                                                                                                      |                                                                                                                                       |  |  |  |

| AOUTP0<br>AOUTN0                    | E12<br>F12        | Output                                             | Differential output, lane 0, fabric switch_A_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| AOUTP1<br>AOUTN1                    | H12<br>J12        | Output                                             | Differential output, lane 1, fabric switch_A_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| AOUTP2<br>AOUTN2                    | M13<br>M12        | Output                                             | Differential output, lane 2, fabric switch_A_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| AOUTP3<br>AOUTN3                    | M10<br>M9         | Output                                             | Differential output, lane 3, fabric switch_A_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| BOUTP0<br>BOUTN0                    | M7<br>M6          | Output                                             | Differential output, lane 0, fabric switch_B_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| BOUTP1<br>BOUTN1                    | M4<br>M3          | Output                                             | Differential output, lane 1, fabric switch_B_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| BOUTP2<br>BOUTN2                    | K3<br>J3          | Output                                             | Differential output, lane 2, fabric switch_B_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| BOUTP3<br>BOUTN3                    | G3<br>F3          | Output                                             | Differential output, lane 3, fabric switch_B_side                                                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |

| CONTROL SIGN                        | ALS               |                                                    |                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                       |  |  |  |

| ADD0/EQA1<br>ADD1/EQB1<br>ADD2/EQC1 | A14<br>B14<br>A1  | Input, 2.5-V or 3.3-V CMOS - 3-state               | GPIO mode<br>EQ control pins. EQA1 and EQA0 pins are 3-state and control the<br>EQ gain of port A.<br>EQ control pins. EQB1 and EQB0 pins are 3-state and control the<br>EQ gain of port B.<br>EQ control pins. EQC1 and EQC0 pins are 3-state and control the<br>EQ gain of port C.<br>Refer to Table 5 for detailed information about equalization. | <b>I<sup>2</sup>C mode</b><br>ADD0 along with pins ADD1 and<br>ADD2 comprise the three bits of<br>the I <sup>2</sup> C slave address. |  |  |  |

| EQA0<br>EQB0<br>EQC0                | D3<br>K1<br>C14   | Input, 2.5-V or 3.3-V CMOS - 3-state               | GPIO mode<br>EQ control pins. EQA1 and EQA0 pins are 3-state and control<br>theEQ gain of port A.<br>EQ control pins. EQB1 and EQB0 pins are 3-state and control<br>theEQ gain of port B.<br>EQ control pins. EQC1 and EQC0 pins are 3-state and control<br>theEQ gain of port C.<br>Refer to Table 5 for detailed information about equalization.    | I <sup>2</sup> C mode<br>No action needed                                                                                             |  |  |  |

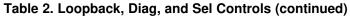

| LPA<br>LPB<br>LPC                   | P14<br>N14<br>M14 | Input (with 48-kΩ pulldown)<br>2.5-V or 3.3-V CMOS | GPIO mode<br>LPx enables loopback for port x<br>HIGH: Loopback enabled<br>LOW: Loopback disabled<br>See Table 2 and Figure 14                                                                                                                                                                                                                         | I <sup>2</sup> C mode<br>No action needed                                                                                             |  |  |  |

## SN65LVCP114 SLLSEA8A – JANUARY 2012 – REVISED MARCH 2016

#### www.ti.com

# Pin Functions (continued)

| PIN                                      |                                                                                                                                                                 |                                                          | DESCRIPTION                                                                                                                                                                                                                                              |                                                                                                |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| NAME                                     | BALLS                                                                                                                                                           | DIRECTION TYPE SUPPLY                                    | DESCRIPTION                                                                                                                                                                                                                                              |                                                                                                |  |  |

| SEL0<br>SEL1<br>SEL2<br>SEL3             | P1<br>N1<br>M1<br>L1                                                                                                                                            | Input (with 48-kΩ pulldown)<br>2.5-V or 3.3-V CMOS       | GPIO mode<br>SELx, A or B switch control for lane x<br>HIGH: port B is selected<br>LOW: port A is selected<br>See Table 2                                                                                                                                | I <sup>2</sup> C mode<br>No action needed                                                      |  |  |

| REXT                                     | P13                                                                                                                                                             | Input, analog                                            | External bias resistor, 1,200 $\Omega$ to ground                                                                                                                                                                                                         | •                                                                                              |  |  |

| CS                                       | C13                                                                                                                                                             | Input (with 48-kΩ pulldown)<br>2.5-V or 3.3-V CMOS       | GPIO mode<br>No action needed                                                                                                                                                                                                                            | I <sup>2</sup> C mode<br>HIGH: acts as chip select<br>LOW: disables I <sup>2</sup> C interface |  |  |

| PWDn                                     | E14                                                                                                                                                             | Input (with 48-kΩ pullup)<br>2.5-V or 3.3-V CMOS         | LOW: Powers down the device, inputs off and outputs disabled, res<br>HIGH: Normal operation                                                                                                                                                              | sets I <sup>2</sup> C                                                                          |  |  |

| DIAG                                     | L12                                                                                                                                                             | Input (with 48-kΩ pulldown)<br>2.5-V or 3.3-V CMOS       | GPIO mode<br>HIGH: Enables the same data on the line side (Port C) to be<br>output on both fabric side ports (Port A and Port B).<br>LOW: Normal operation<br>See Table 2 and Figure 15                                                                  | I <sup>2</sup> C mode<br>No action needed                                                      |  |  |

| LN_0_EN<br>LN_1_EN<br>LN_2_EN<br>LN_3_EN | K12<br>K13<br>L14<br>L13                                                                                                                                        | Input (with 48-kΩ pullup)<br>2.5-V or 3.3-V CMOS         | GPIO mode<br>LN_x_EN = High, enables lane x of ports A, B, and C<br>LN_x_EN = Low, disables lane x of ports A, B, and C                                                                                                                                  | I <sup>2</sup> C mode<br>No action needed                                                      |  |  |

| DIS_AGC_A<br>DIS_AGC_B<br>DIS_AGC_C      | B1<br>C1<br>D1                                                                                                                                                  | Input (with 48-kΩ pulldown)<br>2.5-V or 3.3-V CMOS       | GPIO mode<br>Disables the AGC loop internal to the SN65LVCP114<br>DIS_AGC = High, disables the AGC loop<br>DIS_AGC = Low, enables the AGC loop                                                                                                           | I <sup>2</sup> C mode<br>No action needed                                                      |  |  |

| VOD_A<br>VOD_B<br>VOD_C                  | N2<br>M2<br>L2                                                                                                                                                  | Input, 2.5-V or 3.3-V CMOS - 3-state                     | GPIO mode<br>HIGH: selects VOD output range: 1.2 V maximum and a gain of<br>2.2<br>LOW: selects VOD output range: 600 mV maximum and a gain of<br>1.1<br>If the VOD_x signal is left floating, the signal defaults to 1.2 V<br>maximum and a gain of 2.2 | I <sup>2</sup> C mode<br>No action needed                                                      |  |  |

| Gain_A<br>Gain_B<br>Gain_C               | E2<br>D2<br>E3                                                                                                                                                  | Input, 2.5-V or 3.3-V CMOS - 3-state                     | GPIO mode<br>HIGH: Receiver gain = 1<br>LOW: Receiver gain = 0.5<br>If the Gain_x signal is left floating, the signal defaults to 0.5                                                                                                                    | <b>I<sup>2</sup>C mode</b><br>No action needed                                                 |  |  |

| SDA                                      | A2                                                                                                                                                              | Input / output, open-drain output                        | GPIO mode<br>No action needed                                                                                                                                                                                                                            | I <sup>2</sup> C mode<br>I <sup>2</sup> C data. Connect a 10-kΩ pullup<br>resistor externally  |  |  |

| SCL                                      | B2                                                                                                                                                              | Input, open-drain input                                  | GPIO mode<br>No action needed                                                                                                                                                                                                                            | I <sup>2</sup> C mode<br>I <sup>2</sup> C clock. Connect a 10-kΩ pullup<br>resistor externally |  |  |

| FST_SW                                   | D13                                                                                                                                                             | Input (with 48-kΩ pullup)<br>2.5-V or 3.3-V CMOS input   | GPIO mode<br>HIGH: Fast switching; the idle outputs are squelched (see tSM<br>specification).<br>LOW: Slow switching; the idle outputs are powered off (see tSM1<br>specification).                                                                      | <b>I<sup>2</sup>C mode</b><br>No action needed                                                 |  |  |

| I2C_SEL                                  | D14                                                                                                                                                             | Input (with 48-kΩ pulldown)<br>2.5-V or 3.3-V CMOS input | Configures the device in I <sup>2</sup> C or GPIO mode of operation<br>HIGH: Enables I <sup>2</sup> C mode<br>LOW: Enables GPIO mode                                                                                                                     |                                                                                                |  |  |

| POWER SUPPL                              | Y                                                                                                                                                               | ·                                                        | ·                                                                                                                                                                                                                                                        |                                                                                                |  |  |

| VCC                                      | B4, B5, B7, B8, B10,<br>B11, B13, E13, G2,<br>G13, H2, H13, K2,N4,<br>N5, N7, N10, N11,<br>N13                                                                  | Power, 2.5 V ±5% or 3.3 V ±5%                            | Power supply pins                                                                                                                                                                                                                                        |                                                                                                |  |  |

| GROUND                                   |                                                                                                                                                                 |                                                          |                                                                                                                                                                                                                                                          |                                                                                                |  |  |

| GND                                      | A5, A8, A11, B3, B6,<br>B9, B12, C4, C7,<br>C10,D12, F2, F13,G1,<br>G12, G1, G12, H3,<br>H14,J2, J13, L3,<br>M5,M8, M11, N3, N6,<br>N8, N9, N12, P4, P7,<br>P10 | Ground                                                   | Ground pins                                                                                                                                                                                                                                              |                                                                                                |  |  |

## **Pin Functions (continued)**

|                   | PIN                                                                                                                                                               | DIRECTION TYPE SUPPLY | DESCRIPTION                                    |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|--|--|

| NAME              | BALLS                                                                                                                                                             | DIRECTION TYPE SUPPLY |                                                |  |  |

| GND_CenterPa<br>d | E6, E7, E8, E9, E10,<br>F5, F6, F7, F8, F9,<br>F10, G5, G6, G7, G8,<br>G9, G10, H5, H6, H7,<br>H8, H9, H10, J5, J6,<br>J7, J8, J9, J10, K5,<br>K6, K7,K8, K9, K10 | Ground                | These pins must be connected to the GND plane. |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                        |                                                                          | MIN  | МАХ       | UNIT |

|----------------------------------------|--------------------------------------------------------------------------|------|-----------|------|

| V <sub>CC</sub>                        | Supply voltage range <sup>(2)</sup>                                      | -0.3 | 4         | V    |

| V <sub>IN,DIFF</sub>                   | Differential voltage between xINx_P and xINx_N                           |      | ±2.5      | V    |

| V <sub>IN+</sub> ,<br>V <sub>IN-</sub> | Voltage at xINx_P and xINx_N                                             | -0.5 | VCC + 0.5 | V    |

| V <sub>IO</sub>                        | Voltage on control I/O pins                                              | -0.3 | VCC + 0.5 | V    |

| I <sub>IN+</sub><br>I <sub>IN-</sub>   | Continuous current at high-speed differential data inputs (differential) | -25  | 25        | mA   |

| I <sub>OUT+</sub><br>I <sub>OUT-</sub> | Continuous current at high-speed differential data outputs               | -25  | 25        | mA   |

| T <sub>stg</sub>                       | Storage temperature                                                      | -55  | 125       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values, except differential I/O bus voltages, are with respect to network ground terminal. (2)

# 7.2 ESD Ratings

|        |                           |                                                                                   | VALUE | UNIT |

|--------|---------------------------|-----------------------------------------------------------------------------------|-------|------|

| V      | Electrostatio discharge   | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)(2)</sup>              | ±2000 | V    |

| V(ESD) | V Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(3)(4)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

Tested in accordance with JEDEC Standard 22, Test Method A114-A.

(3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

Tested in accordance with JEDEC Standard 22, Test Method C101. (4)

# 7.3 Recommended Operating Conditions

|                 |                                                        | MIN                      | NOM | MAX                 | UNIT |

|-----------------|--------------------------------------------------------|--------------------------|-----|---------------------|------|

|                 | Operating data rate, dR                                |                          |     | 14.2                | Gbps |

|                 | Supply voltage, V <sub>CC</sub> , 2.5-V nominal supply | 2.375                    | 2.5 | 2.625               | V    |

|                 | Supply voltage, V <sub>CC</sub> , 3.3-V nominal supply | 3.135                    | 3.3 | 3.465               | V    |

|                 | PSNR BG, bandgap circuitry PSNR, 10 Hz–10 GHz          | 20                       |     |                     | dB   |

| CON             | FROL INPUTS                                            |                          |     |                     |      |

| V <sub>IH</sub> | High-level input voltage                               | 0.8 ×<br>V <sub>CC</sub> |     |                     |      |

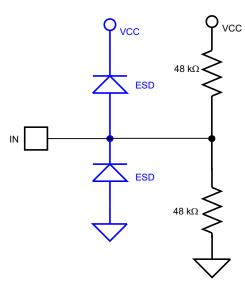

| $V_{\text{IM}}$ | Mid-level input voltage                                | V <sub>CC</sub> /2 - 0.3 |     | $V_{CC}/2 + 0.3$    | V    |

| VIL             | Low- level input voltage                               |                          |     | $0.2 \times V_{CC}$ | V    |

| T <sub>C</sub>  | Junction temperature <sup>(1)</sup>                    | -10                      |     | 125                 | °C   |

Use of  $\theta$ JB and  $\varphi$ JB are recommended for thermal calculations. For more information about traditional and new thermal metrics, see IC (1) Package Thermal Metrics application report, SPRA953.

### SN65LVCP114

SLLSEA8A - JANUARY 2012 - REVISED MARCH 2016

#### www.ti.com

RUMENTS

XAS

## **Recommended Operating Conditions (continued)**

|                                          | MIN | NOM | MAX | UNIT |

|------------------------------------------|-----|-----|-----|------|

| Maximum board temperature <sup>(1)</sup> |     | Se  |     | °C   |

## 7.4 Thermal Information

|                       |                                              | SN65LVCC114 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | ZJA (NFBGA) | UNIT |

|                       |                                              | 167 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 38.8        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 7.55        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 17.8        | °C/W |

| $\psi_{JT}$           | Junction-to-top characterization parameter   | 0.2         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 17.5        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 7.5 Electrical Characteristics (V<sub>cc</sub> 2.5 V ±5%)

over operating conditions range. All parameters are referenced to package pins (unless otherwise noted).

| PARAMETER         |                                          | TEST CONDITIONS                                                                                        | MIN | ТҮР  | MAX  | UNIT |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|------|------|------|

| POWER             | CONSUMPTION                              |                                                                                                        |     |      |      |      |

| $PD_L$            | Device power dissipation, loopback mode  | Ports A, B, and C in loopback mode with all 12 channels active. VOD = LOW                              |     | 1800 | 2300 | mW   |

| $PD_{N}$          | Device power dissipation, normal mode    | Device configured in mux-demux mode with 8 channels active.<br>VOD = LOW                               |     | 1400 | 1800 | mW   |

| PD <sub>OFF</sub> | Device power dissipation, lanes disabled | All 4 lanes disabled. See the I <sup>2</sup> C section for device configuration.                       |     | 50   |      | mW   |

| PD <sub>STB</sub> | Device power dissipation, standby        | All 12 channels active, VOD = LOW, FAST_SW = HIGH.<br>See the $I^2C$ section for device configuration. |     | 1800 | 2300 | mW   |

# 7.6 Electrical Characteristics (V<sub>cc</sub> 3.3 V ±5%)

over operating conditions range. All parameters are referenced to package pins (unless otherwise noted).

| PARAMETER         |                                          | TEST CONDITIONS                                                                                    | MIN | TYP  | MAX  | UNIT |

|-------------------|------------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|------|------|

| POWER             | CONSUMPTION                              |                                                                                                    |     |      |      |      |

| $PD_L$            | Device power dissipation, loopback mode  | Ports A, B, and C in loopback mode with all 12 channels active. VOD = LOW                          |     | 2500 | 3150 | mW   |

| PD <sub>N</sub>   | Device power dissipation, normal mode    | Device configured in mux-demux mode with 8 channels active.<br>VOD = LOW                           |     | 1800 | 2500 | mW   |

| PD <sub>OFF</sub> | Device power dissipation, lanes disabled | All 4 lanes disabled. See the I <sup>2</sup> C section for device configuration.                   |     | 50   |      | mW   |

| PD <sub>STB</sub> | Device power dissipation, standby        | All 12 channels active, VOD = LOW, FAST_SW = HIGH.<br>See $I^2C$ section for device configuration. |     | 2500 | 3150 | mW   |

# 7.7 Electrical Characteristics (V<sub>cc</sub> 3.3 V ±5%, 2.5 V ±5%)

over operating conditions range. All parameters are referenced to package pins (unless otherwise noted).

|                   | PARAMETER                                            | TEST CONDITIONS              | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-------------------|------------------------------------------------------|------------------------------|-----|--------------------|-----|------|

| CMOS DC           | SPECIFICATIONS                                       |                              |     |                    |     |      |

| IIH               | High-level input current                             | $V_{IN} = 0.9 \times V_{CC}$ |     |                    | 80  | μA   |

| I <sub>IL</sub>   | Low-level input current                              | $V_{IN} = 0.1 \times V_{CC}$ | -80 |                    |     | μA   |

| CML INPUT         | TS (AINP[3:0], AINN[3:0], BINP[3:0], BINN[3:0], CINP | [3:0], CINN[3:0])            |     |                    |     |      |

| r <sub>IN</sub>   | Differential input resistance                        | INx_P to INx_N               |     | 100                |     | Ω    |

| V <sub>INPP</sub> | Input linear dynamic range                           | Gain = 0.5                   |     | 1200               |     | mVpp |

| ,                 |                                                      |                              |     |                    |     |      |

(1) All typical values are at 25°C and with 2.5-V and 3.3-V supply, unless otherwise noted.

# Electrical Characteristics (V<sub>cc</sub> 3.3 V ±5%, 2.5 V ±5%) (continued)

### over operating conditions range. All parameters are referenced to package pins (unless otherwise noted).

|                                             | PARAMETER                                                                 | TEST CONDITIONS                                                                                                                      | MIN TYP <sup>(1)</sup> | MAX  | UNIT                        |

|---------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----------------------------|

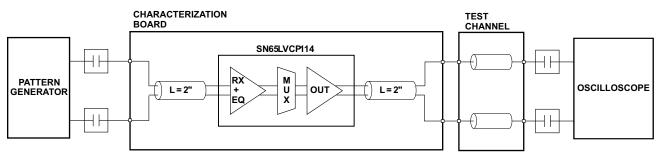

| VICM                                        | Common-mode input voltage                                                 | Internally biased                                                                                                                    | $V_{CC} - 0.3$         |      | V                           |

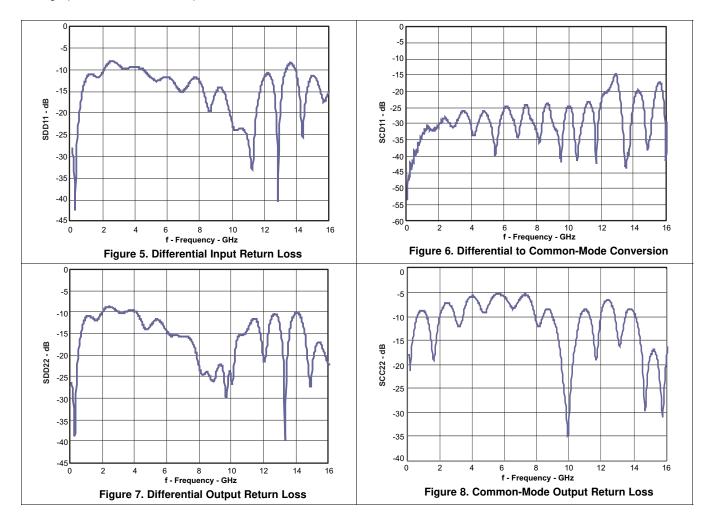

| SCD11                                       | Input differential to common-mode conversion                              | 100 MHz to 7.1GHz                                                                                                                    | -25                    |      | dB                          |

| SDD11                                       | Differential input return loss                                            | 100 MHz to 7.1GHz                                                                                                                    | -10                    |      | dB                          |

| CML OUTPL                                   | JTS (AOUTP[3:0], AOUTN[3:0], BOUTP[3:0], BOUT                             | N[3:0], COUTP[3:0], COUTN[3:0])                                                                                                      |                        |      |                             |

| .,                                          |                                                                           | $R_L = 100 \Omega$ , $V_{OD} = High$                                                                                                 | 1200                   |      |                             |

| V <sub>OD</sub> Output linear dynamic range | Output linear dynamic range                                               | $R_L = 100 \Omega$ , $V_{OD} = Low$                                                                                                  | 600                    |      | mV <sub>PP</sub>            |

| V <sub>OS</sub>                             | Output offset voltage                                                     | $R_L = 100 \Omega$ , 0 V applied at inputs                                                                                           |                        | 20   | $mV_{PP}$                   |

| V <sub>CM,RIP</sub>                         | Common-mode output ripple                                                 | K28.5 pattern at 14.2 Gbps,<br>no interconnect loss, V <sub>oD</sub> = HIGH                                                          | 10                     | 20   | mV <sub>RMS</sub>           |

| V <sub>OD,RIP</sub>                         | Differential path output ripple                                           | K28.5 pattern at 14.2Gbps, no interconnect loss, $V_{IN}$ = 1200 mVpp. Outputs squelched.                                            |                        | 20   | $\mathrm{mV}_{\mathrm{PP}}$ |

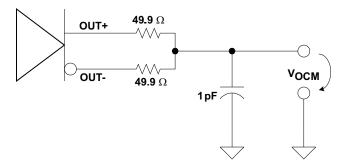

| V <sub>OCM</sub>                            | Output common mode voltage                                                | See Figure 9                                                                                                                         | $V_{CC} - 0.35$        |      | V                           |

| V <sub>OC(SS)</sub>                         | Change in steady-state common-mode output<br>voltage between logic states |                                                                                                                                      | ±10                    |      | mV                          |

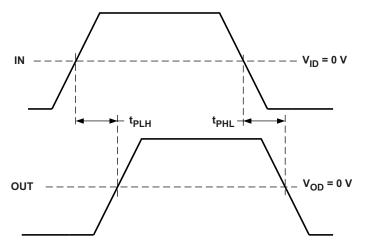

| t <sub>PLH</sub>                            | Low-to-high propagation delay                                             | See Figure 1                                                                                                                         | 200                    |      | ps                          |

| t <sub>PHL</sub>                            | High-to-low propagation delay                                             | See Figure 1                                                                                                                         | 200                    |      | ps                          |

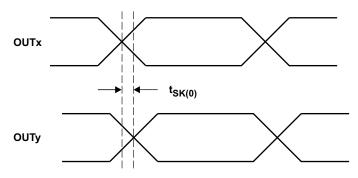

| t <sub>SK(O)</sub>                          | Inter-pair output skew (2)                                                | All outputs terminated with 100 $\Omega$ . See Figure 3                                                                              | 50                     |      | ps                          |

| t <sub>SK(PP)</sub>                         | Part-to-part skew <sup>(3)</sup>                                          |                                                                                                                                      |                        | 100  | ps                          |

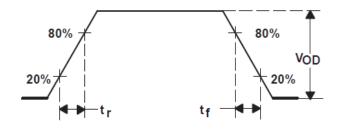

| t <sub>R</sub>                              | Rise time                                                                 | Input signal with 30-ps rise time, 20% to 80%. See Figure 2                                                                          | 31                     |      | ps                          |

| t <sub>F</sub>                              | Fall time                                                                 | Input signal with 30-ps fall time, 20% to 80%. See Figure 2                                                                          | 31                     |      | ps                          |

| SDD22                                       | Differential output return loss                                           | 100 MHz to 7.1 GHz                                                                                                                   | -10                    |      | dB                          |

| SCC22                                       | Common-mode output return loss                                            | 100 MHz to 7.1 GHz                                                                                                                   | -5                     |      | dB                          |

| t <sub>SM</sub>                             |                                                                           | Mux to valid output (idle outputs are squelched)                                                                                     | 100                    |      | ns                          |

| t <sub>SM1</sub>                            | Multiplexer switch time                                                   | Mux to valid output (idle outputs are turned off)                                                                                    | 10                     |      | μs                          |

| SMI                                         |                                                                           | Frequency at 5.1625 GHz                                                                                                              | 52.2                   |      | μο                          |

| Ch <sub>iso</sub>                           | Channel-to-channel isolation <sup>(4)</sup>                               | Frequency at 7.1 GHz                                                                                                                 | 43.5                   |      | dB                          |

|                                             |                                                                           | 10 MHz to 7.1 GHz. No other noise source present. $V_{OD} = LOW$                                                                     |                        | 1500 |                             |

| OUT <sub>NOISE</sub>                        | Output referred noise                                                     | 10 MHz to 7.1 GHz. No other noise source present. $V_{OD}$ = HIGH                                                                    |                        | 3000 | μV <sub>RMS</sub>           |

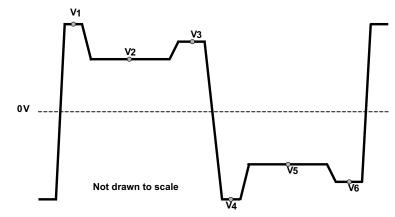

| Vpre                                        | Output pre-cursor pre-emphasis                                            | Input signal with 3.75-dB pre-cursor and measured on the output signal. See Figure 4. Vpre = 20 log(V3/V2)                           | 5                      |      | dB                          |

| Vpst                                        | Output post-cursor pre-emphasis                                           | Input signal with 12-dB post-cursor and measure on the output signal.<br>See Figure 4. Vpst = 20 log(V1/V2)                          | 14                     |      | dB                          |

| r <sub>ot</sub>                             | Single-ended output resistance                                            | Single-ended on-chip terminations to VCC, outputs are AC-<br>coupled                                                                 | 50                     |      | Ω                           |

| r <sub>ом</sub>                             | Output termination mismatch at 1 MHz                                      | $\Delta rom = 2 \times \frac{rp - rn}{rp + rn} \times 100$                                                                           |                        | 5%   |                             |

| EQUALIZAT                                   | ION                                                                       |                                                                                                                                      |                        |      |                             |

| EQ <sub>Gain</sub>                          | At 7.1 GHz input signal                                                   | Equalization gain, EQ = MAX                                                                                                          | 10 15                  |      | dB                          |

| DJ1                                         | TX residual deterministic jitter at 10.3125 Gbps                          | Tx launch amplitude = 0.6 Vpp, EQ = 1.3 dB, VOD and GAIN are high. Test channel = 0". See Figure 11.                                 | 0.08                   |      | Ulp-p                       |

| DJ2                                         | TX residual deterministic jitter at 14.2 Gbps                             | Tx launch amplitude = 0.6 Vpp, EQ = 1.3 dB, VOD and GAIN are high. Test channel = 0". See Figure 11.                                 | 0.06                   |      | Ulp-p                       |

| DJ3                                         | RX residual deterministic jitter at 10.3125 Gbps                          | Tx launch amplitude = 0.6 Vpp, test channel = $12^{\circ}$ (9-dB loss at 5 GHz), EQ = 13.9 dB, VOD and GAIN are high. See Figure 10. | 0.04                   |      | Ulp-p                       |

| DJ4                                         | RX residual deterministic Jitter at 14.2 Gbps                             | Tx launch amplitude = 0.6 Vpp, test channel = 8" (9-dB loss at 7 GHz), EQ = 13.9 dB, VOD = LOW and GAIN = HIGH. See Figure 10.       | 0.08                   |      | Ulp-p                       |

(2) t<sub>SK(O)</sub> is the magnitude of the time difference between the channels within a Port. For more information, see *SN65LVCP114 Guidelines* for Skew Compensation, SLLA323.

(3) t<sub>SK(PP)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

(4) All noise sources added.

Figure 1. Propagation Delay, Input to Output

Figure 2. Output Rise and Fall Times

Figure 3. Output Inter-Pair Skew

Figure 4. VPRE and VPOST [The Test Pattern is 111111100000000 (Eight 1s, Eight 0s)]

# 7.8 Typical Characteristics

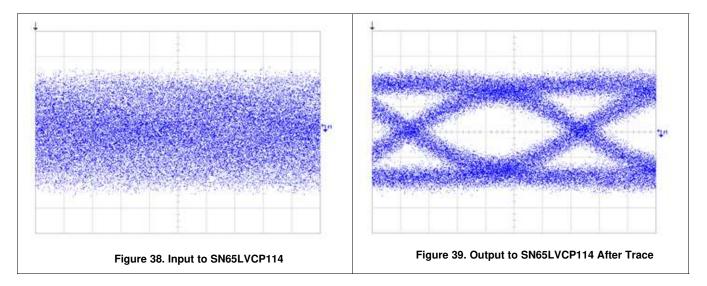

Typical operating condition is at  $V_{CC} = 2.5$  V and  $T_A = 25$ °C, no interconnect line at the output, and with default device settings (unless otherwise noted).

# 8 Parameter Measurement Information

# 8.1 Test Circuits

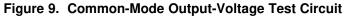

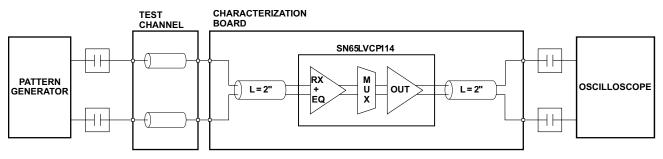

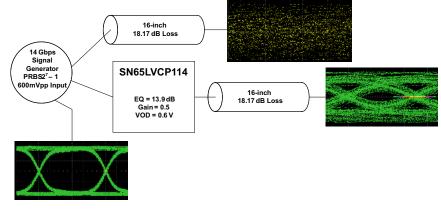

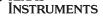

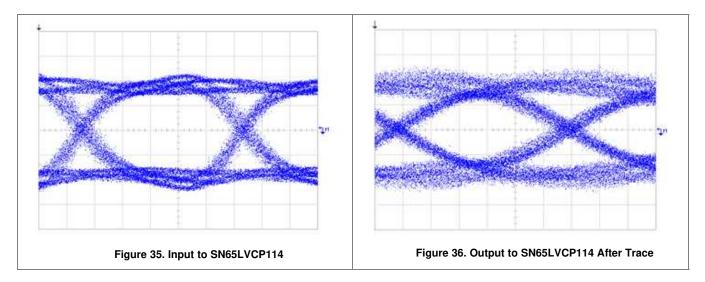

Figure 10. Receive-Side Performance Test Circuit

Figure 11. Transmit-Side Performance Test Circuit

www.ti.com

# 8.2 Equivalent Input and Output Schematic Diagrams

# 8.3 Functional Definitions

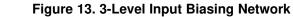

| Table 2. Loopback, Diag, and Ser Controls |        |        |      |          |                |                |                |

|-------------------------------------------|--------|--------|------|----------|----------------|----------------|----------------|

| LOOP_A                                    | LOOP_B | LOOP_C | DIAG | SEL[3:0] | OUTPUT PORT A  | OUTPUT PORT B  | OUTPUT PORT C  |

| 0                                         | 0      | 0      | 0    | 0        | In_Port_C[3:0] | idle           | In_Port_A[3:0] |

| 0                                         | 0      | 0      | 0    | 1        | idle           | In_Port_C[3:0] | In_Port_B[3:0] |

| 0                                         | 0      | 0      | 1    | 0        | In_Port_C[3:0] | In_Port_C[3:0] | In_Port_A[3:0] |

| 0                                         | 0      | 0      | 1    | 1        | In_Port_C[3:0] | In_Port_C[3:0] | In_Port_B[3:0] |

| 0                                         | 0      | 1      | 0    | 0        | In_Port_C[3:0] | Idle           | In_Port_C[3:0] |

| 0                                         | 0      | 1      | 0    | 1        | ldle           | In_Port_C[3:0] | In_Port_C[3:0] |

| 0                                         | 0      | 1      | 1    | 0        | In_Port_C[3:0] | In_Port_C[3:0] | In_Port_C[3:0] |

| 0                                         | 0      | 1      | 1    | 1        | In_Port_C[3:0] | In_Port_C[3:0] | In_Port_C[3:0] |

| 0                                         | 1      | 0      | 0    | 0        | In_Port_C[3:0] | In_Port_B[3:0] | In_Port_A[3:0] |

| 0                                         | 1      | 0      | 0    | 1        | ldle           | In_Port_B[3:0] | In_Port_B[3:0] |

| 0                                         | 1      | 0      | 1    | 0        | In_Port_C[3:0] | In_Port_B[3:0] | In_Port_A[3:0] |

| 0                                         | 1      | 0      | 1    | 1        | In_Port_C[3:0] | In_Port_B[3:0] | In_Port_B[3:0] |

| 0                                         | 1      | 1      | 0    | 0        | In_Port_C[3:0] | In_Port_B[3:0] | In_Port_C[3:0] |

| 0                                         | 1      | 1      | 0    | 1        | Idle           | In_Port_B[3:0] | In_Port_C[3:0] |

| 0                                         | 1      | 1      | 1    | 0        | In_Port_C[3:0] | In_Port_B[3:0] | In_Port_C[3:0] |

| 0                                         | 1      | 1      | 1    | 1        | In_Port_C[3:0] | In_Port_B[3:0] | In_Port_C[3:0] |

| 1                                         | 0      | 0      | 0    | 0        | In_Port_A[3:0] | Idle           | In_Port_A[3:0] |

| 1                                         | 0      | 0      | 0    | 1        | In_Port_A[3:0] | In_Port_C[3:0] | In_Port_B[3:0] |

| 1                                         | 0      | 0      | 1    | 0        | In_Port_A[3:0] | In_Port_C[3:0] | In_Port_A[3:0] |

| 1                                         | 0      | 0      | 1    | 1        | In_Port_A[3:0] | In_Port_C[3:0] | In_Port_B[3:0] |

| 1                                         | 0      | 1      | 0    | 0        | In_Port_A[3:0] | Idle           | In_Port_C[3:0] |

| 1                                         | 0      | 1      | 0    | 1        | In_Port_A[3:0] | In_Port_C[3:0] | In_Port_C[3:0] |

| 1                                         | 0      | 1      | 1    | 0        | In_Port_A[3:0] | In_Port_C[3:0] | In_Port_C[3:0] |

| 1                                         | 0      | 1      | 1    | 1        | In_Port_A[3:0] | In_Port_C[3:0] | In_Port_C[3:0] |

| 1                                         | 1      | 0      | 0    | 0        | In_Port_A[3:0] | In_Port_B[3:0] | In_Port_A[3:0] |

## Table 2. Loopback, Diag, and Sel Controls

Copyright © 2012-2016, Texas Instruments Incorporated

Texas Instruments

www.ti.com

# **Functional Definitions (continued)**

|        |        |        |      | -        | -              |                |                |

|--------|--------|--------|------|----------|----------------|----------------|----------------|

| LOOP_A | LOOP_B | LOOP_C | DIAG | SEL[3:0] | OUTPUT PORT A  | OUTPUT PORT B  | OUTPUT PORT C  |

| 1      | 1      | 0      | 0    | 1        | In_Port_A[3:0] | In_Port_B[3:0] | In_Port_B[3:0] |

| 1      | 1      | 0      | 1    | 0        | In_Port_A[3:0] | In_Port_B[3:0] | In_Port_A[3:0] |

| 1      | 1      | 0      | 1    | 1        | In_Port_A[3:0] | In_Port_B[3:0] | In_Port_B[3:0] |

| 1      | 1      | 1      | 0    | 0        | In_Port_A[3:0] | In_Port_B[3:0] | In_Port_C[3:0] |

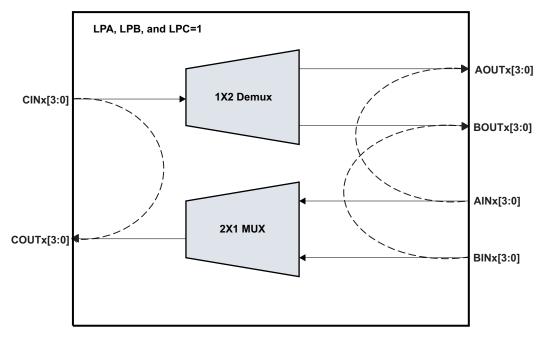

Figure 14. Loopback Mode

SELx = 0, DIAG = 1 AOUTx[3:0] = CINx[3:0] AOUTx[3:0] 1X2 Demux CINx[3:0] BOUTx[3:0] BOUTx[3:0] = CINx[3:0] COUTx[3:0] = AINx[3:0] AINx[3:0] ------2X1 MUX COUTx[3:0] BINx[3:0] SELx=1, DIAG = 1 AOUTx[3:0] = CINx[3:0] AOUTx[3:0] 1X2 Demux CINx[3:0] BOUTx[3:0] BOUTx[3:0] = CINx[3:0] AINx[3:0] COUTx[3:0] 2X1 MUX BINx[3:0] COUTx[3:0] = BINx[3:0]

Figure 15. Diagnostic Mode

www.ti.com

SN65LVCP114 SLLSEA8A – JANUARY 2012 – REVISED MARCH 2016

www.ti.com

NSTRUMENTS

Texas

# Table 3. Overall Gain Settings

|        |                    |       | Table 5. Overa   |        | 193    |                          |                                  |

|--------|--------------------|-------|------------------|--------|--------|--------------------------|----------------------------------|

| GAIN_x | INPUT GAIN<br>[dB] | VOD_x | VOD GAIN<br>[dB] | EQ[x]0 | EQ[x]1 | TOTAL DC<br>GAIN<br>[dB] | TOTAL EQ<br>GAIN<br>(7 GHz) [dB] |

| LOW    | 6                  | LOW   | 1                | LOW    | LOW    | -5                       | 1.3                              |

| LOW    | 6                  | LOW   | 1                | LOW    | HiZ    | -5                       | 2                                |

| LOW    | 6                  | LOW   | 1                | LOW    | HIGH   | -5                       | 3.6                              |

| LOW    | 6                  | LOW   | 1                | HiZ    | LOW    | -8                       | 5                                |

| LOW    | 6                  | LOW   | 1                | HiZ    | HiZ    | 8                        | 6.5                              |

| LOW    | 6                  | LOW   | 1                | HiZ    | HIGH   | 8                        | 8.3                              |

| LOW    | 6                  | LOW   | 1                | HIGH   | LOW    | -11                      | 10                               |

| LOW    | 6                  | LOW   | 1                | HIGH   | HiZ    | -11                      | 11.9                             |

| LOW    | -6                 | LOW   | 1                | HIGH   | HIGH   | -11                      | 13.9                             |

| LOW    | -6                 | HIGH  | 6.8              | LOW    | LOW    | 0.8                      | 1.3                              |

| LOW    | 6                  | HIGH  | 6.8              | LOW    | HiZ    | 0.8                      | 2                                |

| LOW    | 6                  | HIGH  | 6.8              | LOW    | HIGH   | 0.8                      | 3.6                              |

| LOW    | 6                  | HIGH  | 6.8              | HiZ    | LOW    | -2.2                     | 5                                |

| LOW    | 6                  | HIGH  | 6.8              | HiZ    | HiZ    | -2.2                     | 6.5                              |

| LOW    | 6                  | HIGH  | 6.8              | HiZ    | HIGH   | -2.2                     | 8.3                              |

| LOW    | 6                  | HIGH  | 6.8              | HIGH   | LOW    | -5.2                     | 10                               |

| LOW    | 6                  | HIGH  | 6.8              | HIGH   | HiZ    | -5.2                     | 11.9                             |

| LOW    | -6                 | HIGH  | 6.8              | HIGH   | HIGH   | -5.2                     | 13.9                             |

| HIGH   | 0                  | LOW   | 1                | LOW    | LOW    | 1                        | 1.3                              |

| HIGH   | 0                  | LOW   | 1                | LOW    | HiZ    | 1                        | 2                                |

| HIGH   | 0                  | LOW   | 1                | LOW    | HIGH   | 1                        | 3.6                              |

| HIGH   | 0                  | LOW   | 1                | HiZ    | LOW    | -2                       | 5                                |

| HIGH   | 0                  | LOW   | 1                | HiZ    | HiZ    | -2                       | 6.5                              |

| HIGH   | 0                  | LOW   | 1                | HiZ    | HIGH   | -2                       | 8.3                              |

| HIGH   | 0                  | LOW   | 1                | HIGH   | LOW    | -5                       | 10                               |

| HIGH   | 0                  | LOW   | 1                | HIGH   | HiZ    | -5                       | 11.9                             |

| HIGH   | 0                  | LOW   | 1                | HIGH   | HIGH   | -5                       | 13.9                             |

| HIGH   | 0                  | HIGH  | 6.8              | LOW    | LOW    | 6.8                      | 1.3                              |

| HIGH   | 0                  | HIGH  | 6.8              | LOW    | HiZ    | 6.8                      | 2                                |

| HIGH   | 0                  | HIGH  | 6.8              | LOW    | HIGH   | 6.8                      | 3.6                              |