# SLUSB57 -SEPTEMBER 2012

# 3.1-V to 5.5-V Input, 3-A Output, Synchronous, Step-Down Regulator with Integrated FETs

# Check for Samples: TPS51312

### **FEATURES**

- **D-CAP2™ Mode Enables Fast Transient** Response

- **No External Compensation Required**

- Input Voltage VIN Range: 3.1 V to 5.5 V

- Bias Voltage VCC Range: 3.1 V to 5.5 V

- Output Voltage Range: 0.6 V to 3.3 V

- 0.6-V, 1% Voltage Reference Accuracy

- **Fixed Voltage Servo Soft-Start Function**

- Auto-Skip, Eco-mode™ for High Efficiency at **Light Loads**

- Switching Frequency: 900-kHz

- UVLO, UVP, OTP and OVP Power Good Output

- Cycle-By-Cycle Current Limit, Latch-off OCP

- Thermally Enhanced 3 mm x 3 mm, 10-pin SON (DRC)

#### **APPLICATIONS**

- **Battery Powered Equipment**

- **Notebook Computers**

#### DESCRIPTION

The TPS51312 is a high-efficiency, synchronous, step-down DC/DC converter. It supports (maximum) of dc output current at output voltages from 0.6 V to 3.3 V. The D-CAP2 mode adaptive ontime control allows a small footprint when designed using all ceramic output capacitors and offers a low external component count. The device also features auto-skip function at light load condition, pre-biased start-up and internally fixed soft-start time. When the device is disabled, the output capacitor is discharged through internal resistor.

The TPS51312 is available in a 3 mm x 3 mm, 10-pin DRC package (Green RoHS compliant and Pb free) and is specified between -40°C and 85°C.

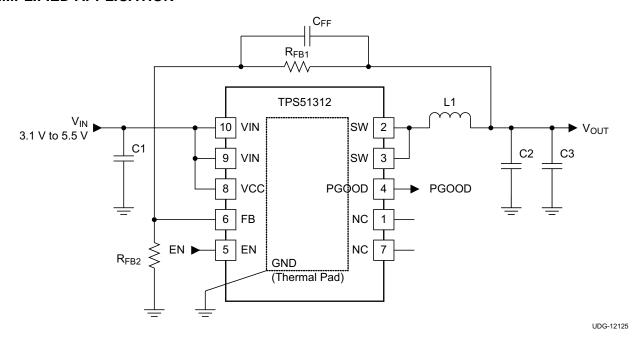

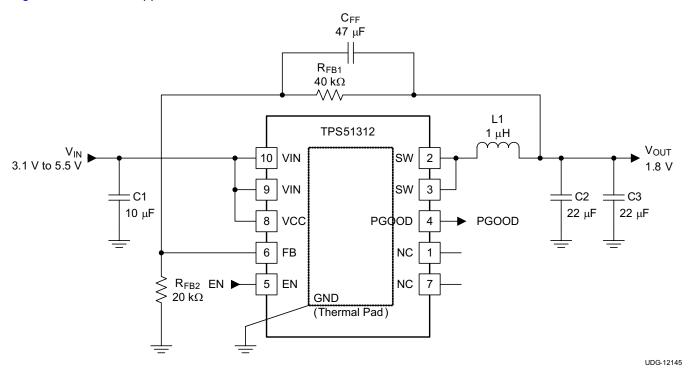

#### SIMPLIFIED APPLICATION

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

D-CAP2, Eco-mode are trademarks of Texas Instruments. All other trademarks are the property of their respective owners. SLUSB57 -SEPTEMBER 2012 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE           | ORDERABLE DEVICE NUMBER | PINS | OUTPUT<br>SUPPLY | MINIMUM<br>QUANTITY | ECO PLAN        |  |

|----------------|-------------------|-------------------------|------|------------------|---------------------|-----------------|--|

| 40°C to 05°C   | Diagtic CON (DDC) | TPS51312DRCR            | 10   | Tape and reel    | 3000                | Green (RoHS and |  |

| –40°C to 85°C  | Plastic SON (DRC) | TPS51312DRCT            | 10   | Mini reel        | 250                 | no Pb/Br)       |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS(1)

|                                       |                      | VALU        | JE  | UNIT |

|---------------------------------------|----------------------|-------------|-----|------|

|                                       |                      | MIN         | MAX | UNII |

|                                       | VIN, VCC, EN         | -0.3        | 6.0 |      |

| Input voltage range (2)               | SW                   | -2.0        | 6.0 | V    |

| input voltage range (                 | SW (transient 20 ns) |             | 8.5 | V    |

|                                       | FB                   | -1          | 3.6 |      |

| Output voltage range <sup>(2)</sup>   | PGOOD                | -0.3        | 6.0 | V    |

| Junction temperature, T <sub>J</sub>  |                      |             | 125 | °C   |

| Storage temperature, T <sub>stg</sub> |                      | <b>–</b> 55 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal unless otherwise noted.

#### THERMAL INFORMATION

|                  | THERMAL METRIC(1)                            | TPS51312     | LINUTO |

|------------------|----------------------------------------------|--------------|--------|

|                  | THERMAL METRIC <sup>(1)</sup>                | DRC (10-PIN) | UNITS  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 42.4         |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 53.9         |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 18.1         | 00044  |

| Ψлт              | Junction-to-top characterization parameter   | 1.1          | °C/W   |

| ΨЈВ              | Junction-to-board characterization parameter | 18.3         |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 6.3          |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### RECOMMENDED OPERATING CONDITIONS

|                              |                    | MIN  | MAX | UNIT |

|------------------------------|--------------------|------|-----|------|

| Input voltage range          | VIN, VCC, SW, EN   | -0.1 | 5.5 | V    |

| input voitage range          | FB                 | -0.1 | 3.5 | V    |

| Output voltage range         | PGOOD              | -0.1 | 5.5 | V    |

| Operating free-air temperatu | re, T <sub>A</sub> | -40  | 85  | °C   |

# **ELECTRICAL CHARACTERISTICS**

Over operating free-air temperature range,  $V_{IN} = 5 \text{ V}$ ,  $V_{CC} = 5 \text{ V}$ ,  $V_{EN} = 3.3 \text{ V}$  (unless otherwise noted).

|                       | PARAMETER                      | TEST CONDITION                                                                       | MIN  | TYP  | MAX  | UNIT     |

|-----------------------|--------------------------------|--------------------------------------------------------------------------------------|------|------|------|----------|

| SUPPLY VO             | DLTAGE                         |                                                                                      |      |      |      |          |

| V <sub>IN</sub>       | Supply voltage                 |                                                                                      | 3.1  |      | 5.5  | V        |

| V <sub>CC</sub>       | Supply voltage                 |                                                                                      | 3.1  |      | 5.5  | V        |

| SUPPLY CU             | JRRENT                         |                                                                                      |      |      |      |          |

| I <sub>IN</sub>       | Input voltage supply current   | EN = High                                                                            |      |      | 100  | μA       |

| I <sub>SD</sub>       | Input voltage shutdown current | EN = Low                                                                             |      |      | 12   | μA       |

| I <sub>VCC(in)</sub>  | VCC supply current             | EN = High                                                                            |      | 700  |      | μA       |

| I <sub>VCC(sd)</sub>  | VCC shutdown current           | EN = Low, T <sub>A</sub> = 25°C                                                      |      |      | 20   | μA       |

| VFB REFER             | RNCE VOLTAGE                   |                                                                                      |      |      |      |          |

| V <sub>FBREF</sub>    | Reference voltage              |                                                                                      |      | 0.6  |      | V        |

| V <sub>FBREFTOL</sub> | Reference voltage tolerance    | T <sub>A</sub> = 25°C                                                                | -1%  |      | 1%   |          |

| I <sub>FB</sub>       | Feedback pin leakage current   |                                                                                      | -100 |      | 100  | nA       |

| SMPS FREC             |                                |                                                                                      | L    |      |      |          |

| f <sub>SW</sub>       | Switching frequency            |                                                                                      |      | 0.9  |      | MHz      |

| t <sub>OFF(min)</sub> | Minimum off-time               |                                                                                      | 110  | 190  | 270  | ns       |

|                       | (4)                            | SW node high, V <sub>IN</sub> = 5 V                                                  |      | 9    |      |          |

| t <sub>DEAD</sub>     | Dead time <sup>(1)</sup>       | SW node low, V <sub>IN</sub> = 5 V                                                   |      | 10   |      | ns       |

| LOGIC THR             | ESHOLD AND CURRENT             | ***                                                                                  |      |      |      |          |

| V <sub>LL</sub>       | EN low-level voltage           |                                                                                      |      |      | 0.8  | V        |

| V <sub>LH</sub>       | EN high-level voltage          |                                                                                      | 1.5  |      |      | V        |

| I <sub>LLK</sub>      | EN input leakage current       | V <sub>IN</sub> = V <sub>CC</sub> = 3.3 V                                            | -3   | 1    | 3    | μA       |

| MOSFET                | 1                              | IIV GG -                                                                             |      |      |      | <u> </u> |

| R <sub>DS(on)_H</sub> | 40                             | V <sub>IN</sub> = 5 V                                                                |      | 81   |      |          |

| R <sub>DS(on)_L</sub> | On-resistance <sup>(1)</sup>   | V <sub>IN</sub> = 5 V                                                                |      | 41   |      | mΩ       |

| SOFT-STAF             | RT                             | IIV                                                                                  |      |      |      |          |

| t <sub>SS</sub>       | Soft-start time <sup>(1)</sup> | V <sub>FB</sub> rising from 0 V to 0.6 V                                             |      | 300  |      | μs       |

|                       | MPARATOR                       | The many many are to end a                                                           |      |      |      | F        |

|                       |                                | PGOOD out to higher w/r/t V <sub>FB</sub>                                            |      | 130% |      |          |

| $V_{PGTH}$            | PGOOD threshold                | PGOOD out to lower w/r/t V <sub>FB</sub>                                             |      | 50%  |      |          |

| t <sub>PGDLY</sub>    | PGOOD high delay time          | Delay for PGOOD in, after EN = Hi                                                    |      | 1.3  |      | ms       |

| I <sub>PGLK</sub>     | PGOOD leakage current          |                                                                                      | -1   | 0    | 1    | μΑ       |

| PROTECTION            |                                |                                                                                      |      |      | •    | μ        |

| I <sub>OCL</sub>      | Current limit threshold        | Valley current limit, $V_{IN} = V_{CC} = 3.3 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ | 4.8  |      |      | Α        |

|                       |                                | Wake-up                                                                              | 2.85 | 2.95 | 3.05 |          |

| $V_{IN\_UVLO}$        | VIN UVLO threshold voltage     | Shutdown                                                                             | 2.6  | 2.7  | 2.8  | V        |

|                       |                                | Wake-up                                                                              | 2.85 | 2.95 | 3.05 |          |

| $V_{CC\_UVLO}$        | VCC UVLO threshold voltage     | Shutdown                                                                             | 2.6  | 2.7  | 2.8  | V        |

| V <sub>OVP</sub>      | OVP threshold voltage          | OVP detect                                                                           |      | 130% |      |          |

| t <sub>OVP</sub>      | OVP delay time                 | Overdrive = 100 mV                                                                   |      | 1.9  |      | μs       |

| V <sub>UVP</sub>      | UVP threshold voltage          | UVP detect                                                                           |      | 50%  |      | μo       |

|                       |                                |                                                                                      |      |      |      | lie      |

| t <sub>UVPDLY</sub>   | UVP delay time                 | Overdrive = 100 mV                                                                   |      | 2.4  |      | μs       |

<sup>(1)</sup> Specified by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS (continued)**

Over operating free-air temperature range,  $V_{IN} = 5 \text{ V}$ ,  $V_{CC} = 5 \text{ V}$ ,  $V_{EN} = 3.3 \text{ V}$  (unless otherwise noted).

|                   | PARAMETER                      | TEST CONDITION       | MIN | TYP | MAX | UNIT |  |

|-------------------|--------------------------------|----------------------|-----|-----|-----|------|--|

| SW PULL           | -DOWN RESISTANCE               |                      |     |     |     |      |  |

| R <sub>SWPD</sub> | SW pull-down resistance        | EN = Lo              |     | 260 |     | Ω    |  |

| THERMAL           | L SHUTDOWN                     |                      |     |     |     |      |  |

| _                 | Thermal shutdown threshold (2) | Shutdown temperature |     | 145 |     | 00   |  |

| I <sub>SDN</sub>  | mermai shutdown threshold —    | Hysteresis           |     | 20  |     | °C   |  |

(2) Specified by design. Not production tested.

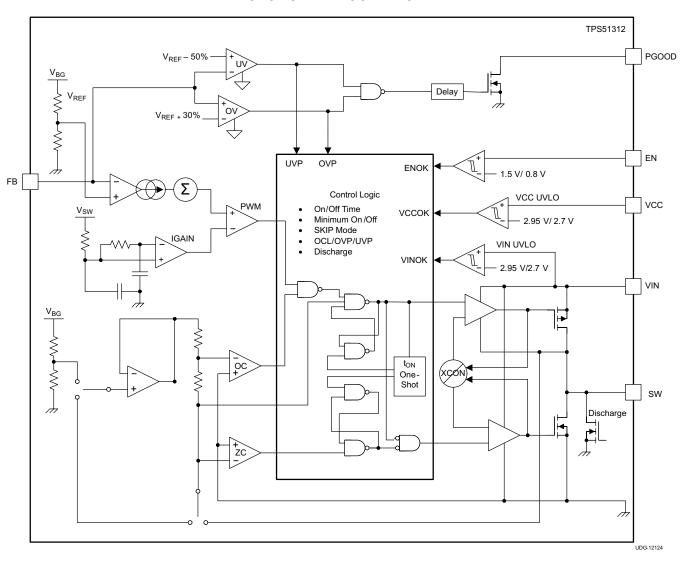

# DEVICE INFORMATION FUNCTIONAL BLOCK DIAGRAM

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

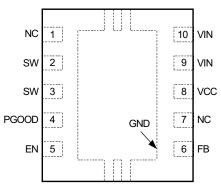

# **PIN FUNCTIONS**

| PI         | N   | 1/0 | DECORIDATION                                                                                               |

|------------|-----|-----|------------------------------------------------------------------------------------------------------------|

| NAME       | NO. | 1/0 | DESCRIPTION                                                                                                |

| EN         | 5   | 1   | Enable function for the switched-mode power supply (SMPS) (3.3-V logic compatible)                         |

| FB         | 6   | 1   | Voltage feedback. Also used for OVP, UVP and PGOOD determination.                                          |

| NC         | 1   |     | No connection Make no external connection to this nin                                                      |

| NC -       | 7   | _   | No connection. Make no external connection to this pin.                                                    |

| PGOOD      | 4   | 0   | Power good indicator. Requires external pull-up resistor.                                                  |

| CM         | 2   |     | Switching node output. Connect to external inductor. Also serve as current sensing negative input for over |

| SW         | 3   |     | current protection purpose                                                                                 |

| VCC        | 8   | 1   | Power supply for analog circuit.                                                                           |

| VIN        | 9   | _   | Main power conversion input and gate drive veltage cumply for cutout EETs                                  |

| VIIN       | 10  | ı   | Main power conversion input and gate-drive voltage supply for output FETs.                                 |

| Thermal Pa | ad  | I   | Ground terminal.                                                                                           |

# TEXAS INSTRUMENTS

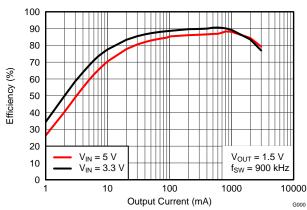

#### TYPICAL CHARACTERISTICS

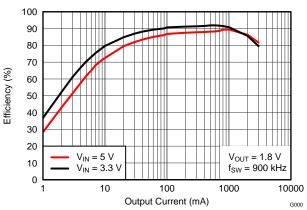

Figure 1. Efficiency vs. Output Current

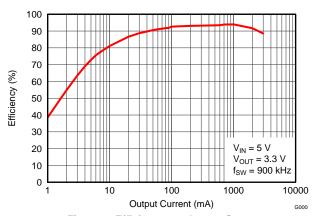

Figure 2. Efficiency vs. Output Current

Figure 3. Efficiency vs. Output Current

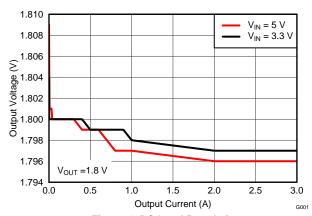

Figure 4. DC Load Regulation

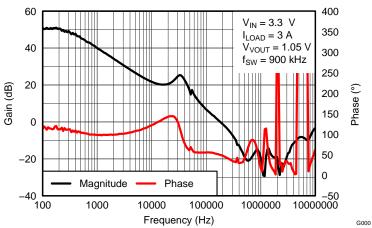

Figure 5. Bode Plot

Submit Documentation Feedback

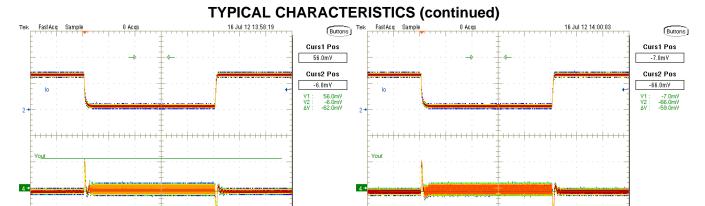

Figure 6. 3.3-V Input, 1.8-V Output from 0 A to 3 A

2.0A Ω Bw 50.0mV % Bw M 200μs 125MS/s A Ch2 \ 1.52A

Figure 7. 5-V Input, 1.8-V Output from 0 A to 3 A

$\begin{array}{cccc} \text{Ch2} & 2.0\text{A} & \Omega & \text{Bw} \\ \text{Ch4} & 50.0\text{mV} & \text{6} & \text{Bw} \\ \end{array}$

M 200μs 125MS/s A Ch2 \ 1.52A

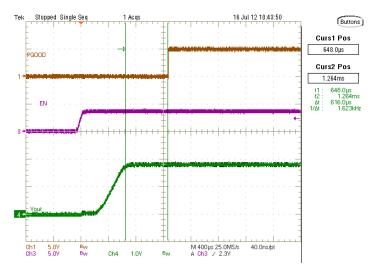

Figure 8. 5-V Input, 1.8-V Output Start-Up

#### APPLICATION INFORMATION

#### **Functional Overview**

TPS51312 is a D-CAP2 mode adaptive on time converter with internal integrator. Monolithically integrate high side and low side FET supports output current to a maximum of 3-ADC. The converter automatically runs in discontinuous conduction mode to optimize light load efficiency. A switching frequency of 900 kHz enables optimization of the power train for the cost, size and efficiency performance of the design.

# **PWM Operation**

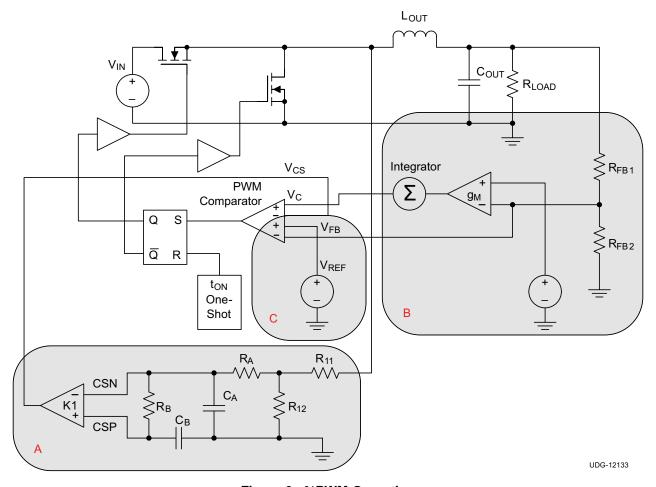

The PWM operation is comprised of three separate loops, A, B and C as shown in Figure 9.

Figure 9. ¾PWM Operation

# **Internal Current Loop (A)**

Loop A is the internal current loop. The current information is sampled, divided and averaged at the SW node. The RC time constant and the gain of the current sense amplifier is chosen to cover the wide range of power stage design intended for this application.

#### **Internal Voltage Loop (B)**

Loop B is the internal voltage loop. The feedback voltage information is compared to the voltage reference at the input of the  $g_M$  amplifier, the internal integrator is designed to provide a zero at the double pole location to boost phase margin at the desired crossover frequency.

#### Fast Feedforward Loop (C)

Loop C is the additional loop that acts a direct fast feedforward loop to enhance the transient response.

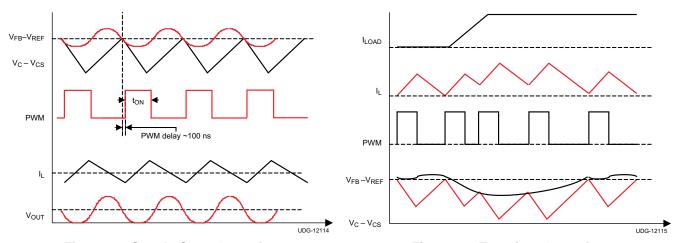

In steady state operation as shown in Figure 10, the on time is initiated by the interaction of the three loops mentioned above. When the  $(V_C - V_{CS})$  is rising above threshold defined by  $(V_{FB} - V_{REF})$ , the PWM comparator issues the on time pulse after the propagation delay. The demand of on time occurs when the artificial current has reached the valley point. The load regulation is maintained by the integrator provided by the  $g_M$  amplifier and integrator.

In transient operation as shown in Figure 11, the benefit of this topology is becoming evident. In an all MLCC output configuration, especially when the output capacitance is low, when the load step is applied, the output voltage is immediately discharged to try to keep the load demand. The immediate reflection of the load demand is instantly reflected in the FB voltage. The  $(V_{FB} - V_{REF})$  is thus served as a termination voltage level for the  $(V_{C} - V_{CS})$ , thus modulating the initiation of the on time. The transient response can be improved further by amplifying the difference between  $V_{FB}$  and the  $V_{RFF}$  reference.

Figure 10. Steady-State Operation

**Figure 11. Transient Operation**

#### **PWM Frequency**

The TPS51312 operates at a switching frequency of 900 kHz.

#### **Light Load Power Saving Features**

The TPS51312 offers an automatic pulse-skipping feature to provide excellent efficiency over the entire load range. The converter senses the current during low side FET on and prevents negative current flow by turning off the low side FET. This saves power by eliminating re-circulation of the inductor current. When the bottom FET is turned off, the converter enters discontinuous mode, and the switching frequency decreases, reducing switching loss.

#### **Power Sequences**

TPS51312 initiates the soft-start process when the EN, VIN and VCC pins are ready. The soft-start time 300  $\mu$ s when the reference voltage is between 0 V and 0.6 V ( $V_{REF}$ ). The actual voltage ramp up time is the same as that of the  $V_{REF}$  start-up time, which is 300  $\mu$ s.

# **Power Good Signal**

The TPS51312 has one open-drain power good (PGOOD) pin. During initial startup, there is a 1.3-ms power good high propagation delay after EN goes high. The PGOOD de-asserts when the EN is pulled low or an undervoltage condition on VCC or VIN or any other faults (such as V<sub>OUT</sub>, UVP, OCP, OVP) that require latch off action is detected.

#### **Protection Features**

The TPS51312 offers many features to protect the converter power chain as well as the system electronics.

#### Input Undervoltage Protection on V<sub>CC</sub> and V<sub>IN</sub> (UVLO)

The TPS51312 continuously monitor the voltage on the  $V_{CC}$  and  $V_{IN}$  to ensure the voltage level is high enough to bias the converter properly and to provide sufficient gate drive potential to maintain high efficiency for the converter. The converter starts with  $V_{CC}$  and  $V_{IN}$  approximately 2.95 V and has a nominal of 250 mV of hysteresis, assuming EN is above the logic threshold level. If the UVLO level is reached for either  $V_{CC}$  or  $V_{IN}$ , the converter transitions the SW node into a tri-state and remains off until the device is reset by both  $V_{CC}$  and  $V_{IN}$  reaches 2.95 V (nominal). The PGOOD is deasserted when UVLO is detected and remains low until the device is reset.

#### **Output Overvoltage Protection (OVP)**

The TPS51312 has OVP protection circuit. An OVP event is detected when the FB voltage is approximately 130% x 0.6VREF. In this case, the converter de-asserts the PGOOD signal and performs the overvoltage protection function. The converter latches off both high-side and low-side FET and remains in this state after a delay of 1.9  $\mu$ s (typ) until the device is reset by EN, or  $V_{CC}$  or  $V_{IN}$ .

#### **Output Undervoltage Protection (UVP)**

Output undervoltage protection works in conjunction with the current protection described in the Overcurrent and Current Limit Protection section. If the FB voltage drops below 50% x 0.6  $V_{REF}$ , after a delay of 2.4  $\mu$ s (typ), the converter latches off. Undervoltage protection can be reset by EN,  $V_{CC}$  or  $V_{IN}$ .

#### **Overcurrent and Current Limit Protection**

The TPS51312 provides an overcurrent protection function. The nominal OCP is 4.8-A DC. When the current limit is exceeded for consecutive 9 cycles, the converter latches off and remains latched off until it is reset by EN,  $V_{CC}$  or  $V_{IN}$ .

The TPS51312 also provides current limit protection function. If the sense current is above the OCL setting, the converter delays the next on pulse until the current level drops below the OCL limit. Current limiting occurs on a pulse-by-pulse basis. During a fast or very fast overcurrent event, the output voltage tends to droop until the UVP limit is reached. Then the converter de-asserts the PGOOD signal, and latches off after a typical delay time of 2.4  $\mu$ s. The converter remains in this state until the device is reset by EN,  $V_{CC}$  or  $V_{IN}$ .

#### **Thermal Protection**

The TPS51312 has an internal temperature sensor. When the die temperature reaches a nominal of 145°C, the device shuts down until the temperature cools by approximately 20°C. Then the converter restarts. The thermal shutdown is an non-latched behavior.

www.ti.com SLUSB57 -SEPTEMBER 2012

#### REFERENCE DESIGN

# **Application Schematic**

Figure 12 shows the application schematic..

Figure 12. Reference Design Schematic

**Table 1. Reference Design List of Materials**

| FUNCTION                    | MANUFACTURER | PART NUMBER        |

|-----------------------------|--------------|--------------------|

| Output Inductor             | Vishay       | IHLP-2020BZ-01     |

| Companie Outrout Compaitant | Panasonic    | ECJ2FB0J226M       |

| Ceramic Output Capacitors   | Murata       | GRM21BR60J226ME39L |

# **Design Procedure**

# Step One. Determine the specifications.

- V<sub>OUT</sub> = 1.8 V

- $I_{CC(max)} = 3 A$

- di/dt = 2.5 A/µs

#### Step Two. Determine the system parameters.

The input voltage range and operating frequency are of primary interest. For example,

- V<sub>IN</sub> = V<sub>CC</sub> = 5 V

- $f_{SW} = 900 \text{ kHz}.$

# **STRUMENTS**

#### Step Three. Set the output voltage.

Use Equation 1 to determine the output voltage.

$$V_{OUT} = V_{REF} \times \left(\frac{R_{FB1} + R_{FB2}}{R_{FB2}}\right) \tag{1}$$

The output voltage is determined by VREF (0.6 V) and the resistor dividers (RFB1 and RFB2). The output voltage is regulated to the FB pin. For the current reference design of 1.8 V, select 40 k $\Omega$  as the value for R<sub>FB1</sub> and 20 k $\Omega$  as the value of R<sub>FB2</sub> (see Figure 12). As a recommendation, choose a value of less 50 k $\Omega$  both resisters. Place a 47-pF, feedford capacitor in parallel with R<sub>FB1</sub> to help reduce the output voltage ripple during the transition from DCM to CCM.

#### Step Four. Determine inductor value and choose inductor.

Smaller inductance yields better transient performance but the consequence is higher ripple and lower efficiency. Higher values have the opposite characteristics. It is common practice to limit the ripple current to 25% to 50% of the maximum current. In this case, use 40%:

$$I_{D} = 3A \times 0.4 = 1.2A$$

where

- f<sub>SW</sub> = 900 kHz

- V<sub>IN</sub> = 5 V

•

$$V_{OUT} = 1.8 \text{ V}$$

(2)

$$L = \frac{V \times dT}{I_{P-P}} = \left(\frac{\left(V_{IN} - V_{OUT}\right)}{I_{P-P}}\right) \times \left(\frac{V_{OUT}}{\left(f_{SW} \times V_{IN}\right)}\right) = 1 \mu H$$

(3)

For this application, choose a 1-μH, 18.9-mΩ inductor from Vishay part number IHLP-2020BZ-01.

#### Step Five. Determine the output capacitance.

To determine C<sub>OUT</sub> based on transient and stability requirement, first calculate the minimum output capacitance for a given transient.

Equation 4 and Equation 5 calculate the minimum output capacitance for meeting the transient requirement.

$$C_{OUT(min\_under)} = \frac{L \times \Delta I_{LOAD(max)}^{2} \times \left(\frac{V_{VOUT} \times t_{SW}}{V_{IN(min)}} + t_{MIN(off)}\right)}{2 \times \Delta V_{LOAD(insert)} \times \left(\left(\frac{V_{IN(min)} - V_{VOUT}}{V_{IN(min)}}\right) \times t_{SW} - t_{MIN(off)}\right) \times V_{VOUT}}$$

$$C_{OUT(min\_over)} = \frac{L_{OUT} \times \left(\Delta I_{LOAD(max)}\right)^{2}}{2 \times \Delta V_{LOAD(release)} \times V_{VOUT}}$$

(5)

Table 2. Choosing Output Inductors and Output Capacitors

| TEMPERATURE                   | OUTPUT<br>VOLTAGE                          | INDUCTANCE |        | TPUT<br>CITORS | FAST<br>FEEDFORWARD               |  |  |

|-------------------------------|--------------------------------------------|------------|--------|----------------|-----------------------------------|--|--|

|                               | V <sub>OUT</sub> (V) L <sub>OUT</sub> (μH) |            | NUMBER | VALUE (μF)     | CAPACITOR<br>C <sub>FF</sub> (pF) |  |  |

|                               | 1.5                                        | 1          | 1      |                |                                   |  |  |

| -10°C ≤ T <sub>A</sub> ≤ 85°C | 1.8                                        | 1          | 1      |                |                                   |  |  |

|                               | 3.3                                        | 2.2        | 2      | 22             | 47                                |  |  |

|                               | 1.5                                        | 1          | 2      | 22             | 47                                |  |  |

| -40°C ≤ T <sub>A</sub> ≤ 85°C | 1.8                                        | 1          | 2      |                |                                   |  |  |

|                               | 3.3                                        | 2.2        | 3      |                |                                   |  |  |

Product Folder Links: TPS51312

Submit Documentation Feedback

# Step Six. Establishing the internal compensation loop.

The TPS51312 is designed with an internal compensation loop. The internal integrator zero location is approximately 60 kHz. During the time that the power stage double pole frequency contributed by the  $L_{OUT}$  and  $C_{OUT}$  is less than or equal to that of the zero location, the converter is stable with sufficient margin.

#### Step Seven. Select decoupling and peripheral components.

For TPS51312 peripheral capacitors use the following minimum value of ceramic capacitance, X5R or better temperature coefficient is recommended. Tighter tolerances and higher voltage ratings are always appropriate.

$V_{CC}$  and  $V_{IN}$  decoupling  $\geq 2 \times 10 \mu F$ , 6.3 V

Pull up resistor on PGOOD =  $100 \text{ k}\Omega$

#### **Layout Considerations**

Good layout is essential for stable power supply operation. Follow these guidelines for an efficient PCB layout.

- Place V<sub>IN</sub>, V<sub>CC</sub> decoupling capacitors as close to the device as possible.

- Use wide traces for the VIN, SW and GND pins. These nodes carry high current and also serve as heat sinks.

- Place FB and voltage setting dividers as close to the device as possible.

- Place an R-C network from SW to GND to help to reduce the voltage spikes on the SW pin.

www.ti.com 18-Jul-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TPS51312DRCR     | ACTIVE | VSON         | DRC                | 10   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | S51312                  | Samples |

| TPS51312DRCT     | ACTIVE | VSON         | DRC                | 10   | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | S51312                  | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 18-Jul-2023

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

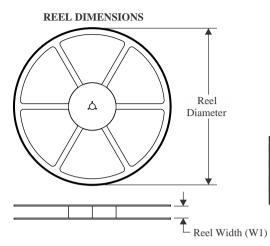

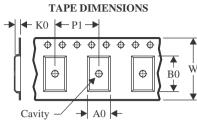

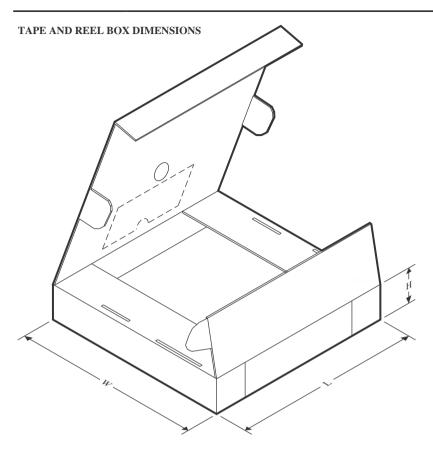

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

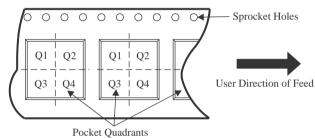

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS51312DRCR | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51312DRCR | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51312DRCT | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS51312DRCT | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 3-Jun-2022

#### \*All dimensions are nominal

| 7 III dilitoriciono di o nominali |              |                 |      |      |             |            |             |  |

|-----------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| Device                            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

| TPS51312DRCR                      | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |  |

| TPS51312DRCR                      | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |  |

| TPS51312DRCT                      | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |  |

| TPS51312DRCT                      | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |  |

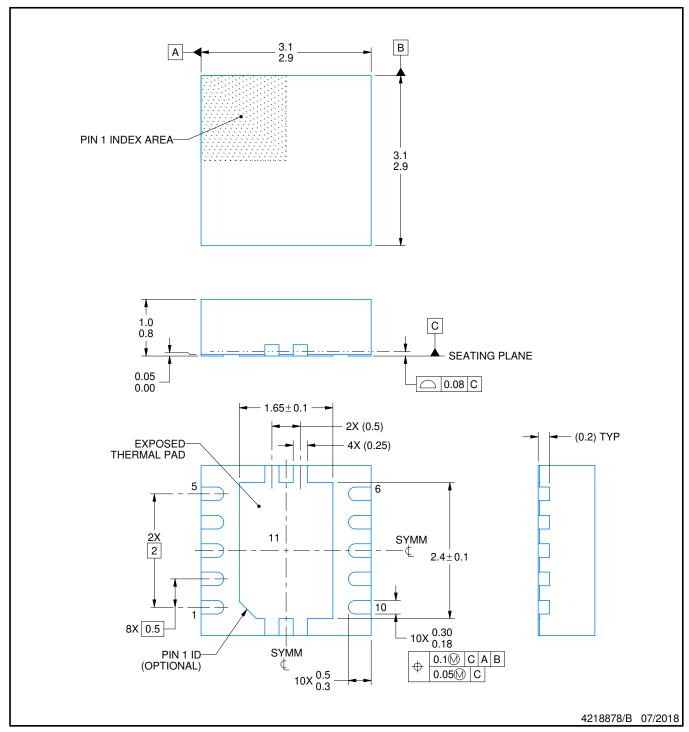

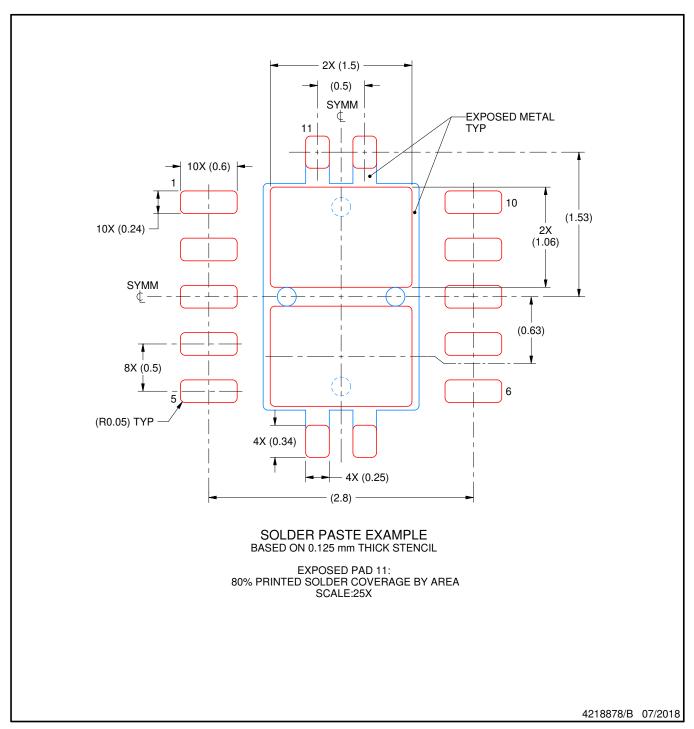

3 x 3, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

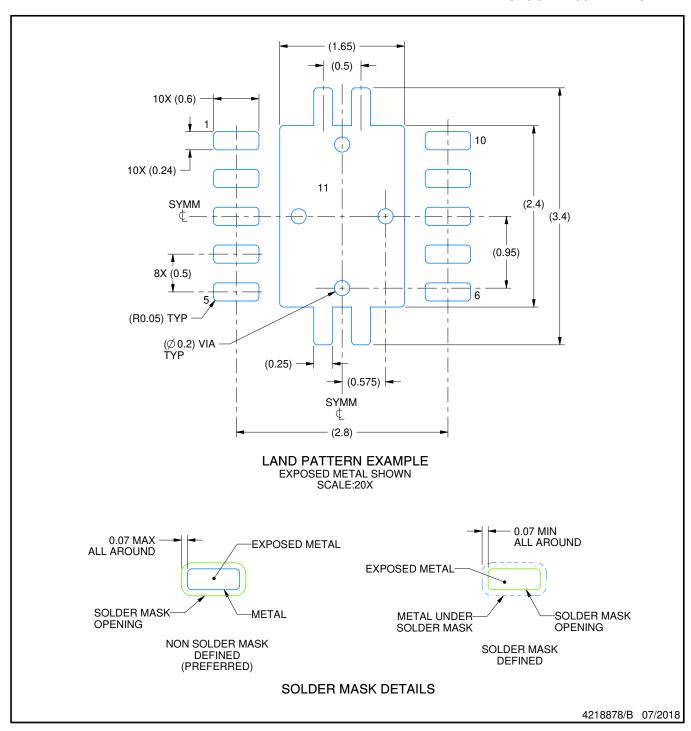

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated