# Dual-Mode WPC/PMA 5 Watt Wireless Power Receiver IC

## **Product Datasheet**

## P9028AC Features

- Single Chip Receiver (Rx) Solution

- WPC v1.1.2 Compliant

- PMA v1, v3 Pre-Release Compatible with Options

- Advanced WPC v1.1.2 Foreign Object Detection (FOD)

- Programmable FOD setting via external resistor and I<sup>2</sup>C registers

- Programmable current limit via external resistor

- Integrated Full-Bridge Synchronous Rectifier

- Integrated 5V @ 1A LDO Regulator Output

- Closed-loop power transfer control between TX and RX

- I<sup>2</sup>C interface provides VRECT, lout and switching frequency values

- Open-Drain LED Indicator Output

- Over-Temperature/Voltage/Current Protection

## Applications

- WPC-Compliant and PMA-Compatible Wireless Chargers for Mobile Applications.

- Cellular Mobile Phones

- Tablets, DSC, DVC and Handhelds

## Introduction

The P9028AC is an integrated single-chip, dual-mode WPC v1.1.2-compliant and PMA v1.0-compatible, wireless power receiver IC with advanced WPC v1.1.2 Foreign Object Detection (FOD). The device operates with an AC power signal from a resonant tank and converts it into a regulated 5V output voltage, which can be used to supply power to a mobile application. It includes a high efficiency Synchronous Full Bridge Rectifier and 5V tracking LDO output stage. The P9028AC dual-mode operation automatically detects the transmitter type and initiates either WPC or PMA AC modulation communication protocols with optimal efficiency.

The device includes the control circuit required to modulate the load to transmit WPC-compliant or PMA-compatible message packets to the base station. It uses minimal external components to reduce overall solution area.

The P9028AC employs advanced programmable WPC FOD techniques to detect foreign metallic objects placed on the transmitter base station derived from a transmitted and received power transfer algorithm.

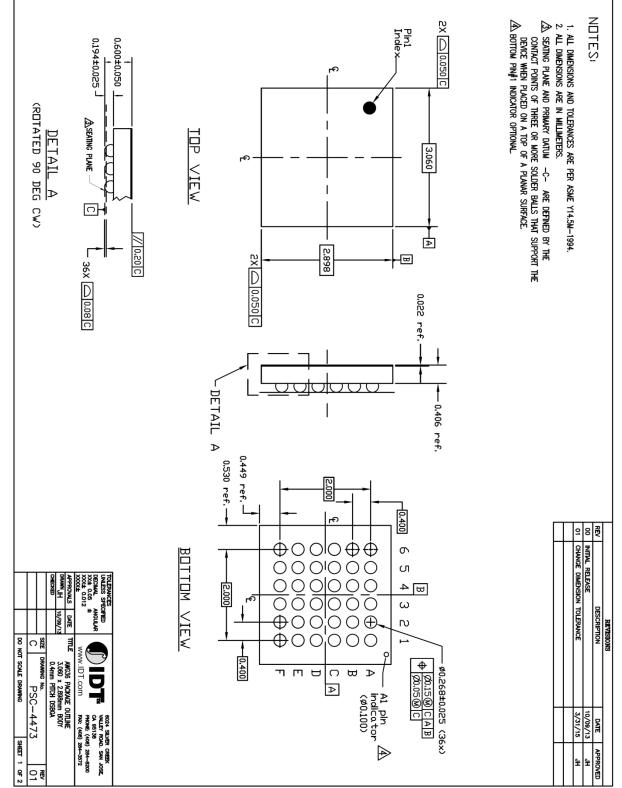

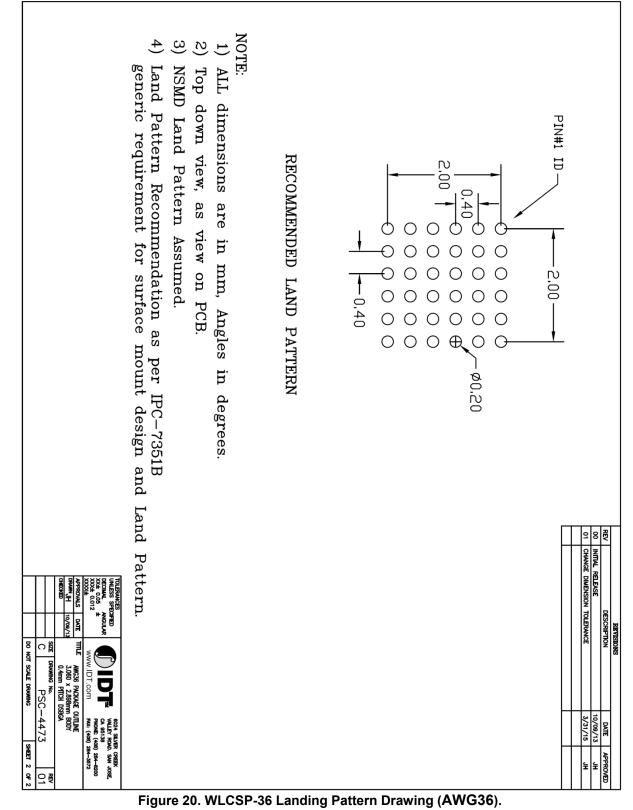

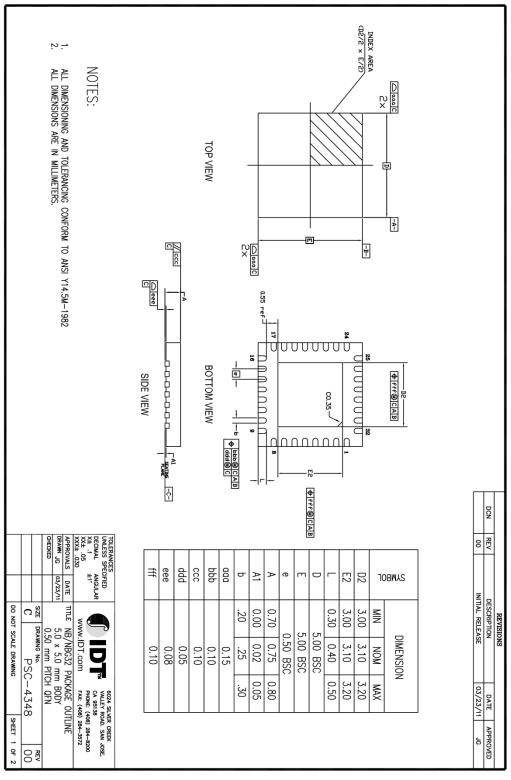

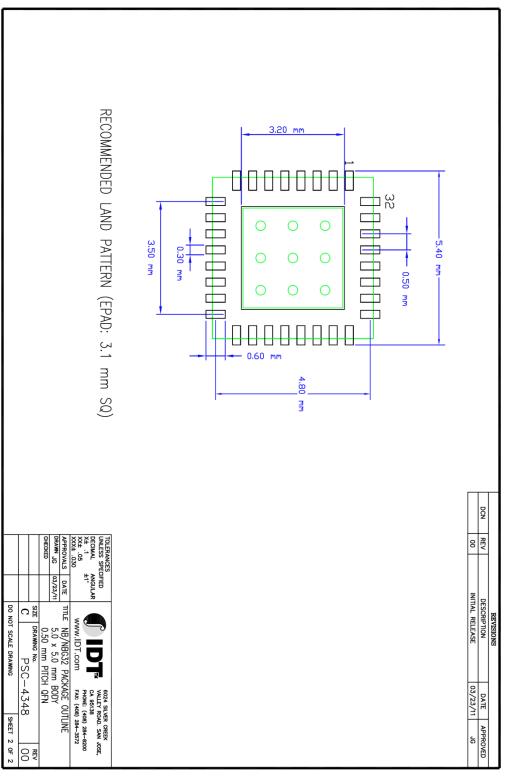

The P9028AC is available in a 36 ball 3mm X 3mm WLCSP or 32 pin 5mm X 5mm TQFN package.

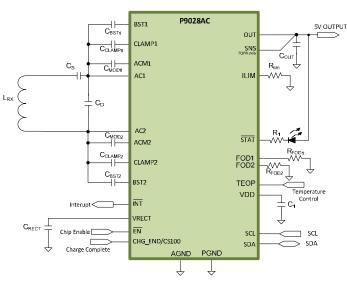

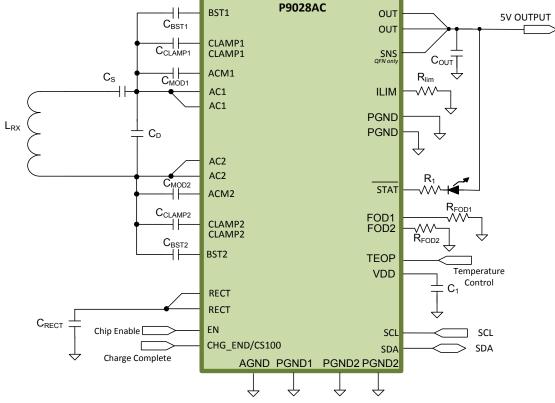

## **Typical Application Circuit**

Packages: WLCSP-36 6x6 balls (3.06mm x 2.9mm) (See page 33) TQFN-32 5x5mm (See page 35) Ordering information: (See page 38)

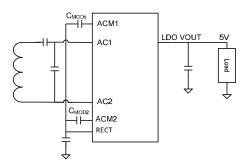

## SIMPLIFIED APPLICATION DIAGRAM

Figure 1. Simplified Applications Schematic.

## **ABSOLUTE MAXIMUM RATINGS**

These absolute maximum ratings are stress ratings only. Stresses greater than those listed below (Table 1 and Table 2) may cause permanent damage to the device. Functional operation of the P9028AC at absolute maximum ratings is not implied. Application of the absolute maximum rating conditions affects device reliability.

### Table 1. Absolute Maximum Ratings Summary.

| Description                                                      | Value                  | Units |

|------------------------------------------------------------------|------------------------|-------|

| AC1, AC2, VRECT, ACM1, ACM2, CLAMP1, CLAMP2                      | -0.3 to 20             | V     |

| BST1, BST2                                                       | -0.3 to (AC1, AC2 + 6) | V     |

| EN, STAT, SCL, SDA, OUT, SNS, TEOP, RLIM, CS100, FOD1, FOD2, VDD | -0.3 to 6              | V     |

| PGND, PGND1, PGND2, AGND                                         | -0.3 to 0.3            | V     |

| Output Current OUT                                               | 1.5                    | Α     |

| Input Current AC1, AC2                                           | 2                      | ARMS  |

#### Table 2. Package Thermal Information.<sup>1,2,3,4</sup>

| Symbol            | Description                                   | TQFN Rating | WLCSP Rating<br>(7 thermal vias) | Units |

|-------------------|-----------------------------------------------|-------------|----------------------------------|-------|

| $\Theta_{JA}$     | Thermal Resistance Junction to Ambient        | 35          | 70                               | °C/W  |

| Θ <sub>JC</sub>   | Thermal Resistance Junction to Case           | 29.6        | 0.9                              | °C/W  |

| Θ <sub>JB</sub>   | Thermal Resistance Junction to Board          | 2.4         | 47.3                             | °C/W  |

| TJ                | Operating Junction Temperature                | 0 to +125   | 0 to +125                        | °C    |

| T <sub>A</sub>    | Operating Ambient Temperature                 | 0 to +85    | 0 to +85                         | °C    |

| T <sub>STG</sub>  | Storage Temperature                           | -55 to +150 | -55 to +150                      | °C    |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at Leads, 10s) | 300         | 300                              | °C    |

Note 1: The maximum power dissipation is  $P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$  where  $T_{J(MAX)}$  is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

Note 2: This thermal rating was calculated on JEDEC 51 standard 4-layer board with dimensions 3" x 4.5" in still air conditions.

Note 3: Actual thermal resistance is affected by PCB size, solder joint quality, layer count, copper thickness, air flow, altitude, and other unlisted variables. Note 4: For the NBG32 package, connecting the 5 mm X 5 mm EP to internal/external ground planes with a 5x5 matrix of PCB plated-through-hole (PTH) vias, from top to bottom sides of the PCB, is recommended for improving the overall thermal performance. For the WLCSP (AWG36) package, connecting the 7 thermal balls to internal/external ground planes from top to bottom sides of the PCB.

#### Table 3. ESD Information.

| Test<br>Model | Pins | Rating | Units |

|---------------|------|--------|-------|

| HBM           | All  | ±1500  | V     |

| CDM           | All  | ±500   | V     |

# **ELECTRICAL SPECIFICATION TABLE**

$v_{\text{RECT}}$ =6V, C<sub>OUT</sub>=1uF, C<sub>VRECT</sub>=20uF,  $v_{\overline{EN}}$ =0V, T<sub>A</sub> = 0C to 85°C, unless otherwise noted. Typical values are at 25°C, unless otherwise noted. Table 4. Device Characteristics.

| Symbol                | Description                     | Conditions                                                  | Min  | Тур  | Max  | Units |

|-----------------------|---------------------------------|-------------------------------------------------------------|------|------|------|-------|

| Under-volta           | age Lock-out                    |                                                             |      |      |      |       |

| V <sub>UVLO</sub>     | Under-voltage lockout           | Rising voltage on VRECT                                     | 2.3  | 2.5  | 2.7  | V     |

| V <sub>UVLO-HYS</sub> | UVLO hysteresis                 |                                                             |      | 50   |      | mV    |

| Over-volta            | ge Protection                   |                                                             |      |      |      |       |

| V <sub>OVP</sub>      | Over-voltage VRECT              | Rising voltage on VRECT                                     | 12.8 | 13.3 | 13.8 | V     |

| V <sub>OVP-HYS</sub>  | Over-voltage hysteresis         |                                                             |      | 1.5  |      | V     |

|                       | ply Current                     |                                                             |      |      |      |       |

| Quiescent curre       | Quieseent eurrent               | I <sub>OUT</sub> = 0mA, with internal load                  | 14   | 16   | 18   | mA    |

| I <sub>RECT</sub>     | Quiescent current               | I <sub>OUT</sub> = 0mA, no internal load                    | 2    | 3    | 4    | mA    |

| Low-drop-o            | out Regulator                   |                                                             |      |      |      |       |

| I <sub>LIM</sub>      | Output current limit            | R <sub>LIM</sub> =30kΩ                                      | 1.15 | 1.6  | 1.95 | A     |

| LIM                   | OUT                             | R <sub>LIM</sub> <25KΩ (Note 1)                             |      |      | 2.0  | ~     |

| V <sub>OUT</sub>      | Regulated output voltage OUT    | I <sub>OUT</sub> = 0mA to 1000mA                            | 5.04 | 5.3  | 5.56 | V     |

| VDD Voltag            | ge (For Internal Supply Use     | Only)                                                       |      |      |      |       |

| $V_{DD_{INT}}$        | Internal Supply Voltage         | $I_{VDD}$ = 100µA, maximum allowable load for test purposes | 4.44 | 4.54 | 4.64 | V     |

| Thermal Sh            | nutdown                         | •                                                           |      | •    | •    |       |

| <b>-</b>              | Thermal shutdown                | Temperature rising                                          |      | 150  |      | °C    |

| T <sub>SHD</sub>      | threshold                       | Temperature falling                                         |      | 130  |      | °C    |

| Digital Inpu          | ut and Output Characteristic    | S                                                           |      |      |      |       |

| V <sub>IL</sub>       | Logic level input low           | EN, CS100, TEOP                                             |      |      | 0.4  | V     |

| V <sub>IH</sub>       | Logic level input high          | ĒN, CS100, TEOP                                             | 1.3  |      |      | V     |

| V <sub>OL</sub>       | Open drain voltage<br>STAT, INT | I <sub>STAT</sub> = 4mA                                     |      |      | 400  | mV    |

| P                     | Pull-down resistance            | EN, CS100                                                   |      | 200  |      | kΩ    |

| R <sub>PD</sub>       |                                 | TEOP                                                        |      | 1000 |      | K12   |

| Switch On-            | resistance                      |                                                             |      |      |      |       |

|                       | ACM1, ACM2 switches             |                                                             |      | 1600 |      | mΩ    |

| R <sub>DSON</sub>     | CLAMP1, CLAMP2<br>switches      | 150mA                                                       | 400  | 475  | 680  | mΩ    |

|                       | Rectifier bridge switches       |                                                             | 60   | 110  | 180  | mΩ    |

# **ELECTRICAL SPECIFICATION TABLE**

$V_{RECT}=6V$ ,  $C_{OUT}=1uF$ ,  $C_{VRECT}=20uF$ ,  $V_{EN}=0V$ ,  $T_{A}=0C$  to 85°C, unless otherwise noted. Typical values are at 25°C, unless otherwise noted. Table 4. Device Characteristics (Continued).

| Symbol              | Description                                                    | Conditions | Min                     | Тур | Max | Units |

|---------------------|----------------------------------------------------------------|------------|-------------------------|-----|-----|-------|

| SCL, SDA (          | I <sup>2</sup> C Interface)                                    |            |                         |     |     |       |

| f <sub>SCL</sub>    | Clock Frequency                                                |            | 0                       |     | 400 | kHz   |

| t <sub>LOW</sub>    | Clock Low Period                                               |            | 1.3                     |     |     | μs    |

| t <sub>HIGH</sub>   | Clock High Period                                              |            | 0.6                     |     |     | μs    |

| t <sub>HD,STA</sub> | Hold Time (Repeated) for<br>START Condition                    |            | 0.6                     |     |     | μs    |

| t <sub>su:sta</sub> | Set-up Time for<br>Repeated START<br>Condition                 |            | 0.6                     |     |     | μs    |

| t <sub>su:dat</sub> | Data Setup Time                                                |            | 100                     |     |     | ns    |

| t <sub>HD:DAT</sub> | Data Hold Time                                                 |            |                         |     | 0.9 | μs    |

| t <sub>SU:STO</sub> | Setup Time for STOP<br>Condition                               |            | 0.6                     |     |     | μs    |

| t <sub>BUF</sub>    | Bus Free Time Between<br>STOP and START<br>Condition           |            | 1.3                     |     |     | μs    |

| t <sub>R</sub>      | Rise Time of Both SDA<br>and SCL Signals (Note 1,2)            |            | 20 + 0.1 C <sub>B</sub> |     | 300 | ns    |

| t <sub>F</sub>      | Fall Time of Both SDA<br>and SCL Signals (Note 1,2)            |            | 20 + 0.1 C <sub>B</sub> |     | 300 | ns    |

| T <sub>SP</sub>     | Spike Pulse Widths<br>Suppressed by Input<br>Filter (Note 1,2) |            | 0                       |     | 50  | ns    |

| C <sub>B</sub>      | Capacitive Load for Each<br>Bus Line (Note 1,2)                |            |                         |     | 400 | pF    |

| C <sub>BIN</sub>    | SCL, SDA Input<br>Capacitance (Note 1,2)                       |            |                         |     | 60  | pF    |

| V <sub>IL</sub>     | Input Threshold Low                                            |            |                         |     | 0.4 | V     |

| V <sub>IH</sub>     | Input Threshold High                                           |            | 1.4                     |     |     | V     |

| I <sub>I</sub>      | Input Leakage Current                                          |            | -1.0                    |     | 1.0 | μA    |

Note 1: Guaranteed by design. Not 100% tested in production.

Note 2: Guaranteed by design/simulation data.

**Product Datasheet**

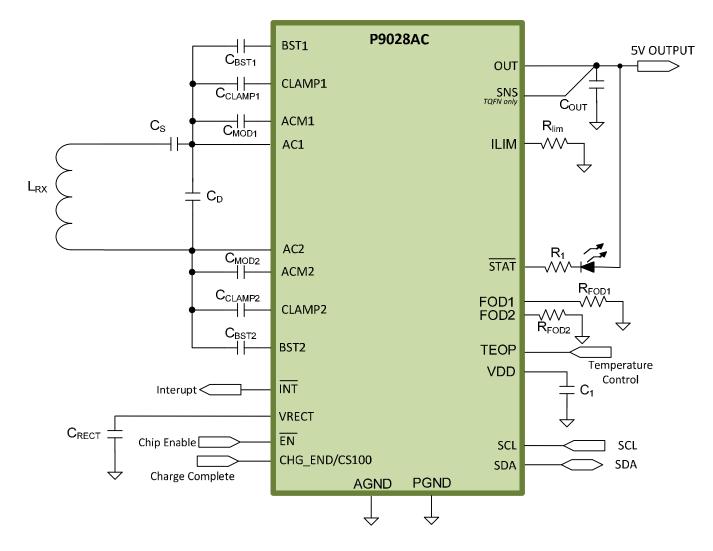

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Typical Performance Characteristics: System Efficiency versus RX Output Power  $\overline{EN}~$  = RESET = 0, TA = 25°C

Figure 2. P9028AC WPC and PMA System Efficiency.

Product Datasheet

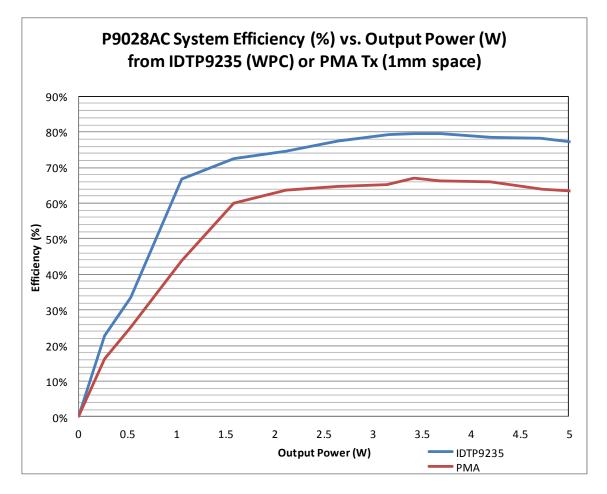

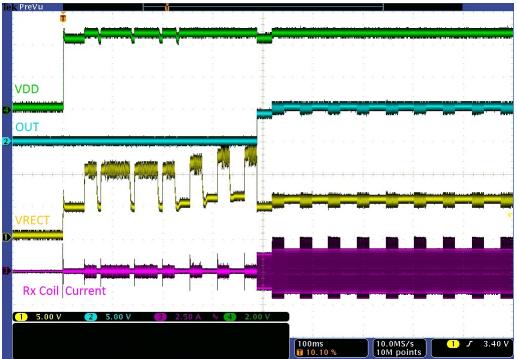

Figure 3. P9028AC RX Startup-to-out waveforms from IDTP9235 TX, I<sub>OUT</sub>=0A, CH1=VRECT, CH2=V<sub>OUT</sub>, CH3=Rx coil Current, CH4=VDD.

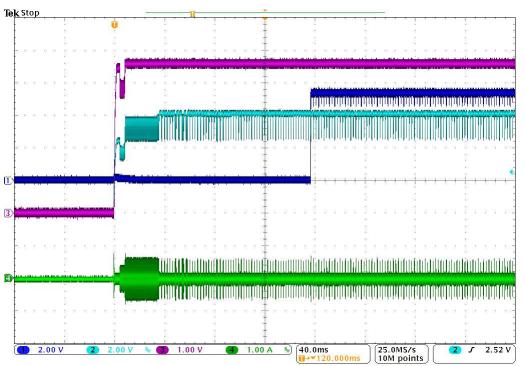

Figure 4. P9028AC RX Startup-to-out waveforms from IDTP9235 TX, I<sub>OUT</sub>=1A, CH1=VRECT, CH2= V<sub>OUT</sub>, CH3=Rx coil Current, CH4=VDD.

**Product Datasheet**

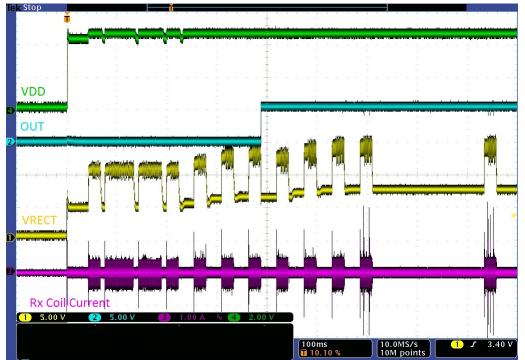

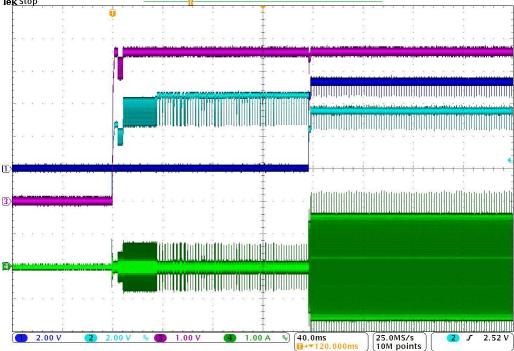

Figure 5. P9028AC RX Startup-to-out waveforms from PMA TX, I<sub>OUT</sub>=0A, CH1= V<sub>OUT</sub>, CH2= VRECT, CH3= VDD, CH4= Rx coil Current.

Figure 6. P9028AC RX Startup-to-out waveforms from PMA TX, I<sub>OUT</sub>=0A, CH1= V<sub>OUT</sub>, CH2= VRECT, CH3= VDD, CH4= Rx coil Current.

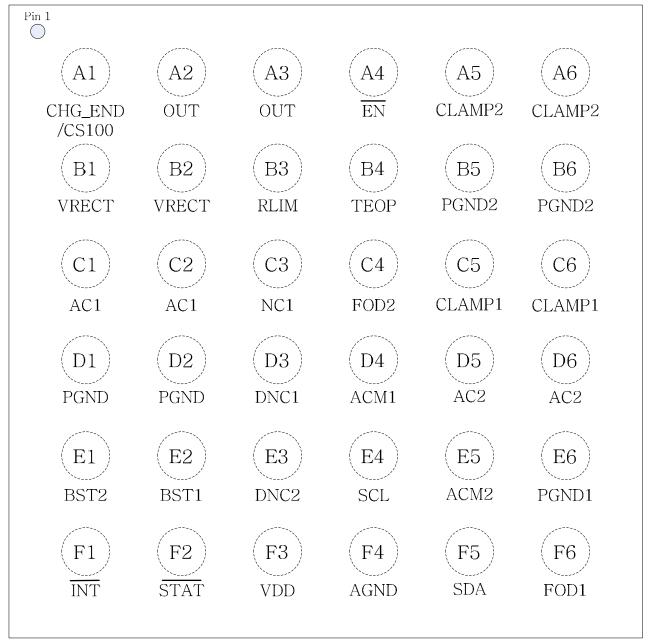

## **PIN CONFIGURATION & DESCRIPTION**

Figure 7. P9028AC WLCSP Pin Configuration (Top View).

### Table 5. WLCSP Pin Descriptions.

| Pin #    | Name              | Туре     | Description                                                                                                                            |  |

|----------|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|          |                   |          | Active-high input pin. Default setting is a Charge-End active-high input from                                                          |  |

|          |                   |          | an external battery charger to terminate power transfer. Alternatively, a                                                              |  |

| A1       | CHG_END/CS100     | I        | Charge-Status active high input which will send a WPC Charge Status packet with value 100 (100% charge). In PMA mode, an End Of Charge |  |

|          |                   |          | (EOC) command will be sent. This pin has an internal pull down resistor.                                                               |  |

| A2       | OUT_A2            | 0        | 5V LDO output. A 0.1µF ceramic capacitor and a 1µF to 10µF ceramic                                                                     |  |

| A3       | OUT_A3            | 0        | capacitor must be connected between this pin and ground.                                                                               |  |

|          |                   |          | Active-low enable pin. If this pin is pulled high, the chip will send a WPC                                                            |  |

| A4       | EN                | I        | EOP packet with code 0x04 (over-voltage code) or a PMA EOC signal. This<br>pin has an internal pull down resistor.                     |  |

| A5       | CLAMP2 A5         |          | · · · · ·                                                                                                                              |  |

| A6       | CLAMP2 A6         | I        | AC clamp input 2.                                                                                                                      |  |

| B1       | VRECT_B1          | _        |                                                                                                                                        |  |

| B2       | VRECT B2          | 0        | Output of the full-wave rectifier.                                                                                                     |  |

|          |                   |          | Current-limit resistor. A resistor connected between this pin and ground                                                               |  |

| B3       | RLIM              | Ι        | sets the current limit of the 5V LDO.                                                                                                  |  |

|          |                   |          | Active-high over-temperature input pin. If this pin is pulled high, the chip will                                                      |  |

| B4       | TEOP              | I        | send a WPC EOP packet with code 0x03 (over-temperature code) or a PMA                                                                  |  |

| B5       | PGND2 B5          |          | EOC signal. This pin has an internal pull down resistor.                                                                               |  |

| B6       | PGND2_B5          | -        | Power ground for the AC clamp FETs.                                                                                                    |  |

| C1       | AC1 C1            |          |                                                                                                                                        |  |

| C2       | AC1_C2            | Ι        | AC1 input to the Internal full-wave rectifier.                                                                                         |  |

| C3       | NC1               | NC       | Not internally connected. This pin may be connected to ground to improve                                                               |  |

|          |                   |          | thermal performance or to other pins to facilitate routing.                                                                            |  |

| C4<br>C5 | FOD2<br>CLAMP1 C5 | I        | Foreign object detection 2 offset adjustment.                                                                                          |  |

| C6       | CLAMP1 C6         | I        | AC clamp input 1.                                                                                                                      |  |

| D1       | PGND D1           |          |                                                                                                                                        |  |

| D2       | PGND_D2           | -        | Power ground for the full-wave rectifier.                                                                                              |  |

| D3       | DNC1              | DNC      | DO NOT connect to this pin, it is internally connected.                                                                                |  |

| -        |                   | - DINO   | This pin must be left floating.                                                                                                        |  |

| D4       | ACM1              |          | AC Modulation input 1.                                                                                                                 |  |

| D5<br>D6 | AC2_D5<br>AC2_D6  | I        | AC2 input to the Internal full-wave rectifier.                                                                                         |  |

| E1       | BST2              | 0        | Bootstrap output for high-side rectifier FET 2.                                                                                        |  |

| E2       | BST1              | 0        | Bootstrap output for high-side rectifier FET 1.                                                                                        |  |

| E3       |                   | DNC      | INTERNALLY CONNECTED. DO NOT connect to this pin. This pin must be                                                                     |  |

|          | DNC2              | DNC      | left floating.                                                                                                                         |  |

| E4       | SCL               | <br>     | I <sup>2</sup> C clock port. If not used, connect to ground.                                                                           |  |

| E5       | ACM2              | <u> </u> | AC Modulation input 2.                                                                                                                 |  |

| E6       | PGND1             | -        | Power ground for modulation FETs.<br>Interrupt output. Open drain output pin. A low condition indicates that an                        |  |

| F1       | INT               | 0        | OC, OV, or OT event has occurred.                                                                                                      |  |

| 50       | 0747              |          | Status output (STAT). Open drain output pin. A low condition indicates that                                                            |  |

| F2       | STAT              | 0        | power is being transferred.                                                                                                            |  |

| F3       | VDD               | 0        | Internal voltage supply. Connect a 1uF to 10uF capacitor between this pin                                                              |  |

|          |                   |          | and ground. Must be left unloaded.                                                                                                     |  |

| F4       | AGND              | -        | Analog ground connection.                                                                                                              |  |

| F5       | SDA<br>FOD1       | I/O      | I <sup>2</sup> C data port. If not used, connect to ground.                                                                            |  |

| F6       | FOD1              |          | Foreign object detection 1 to select internal FOD1 settings.                                                                           |  |

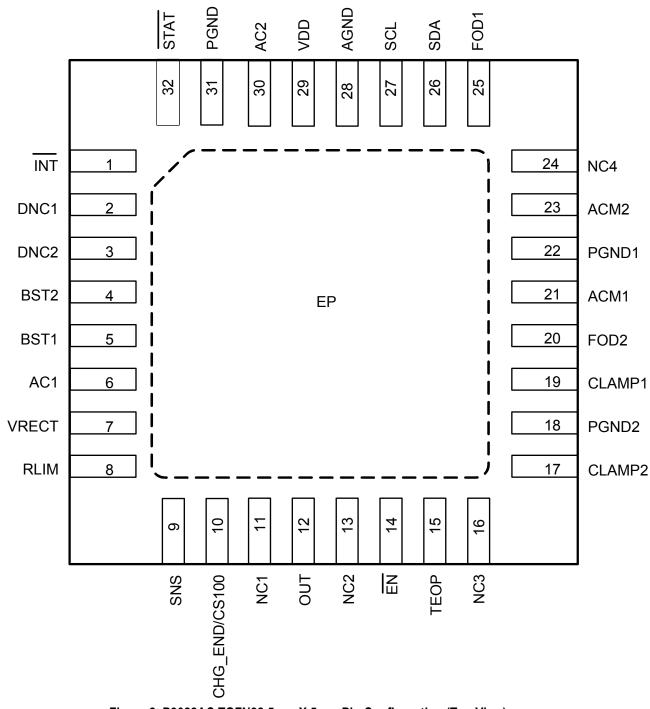

## **PIN CONFIGURATION & DESCRIPTION (CONTINUED)**

Figure 8. P9028AC TQFN32 5mm X 5mm Pin Configuration (Top View).

### Table 6. TQFN Pin Descriptions.

| Pin # | Name          | Туре | Description                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ĪNT           | 0    | Interrupt output. Open drain output pin. A low condition indicates that an OC, OV, or OT event has occurred.                                                                                                                                                                                                                                                            |

| 2     | DNC1          | DNC  | DO NOT connect to this pin, it is internally connected.<br>This pin must be left floating.                                                                                                                                                                                                                                                                              |

| 3     | DNC2          | DNC  | DO NOT connect to this pin, it is internally connected.<br>This pin must be left floating.                                                                                                                                                                                                                                                                              |

| 4     | BST2          | 0    | Bootstrap output for high-side rectifier FET 2.                                                                                                                                                                                                                                                                                                                         |

| 5     | BST1          | 0    | Bootstrap output for high-side rectifier FET 1.                                                                                                                                                                                                                                                                                                                         |

| 6     | AC1           | I    | AC1 input to the Internal full-wave rectifier.                                                                                                                                                                                                                                                                                                                          |

| 7     | VRECT         | 0    | Output of the full-wave rectifier.                                                                                                                                                                                                                                                                                                                                      |

| 8     | RLIM          | I    | Current-limit resistor. A resistor connected between this pin and ground sets the current limit of the 5V LDO.                                                                                                                                                                                                                                                          |

| 9     | SNS           | I    | LDO output sense pin. Connect to the OUT pin (TQFN only).                                                                                                                                                                                                                                                                                                               |

| 10    | CHG_END/CS100 | I    | Active-high input pin. Default setting is a Charge-End active-high input from an external battery charger to terminate power transfer. Alternatively, a Charge-Status active high input which will send a WPC Charge Status packet with value 100 (100% charge). In PMA mode, an End Of Charge (EOC) command will be sent. This pin has an internal pull down resistor. |

| 11    | NC1           | NC   | Not internally connected. This pin may be connected to others to facilitate routing or to improve thermal performance.                                                                                                                                                                                                                                                  |

| 12    | OUT           | 0    | 5V LDO output. A 1µF ceramic capacitor must be connected between this pin and ground.                                                                                                                                                                                                                                                                                   |

| 13    | NC2           | NC   | Not internally connected. This pin may be connected to others to facilitate routing or to improve thermal performance.                                                                                                                                                                                                                                                  |

| 14    | ĒN            | I    | Active-low enable pin. The chip is suspended and placed in low-current (sleep) mode when pulled high. This pin is pulled low inside the chip.                                                                                                                                                                                                                           |

| 15    | ТЕОР          | Ι    | Active-high over-temperature input pin. If this pin is pulled high, the chip will send<br>a WPC EOP packet with code 0x03 (over-temperature code) or a PMA EOC<br>signal. This pin has an internal pull down resistor.                                                                                                                                                  |

| 16    | NC3           | NC   | Not internally connected. This pin may be connected to others to facilitate routing or to improve thermal performance.                                                                                                                                                                                                                                                  |

| 17    | CLAMP2        | I    | AC clamp input 2.                                                                                                                                                                                                                                                                                                                                                       |

| 18    | PGND2         | -    | Power ground for the AC clamp FETs.                                                                                                                                                                                                                                                                                                                                     |

| 19    | CLAMP1        | I    | AC clamp input 1.                                                                                                                                                                                                                                                                                                                                                       |

| 20    | FOD2          | I    | FOD2 adjustment                                                                                                                                                                                                                                                                                                                                                         |

| 21    | ACM1          | I    | AC Modulation input 1.                                                                                                                                                                                                                                                                                                                                                  |

| 22    | PGND1         | -    | Power ground for the full-wave rectifier.                                                                                                                                                                                                                                                                                                                               |

| 23    | ACM2          | I    | AC Modulation input 2.                                                                                                                                                                                                                                                                                                                                                  |

| 24    | NC4           | NC   | Not internally connected. This pin may be connected to others to facilitate routing or to improve thermal performance.                                                                                                                                                                                                                                                  |

| 25    | FOD1          | I    | Select FOD settings                                                                                                                                                                                                                                                                                                                                                     |

| 26    | SDA           | I/O  | I <sup>2</sup> C data port. If not used, connect to ground.                                                                                                                                                                                                                                                                                                             |

| 27    | SCL           | I    | I <sup>2</sup> C clock port. If not used, connect to ground.                                                                                                                                                                                                                                                                                                            |

| 28    | AGND          | -    | Analog ground connection.                                                                                                                                                                                                                                                                                                                                               |

| 29    | VDD           | 0    | Internal voltage supply. Connect a 1uF to 10uFcapacitor between this pin and ground. Must be left unloaded.                                                                                                                                                                                                                                                             |

### Table 6. TQFN Pin Descriptions (Continued).

| PIN # | NAME           | TYPE | DESCRIPTION                                                               |

|-------|----------------|------|---------------------------------------------------------------------------|

| 30    | AC2            | I    | AC2 input to the Internal full-wave rectifier.                            |

| 31    | PGND           | -    | Power ground for the full-wave rectifier.                                 |

| 32    | STAT           | 0    | Status output. A low condition indicates that power is being transferred. |

| EP    | Exposed Paddle | -    | Exposed pad for thermal                                                   |

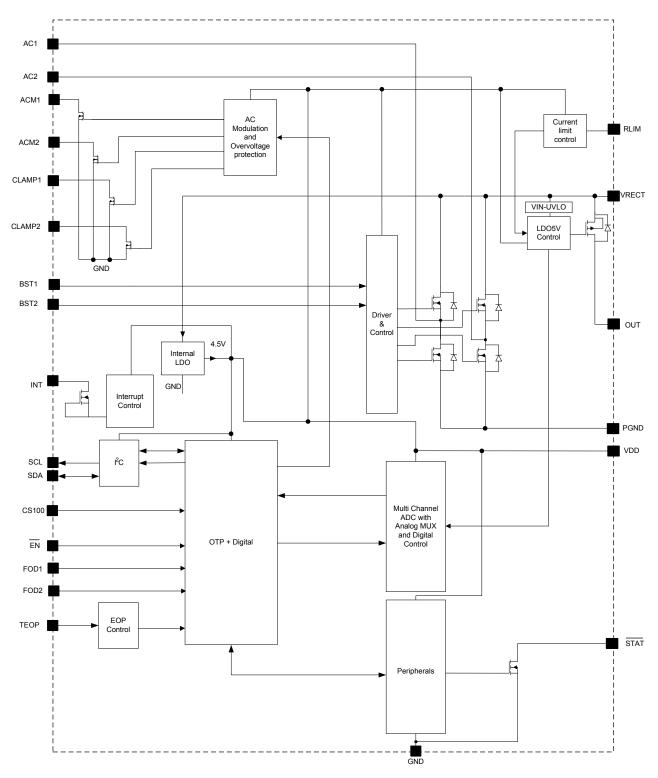

## FUNCTIONAL BLOCK DIAGRAM

## DESCRIPTION OF THE WIRELESS POWER CHARGING SYSTEM

A wireless power charging system has a base station with one or more transmitters that make power available via DC-to-AC inverter(s) and transmit the power over a strongly-coupled inductor pair to a receiver in a mobile device. A WPC<sup>1</sup> transmitter may be a free-positioning or magnetically-guided type. PMA<sup>2</sup> supports only the magnetically-guided configuration. A free-positioning type of transmitter has one coil or an array of coils that gives limited spatial freedom to the end-user, whereas a magnetically-guided type of transmitter helps the end-user align the receiver to the transmitter with a magnetic attraction.

The amount of power transferred to the mobile device is controlled by the receiver. The receiver sends communication packets to the transmitter to increase power, decrease power, or maintain the power level. The bit rate for RX-to-TX communication link is 2-kbps for WPC compliant receivers and variable for PMA compatible receivers. The communication is purely digital and communication 1's and 0's ride on top of the power link that exists between the two coils.

## THEORY OF OPERATION

The P9028AC is a highly-integrated wireless power receiver IC for mobile devices. The device can transfer up to 5W from a wireless transmitter to a load (e.g., a battery charger) in either WPC or PMA (Dual-mode) using near-field magnetic induction. Dual-mode operation is achieved using a single RX coil with fixed inductance for both WPC and PMA AC modulation for maximum efficiency.

## OVERVIEW

The simplified internal block diagram of the P9028AC is shown in Figure 9. An external inductor and capacitor transfers energy from the transmitter's coil through the P9028AC's AC1 and AC2 pins to be full-wave-rectified and stored on a capacitor connected to VRECT. Until the voltage across the capacitor exceeds the threshold of the VIN\_UVLO block, the rectification is performed by the body diodes of the Synchronous Full Bridge Rectifier FETs. After the internal biasing circuit is enabled, the Driver and Control block operates the MOSFET switches in the rectifier for increased efficiency. An internal ADC monitors the voltage at VRECT and the load current, the P9028AC sends instructions to the wireless power transmitter to increase or decrease the amount of power transferred or to terminate power transmission based on these readings. The voltage at the output of the 5V lowdrop-out regulator and the internal temperature are also monitored to ensure proper operation.

### POWER CONTROL

The voltage at VRECT and the current through the rectifier are sampled periodically and digitized by the ADC. The digital equivalents of the voltage and current are supplied to the internal control logic, which decides whether the loading conditions on VRECT indicate that a change in the operating point is required. If the load is heavy enough to bring the voltage at VRECT below its target, the transmitter is instructed to move its frequency lower, closer to resonance. If the voltage at VRECT is higher than its target, the transmitter is instructed to increase its frequency. To maximize efficiency, the voltage at VRECT is programmed to decrease as the LDO's load current increases.

## WPC MODE CHARACTERISTICS

### STARTUP

When a mobile device containing the P9028AC is placed on a WPC "Qi" charging pad, it responds to the transmitter's "ping" signal by rectifying the AC power from the transmitter and storing it on a capacitor connected to VRECT. During the "ping" phase, the rectifier provides about 5V at the VRECT pin. An internal capacitor-less linear voltage regulator provides the supply voltage for the digital section to enable WPC communication. To increase the reliability of the communication, an internal load of about 15mA is connected to VRECT until the external load is large enough to support communication.

Note 1 - Refer to the WPC specification at http://www.wirelesspowerconsortium.com/ for the most current information.

**Note 2** – PMA members can download the most current PMA Receiver Interoperability Specification at <u>http://www.powermatters.org</u>.

The control loop of the P9028AC adjusts the rectifier voltage to 7V by sending error packets to the transmitter before it enables the 5V LDO.

The LDO is enabled when the power transfer mode is initiated and the voltage at VRECT, the output of the full-wave synchronous rectifier, is 7V. The enable pin of the P9028AC can be asserted to shut down the LDO and send an "end power transfer" communication packet to the transmitter.

### POWER TRANSFER

Once the "identification and configuration" phase is completed, the transmitter initiates the power transfer mode. The P9028AC control circuit measures the rectifier voltage and sends error packets to the transmitter to adjust the rectifier voltage to the level required to maximize the efficiency of the linear regulator.

### SYNCHRONOUS RECTIFIER

The efficiency of the full-bridge rectifier in the P9028AC is increased by implementing it as a synchronous rectifier. The rectifier comprises four self-driven switches that work in a full synchronous mode of operation when the load is higher than 300 mA. Below that threshold, the rectifier works in half-synchronous rectification mode. At power-up, when the voltage is below the UVLO threshold, the rectifier works by using the body diodes associated with the NMOS transistors. Charge pumps are used to drive the high-side NMOS switches.

# ADVANCED FOREIGN OBJECT DETECTION (FOD) WPC MODE

When metallic objects are exposed to an alternating magnetic field, eddy currents cause such objects to heat up. Examples of parasitic metal objects as such are coins, keys, paperclips, etc. The amount of heating depends on the amplitude and frequency of the magnetic field coupled, as well as on the characteristics of the object such as its resistivity, size, and shape. In a wireless power transfer system, the heating manifests itself as a power loss, and therefore a reduced power transfer efficiency. Moreover, if no appropriate measures are taken, the heating could lead to unsafe situations if the objects reach high temperatures.

WPC-compliant power transmitters and receivers need to also compensate for the power loss due to parasitic metals—i.e. metals that are neither part of the power transmitter, nor of the power receiver, but which dissipate power from magnetic field coupling during power transfer. The power transmitter uses both an input power and received power method to detect susceptible metallic objects near the interface surface. This method relies on *Analog Ping* and does not involve waking up the power receiver and starting digital communications. Typically zero or more *Analog Pings* precede *Digital Ping*ing, which the power transmitter executes in an attempt to communicate with a possible receiver client device.

The P9028AC employs advanced FOD techniques to detect foreign objects placed on the transmitter base station. The FOD algorithm includes values that are programmable through either the I<sup>2</sup>C interface or OTP (One Time Programmable) bits. Programmability is necessary so that the FOD settings can be optimized to match the power transfer characteristics of each particular WPC system to include the power losses of the Tx and Rx coils, battery, shielding and case materials under no load to full load conditions. The values are based on the comparison of the received power against a reference power curve so that any foreign object can be sensed when the received power is different than the expected system power. The I<sup>2</sup>C interface FOD option has 1 volatile setting that can accommodate the power transfer characteristics of one system. The OTP option has up to 10 non-volatile value settings for up to ten different systems. The 10 programmed OTP settings are externally selected through the FOD1 setting resistor value (see Figure 16 and 17) which selects the settings chosen for the particular system. A further enhancement is selected by the FOD2 offset resistor which adds a -300 to +300mW power offset to the values selected by the FOD1 resistor.

There are three available options to set the advanced FOD programming and testing:

Option 1: IDT completes all the FOD system tests and programming.

Option 2: IDT completes the programming only with information provided by customer.

Option 3: The customer performs the FOD system tests and programming.

Please contact IDT for application note #814A which contains a detailed description of the advanced FOD programming and options available.

### **OVERVOLTAGE PROTECTION**

In the event that the input voltage increases above 15V, the control loop disables the LDO, sends error packets to the transmitter in an attempt to bring the rectifier voltage below 7V, and clamps the input pins. If the voltage at VRECT exceeds  $V_{OVP}$ , two internal FETs turn on to clamp the VRECT voltage. This is accomplished through loading the receiver resonant tank with extra capacitance shorted to ground through the above mentioned internal FETs. This changes the parallel resonance of the tank circuit which causes the Tx to Rx gain to decrease dramatically. The clamp is released when the VRECT voltage falls below the  $V_{OVP}$  hysteresis level. VRECT must not be directly loaded.

# OVERCURRENT PROTECTION AND THERMAL SHUTDOWN

The P9028AC employs over-current and thermal protection by sending an End of Power packet to the transmitter when the output current reaches the current limit level or the die temperature exceeds the thermal shutdown level. The LDO output is also disabled during these conditions.

The current limit level is programmable with an external resistor:

$$I_{LIM} = \frac{45000}{R_{LIM}}$$

For any value of  $R_{LIM}$  below  $25k\Omega$ , the output current is limited to 2A. RLIM is not recommended to be set higher than 60k ohms

### **RECTIFIER and VRECT LEVEL**

Once VRECT powers up to greater than 7V for WPC mode and 5.6V for PMA mode, the full-bridge rectifier switches to half synchronous or full synchronous mode (depending on the loading conditions) to efficiently transfer energy from the transmitter to VRECT. The control loop of the IDTP9028AC maintains the rectifier voltage between 5V and 7V, depending upon the output current ( $I_{OUT}$ ). The R<sub>LIM</sub> resistor sets both the current limit ( $I_{LIM}$ ) and the VRECT steps based on  $I_{SET}$  which is a reference current used to partition the  $I_{OUT}$  load range into 4 regions, each with a VRECT target for efficiency and transient optimization.  $I_{SET}$  is equal to:

$$I_{SET} = \frac{38000}{R_{LIM}}$$

#### Table 7. VRECT target range.

| VRECT | Ιουτ                                            |

|-------|-------------------------------------------------|

| 7V    | I <sub>OUT</sub> < 10% of I <sub>SET</sub>      |

| 6.3V  | 10% of $I_{SET}$ < $I_{OUT}$ < 20% of $I_{SET}$ |

| 5.5V  | 20% of $I_{SET}$ < $I_{OUT}$ < 40% of $I_{SET}$ |

| 5.45V | 40% of I <sub>SET</sub> < I <sub>OUT</sub>      |

### STATUS OUTPUT

The  $\overline{\text{STAT}}$  output goes low when the power transfer is established.

### INTERRUPT OUTPUT

The INT output goes low to indicate that an Over-Current, Over-Voltage or Over-Temperature event has occured. See Electrical Specifications for threshold levels.

### ENABLE INPUT

If the particular application requires the P9028AC to be disabled, this can be accomplished with the  $\overline{\text{EN}}$  pin. When the  $\overline{\text{EN}}$  pin is pulled high, the device is suspended and placed in low current (sleep) mode. If pulled low or floating, the device is active.

### **TEOP INPUT**

In addition to the  $\overline{\text{EN}}$  input, the P9028AC can also be disabled with the TEOP pin. When the TEOP pin is pulled high, the chip will send an EOP packet with code 0x03 (over-temperature code).

### CHG\_END/CS100 INPUT

This pin has two functions. The Charge-End default function will terminate power transfer when pulled high from an external battery charger. If the pin is set in Charge-Status mode, the device will send a WPC Charge Status packet with value 100 (100% charge) indicating a fully charged battery. In PMA mode, an End Of Charge (EOC) command will be sent.

### LDO

The P9028AC has one LDO, the 5 VOUT LDO that is powered by VRECT. The LDO in turn supplies power to the system and/or charging circuitry.

### MODULATION/COMMUNICATION

Receiver-to-transmitter communication is accomplished by modulating the load seen by the receiver's inductor. To the transmitter, this appears as an impedance change, which results in measurable variations of the transmitter's output waveform. Modulation is done with AC Modulation,

P9028AC

using internal switches to connect external capacitors from AC1 and AC2 to ground The communication protocol is covered in the next section.

### WPC MODE COMMUNICATION

The P9028AC communicates with the base via communication packets. Each communication packet has the following structure:

| Preamble | Header | Message | Checksum |

|----------|--------|---------|----------|

|----------|--------|---------|----------|

Figure 10. Communication packet structure.

According to the WPC specification, the power receiver communicates with the power transmitter using backscatter modulation. The load seen by the power transmitter's inductor is modulated on the receiver side to send packets. The power transmitter detects this as a modulation of coil current/voltage to receive packets.

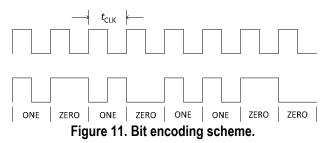

### **BIT ENCODING SCHEME**

As required by the WPC, the P9028AC uses a differential bi-phase encoding scheme to modulate data bits onto the Power Signal. A clock frequency of 2kHz is used for this purpose. A logic ONE bit is encoded using two narrow transitions, whereas a logic ZERO bit is encoded using two wider transitions as shown below:

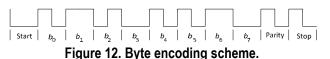

Each byte in the communication packet comprises 11bits in an asynchronous serial format, as shown below:

Each byte has a start bit, 8 data bits, a parity bit, and a single stop bit.

## SYSTEM FEEDBACK CONTROL

The P9028AC is fully compatible with WPC specification Rev. 1.1 and has all necessary circuitry to communicate with the base station via WPC-compliant communication packets.

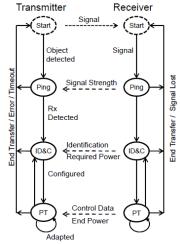

The overall WPC-compliant system behavior between the transmitter and receiver follows the state machine below:

Figure 13. WPC System Feedback control.

The P9028AC goes through four phases: Selection, Ping, Identification & Configuration, and Power Transfer.

### SELECTION

In this phase, the P9028AC senses the incoming power from the base station and proceeds to the *PING* state. It monitors the rectified voltage, and when the voltage is above the  $V_{\text{RECT,UVLO}}$  threshold, the P9028AC wakes up its digital electronics and prepares to communicate with the base station. If the P9028AC does not proceed to *PING*, then it does not transmit any communication packets.

### PING

In this phase, the P9028AC transmits a Signal Strength Packet as the first communication packet to instruct the base to keep the power signal ON. After sending the Signal Strength Packet, the P9028AC proceeds to the *Identification and Configuration* phase. If, instead, the P9028AC sends End of Power Packets, then it remains in the *PING* phase.

In this phase, the P9028AC sends the following packets:

- Signal Strength Packet

- End of Power Packet

### IDENTIFICATION AND CONFIGURATION (ID & Config)

In this phase, the P9028AC may send the following packets:

- Identification Packet

- Configuration Packet

After sending the Configuration Packet, the P9028AC proceeds to the *power transfer* phase.

### **POWER TRANSFER**

In this phase, the P9028AC controls the power transfer from the Power Transmitter by means of the following Control Data Packets:

- Control Error Packets

- Rectified Power Packet

- End Power Transfer Packet

### MODULATION

The P9028AC is compatible with WPC V1.1 and PMA v and v3 coils. Each receiver coil type has a unique inductance value. As such, a unique resonant capacitor ( $C_S$ ) is used for a given type of receiver coil. The modulation capacitors are shown in Figure 14.

Dual-mode operates with a single LC tank RX coil and AC modulation for maximum efficiency. ( $C_{MODE1}$ ,  $C_{MOD2}$ )

### Figure 14. Modulation components.

Consult the factory for assistance with configuring a system with a specific coil type.

## PMA MODE CHARACTERISTICS

### STARTUP AND COMMUNICATION

Before the receiver is placed on the transmitter pad, the transmitter is in the Standby state. In Standby, the transmitter is waiting to detect any new, detectable object. Once the receiver is placed on the PMA transmitter pad, there are two states that the system must pass through before power transfer begins. These states are: Digital Ping, and Identification and the final two states are: Power Transfer, and End-of-Charge (EOC).

In Standby, the transmitter is waiting to detect an object on its pad. Once detected the transmitter tries to initiate communication, emitting a predetermined signal called a "Digital Ping". If the receiver is aligned well enough to energize and if it responds in the correct manner, it is recognized by the transmitter as a PMA capable device. At this point, if the Identification state is not supported, the transmitter starts transmitting power to the receiver. If the Identification state is supported, the receiver sends its unique RXID to the transmitter, which identifies it as a fully compliant PMA device. After that transaction, the system enters the Power Transfer state and power transfer from the transmitter to receiver begins.

The 5V LDO is enabled when the power transfer mode is initiated and the voltage at VRECT, the output of the full-wave synchronous rectifier, is more than 5.6V.

### PMA EOC

A receiver that transmits a PMA EOC signal shall remain in the power transfer phase but shall disable its output and shall continue to transmit PMA EOC signals until the transmitter removes the power. The P9028AC operation is summarized in table 8 from the PMA specification:

Figure 15. Simplified PMA-State Machine.

### Table 8. Receiver Power Transfer Operation.

| DESCRIPTION                                                                                    | SYMBOL                  | VALUE                   | UNITS |

|------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|

| Maximum period in power transfer phase $I_{OUT}$ < $I_{CC}$ before transmitting PMA EOC signal | T <sub>EOC</sub>        | 40                      | min   |

| Charge complete threshold current                                                              | lcc                     | 0.05 x I <sub>LIM</sub> | mA    |

| No load threshold current                                                                      | NoLoad                  | 25                      | mA    |

| Time to enter No load EOC                                                                      | I <sub>NoLoad_EOC</sub> | 40                      | sec   |

| Maximum receiver temperature                                                                   | $T_{Rx\_max}$           | 60                      | °C    |

## **APPLICATIONS INFORMATION**

## EXTERNAL COMPONENTS

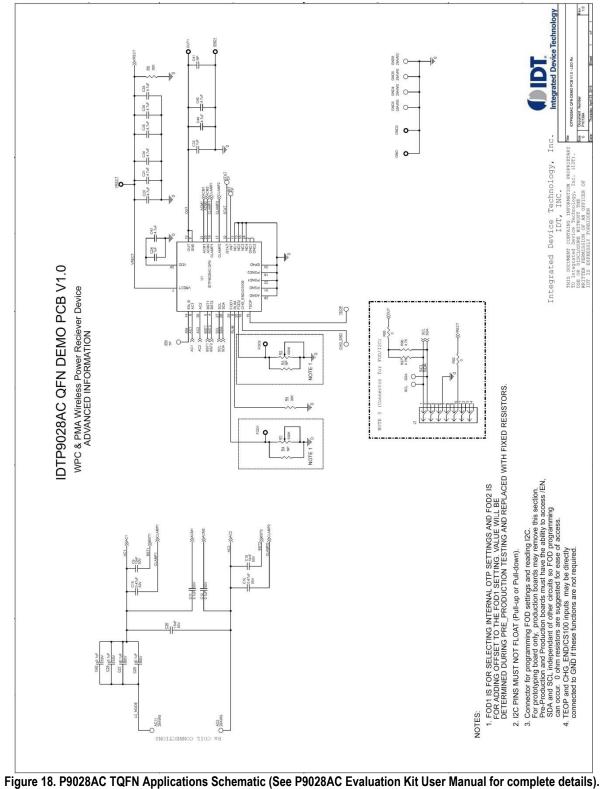

The P9028AC requires a minimum number of external components for proper operation, as indicated in Figure 16, 17 and 18 as well as Table 9, 10 and 11.

## LDO

### Input Capacitor (VRECT Capacitors)

The LDO input capacitors (VRECT capacitors) should be located as close as possible to the VRECT pins, and ground (PGND). Ceramic capacitors are recommended for their lower ESR and small profile. See Figure 17 and Table 10 for values and type of capacitor.

### **VDD** Capacitor

The P9028AC has an internal LDO regulator that must have a capacitor connected from the VDD pin to GND. This capacitor should be as close as possible to the VDD pin with a close GND connection. See Figure 17, 18 and Table 10, 11 for values and type of capacitor.

### **Output Capacitor**

The output capacitor connection to the ground pin (PGND) should be made as short as practical for maximum device performance. Since the LDO has been designed to function with very low ESR capacitors, a ceramic capacitor is recommended for best performance. For better transient response increase the total amount of output capacitance. For 1A load steps, an output capacitance of at least  $10\mu$ F is recommended.

## **PCB LAYOUT CONSIDERATIONS**

- For optimum device performance and lowest output phase noise, the following guidelines should be observed. Please contact IDT Inc. for Gerber files that contain the recommended board layout and application note AN883, "P9028AC Layout Guidelines".

- An optimum layout is one with all components on the same side of the board, minimizing vias through other signal layers. Signal traces not related to the P9028AC should be routed away from the IC as much as possible to avoid blocking thermal dissipation paths from the IC to the PCB. This includes signal traces just underneath the device, or on layers adjacent to the ground plane layer used by the device.

- Layout and PCB design have a significant influence on the power dissipation capabilities of power management ICs because the surface mount packages used with these devices rely heavily on thermally conductive traces or pads to transfer heat away from the package. Appropriate PC layout techniques should be used to remove the heat due to device power dissipation.

- The following general guidelines will be helpful in designing a board layout for lowest thermal resistance:

- 1. PC board traces with large cross-sectional areas remove more heat. For optimum results, use large-area PCB patterns with wide copper traces, placed on the uppermost side of the PCB.

- 2. In cases where maximum heat dissipation is required, use double-sided copper planes connected with multiple vias.

- 3. Thermal vias are needed to provide a thermal path to inner and/or bottom layers of the PCB to remove the heat generated by device power dissipation.

## POWER DISSIPATION AND THERMAL REQUIREMENTS

The P9028AC is offered in a QFN-32 package which has a maximum power dissipation capability of about 1.9W and in a WLCSP package, the maximum power dissipation of which is determined by the number of thermal vias between the package and the printed circuit board. The maximum power dissipation of both packages is defined by the die's specified maximum operating junction temperature, T<sub>.</sub>, of 125°C. The junction temperature rises when the heat generated by the device's power dissipation goes through the package thermal resistance. The QFN package offers a typical thermal resistance, junction to ambient ( $\Theta_{JA}$ ), of 35°C/W when the PCB layout and surrounding devices are optimized as described in the PCB Layout Considerations section. The WLCSP package has a typical  $\Theta_{JA}$  of 70°C/W with 7 thermal vias and 144°C/W with no thermal vias. Clearly, maximizing the thermal vias is highly recommended. The techniques as noted in the PCB layout section must be followed when designing the printed circuit board layout, as well as the placement of the P9028AC IC package in proximity to other heat-

generating devices in a given application design. The ambient temperature around the power IC will also have an effect on the thermal limits of an application. The main factors influencing  $\Theta_{JA}$  (in the order of decreasing influence) are PCB characteristics, Die/package attach thermal pad size (QFN), thermal vias (WLCSP), and internal package construction. Board designers should keep in mind that the package thermal metric  $\Theta_{JA}$  is impacted by the characteristics of the PCB itself upon which the IC is mounted. For example, in a still-air environment, as is often the case, a significant amount of the heat generated (~85%) is absorbed by the PCB. Changing the design or configuration of the PCB changes the overall thermal resistivity and, thus, the board's heatsinking efficiency.

The use of integrated circuits in low-profile and fine-pitch surface-mount packages requires special attention to power dissipation. Many system-dependant issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heatgenerating components, affect the power-dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are listed below:

- 1. Improving the power dissipation capability of the PCB design

- 2. Improving the thermal coupling of the component to the PCB

- 3. Introducing airflow into the system

First, the maximum power dissipation for a given situation should be calculated:

$P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$

In which

P<sub>D(MAX)</sub> = Maximum Power Dissipation

$\theta_{JA}$  = Package Thermal Resistance (°C/W)

T<sub>J(MAX)</sub> = Maximum Device Junction Temperature (°C)

$T_A$  = Ambient Temperature (°C)

The maximum recommended junction temperature  $(T_{J(MAX)})$  for the P9028AC device is 125°C. The thermal resistance of the 32-pin QFN package (NBG32) is nominally  $\theta_{JA}$ =35°C/W. Operation is specified to a maximum steady-state ambient temperature (T<sub>A</sub>) of 85°C. Therefore, the maximum recommended power dissipation is:

$P_{D(Max)} = (125^{\circ}C - 85^{\circ}C) / 35^{\circ}C/W \cong 1.14$  Watt.

The thermal resistance for the WLCSP package (AWG36) is nominally  $\theta_{JA}$ =70°C/W with 7 thermal vias, the maximum recommended power dissipation is:

$P_{D(Max)} = (125^{\circ}C - 85^{\circ}C) / 70^{\circ}C/W \cong 0.57$  Watt

All the above-mentioned thermal resistances are the values found when the ICs are mounted on a standard board of the dimensions and characteristics specified by the JEDEC 51 standard.

### THERMAL OVERLOAD PROTECTION

The P9028AC integrates thermal overload shutdown circuitry to prevent damage resulting from excessive thermal stress that may be encountered under fault conditions. This circuitry will shut down or reset the device if the die temperature exceeds 150°C. To allow the maximum load current on each regulator and the synchronous rectifier, and to prevent thermal overload, it is important to ensure that the heat generated by the P9028AC is dissipated into the PCB.

### End of Charge (EOC)

In the event of thermal shutdown (150°C), EN, CHG\_END or TEOP pins assertion the device turns off the LDO and continually sends End Of Power (EOP) packets in WPC or End Of Charge (EOC) in PMA until the transmitter removes the power and the rectifier voltage on the receiver side drops below the UVLO threshold.

NC pins that are indicated as "Not Internally Connected" should be soldered to the PCB ground plane to improve thermal performance with multiple vias exiting the bottom side of the PCB. This improves heat flow away from the package and minimizes package thermal gradients.

DNC pins that are indicated as "Internally connected" MUST BE LEFT FLOATING.

## **Special Notes**

### TQFN NBG32 Package Assembly

Note 1: Unopened Dry Packaged Parts have a one year shelf life.

Note 2: The HIC indicator card for newly-opened Dry Packaged Parts should be checked. If there is any moisture content, the parts must be baked for a minimum of 8 hours at 125°C within 24 hours of the assembly reflow process.

Product Datasheet

Figure 16. Simplified Applications Schematics.

| Item | Quantity | Reference                                 | Value                            |  |  |

|------|----------|-------------------------------------------|----------------------------------|--|--|

| 1    | 1        | L <sub>RX</sub>                           | 7.5μH (Custom Coil) <sup>1</sup> |  |  |

| 2    | 2        | C <sub>MOD1</sub> , C <sub>MOD2</sub>     | 100nF                            |  |  |

| 3    | 2        | C <sub>CLAMP1</sub> , C <sub>CLAMP2</sub> | 470nF                            |  |  |

| 4    | 2        | C <sub>BST1</sub> , C <sub>BST2</sub>     | 10nF                             |  |  |

| 5    | 2        | С <sub>ОИТ</sub> , С <sub>1</sub>         | 10µF                             |  |  |

| 6    | 1        | C <sub>RECT</sub>                         | 30µF                             |  |  |

| 7    | 1        | C <sub>D</sub>                            | 1800pf                           |  |  |

| 8    | 2        | Cs                                        | 400nF                            |  |  |

| 9    | 1        | LED                                       | RED_LED                          |  |  |

| 14   | 2        | R <sub>FOD1</sub> , R <sub>FOD2</sub>     | TBD (Sytem Dependent)            |  |  |

| 15   | 1        | R <sub>UM</sub>                           | 30K                              |  |  |

| 18   | 1        | IDTP9028AC                                | IDTP9028AC                       |  |  |

|      |          |                                           |                                  |  |  |

| Table 9. | Bill of Mate | erials. |

|----------|--------------|---------|

|----------|--------------|---------|

Note 1 – Contact the factory for suitable coil recommendations.

**Product Datasheet**

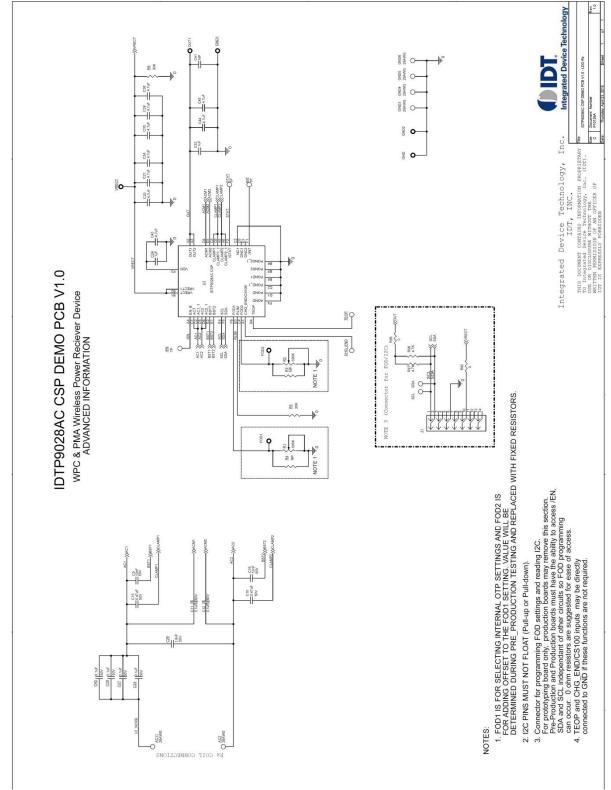

## DETAILED SYSTEM DIAGRAM WLCSP

# **COMPONENTS SELECTION WLCSP**

Table 10. P9028AC WLCSP Evaluation Kit Bill of Materials.

| Item       | Quantity | Reference                | Part Number          | Value          | PCB Footprint       |

|------------|----------|--------------------------|----------------------|----------------|---------------------|

| 1          | 1        | /EN                      |                      | ТР             | tp_25mil            |

| 2          | 2        | C9,C16                   | C1005X7R1H103K050BB  | 10nF           | 402                 |

| 3          | 2        | C10,C15                  | UMK105ABJ474KV-F     | 0.47uF         | 402                 |

| 4          | 6        | C11,C12,C27,C28,C29,C42  | GRM155R61H104KE19D   | 0.1uF          | 402                 |

| 5          | 9        | C20,C21,C34,C35,C38,C39, | GRM155R61E475M       | 4.7uF          | 402                 |

|            |          | C43,C44,C45              |                      |                |                     |

| 6          | 2        | C24,C32                  | C1005X5R1E105M050BC  | 1uF            | 402                 |

| 7          | 1        | C26                      | GRM155R71H182KA01D   | 1.8nF          | 402                 |

| 8          | 3        | OUT1,GND1,VRECT          | 5015                 | 1P             | test_pt_sm_135x70   |

| 9          | 2        | R3,R4                    | TBD                  | NP             | 402                 |

| 10         | 2        | R5,R6                    | ERJ-1GEF3002C        | 30К            | 201                 |

| 11         | 2        | R96,R97                  | ERJ-2GEJ472X         | 4.7K           | 402                 |

| 12         | 1        | U1                       | P9028AC              | IDTP9028AC CSP | CSP36P500X500       |

| Optional ( | Componen | ts                       |                      |                |                     |

| 13         | 4        | CS100,TEOP,STAT,INT      |                      | ТР             | tp_25mil            |

| 14         | 8        | AC2,GND3,GND4,GND5,GND6, |                      | 28AWG          | 28AWG               |

|            |          | AC11,SDA,SCL             |                      |                |                     |

| 15         | 1        | C41                      | GRM155R61E475M       | NP             | 402                 |

| 16         | 4        | GND,FOD1,GND2,FOD2,      | 5015                 | 1P             | test_pt_sm_135x70   |

| 17         | 1        | J1                       | SBH11-PBPC-D07-ST-BK | 14P            | P_014_2R            |

| 18         | 2        | R1,R2                    | 3223W-1-504E         | 500K           | res_adj_smd_3p9x3p9 |

| 19         | 1        | R82                      | ERJ-2GEOROOX         | 0              | 402                 |

| 20         | 1        | R85                      | RC0402JR-070RL       | 0              | 402                 |

Product Datasheet

# **COMPONENTS SELECTION TQFN**

Table 11. P9028AC TQFN Evaluation Kit Bill of Materials.

| Item       | Quantity | Reference                | Part Number          | Value          | PCB Footprint       |

|------------|----------|--------------------------|----------------------|----------------|---------------------|

| 1          | 3        | /en,sda,scl              |                      | ТР             | tp_25mil            |

| 2          | 2        | C9,C16                   | C1005X7R1H103K050BB  | 10nF           | 402                 |

| 3          | 2        | C10,C15                  | UMK105ABJ474KV-F     | 0.47uF         | 402                 |

| 4          | 6        | C11,C12,C27,C28,C29,C42  | GRM155R61H104KE19D   | 0.1uF          | 402                 |

| 5          | 9        | C20,C21,C34,C35,C38,C39, | GRM155R61E475M       | 4.7uF          | 402                 |

|            |          | C43,C44,C45              |                      |                |                     |

| 6          | 2        | C24,C32                  | C1005X5R1E105M050BC  | 1uF            | 402                 |

| 7          | 1        | C26                      | GRM155R71H182KA01D   | 1.8nF          | 402                 |

| 8          | 3        | OUT1,GND1,VRECT          | 5015                 | 1P             | test_pt_sm_135x70   |

| 9          | 2        | R3,R4                    | TBD                  | NP             | 402                 |

| 10         | 2        | R5,R6                    | ERJ-1GEF3002C        | 30K            | 201                 |

| 11         | 2        | R96,R97                  | ERJ-2GEJ472X         | 4.7K           | 402                 |

| 12         | 1        | U1                       | P9028AC              | IDTP9028AC QFN | QFN_32LD_5X5_0p5mm  |

| Optional 0 | Componen | ts                       |                      |                |                     |

| 13         | 4        | CS100,TEOP,STAT,INT      |                      | ТР             | tp_25mil            |

| 14         | 6        | AC2,GND3,GND4,GND5,GND6, |                      | 28AWG          | 28AWG               |

|            |          | AC11                     |                      |                |                     |

| 15         | 1        | C41                      | GRM155R61E475M       | NP             | 402                 |

| 16         | 4        | GND,FOD1,GND2,FOD2,      | 5015                 | 1P             | test_pt_sm_135x70   |

| 17         | 1        | J1                       | SBH11-PBPC-D07-ST-BK | 14P            | P_014_2R            |

| 18         | 2        | R1,R2                    | 3223W-1-504E         | 500K           | res_adj_smd_3p9x3p9 |

| 19         | 1        | R82                      | ERJ-2GEOROOX         | 0              | 402                 |

| 20         | 1        | R85                      | RC0402JR-070RL       | 0              | 402                 |

# I<sup>2</sup>C REGISTER MAP

The P9028AC has a one-time programmable I<sup>2</sup>C address that is set to default 0X25h.

### Table 12. READ Registers - VRECT voltage: VRECT=5 X ADC1<12:1> = [ADC1<12:1>] X 5 X [1.8V/2<sup>12</sup>].

| Byte<br>Address | Byte<br>Name | Bit Field | Field Name | Туре | Default<br>Value | Description                                            |

|-----------------|--------------|-----------|------------|------|------------------|--------------------------------------------------------|

| 0x40            | REG0         | 7         | ADC1<12>   | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 6         | ADC1<11>   | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 5         | ADC1<10>   | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 4         | ADC1<9>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 3         | ADC1<8>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 2         | ADC1<7>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 1         | ADC1<6>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x40            | REG0         | 0         | ADC1<5>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x41            | REG1         | 7         | ADC1<4>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x41            | REG1         | 6         | ADC1<3>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x41            | REG1         | 5         | ADC1<2>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x41            | REG1         | 4         | ADC1<1>    | R    |                  | VRECT ADC code (average of 8 consecutive measurements) |

| 0x41            | REG1         | 3         | RESERVED.  | R    |                  | RESERVED.                                              |

| 0x41            | REG1         | 2         | RESERVED.  | R    |                  | RESERVED.                                              |

| 0x41            | REG1         | 1         | RESERVED.  | R    |                  | RESERVED.                                              |

| 0x41            | REG1         | 0         | RESERVED.  | R    |                  | RESERVED.                                              |

# I<sup>2</sup>C REGISTER MAP (CONTINUED)

| Byte<br>Address | Byte<br>Name | Bit Field | Field Name | Туре | Default<br>Value | Description                                          |

|-----------------|--------------|-----------|------------|------|------------------|------------------------------------------------------|

| 0x42            | REG2         | 7         | ADC2<12>   | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 6         | ADC2<11>   | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 5         | ADC2<10>   | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 4         | ADC2<9>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 3         | ADC2<8>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 2         | ADC2<7>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 1         | ADC2<6>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0x42            | REG2         | 0         | ADC2<5>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0X43            | REG3         | 7         | ADC2<4>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0X43            | REG3         | 6         | ADC2<3>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0X43            | REG3         | 5         | ADC2<2>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0X43            | REG3         | 4         | ADC2<1>    | R    |                  | lout ADC code (average of 8 consecutive measurements |

| 0X43            | REG3         | 3         | RESERVED.  | R    |                  | RESERVED.                                            |

| 0X43            | REG3         | 2         | RESERVED.  | R    |                  | RESERVED.                                            |