**ON Semiconductor**

Is Now

# Onsemí

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# **Ultra Low-Noise Low Dropout Voltage Regulator** with 1.0 V ON/OFF Control

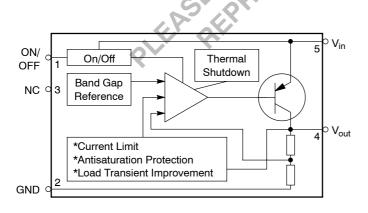

The NCP4561 is a Low DropOut (LDO) regulator featuring excellent noise performances. Thanks to its innovative concept, the circuit reaches an incredible 40 µVRMS noise level without an external bypass capacitor. Housed in a small SOT-23 5 leads-like package, it represents the ideal designer's choice when space and noise are at premium.

The absence of external bandgap capacitor unleashes the response time to a wake-up signal and makes it stay within 40 µs (in repetitive mode), pushing the NCP4561 as a natural candidate in portable applications.

The NCP4561 also hosts a novel architecture which prevents excessive undershoots when the regulator is the seat of fast transient bursts, as in any bursting systems.

Finally, with a static line regulation better than -75 dB, it naturally shields the downstream electronics against choppy lines.

### Features

- Ultra Low-Noise: 150 nV/√Hz @ 100 Hz, 40 μVRMS 100 Hz -100 kHz Typical, Iout = 60 mA,  $C_0 = 1.0 \mu F$

- Fast Response Time from OFF to ON: 40 µs Typical at a 200 Hz **Repetition Rate**

- Ready for 1.0 V Platforms: ON with a 900 mV High Level

- JI-SENTAINE OF • Nominal Output Current of 80 mA with a 100 mA Peak Capability

- Typical Dropout of 90 mV @ 30 mA, 160 mV @ 80 mA

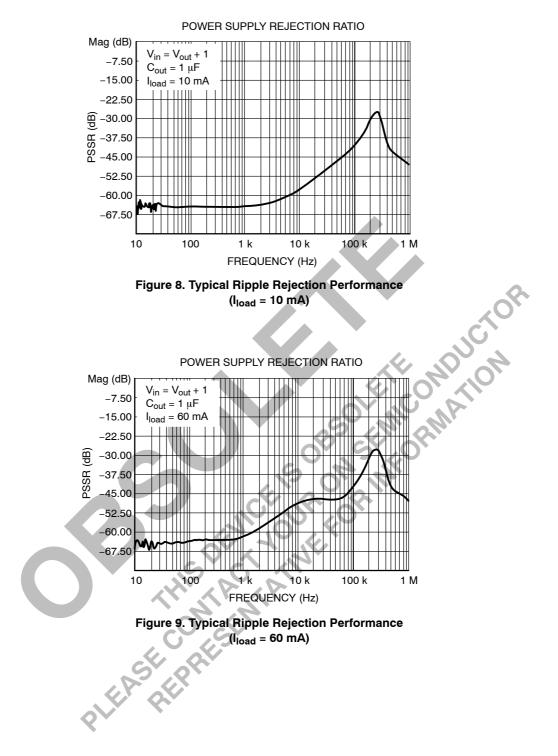

- Ripple Rejection: 70 dB @ 1.0 kHz

- 1.5% Output Precision @ 25°C

- Noise Sensitive Circuits: VCOs RF Stages, etc.

Bursting Systems (TDMA Phones)

All Battery Or

- All Battery Operated Devices

### **ON Semiconductor®**

http://onsemi.com

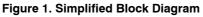

P28 = Device Code

= Year

= Work Week

### **ORDERING INFORMATION**

| Device        | Voltage<br>Output* | Shipping         |

|---------------|--------------------|------------------|

| NCP4561SN28T1 | 2.8 V              | 3000/Tape & Reel |

\* Contact your ON Semiconductor sales representative for other output voltage values.

### **PIN FUNCTION DESCRIPTIONS**

| Pin # | Pin Name         | Function                       | Description                                                                                     |

|-------|------------------|--------------------------------|-------------------------------------------------------------------------------------------------|

| 1     | ON/OFF           | Shuts or<br>wakes–up the IC    | A 900 mV level on this pin is sufficient to start the IC. A 150 mV shuts it down.               |

| 2     | GND              | The IC's ground                |                                                                                                 |

| 3     | NC               | None                           | It makes no arm to connect the pin to a known potential, like in a pin-to-pin replacement case. |

| 4     | V <sub>out</sub> | Delivers the<br>output voltage | This pin requires a 1.0 $\mu F$ output capacitor to be stable.                                  |

| 5     | V <sub>in</sub>  | Powers the IC                  | A positive voltage up to 12 V can be applied upon this pin.                                     |

### MAXIMUM RATINGS

| MAXIMUM RATINGS                                                                                                           |          |                                     |          |                              |           |

|---------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------|----------|------------------------------|-----------|

|                                                                                                                           |          |                                     | Va       | lue                          |           |

| Rating                                                                                                                    | Pin #    | Symbol                              | Min      | Max                          | Unit      |

| Power Supply Voltage                                                                                                      | 5        | V <sub>in</sub>                     | -        | 12                           | V         |

| ESD Capability, HBM Model                                                                                                 | All Pins |                                     | -        | 1.0                          | kV        |

| ESD Capability, Machine Model                                                                                             | All Pins |                                     | -        | 200                          | V         |

| Maximum Power Dissipation<br>NW Suffix, Plastic Package<br>Thermal Resistance Junction-to-Air                             |          | P <sub>D</sub><br>R <sub>θJ-A</sub> | ETE-OND  | Internally<br>Limited<br>210 | W<br>°C/W |

| Operating Ambient Temperature<br>Maximum Junction Temperature (Note 1)<br>Maximum Operating Junction Temperature (Note 2) |          | T <sub>A</sub><br>TJmax<br>TJ       | ENIC-RNP | -40 to +85<br>150<br>125     | °C        |

| Storage Temperature Range                                                                                                 |          | T <sub>stg</sub>                    | 20       | -60 to +150                  | °C        |

### **ELECTRICAL CHARACTERISTICS**

(For Typical Values  $T_A = 25^{\circ}$ C, for Min/Max values  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, Max  $T_J = 125^{\circ}$ C unless otherwise noted)

| Characteri                                                                                                                     | stics                               | Pin # | Symbol              | Min      | Тур | Max             | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|---------------------|----------|-----|-----------------|------|

| ogic Control Specifications                                                                                                    |                                     | 1     |                     |          |     |                 |      |

| Input Voltage Range                                                                                                            |                                     | 1     | V <sub>ON/OFF</sub> | 0        | -   | V <sub>in</sub> | V    |

| ON/OFF Input Resistance                                                                                                        | $-\chi_{c}\chi_{c}\chi_{c}\chi_{c}$ | 1     | R <sub>ON/OFF</sub> | -        | 250 | -               | kΩ   |

| ON/OFF Control Voltages (Note 3)<br>Logic Zero, OFF State, $I_0 = 50 \text{ mA}$<br>Logic One, ON State, $I_0 = 50 \text{ mA}$ | CONSER                              | 1     | V <sub>ON/OFF</sub> | _<br>900 |     | 150<br>-        | mV   |

| Currents Parameters                                                                                                            | CN AN                               | •     |                     |          | •   |                 | •    |

### **Currents Parameters**

| Current Consumption in OFF State<br>OFF Mode Current: $V_{in} = V_{out} + 1.0 V$ , $I_O = 0$ , $V_{OFF} = 150 mV$          | IQ <sub>OFF</sub> | -   | 0.1 | 2.0 | μΑ |

|----------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|----|

| Current Consumption in ON State ON Mode Current: $V_{in} = V_{out} + 1.0 \text{ V}$ , $I_O = 0$ , $V_{ON} = 3.5 \text{ V}$ | IQ <sub>ON</sub>  | -   | 180 | -   | μA |

| Current Consumption in ON State, ON Mode<br>Saturation Current: V <sub>in</sub> = V <sub>out</sub> - 0.5 V, No Output Load | IQ <sub>SAT</sub> | -   | 800 | -   | μA |

| Current Limit V <sub>in</sub> = Vout <sub>nom</sub> + 1.0 V,<br>Output is brought to Vout <sub>nom</sub> – 0.3 V           | I <sub>MAX</sub>  | 100 | 180 | _   | mA |

Internally Limited by Shutdown.

Specifications are guaranteed below this value.

Voltage Slope should be Greater than 2.0 mV/μs.

### ELECTRICAL CHARACTERISTICS (continued)

(For Typical Values  $T_A = 25^{\circ}$ C, for Min/Max values  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, Max  $T_J = 125^{\circ}$ C unless otherwise noted)

| Characteristics                                                                                                         | Pin #       | Symbol                                                                                                      | Min   | Тур              | Max               | Unit       |

|-------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------|-------|------------------|-------------------|------------|

| Dutput Voltages                                                                                                         |             |                                                                                                             |       |                  |                   |            |

| $V_{out}$ + 1.0 V < $V_{in}$ < 6.0 V, $T_A$ = 25°C, 1.0 mA < $I_{out}$ < 80 mA                                          | 4           | V <sub>out</sub>                                                                                            | 2.758 | 2.8              | 2.842             | V          |

| $V_{out}$ + 1.0 V < $V_{in}$ < 6.0 V, $T_A$ = -40°C to +85°C, 1.0 mA < $I_{out}$ < 80 mA                                | 4           | V <sub>out</sub>                                                                                            | 2.716 | 2.8              | 2.884             | V          |

| ine and Load Regulation, Dropout Voltages                                                                               |             |                                                                                                             |       |                  |                   |            |

| Line Regulation<br>$V_{out}$ + 1.0 V < $V_{in}$ < 12 V, $I_{out}$ = 80 mA                                               | 4/5         | Reg <sub>line</sub>                                                                                         | -     | -                | 20                | mV         |

| Load Regulation $V_{in} = V_{out} + 1.0 \text{ V}, C_{out} = 1.0 \mu\text{F}, I_{out} = 1.0 \text{ to } 80 \text{ mA}$  | 4           | Reg <sub>load</sub>                                                                                         | -     | -                | 40                | mV         |

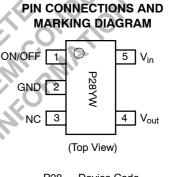

| Dropout Voltage (Note 4)<br>I <sub>out</sub> = 30 mA<br>I <sub>out</sub> = 60 mA<br>I <sub>out</sub> = 80 mA            | 4<br>4<br>4 | V <sub>in</sub> -V <sub>out</sub><br>V <sub>in</sub> -V <sub>out</sub><br>V <sub>in</sub> -V <sub>out</sub> | -     | 90<br>140<br>160 | 150<br>200<br>250 | mV         |

| Dynamic Parameters                                                                                                      |             |                                                                                                             |       |                  | O.                |            |

| Ripple Rejection<br>V <sub>in</sub> = V <sub>out</sub> + 1.0 V + 1.0 kHz 100 mVpp Sinusoidal Signal                     | 4/5         | Ripple                                                                                                      | -     | -70              | -                 | dB         |

| Output Noise Density @ 1.0 kHz                                                                                          | 4           |                                                                                                             |       | 150              |                   | nV/<br>√Hz |

| RMS Output Noise Voltage $C_{out}$ = 1.0 $\mu$ F, I <sub>out</sub> = 50 mA, F = 100 Hz to 1.0 MHz                       | 4           | Noise                                                                                                       |       | 35               | -                 | μV         |

| Output Rise Time $C_{out}$ = 1.0 $\mu$ F, $I_{out}$ = 50 mA, 10% of Rising ON Signal to 90% of Nominal V <sub>out</sub> | 4           | t <sub>rise</sub>                                                                                           |       | 40               | -                 | μs         |

| Thermal Shutdown                                                                                                        | S           | $\sim$ $\sim$                                                                                               | 2     |                  |                   |            |

| Thermal Shutdown                                                                                                        |             |                                                                                                             | -     | -                | 125               | °C         |

| Thermal Shutdown Thermal Shutdown . V <sub>out</sub> is brought to V <sub>out</sub> – 100 mV.                           |             |                                                                                                             |       |                  |                   |            |

### DEFINITIONS

### Load Regulation

The change in output voltage for a change in output current at a constant chip temperature.

### **Dropout Voltage**

The input/output differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output drops 100 mV below its nominal value (which is measured at 1.0 V differential value). The dropout level is affected by the chip temperature, load current and minimum input supply requirements.

### **Output Noise Voltage**

This is the integrated value of the output noise over a specified frequency range. Input voltage and output current are kept constant during the measurement. Results are expressed in µVRMS.

### **Maximum Power Dissipation**

The maximum total dissipation for which the regulator will operate within its specs.

### **Quiescent Current**

ered .patio its ma .conting on the .aculate the maxin maximum available to .red The quiescent current is the current which flows through the ground when the LDO operates without a load on its output: internal IC operation, bias, etc. When the LDO becomes loaded, this term is called the Ground current. It is actually the difference between the input current (measured through the LDO input pin) and the output current.

### Line Regulation

The change in output voltage for a change in input voltage. The measurement is made under conditions of low dissipation or by using pulse technique such that the average chip temperature is not significantly affected. One usually distinguishes static line regulation or DC line regulation (a DC step in the input voltage generates a corresponding step in the output voltage) from ripple rejection or audio *susceptibility* where the input is combined with a frequency generator to sweep from a few hertz up to a defined boundary while the output amplitude is monitored.

### **Thermal Protection**

Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated at typically 125°C, the regulator turns off. This feature is provided to prevent catastrophic failures from accidental overheating.

### Maximum Package Power Dissipation

The maximum power package power dissipation is the power dissipation level at which the junction temperature reaches its maximum operating value, i.e. 125°C. Depending on the ambient temperature, it is possible to calculate the maximum power dissipation and thus the maximum available output current.

### **TYPICAL CHARACTERISTICS**

### **APPLICATION HINTS**

or

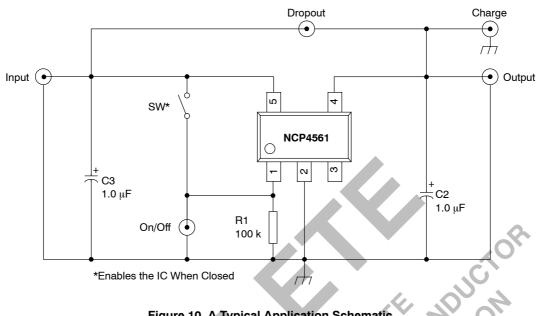

### Input Decoupling

As with any regulator, it is necessary to reduce the dynamic impedance of the supply rail that feeds the component. A 1.0 µF capacitor either ceramic or tantalum is recommended and should be connected close to the NCP4561 package. Higher values will correspondingly improve the overall line transient response.

### **Output Decoupling**

Thanks to a novel concept, the NCP4561 is a stable component and does not require any specific Equivalent Series Resistance (ESR) neither a minimum output current. Capacitors exhibiting ESRs ranging from a few m $\Omega$  up to 3.0  $\Omega$  can thus safely be used. The minimum decoupling value is 1.0 µF and can be augmented to fulfill stringent load transient requirements. The regulator accepts ceramic chip capacitors as well as tantalum devices.

### **Noise Decoupling**

Unlike other LDOs, the NCP4561 is a true low-noise regulator. Without the need of an external bypass capacitor, it typically reaches the incredible level of 40 µVRMS overall noise between 100 Hz and 100 kHz. To give maximum insight on noise specifications, ON Semiconductor includes a 80 mA stracted from, a NCP4561SN, a 25°C, the max spectral density graphics. The classical bypass capacitor impacts the start-up phase of standard LDOs. However, thanks to its low-noise architecture, the NCP4561 operates without a bypass element and thus offers a typical 40 µs start-up phase.

### Protections

The NCP4561 hosts several protections, giving natural ruggedness and reliability to the products implementing the component. The output current is internally limited to a maximum value of 180 mA typical while temperature shutdown occurs if the die heats up beyond 125°C. These values let you assess the maximum differential voltage the device can sustain at a given output current before its protections come into play.

The maximum dissipation the package can handle is given by:

$$P_{max} = \frac{T_{Jmax} - T_A}{R_{\theta JA}}$$

If T<sub>Imax</sub> is limited to 125°C, then the NCP4561 can dissipate up to 470 mW @ 25°C. The power dissipated by the NCP4561 can be calculated from the following formula:

$$Ptot = \left(V_{in} \times I_{gnd}(I_{out})\right) + \left(V_{in} - V_{out}\right) \times I_{out}$$

$$Vin_{max} = \frac{Ptot + V_{out} \times I_{out}}{I_{gnd} + I_{out}}$$

If a 80 mA output current is needed, the ground current is extracted from the data-sheet curves: 4.0 mA @ 80 mA. For a NCP4561SN28T1 (2.8 V) delivering 80 mA and operating at 25°C, the maximum input voltage will then be 8.3 V.

### **Typical Applications**

The following figure portrays the typical application of the NCP4561.

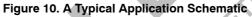

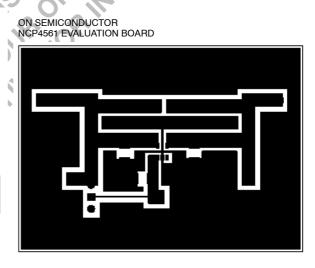

### **PCB Layout Considerations**

As for any low noise designs, particular care has to be taken when tackling Printed Circuit Board (PCB) layout. The figure below gives an example of a layout where stray

inductances/capacitances are minimized. This layout is the basis for the NCP4561 performance evaluation board. The BNC connectors give the user an easy and quick evaluation mean.

Figure 11. PCB Layout

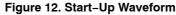

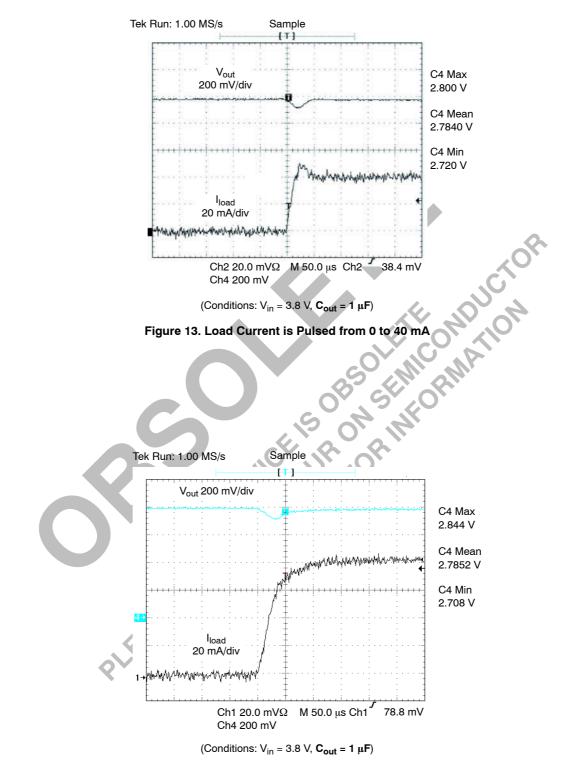

### Understanding the Load Transient Improvement

The NCP4561 features a novel architecture which allows the user to easily implement the regulator in burst systems where the time between two current shots is kept very small.

The quality of the transient response time is related to many parameters, among which the closed-loop bandwidth with the corresponding phase margin plays an important role. However, other characteristics also come into play like the series pass transistor saturation. When a current perturbation suddenly appears on the output, e.g. a load increase, the error amplifier reacts and actively biases the PNP transistor. During this reaction time, the LDO is in open-loop and the output impedance is rather high. As a result, the voltage brutally drops until the error amplifier effectively closes the loop and corrects the output error. When the load disappears, the opposite phenomenon takes place with a positive overshoot. The problem appears when this overshoot decays down to the LDO steady-state value. During this decreasing phase, the LDO stops the PNP bias and one can consider the LDO asleep. If by misfortune a current shot appears, the reaction time is incredibly lengthened and a strong undershoot takes place. This reaction is clearly not acceptable for line sensitive devices, such as VCOs or other Radio–Frequency parts. This problem is dramatically exacerbated when the output current drops to zero rather than a few mA. In this later case, the internal feedback network is the only discharge path, accordingly lengthening the output voltage decay period.

The NCP4561 cures this problem by implementing a clever design where the LDO detects the presence of the overshoot and forces the system to go back to steady–state as soon as possible, ready for the next shot, which positively improves the response time and decreases the negative peak voltage.

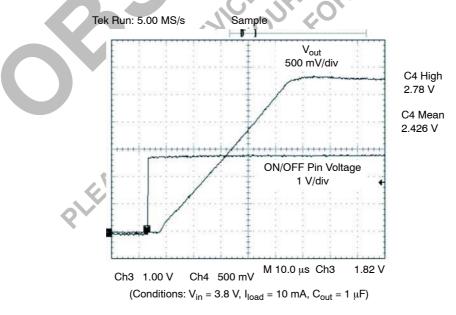

### NCP4561 has a fast start-up phase

Thanks to the lack of bypass capacitor the NCP4561 is able to supply its downstream circuitry as soon as the OFF to ON signal appears. In a standard LDO, the charging time of the external bypass capacitor hampers the response time. A simple solution consists in suppressing this bypass element but, unfortunately, the noise rises to an unacceptable level. NCP4561 offers the best of both worlds since it no longer includes a bypass capacitor and starts in less than 40  $\mu$ s typically (Repetitive at 200 Hz). It also ensures a low-noise level of 40  $\mu$ VRMS 100 Hz-100 kHz. The following picture details the typical NCP4561 startup phase.

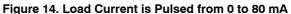

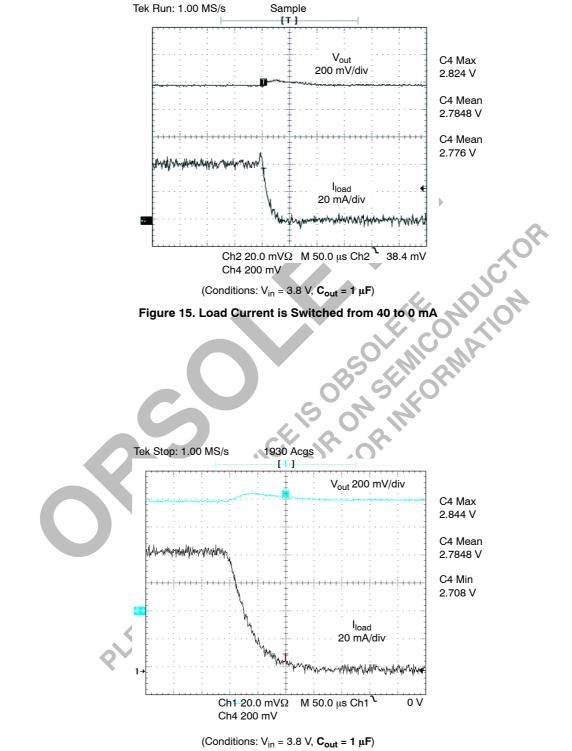

### **TYPICAL TRANSIENT RESPONSES**

### **TYPICAL TRANSIENT RESPONSES**

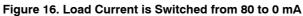

### MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

# **ORDERING INFORMATION**

| Device        | Voltage Output*                       | Package            | Shipping                |

|---------------|---------------------------------------|--------------------|-------------------------|

| ICP4561SN28T1 | 2.8 V                                 | TSOP-5             | 3000 Units /Tape & Reel |

|               | r sales representative for other outp | ut voltage values. |                         |

| Ó             | FRAFERM                               |                    |                         |

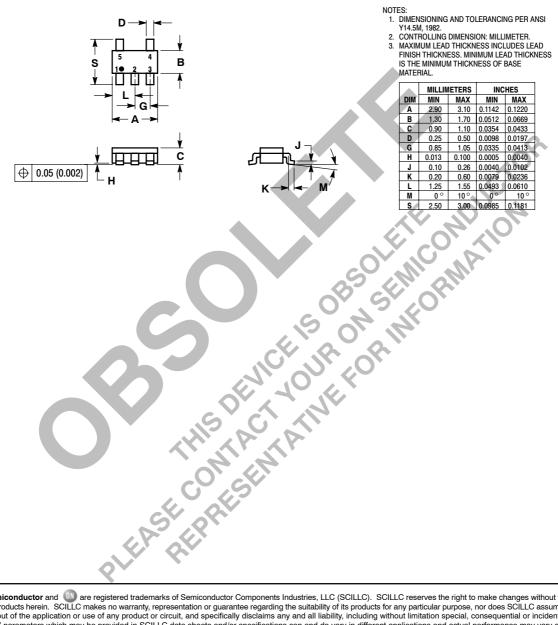

### PACKAGE DIMENSIONS

TSOP-5 SN SUFFIX PLASTIC PACKAGE CASE 483-01 ISSUE B

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agsociated with such unintended or unauthorized use payers that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit//Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative