#### **Features**

- Processor Bus Frequency Up to 66 MHz and 83.3 MHz

- · 64-bit Data Bus and 32-bit Address Bus

- L2 Cache Control for 256-Kbyte, 512-Kbyte, 1-Mbyte Sizes

- Provides Support for Either Asynchronous SRAM, Burst SRAM or Pipelined Burst SRAM

- Compliant with PCI Specification, Revision 2.1

- PCI Interface Operates at 20 to 33 MHz, 3.3V/5.0V-compatible

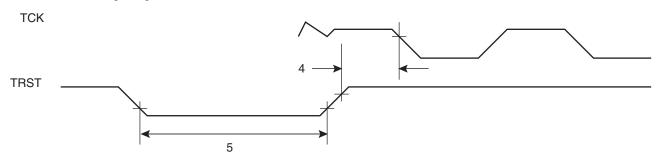

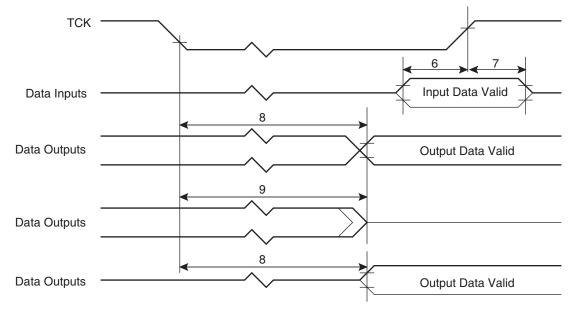

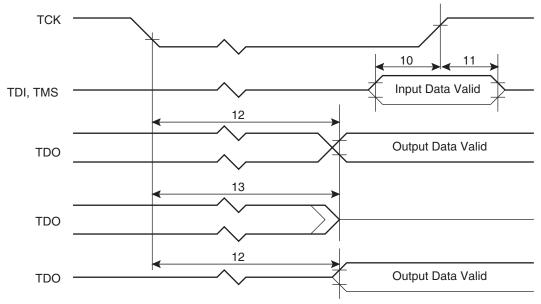

- IEEE 1149.1-compliant, JTAG Boundary-scan Interface

- P<sub>D</sub> Max = 1.7 Watts (66 MHz), Full Operating Conditions

- Nap, Doze and Sleep Modes Reduce Power Consumption

- Fully Compliant with MIL-STD-883 Class Q or According to Atmel Standards

- Upscreenings Based on Atmel Standards

- Full Military Temperature Range (-55°C  $\leq$  T<sub>i</sub>  $\leq$  +125°C)

- Industrial Temperature Range (-40°C ≤ T<sub>i</sub> ≤ +110°C)

- $V_{CC} = 3.3V \pm 5\%$

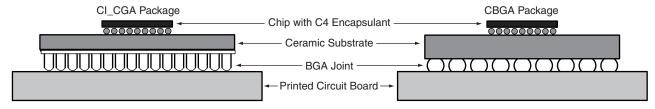

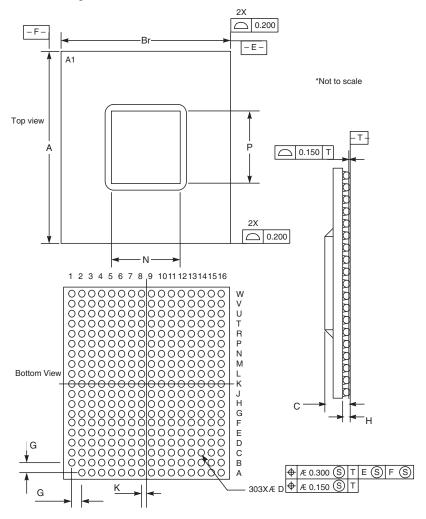

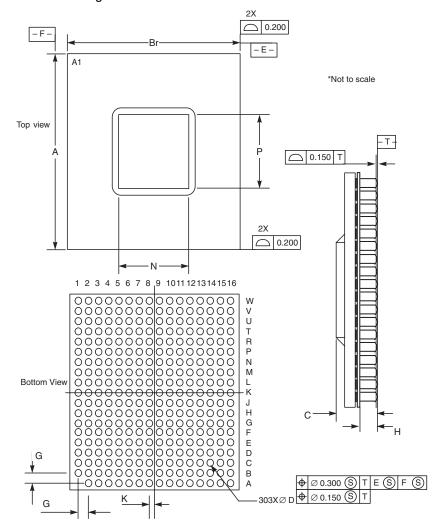

- Available in a 303-ball CBGA or a 303-ball CBGA with Solder Column Interposer (SCI) (CI-CGA) Package

#### **Description**

The TSPC106 provides an integrated, high-bandwidth, high-performance, TTL-compatible interface between a 60x processor, a secondary (L2) cache or up to a total of four additional 60x processors, the PCI bus and main memory.

PCI support allows system designers to rapidly design systems using peripherals already designed for PCI.

The TSPC106 uses an advanced 3.3V CMOS-process technology and maintains full interface compatibility with TTL devices.

The TSPC106 integrates system testability and debugging features via JTAG boundary-scan capability.

G suffix CBGA 303 Ceramic Ball Grid Array

GS suffix

CI-CGA 303

Ceramic Ball Grid Array

with Solder Column Interposer (SCI)

## PCI Bus Bridge Memory Controller 66-83 MHz

#### **TSPC106**

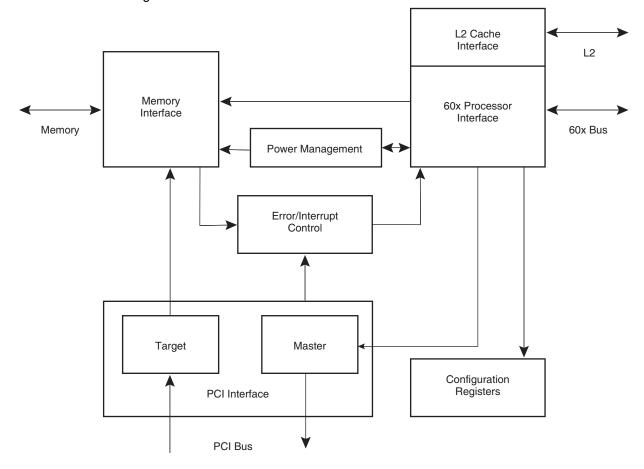

Figure 1. TSPC106 Block Diagram

### **Functional Description**

The TSPC106 provides a PowerPC® microprocessor CHRP-compliant bridge between the PowerPC microprocessor family and the PCI bus. CHRP is a set of specifications that defines a unified personal computer architecture and brings the combined advantages of the Power Macintosh® platform and the standard PC environment to both system vendors and users. PCI support allows system designers to rapidly design systems using peripherals already designed for PCI and other standard interfaces available in the personal computer hardware environment. These open specifications make it easier for system vendors to design computers capable of running multiple operating systems. The TSPC106 integrates secondary cache control and a high-performance memory controller. The TSPC106 uses an advanced 3.3V CMOS process technology and is fully compatible with TTL devices.

The TSPC106 supports a programmable interface to a variety of PowerPC microprocessors operating at select bus speeds. The 60x address bus is 32 bits wide; the data bus is 64 bits wide. The 60x processor interface of the TSPC106 uses a subset of the 60x bus protocol, supporting single-beat and burst data transfers. The address and data buses are decoupled to support pipelined transactions.

The TSPC106 provides support for the following configurations of 60x processors and L2 cache:

- Up to four 60x processors with no L2 cache

- A single 60x processor plus a direct-mapped, lookaside L2 cache using the internal L2 cache controller of the TSPC106

- Up to four 60x processors plus an externally controlled L2 cache (e.g., the Freescale MPC2604GA integrated L2 lookaside cache)

The memory interface controls processor and PCI interactions to main memory and is capable of supporting a variety of configurations using DRAM, EDO, or SDRAM and ROM or Flash ROM.

The PCI interface of the TSPC106 complies with the PCI local bus specification Revision 2.1 and follows the guidelines in the PCI System Design Guide Revision 1.0 for host bridge architecture. The PCI interface connects the processor and memory buses to the PCI bus to which I/O components are connected. The PCI bus uses a 32-bit multiplexed address/data bus plus various control and error signals.

The PCI interface of the TSPC106 functions as both a master and target device. As a master, the 106 supports read and write operations to the PCI memory space, the PCI I/O space and the PCI configuration space. The TSPC106 also supports PCI special-cycle and interrupt-acknowledge commands. As a target, the TSPC106 supports read and write operations to system memory.

The TSPC106 provides hardware support for four levels of power reduction: doze, nap, sleep and suspend. The design of the TSPC106 is fully static, allowing internal logic states to be preserved during all power saving modes.

## **Pin Description**

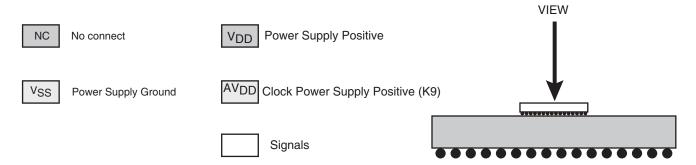

Figure 2. TSPC106 in 303-ball CBGA Package

|   | 16                       | 15                              | 14            | 13             | 12           | 11            | 10             | 9     | 8           | 7    | 6          | 5             | 4                   | 3                     | 2          | 1              |

|---|--------------------------|---------------------------------|---------------|----------------|--------------|---------------|----------------|-------|-------------|------|------------|---------------|---------------------|-----------------------|------------|----------------|

| w | DL26                     | DL28                            | DL30          | DH31           | DH29         | DH27          | DH25           | DH23  | DH21        | DH19 | DH17       | DH15          | DH13                | DH11                  | DH9        | DH7            |

| ٧ | DL24                     | DL27                            | DL29          | DL31           | DH30         | DH28          | DH26           | DH24  | DH20        | DH18 | DH16       | DH14          | DH12                | DH10                  | DH8        | DL22           |

| U | MA1/<br>SDBA0/<br>AR9    | DL23                            | DL25          | DL14           | PLL2         | PLL0          | DL12           | DL10  | DL4         | DL2  | DL0        | DOE/<br>DBGL2 | DBG1                | DH6                   | DL21       | DL20           |

| т | MA2/<br>SDMA2/<br>AR10   | WE                              | DH0           | DL15           | PLL3         | PLL1          | DL13           | DL11  | DL3         | DL1  | TV/<br>BR2 | BA0/<br>BR3   | HIT                 | DIRTY_IN/<br>BR1      | DL19       | DCS/<br>BG3    |

| R | MA3/<br>SDMA3/<br>AR11   | RCS0                            | DH2           | DH1            | DL16         | VSS           | VDD            | DL9   | DL5         | VSS  | VDD        | TWE/<br>BG2   | DIRTY_OUT/<br>BG1   | ADS/<br>DALE/<br>BRL2 | AO         | TS             |

| Р | MA5/<br>SDMA5/<br>AR13   | MA4/<br>SDMA4/<br>AR12          | DH4           | DH3            | VSS          | VDD           | VSS            | DL8   | DL6         | VDD  | VSS        | VDD           | BA1/<br>BAA<br>BGL2 | DWE0/<br>DBG2         | A1         | XATS/<br>SDMA1 |

| N | MA6/<br>SDMA6/<br>AR14   | MA0/<br>SDBA1/<br>SDMA0/<br>AR0 | DL17          | DH5            | VDD          | VSS           | VDD            | DL7   | DH22        | VSS  | VDD        | VSS           | LBCLAIM             | CI                    | A2         | TA             |

| M | MA8/<br>SDMA8/<br>AR16   | MA7/<br>SDMA7/<br>AR15          | RAS0/<br>CS0  | DL18           | VSS          | VDD           | VSS            | NC    | NC          | VDD  | VSS        | VDD           | WT                  | GBL                   | АЗ         | TT4            |

| L | HRST                     | MA9/<br>SDMA9/<br>AR17          | QACK          | RAS1/<br>CS1   | VDD          | CKO/<br>DWE2  | RAS5/<br>CS5   | VSS   | VDD         | VSS  | SYSCLK     | DBG0          | TBST                | BRO                   | A4         | ТТ3            |

| K | MA11/<br>SDMA11/<br>AR19 | MA10/<br>SDMA10/<br>AR18        | RAS3/<br>CS3  | RAS2/<br>CS2   | RAS4/<br>CS4 | RAS7/<br>CS7  | VDD            | AVDD  | VSS         | VDD  | A9         | A8            | A7                  | BG0                   | <b>A</b> 5 | TT2            |

| J | MA12/<br>SDMA12/<br>AR20 | CAS0/<br>DQM0                   | PPEN          | RCS1           | RAS6/<br>CS6 | MCP           | DBGLB/<br>CKE  | VSS   | VDD         | VSS  | A11        | A6            | A13                 | A12                   | A10        | TEA            |

| н | QREQ                     | CAS1/<br>DQM1                   | SUS-<br>PEND  | TRST           | VSS          | DWE1/<br>DBG3 | PIRQ/<br>SDRAS | NC    | NC          | VDD  | VSS        | VDD           | A15                 | A14                   | A16        | TT1            |

| G | CAS2/<br>DQM2            | RTC                             | CAS4/<br>DQM4 | CAS5/<br>DQM5  | VDD          | LSSD_<br>MODE | VDD            | PAR   | TOCK        | VSS  | VDD        | VSS           | TSIZ1               | TSIZ0                 | A17        | тто            |

| F | BCTL0                    | BCTL1                           | CAS6/<br>DQM6 | тск            | VSS          | VDD           | VSS            | PERR  | DEV-<br>SEL | VDD  | VSS        | VDD           | A21                 | TSIZ2                 | ARTRY      | A18            |

| E | CAS3/<br>DQM3            | NMI                             | CAS7/<br>DQM7 | MDLE/<br>SDCAS | TDO          | VSS           | VDD            | SERR  | ĪRDY        | VSS  | VDD        | A31           | A29                 | A22                   | A20        | A19            |

| D | PAR0/<br>AR1             | PAR1/<br>AR2                    | TMS           | FOE            | AD28         | AD24          | AD21           | AD17  | AD14        | AD10 | C/BE0      | AD4           | AD0                 | A30                   | AACK       | A23            |

| С | PAR2/<br>AR3             | PAR3/<br>AR4                    | PAR5/<br>AR6  | AD30           | AD26         | AD23          | AD19           | C/BE2 | C/BE1       | AD12 | AD8        | AD6           | AD2                 | A27                   | A25        | A24            |

| В | PAR4/<br>AR5             | PAR7/<br>AR8                    | AD1           | TDI            | AD7          | AD11          | AD15           | TRDY  | AD18        | AD22 | AD25       | AD29          | REQ                 | ISA_MASTER/<br>BERR   | A28        | A26            |

| A | PAR6/<br>AR7             | GNT                             | AD3           | AD5            | AD9          | AD13          | FRAME          | STOP  | AD16        | AD20 | C/BE3      | AD27          | AD31                | FLSHREQ               | MEMACK     |                |

Figure 3. Pin Assignments Shading Ley

#### **Pinout**

Table 1. TSPC106 Pinout in 303-ball CBGA Package

| Signal Name                     | Pin Number                                                                                                                                     | Active | I/O    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 60x Processor Interface Signals |                                                                                                                                                |        |        |

| A[0:31]                         | R2, P2, N2, M2, L2, K2, J5, K4, K5, K6, J2, J6, J3, J4, H3, H4, H2, G2, F1, E1, E2, F4, E3, D1, C1, C2, B1, C3, B2, E4, D3, E5                 | High   | I/O    |

| AACK                            | D2                                                                                                                                             | Low    | I/O    |

| ARTRY                           | F2                                                                                                                                             | Low    | I/O    |

| BG0                             | К3                                                                                                                                             | Low    | Output |

| BG1 (DIRTY_OUT)                 | R4                                                                                                                                             | Low    | Output |

| BG2 (TWE)                       | R5                                                                                                                                             | Low    | Output |

| BG3 (DCS)                       | T1                                                                                                                                             | Low    | Output |

| BR0                             | L3                                                                                                                                             | Low    | Input  |

| BR1 (DIRTY_IN)                  | Т3                                                                                                                                             | Low    | Input  |

| BR2 (TV)                        | Т6                                                                                                                                             | Low    | Input  |

| BR3 (BA0)                       | T5                                                                                                                                             | Low    | Input  |

| CI                              | N3                                                                                                                                             | Low    | I/O    |

| DBG0                            | L5                                                                                                                                             | Low    | Output |

| DBG1 (TOE)                      | U4                                                                                                                                             | Low    | Output |

| DBG2 (DWE0)                     | P3                                                                                                                                             | Low    | Output |

| DBG3 (DWE1)                     | H11                                                                                                                                            | Low    | Output |

| DBGLB (CKE)                     | J10                                                                                                                                            | Low    | Output |

| DH[0:31]                        | T14, R13, R14, P13, P14, N13, U3, W1, V2, W2, V3, W3, V4, W4, V5, W5, V6, W6, V7, W7, V8, W8, N8, W9, V9, W10, V10, W11, V11, W12, V12, W13    | High   | I/O    |

| DL[0:31]                        | U6, T7, U7, T8, U8, R8, P8, N9, P9, R9, U9, T9, U10, T10, U13, T13, R12, N14, M13, T2, U1, U2, V1, U15, V16, U14, W16, V15, W15, V14, W14, V13 |        |        |

| GBL                             | M3                                                                                                                                             | Low    | I/O    |

| LBCLAIM                         | N4                                                                                                                                             | Low    | Input  |

Table 1. TSPC106 Pinout in 303-ball CBGA Package (Continued)

| Signal Name                   | Pin Number                                            | Active | I/O    |

|-------------------------------|-------------------------------------------------------|--------|--------|

| MCP                           | J11                                                   | Low    | Output |

| TA                            | N1                                                    | Low    | I/O    |

| TBST                          | L4                                                    | Low    | I/O    |

| TEA                           | J1                                                    | Low    | Output |

| TS                            | R1                                                    | Low    | I/O    |

| TSIZ[0:2]                     | G3, G4, F3                                            | High   | I/O    |

| TT[0:4]                       | G1, H1, K1, L1, M1                                    | High   | I/O    |

| WT                            | M4                                                    | Low    | I/O    |

| XATS (SDMA1)                  | P1                                                    | Low    | Input  |

| L2 Cache Interface Signals    |                                                       |        |        |

| ADS/DALE/BRL2                 | R3                                                    | Low    | Output |

| BA0 (BR3)                     | T5                                                    | Low    | Output |

| BA1/BAA/BGL2                  | P4                                                    | Low    | Output |

| DBGL2/DOE                     | U5                                                    | Low    | Output |

| DCS (BG3)                     | T1                                                    | Low    | Output |

| DIRTY_IN (BR1)                | ТЗ                                                    | Low    | Input  |

| DIRTY_OUT (BG1)               | R4                                                    | Low    | Output |

| DWE0 (DBG2)                   | P3                                                    | Low    | Output |

| DWE1 (DBG3)                   | H11                                                   | Low    | Output |

| DWE2 (CKO)                    | L11                                                   | Low    | Output |

| HIT                           | T4                                                    | Low    | Input  |

| TOE (DBG1)                    | U4                                                    | Low    | Output |

| TV (BR2)                      | T6                                                    | High   | I/O    |

| TWE (BG2)                     | R5                                                    | Low    | Output |

| Memory Interface Signals      |                                                       |        |        |

| BCTL [0:1]                    | F16, F15                                              | Low    | Output |

| BERR (ISA_MASTER)             | В3                                                    | Low    | Input  |

| CAS/DQM[0:7]                  | J15, H15, G16, E16, G14, G13, F14, E14                | Low    | Output |

| CKE/DBGLB                     | J10                                                   | High   | Output |

| FOE                           | D13                                                   | Low    | Output |

| MA0/SDBA1/SDMA0/AR0           | N15                                                   | High   | Output |

| SDMA1 (XATS)                  | P1                                                    | High   | Output |

| MA1/SDBA0/AR9                 | U16                                                   | High   | Output |

| MA[2:12]/SDMA[2:12]/AR[10:20] | T16, R16, P15, P16, N16, M15, M16, L15, K15, K16, J16 | High   | Output |

| MDLE/SDCAS                    | E13                                                   | Low    | Output |

| PAR[0:7]/AR[1:8]              | D16, D15, C16, C15, B16, C14, A16, B15                | High   | I/O    |

Table 1. TSPC106 Pinout in 303-ball CBGA Package (Continued)

| Signal Name                          | Pin Number                                                                                                                                    | Active | I/O    |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| PPEN                                 | J14                                                                                                                                           | Low    | Output |

| RAS/CS[0:7]                          | M14, L13, K13, K14, K12, L10, J12, K11                                                                                                        | Low    | Output |

| RCS0                                 | R15                                                                                                                                           | Low    | I/O    |

| RCS1                                 | J13                                                                                                                                           | Low    | Output |

| RTC                                  | G15                                                                                                                                           | High   | Input  |

| SDRAS (PIRQ)                         | H10                                                                                                                                           | Low    | Output |

| WE                                   | T15                                                                                                                                           | Low    | Output |

| PCI Interface Signals <sup>(2)</sup> |                                                                                                                                               |        |        |

| AD[31:0] <sup>(2)</sup>              | A4, C13, B5, D12, A5, C12, B6, D11, C11, B7, D10, A7, C10, B8, D9, A8, B10, D8, A11, C7, B11, D7, A12, C6, B12, C5, A13, D5, A14, C4, B14, D4 | High   | I/O    |

| C/BE[3:0] <sup>(2)</sup>             | A6, C9, C8, D6                                                                                                                                | Low    | I/O    |

| DEVSEL                               | F8                                                                                                                                            | Low    | I/O    |

| FLSHREQ                              | A3                                                                                                                                            | Low    | Input  |

| FRAME                                | A10                                                                                                                                           | Low    | I/O    |

| GNT                                  | A15                                                                                                                                           | Low    | Input  |

| IRDY                                 | E8                                                                                                                                            | Low    | I/O    |

| ISA_MASTER (BERR)                    | B3                                                                                                                                            | Low    | Input  |

| LOCK                                 | G8                                                                                                                                            | Low    | Input  |

| MEMACK                               | A2                                                                                                                                            | Low    | Output |

| PAR                                  | G9                                                                                                                                            | High   | I/O    |

| PERR                                 | F9                                                                                                                                            | Low    | I/O    |

| PIRQ (SDRAS)                         | H10                                                                                                                                           | Low    | Output |

| REQ                                  | B4                                                                                                                                            | Low    | Output |

| SERR                                 | E9                                                                                                                                            | Low    | I/O    |

| STOP                                 | A9                                                                                                                                            | Low    | I/O    |

| TRDY                                 | В9                                                                                                                                            | Low    | I/O    |

| Interrupt, Clock and Power N         | lanagement Signals                                                                                                                            |        |        |

| CK0 (DWE2)                           | L11                                                                                                                                           | High   | Output |

| HRST                                 | L16                                                                                                                                           | Low    | Input  |

| NMI                                  | E15                                                                                                                                           | High   | Input  |

| QACK                                 | L14                                                                                                                                           | Low    | Output |

| QREQ                                 | H16                                                                                                                                           | Low    | Input  |

| SYSCLK                               | L6                                                                                                                                            | Clock  | Input  |

| SUSPEND                              | H14                                                                                                                                           | Low    | Input  |

| Test/Configuration Signals           | ·                                                                                                                                             |        |        |

| PLL[0:3]                             | U11, T11, U12, T12                                                                                                                            | High   | Input  |

Table 1. TSPC106 Pinout in 303-ball CBGA Package (Continued)

| Signal Name              | Pin Number                                                                                                        | Active | I/O    |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|--------|--------|--|--|--|--|--|

| TCK                      | F13                                                                                                               | Clock  | Input  |  |  |  |  |  |

| TDI                      | B13                                                                                                               | High   | Input  |  |  |  |  |  |

| TDO                      | E12                                                                                                               | High   | Output |  |  |  |  |  |

| TMS                      | D14                                                                                                               | High   | Input  |  |  |  |  |  |

| TRST                     | H13                                                                                                               | Low    | Input  |  |  |  |  |  |

| Power and Ground Signals | Power and Ground Signals                                                                                          |        |        |  |  |  |  |  |

| AV <sub>DD</sub>         | К9                                                                                                                | High   | Clock  |  |  |  |  |  |

| LSSD_MODE(3)             | G11                                                                                                               | Low    | Input  |  |  |  |  |  |

| V <sub>DD</sub>          | E10, E6, F11, F5, F7, G10, G12, G6, H5, H7, K10, K7, L12, M11, M5, M7, N10, N12, N6, P11, P5, P7, R10, R6, J8, L8 | High   | Power  |  |  |  |  |  |

| V <sub>SS</sub>          | E11, E7, F10, F12, F6, G5, G7, H12, H6, J7, L7, M10, M12, M6, N11, N5, N7, P10, P12, P6, R11, R7, K8, J9, L9      | Low    | Ground |  |  |  |  |  |

| NC                       | H8, H9, M8, M9                                                                                                    | _      | _      |  |  |  |  |  |

Notes:

- 1. Some signals have dual functions and are shown more than once in this table.

- 2. All PCI signals are in little-endian bit order.

- 3. This test signal is for factory use only. It must be pulled up to V<sub>DD</sub> for normal device operation.

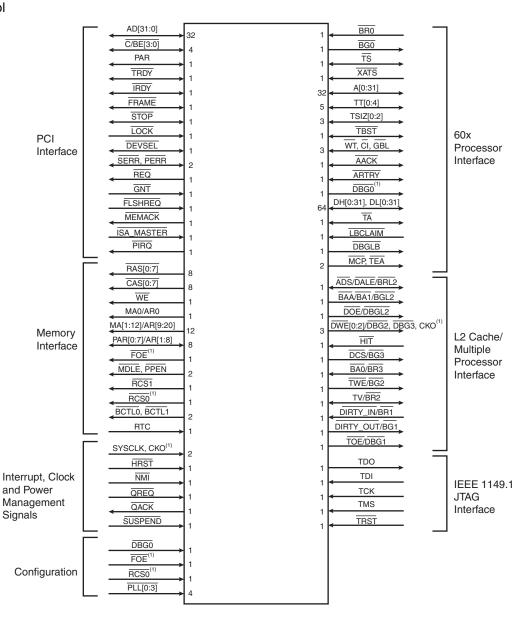

#### **Signal Description**

The signals on the TSPC106 are grouped as follows:

- 60x processor interface signals

- L2 cache/multiple processor interface signals

- Memory interface signals

- PCI interface signals

- Interrupt, clock and power management signals

- IEEE 1149.1 interface signals

- Configuration signals

Note: A bar over a signal name indicates that the signal is active low, for example, address retry  $(\overline{\mathsf{ARTRY}})$  and transfer start  $(\overline{\mathsf{TS}})$ . Active-low signals are referred to as asserted (active)

when they are low and negated when they are high. Signals that are not active low such as tag valid (TV) and nonmaskable interrupt (NMI) are referred to as asserted when they are high and negated when they are low.

are high and negated when they are low.

For multiple-function signals, outlined signal names refer to the alternate function(s) of the signal being described. For example, the L2 controller signal, (tag output enable  $\overline{\text{TOE}}$ ), has the alternate function data bus grant 1 ( $\overline{\text{DBG1}}$ ) when the TSPC106 is configured for a second 60x processor.

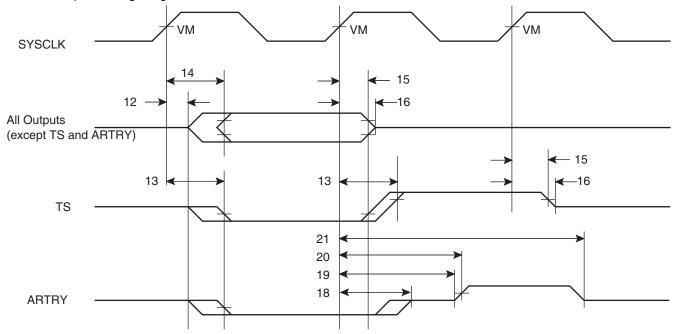

Figure 4. Symbol

Note: Some signals have dual functions and are shown more than once in this figure.

## **60x Processor Interface Signals**

Table 2. 60x Processor Interface Signals

| Signal  | Signal Name                    | Number of Pins | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - J.g   |                                | 1              | 0   | Specifies the physical address for 60x bus snooping.                                                                                                                                                                                                                                                                                              |

| A[0:31] | Address bus                    | 32             | I   | Specifies the physical address of the bus transaction. For burst reads, the address is aligned to the critical double-word address that missed in the instruction or data cache. For burst writes, the address is aligned to the double-word address of the cache line being pushed from the data cache.                                          |

| AACK    | Address                        | 1              | 0   | Indicates that the address tenure of a transaction is terminated. On the cycle following the assertion of AACK, the bus master releases the address-tenure-related signals to a high impedance state and samples ARTRY.                                                                                                                           |

| AACK    | acknowledge                    | , I            | I   | Indicates that an externally-controlled L2 cache is terminating the address tenure. On the cycle following the assertion of AACK, the bus master releases the address-tenure-related signals to a high impedance state and samples ARTRY.                                                                                                         |

|         | Address retry                  |                | 0   | Indicates that the initiating 60x bus master must retry the current address tenure.                                                                                                                                                                                                                                                               |

| ARTRY   |                                | 1              | I   | During a snoop operation, indicates that the 60x either requires the current address tenure to be retried due to a pipeline collision or needs to perform a snoop copy-back operation. During normal 60x bus cycles in a multiprocessor system, indicates that the other 60x or external L2 controller requires the address tenure to be retried. |

| BG0     | Bus grant 0                    | 1              | 0   | Indicates that the primary 60x may, with the proper qualification, begin a bus transaction and assume mastership of the address bus.                                                                                                                                                                                                              |

| BR0     | Bus request 0                  | 1              | 1   | Indicates that the primary 60x requires the bus for a transaction.                                                                                                                                                                                                                                                                                |

| CI      | Cache inhibit                  | 1              | I/O | Indicates that an access is caching-inhibited.                                                                                                                                                                                                                                                                                                    |

| DBG0    | Data bus grant 0               | 1              | 0   | Indicates that the 60x may, with the proper qualification, assume mastership of the data bus.                                                                                                                                                                                                                                                     |

| DBGLB   | Local bus slave data bus grant | 1              | 0   | Indicates that the 60x processor is prepared to accept data and the local bus slave should drive the data bus.                                                                                                                                                                                                                                    |

Table 2. 60x Processor Interface Signals (Continued)

| Signal    | Signal Name                 | Number of<br>Pins | I/O | Signal Description                                                                                                                                                                                                                                    |

|-----------|-----------------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                             |                   |     | The data bus is comprised of two halves - data bus high (DH[0:31]) and data bus low (DL[0:31]). The data bus has the following byte lan assignments:                                                                                                  |

|           |                             |                   |     | Data Byte Byte Lane                                                                                                                                                                                                                                   |

|           |                             |                   |     | DH[0:7] 0                                                                                                                                                                                                                                             |

|           |                             |                   |     | DH[8:15] 1                                                                                                                                                                                                                                            |

|           |                             |                   |     | DH[16:23] 2                                                                                                                                                                                                                                           |

| DH[0:31], | Data bus                    | 64                |     | DH[24:31] 3                                                                                                                                                                                                                                           |

| DL[0:31]  |                             |                   |     | DL[0:7] 4                                                                                                                                                                                                                                             |

|           |                             |                   |     | DL[8:15] 5                                                                                                                                                                                                                                            |

|           |                             |                   |     | DL[16:23] 6                                                                                                                                                                                                                                           |

|           |                             |                   |     | DL[24:31] 7                                                                                                                                                                                                                                           |

|           |                             |                   | 0   | Represents the value of data being driven by the TSPC106.                                                                                                                                                                                             |

|           |                             |                   | I   | Represents the state of data being driven by a 60x processor, the loc bus slave, the L2 cache or the memory subsystem.                                                                                                                                |

| GBL       | Global                      | 1                 | I/O | Indicates that an access is global and hardware needs to enforce coherency.                                                                                                                                                                           |

| LBCLAIM   | Local bus slave cycle claim | 1                 | I   | Indicates that the local bus slave claims the transaction and is responsible for driving TA during the data tenure.                                                                                                                                   |

| MCP       | Machine check               | 1                 | 0   | Indicates that the TSPC106 detected a catastrophic error and the 60 processor should initiate a machine check exception.                                                                                                                              |

| TA        | Transfer                    | 1                 | 0   | Indicates that the data has been latched for a write operation or that the data is valid for a read operation, thus terminating the current dat beat. If it is the last (or only) data beat, this also terminates the data tenure.                    |

| IA        | acknowledge                 | 1                 | 1   | Indicates that the external L2 cache or local bus slave has latched dat for a write operation or is indicating the data is valid for a read operation. If it is the last (or only) data beat, then the data tenure is terminated.                     |

| TBST      | Transfer burst              | 1                 | 0   | Indicates that a burst transfer is in progress.                                                                                                                                                                                                       |

| וטטו      | Hansier Durst               | 1                 | 1   | Indicates that a burst transfer is in progress.                                                                                                                                                                                                       |

| TEA       | Transfer error acknowledge  | 1                 | 0   | Indicates that a bus error has occurred. Assertion of TEA terminates the transaction in progress. An unsupported memory transaction, suc as a direct-store access or a graphics read or write, causes the assertion of TEA (provided TEA is enabled). |

| TS        | Transfer start              | 1                 | 0   | Indicates that the TSPC106 has started a bus transaction and that the address and transfer attribute signals are valid. Note that the TSPC106 only initiates a transaction to broadcast the address of a PC access to memory for snooping purposes.   |

|           |                             |                   | I   | Indicates that a 60x bus master has begun a transaction and that the address and transfer attribute signals are valid.                                                                                                                                |

**Table 2.** 60x Processor Interface Signals (Continued)

| Signal    | Signal Name                     | Number of<br>Pins | I/O | Signal Description                                                                                                                                                                                                                                         |

|-----------|---------------------------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T017[0:0] | Transfer size                   | 2                 | 0   | Specifies the data transfer size for the 60x bus transaction.                                                                                                                                                                                              |

| TSIZ[0:2] | Transfer size                   | 3                 | I   | Specifies the data transfer size for the 60x bus transaction.                                                                                                                                                                                              |

| TT[0,4]   | Transfer type                   | 5                 | 0   | Specifies the type of 60x bus transfer in progress.                                                                                                                                                                                                        |

| TT[0:4]   |                                 |                   | I   | Specifies the type of 60x bus transfer in progress.                                                                                                                                                                                                        |

| WT        | Write-through                   | 1                 | I/O | Indicates that an access is write-through.                                                                                                                                                                                                                 |

| XATS      | Extended address transfer start | 1                 | I   | Indicates that the 60x has started a direct-store access (using the extended transfer protocol). Since direct-store accesses are not supported by the TSPC106, the TSPC106 automatically asserts when TEA and XATS are asserted (provided TEA is enabled). |

### L2 Cache/Multiple Processor Interface Signals

The TSPC106 provides support for either an internal L2 cache controller or an external L2 cache controller and/or additional 60x processors.

**Internal L2 Controller Signals**

Table 3 lists the interface signals for the internal L2 controller and provides a brief description of their functions. The internal L2 controller supports either burst SRAMs or asynchronous SRAMs. Some of the signals perform different functions depending on the SRAM configuration.

Table 3. Internal L2 Controller Signals

| Signal              | Signal Name               | Number of<br>Pins | I/O | Signal Description                                                                                                         |

|---------------------|---------------------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| ADS<br>DALE<br>BRL2 | Address strobe            | 1                 | 0   | For a burst SRAM configuration, indicates to the burst SRAM that the address is valid to be latched                        |

| BA0<br>BR3          | Burst address 0           | 1                 | I/O | For an asynchronous SRAM configuration, indicates bit 0 of the burst address counter                                       |

| BA1<br>BAA<br>BGL2  | Burst address 1           | 1                 | 0   | For an asynchronous SRAM configuration, indicates bit 1 of the burst address counter                                       |

| BAA<br>BA1<br>BGL2  | Bus address<br>advance    | 1                 | 0   | For a burst SRAM configuration, indicates that the burst RAMs should increment their internal addresses                    |

| DALE<br>ADS<br>BRL2 | Data address latch enable | 1                 | 0   | For an asynchronous SRAM configuration, indicates that the external address latch should latch the current 60x bus address |

| DCS<br>BG3          | Data RAM chip select      | 1                 | 0   | Enables the L2 data RAMs for a read or write operation                                                                     |

| DIRTY_IN<br>BR1     | Dirty in                  | 1                 | 1   | Indicates that the selected L2 cache line is modified. The polarity of DIRTY_IN is programmable                            |

| DIRTY_OUT<br>BG1    | Dirty out                 | 1                 | 0   | Indicates that the L2 cache line should be marked as modified. The polarity of DIRTY_OUT is programmable                   |

Table 3. Internal L2 Controller Signals (Continued)

| Signal                   | Signal Name            | Number of Pins | I/O | Signal Description                                                                                      |

|--------------------------|------------------------|----------------|-----|---------------------------------------------------------------------------------------------------------|

| DOE<br>DBGL2             | Data RAM output enable | 1              | 0   | Indicates that the L2 data RAMs should drive the data bus                                               |

| DWE[0:2]<br>DBG2<br>DBG3 | Data RAM write enable  | 3              | 0   | Indicates that a write to the L2 data RAMs is in progress. Multiple pins are provided to reduce loading |

| HIT                      | Hit                    | 1              | I   | Indicates that the L2 cache has detected a hit. The polarity of HIT is programmable                     |

| TOE<br>DBG1              | Tag output enable      | 1              | 0   | Indicates that the tag RAM should drive the L2 tag address onto the address bus.                        |

| TV<br>BR2                | Tag valid              | 1              | I/O | Indicates that the current L2 cache line should be marked valid. The polarity of TV is programmable     |

| TWE<br>BG2               | Tag write enable       | 1              | 0   | Indicates that the L2 tag address, valid, and dirty bits should be updated                              |

**External L2 Controller Signals** When an external L2 cache controller is used instead of the internal L2 cache controller, four signals change their functions.

Table 4. External L2 Controller Signals

| Signal              | Signal Name                | Number of<br>Pins | I/O | Signal Description                                                                                                                                      |

|---------------------|----------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| BGL2<br>BA1<br>BAA  | External L2 bus grant      | 1                 | 0   | Indicates that the external L2 controller has been granted mastership of the 60x address bus                                                            |

| BRL2<br>ADS<br>DALE | External L2 bus request    | 1                 | I   | Indicates that the external L2 controller requires mastership of the 60x bus for a transaction                                                          |

| DBGL2<br>DOE        | External L2 data bus grant | 1                 | 0   | Indicates that the external L2 controller has been granted mastership of the 60x data bus                                                               |

| HIT                 | External L2 hit            | 1                 | I   | Indicates that the current transaction is claimed by the external L2 controller. The external L2 controller will assert AACK and TA for the transaction |

## Multiple Processor Signals

When a system implementation uses more than one 60x processor, nine of the internal L2 cache controller signals change their functions.

Note that in a multi-processor system, with the exception of the bus grant, bus request and data bus grant signals, all of the 60x processor interface signals are shared by all 60x processors.

Table 5. Multiple Processor Signals

| Signal           | Signal Name      | Number of Pins | I/O | Signal Description                                                                                                                   |

|------------------|------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| BG1<br>DIRTY_OUT | Bus grant 1      | 1              | 0   | Indicates that processor 1 may, with the proper qualification, begin a 60x bus transaction and assume mastership of the address bus. |

| BG2<br>TWE       | Bus grant 2      | 1              | 0   | Indicates that processor 2 may, with the proper qualification, begin a 60x bus transaction and assume mastership of the address bus. |

| BG3<br>DCS       | Bus grant 3      | 1              | 0   | Indicates that processor 3 may, with the proper qualification, begin a 60x bus transaction and assume mastership of the address bus. |

| BR1<br>DIRTY_IN  | Bus request 1    | 1              | I   | Indicates that processor 1 requires mastership of the 60x bus for a transaction.                                                     |

| BR2<br>TV        | Bus request 2    | 1              | I   | Indicates that processor 2 requires mastership of the 60x bus for a transaction.                                                     |

| BR3<br>BA0       | Bus request 3    | 1              | I   | Indicates that processor 3 requires mastership of the 60x bus for a transaction.                                                     |

| DBG1<br>TOE      | Data bus grant 1 | 1              | 0   | Indicates that processor 1 may, with the proper qualification, assume mastership of the 60x data bus.                                |

| DBG2<br>DWE0     | Data bus grant 2 | 1              | 0   | Indicates that processor 2 may, with the proper qualification, assume mastership of the 60x data bus.                                |

| DBG3<br>DWE1     | Data bus grant 3 | 1              | 0   | Indicates that processor 3 may, with the proper qualification, assume mastership of the 60x data bus.                                |

# Memory Interface Signals

Table 6 lists the memory interface signals and provides a brief description of their functions. The memory interface supports either standard DRAMs or EDO DRAMs, and either standard ROMs or Flash ROMs. Some of the memory interface signals perform different functions depending on the RAM and ROM configurations.

Table 6. Memory Interface Signals

| Signal                             | Signal Name                    | Number of Pins | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                                    |  |  |

|------------------------------------|--------------------------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AR0<br>MA0                         | ROM address 0                  | 8              | 0   | Represents address bit 0 of the 8-bit ROM/Flash. Note that AR0 is only supported for ROM bank 0 when configured for an 8-bit ROM/Flash data bus width. The extra address bit allows for up to 2 Mbytes of ROM when using the 8-bit wide data path. Bits 1 - 8 of the ROM address are provided by AR[1:8] and bits 9 - 20 of the ROM address are provided by AR[9:20]. |  |  |

| AR[1:8]<br>PAR[0:7]                | ROM address 1 - 8              | 8              | 0   | Represents bits 1 - 8 of the ROM/Flash address. The other ROM address bits are provided by AR0 and AR[9:20].                                                                                                                                                                                                                                                          |  |  |

| AR[9:20]<br>MA[1:12]               | ROM address<br>9 - 20          | 12             | 0   | Represents bits 9 - 20 of the ROM/Flash address (the 12 lowest order bits, with AR20 as the least significant bit (lsb)). Bits 0 - 8 of the ROM address are provided by AR0 and AR[1:8].                                                                                                                                                                              |  |  |

| BCTL[0:1]                          | Buffer control 0 - 1           | 2              | 0   | Used to control external data bus buffers (directional control and high-impedance state) between the 60x bus and memory. Note that external data buffers may be optional for lightly loaded data buses, but buffers are required whenever an L2 cache and ROM/Flash (on the 60x/memory bus are both in the system or when ECC is used.                                |  |  |

| CAS[0:7]                           | Column address<br>strobe 0 - 7 | 8              | 0   | Indicates a memory column address is valid and selects one of the columns in the row. CASO connects to the most significant byte select.  CASO connects to the least significant byte select.                                                                                                                                                                         |  |  |

| FOE                                | Flash output enable            | 1              | 0   | Enables Flash output for the current read access.                                                                                                                                                                                                                                                                                                                     |  |  |

| MA0<br>MA[1:12]<br>AR0<br>AR[9:20] | Memory address<br>0 - 12       | 13             | 0   | Represents the row/column multiplexed physical address for DRAMs or EDOs (MA0 is the most significant address bit; MA12 is the least significant address bit). Note that MA0 also functions as the ROM address signal AR0 and MA[1:12] function as the ROM address signals AR[9:20].                                                                                  |  |  |

| MDLE                               | Memory data latch enable       | 1              | 0   | Enables the external, latched data buffer for read operations, if such a buffer is used in the system.                                                                                                                                                                                                                                                                |  |  |

| PAR[0:7]                           | Data parity/ECC                | 8              | 0   | Represents the byte parity or ECC being written to memory (PAR0 is the most significant bit).                                                                                                                                                                                                                                                                         |  |  |

| AR[1:8]                            | Бата рапту/ЕСС                 | 0              | I   | Represents the byte parity or ECC being read from memory (PAR0 is the most significant bit).                                                                                                                                                                                                                                                                          |  |  |

| PPEN                               | Parity path read enable        | 1              | 0   | Enables external parity/ECC bus buffer or latch for memory read operations.                                                                                                                                                                                                                                                                                           |  |  |

| RAS[0:7]                           | Row address strobe 0 - 7       | 8              | 0   | Indicates a memory row address is valid and selects one of the rows in the bank.                                                                                                                                                                                                                                                                                      |  |  |

| RCS0                               | ROM/Flash bank 0 select        | 1              | 0   | Selects ROM/Flash bank 0 for a read access or Flash bank 0 for a read or write access.                                                                                                                                                                                                                                                                                |  |  |

| RCS1                               | ROM/Flash bank 1 select        | 1              | 0   | Selects ROM/Flash bank 1 for a read access or Flash bank 1 for a read or write access.                                                                                                                                                                                                                                                                                |  |  |

| RTC                                | Real-time clock                | 1              | I   | External clock source for the memory refresh logic when the TSPC106 is in the suspend power-saving mode.                                                                                                                                                                                                                                                              |  |  |

| WE                                 | Write enable                   | 1              | 0   | Enables writing to DRAM, EDO or Flash.                                                                                                                                                                                                                                                                                                                                |  |  |

#### **PCI Interface Signals**

Table 7 lists the PCI interface signals and provides a brief description of their functions. Note that the bits in Table 7 are referenced in little-endian format.

The PCI specification defines a sideband signal as any signal, not part of the PCI specification, that connects two or more PCI-compliant agent, and has meaning only to those agents. The TSPC106 implements four PCI sideband signals -FLSHREQ, ISA\_MASTER, MEMACK and PIRQ.

Table 7. PCI Interface Signals

| Signal         | Signal Name           | Number of<br>Pins                                   | I/O | Signal Description                                                                                                                                                                                                                                                                                 |  |  |

|----------------|-----------------------|-----------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AD[31:0]       | Address/data          | 32 I/O transaction. During th contain data. AD[7:0] |     | Represents the physical address during the address phase of a transaction. During the data phase(s) of a PCI transaction, AD[31:0] contain data. AD[7:0] define the least significant byte and AD[31:24] the most significant byte.                                                                |  |  |

| C/BE[3:0]      | Command/byte          | 4                                                   | 0   | During the address phase, $\overline{\text{C/BE}}[3:0]$ define the PCI bus command. During the data phase, $\overline{\text{C/BE}}[3:0]$ are used as byte enables. Byte enables determine which byte lanes carry meaningful data. $\overline{\text{C/BE0}}$ applies to the least significant byte. |  |  |

|                | enable                |                                                     | ı   | During the address phase, $\overline{\text{C/BE}}[3:0]$ indicates the PCI bus command that another master is sending. During the data phase $\overline{\text{C/BE}}[3:0]$ indicate which byte lanes are valid.                                                                                     |  |  |

| DEVOE          | Devices and at        |                                                     | 0   | Indicates that the TSPC106 has decoded the address and is the target of the current access.                                                                                                                                                                                                        |  |  |

| DEVSEL         | Device select         | 1                                                   | I   | Indicates that some PCI agent (other than the TSPC106) has decoded its address as the target of the current access.                                                                                                                                                                                |  |  |

| FLSHREQ        | Flush request         | 1                                                   | I   | Indicates that a device needs to have the TSPC106 flush all of its current operations.                                                                                                                                                                                                             |  |  |

| FRAME          | Frame                 | 1                                                   | 0   | Indicates that the TSPC106, acting as a PCI master, is initiating a bus transaction.                                                                                                                                                                                                               |  |  |

|                |                       |                                                     | I   | Indicates that another PCI master is initiating a bus transaction.                                                                                                                                                                                                                                 |  |  |

| GNT            | PCI bus grant         | 1                                                   | ı   | Indicates that the TSPC106 has been granted control of the PCI bus. Note that $\overline{\text{GNT}}$ is a point-to-point signal. Every master has its own $\overline{\text{GNT}}$ SIGNAL.                                                                                                         |  |  |

| ĪRDY           | Initializer ready     | 1                                                   | 0   | Indicates that the TSPC106, acting as a PCI master, can complete the current data phase of a PCI transaction. During a write, the TSPC106 asserts IRDY to indicate that valid data is present on AD[31:0]. During a read, the TSPC106 asserts IRDY to indicate that it is prepared to accept data. |  |  |

|                |                       |                                                     | I   | Indicates another PCI master is able to complete the current data phase of the transaction.                                                                                                                                                                                                        |  |  |

| ISA_<br>MASTER | ISA master            | 1                                                   | 1   | Indicates that an ISA master is requesting system memory.                                                                                                                                                                                                                                          |  |  |

| LOCK           | Lock                  | 1                                                   | I   | Indicates that a master is requesting exclusive access to memory, which may require multiple transactions to complete.                                                                                                                                                                             |  |  |

| MEMACK         | Memory<br>acknowledge | 1                                                   | 0   | Indicates that the TSPC106 has flushed all of its current operations and has blocked all 60x transfers except snoop copy-back operations. The TSPC106 asserts MEMACK in response to assertion of FLSHREQ after the flush is complete.                                                              |  |  |

Table 7. PCI Interface Signals

| Signal | Signal Name                       | Number of<br>Pins | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Signal Description                                                                                                                                                                                                                                                                                 |  |  |

|--------|-----------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PAR    | Parity                            | 1                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Asserted indicates odd parity across the AD[31:0] and $\overline{\text{C/BE}}$ [3:0] signals during address and data phases. Negated indicates even parity.                                                                                                                                        |  |  |

|        |                                   |                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Asserted indicates odd parity driven by another PCI master or the PCI target during read data phases. Negated indicates even parity.                                                                                                                                                               |  |  |