## High voltage high-side driver

#### **Features**

- High voltage rail up to 450 V

- dV/dt immunity ±50 V/nsec in full temperature range

- Driver current capability: 500 mA source, 500 mA sink

- Switching times 100 ns rise/fall with 2.5 nF load

- CMOS/TTL Schmitt trigger inputs with hysteresis and pull down

- Under voltage lock out

- Clamping on V<sub>CC</sub>

- Non inverting input

- Reset circuitry

- SO8 package

#### **Description**

The L9857 is an high voltage device, manufactured with the BCD "off-line" technology.

It has the capability of driving N channel PowerMOS transistors. The upper (floating) section is enabled to work with voltage rail up to 450 V. The logic inputs are CMOS/TTL compatible for ease of interfacing with controlling devices..

Table 1. Device summary

| Order code  | Order code Op. temp range, °C |      | Packing       |

|-------------|-------------------------------|------|---------------|

| L9857-TR    | -40 to +125                   | SO-8 | Tape and reel |

| L9857-TR-LF | -40 to +125                   | SO-8 | Tape and reel |

Content L9857

# Content

| 1 | Bloc  | k diagram and pin description    | 3 |

|---|-------|----------------------------------|---|

|   | 1.1   | Block diagram                    | 3 |

|   | 1.2   | Pin description                  | 3 |

| 2 | Elect | trical specifications            | 4 |

|   | 2.1   | Thermal data                     | 4 |

|   | 2.2   | Absolute maximum ratings         | 4 |

|   | 2.3   | Recommended operating conditions | 5 |

|   | 2.4   | Electrical characteristics       | 5 |

|   | 2.5   | Reset functional diagram         | 7 |

| 3 | Timiı | ng diagrams                      | 8 |

| 4 | Pack  | age information                  | 9 |

| 5 | Revis | sion history1                    | 0 |

## 1 Block diagram and pin description

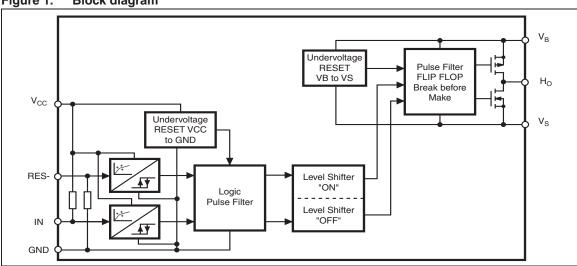

## 1.1 Block diagram

Figure 1. Block diagram

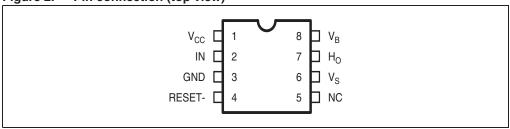

### 1.2 Pin description

Figure 2. Pin connection (top view)

Table 2. Pin function

| Pin # | Pin name       | Description                                  |  |

|-------|----------------|----------------------------------------------|--|

| 1     | $V_{CC}$       | Driver supply, typically 17V                 |  |

| 2     | IN             | Driver control signal input (positive logic) |  |

| 3     | GND            | Ground                                       |  |

| 4     | RESET-         | Driver enable signal input (negative logic)  |  |

| 5     | NC             | No connection (no bondwire)                  |  |

| 6     | V <sub>S</sub> | MOSFET source connection                     |  |

| 7     | H <sub>O</sub> | MOSFET gate connection                       |  |

| 8     | V <sub>B</sub> | Driver output stage supply                   |  |

## 2 Electrical specifications

#### 2.1 Thermal data

Table 3. Thermal data

| Symbol                 | Parameter                                   | Value | Unit |

|------------------------|---------------------------------------------|-------|------|

| R <sub>th(j-amb)</sub> | Thermal resistance junction-to-ambient Max. | 150   | °C/W |

#### 2.2 Absolute maximum ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to GND, all currents are defined positive into any lead. This is a stress only rating and operation of the device at these or any conditions exceeding those indicated in the operational sections of this specifications is not implied.

Table 4. Absolute maximum ratings

|                  | Parameter                                                                                                              | Va                   | Units                 |        |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|--------|--|

| Symbol           | Definition                                                                                                             | Min.                 | Max.                  | Units  |  |

| V <sub>BS</sub>  | High side floating supply voltage                                                                                      | -0.3                 | 20                    | V      |  |

| V <sub>B</sub>   | High side driver output stage voltage                                                                                  | -0.3                 | 300                   | V      |  |

| V <sub>S</sub>   | High side floating supply offset voltage                                                                               | V <sub>B</sub> – 20  | 300                   | V      |  |

| VH <sub>O</sub>  | Output voltage gate connection                                                                                         | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3  | V      |  |

| V <sub>CC</sub>  | Supply voltage                                                                                                         | -0.3                 | 20                    | V      |  |

| V <sub>IN</sub>  | Input voltage                                                                                                          | -0.3                 | V <sub>CC</sub> + 0.3 | V      |  |

| I <sub>IN</sub>  | Input injection current. Full function, no latch-up; (guaranteed by design). Test at 10 V and 17 V on eng. samples.    | -                    | +1                    | mA     |  |

| V <sub>RES</sub> | Reset input voltage                                                                                                    | -0.3                 | V <sub>CC</sub> + 0.3 | V      |  |

| V <sub>esd</sub> | Electrostatic discharge voltage (human body model)                                                                     | 2k                   | -                     | V      |  |

| V <sub>CDM</sub> | Charge device model CDM, EOS/ESD ass. std 5.3. number of discharges per pin: 6                                         | 500                  | -                     | V      |  |

| dV/dt            | Allowable offset voltage slew rate                                                                                     | -50                  | 50                    | V/nsec |  |

| T <sub>j</sub>   | Junction temperature                                                                                                   | -55                  | 150                   |        |  |

| T <sub>stg</sub> | Storage temperature -55 150                                                                                            |                      |                       |        |  |

| TL               | Lead temperature (soldering, 10 seconds) 3 times Bosch soldering profil acc. to Bosch soldering conditions, gen. spec. | -                    | 300                   | °C     |  |

### 2.3 Recommended operating conditions

For proper operations the device should be used within the recommended conditions.

Table 5. Recommended operating conditions

|                  | Parameter                                                       | Val                  | Units           |       |  |

|------------------|-----------------------------------------------------------------|----------------------|-----------------|-------|--|

| Symbol           | Definition                                                      | Min.                 | Max.            | Onits |  |

| V <sub>B</sub>   | High side driver output stage voltage -5 V transient 0.1µs      | VS+10 <sup>(1)</sup> | VS+18           | V     |  |

| V <sub>S</sub>   | High side floating supply offset voltage - 20 V transient 0.1µs | -5                   | 300             | V     |  |

| V <sub>HO</sub>  | Output voltage gate connection                                  | Vs                   | V <sub>B</sub>  | V     |  |

| V <sub>CC</sub>  | Supply voltage                                                  | 10                   | 18              | V     |  |

| V <sub>IN</sub>  | Input voltage                                                   | 0                    | V <sub>CC</sub> | V     |  |

| V <sub>RES</sub> | Reset input voltage                                             | 0                    | V <sub>CC</sub> | V     |  |

| F <sub>S</sub>   | Switching frequency                                             | -                    | 200             | kHz   |  |

| T <sub>amb</sub> | Ambient temperature                                             | -40                  | 125             | °C    |  |

<sup>1.</sup> Reset-Logic functional for  $V_B$ - $V_S$ =2V, independent from VCC-level

#### 2.4 Electrical characteristics

Unless otherwise specified, V<sub>CC</sub> = 15 V, V<sub>BS</sub> = 15 V, V<sub>S</sub> = 0 V, IN = 0 V, RES = 5 V, load R = 50  $\Omega$ , C = 2.5 nF. Unless otherwise noted, these specifications apply for an operating junction temperature range of -40 °C  $\leq$  T $_{\rm j}$   $\leq$  125 °C

Table 6. Electrical characteristics

| Symbol                | Parameter                                              | Test condition                                                        | Min. | Тур. | Max. | Unit |  |  |

|-----------------------|--------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|------|--|--|

| V <sub>CC</sub> suppl | V <sub>CC</sub> supply                                 |                                                                       |      |      |      |      |  |  |

| V <sub>CCUV</sub>     | V <sub>CC</sub> supply undervoltage                    | V <sub>CC</sub> rising from 0 V<br>V <sub>CC</sub> dropping from 10 V | 7.2  | -    | 9.6  | V    |  |  |

| V <sub>CCUVHYS</sub>  | V <sub>CC</sub> supply undervoltage lockout hysteresis | -                                                                     | 0.02 | 0.2  | 0.4  | V    |  |  |

| td <sub>UVCC</sub>    | Undervoltage lockout response time                     | V <sub>CC</sub> steps either from 10 V to 6 V or from 6 V to 10 V     | 0.5  | -    | 20   | μS   |  |  |

| I <sub>QCC</sub>      | V <sub>CC</sub> supply current                         | -                                                                     | -    | -    | 400  | μΑ   |  |  |

| V <sub>BS</sub> suppl | V <sub>BS</sub> supply                                 |                                                                       |      |      |      |      |  |  |

| V <sub>BSUV</sub>     | V <sub>BS</sub> supply undervoltage                    | V <sub>BS</sub> rising from 0 V<br>V <sub>BS</sub> dropping from 10 V | 7.2  | -    | 9.6  | V    |  |  |

| td <sub>UVBS</sub>    | Undervoltage lockout response time                     | V <sub>BS</sub> steps either from 10 V<br>to 6 V or from 6 V to 10 V  | 0.5  | -    | 20   | μS   |  |  |

Table 6. Electrical characteristics (continued)

| Symbol               | Parameter                                                                         | Test condition                                                                                                                                                              | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>BSUVHYS</sub> | V <sub>BS</sub> supply undervoltage lockout hysteresis                            | -                                                                                                                                                                           | 0.02 | 0.2  | 0.4  | V    |

| I <sub>QBS1</sub>    | V <sub>BS</sub> supply current                                                    | static mode, V <sub>BS</sub> = 10 V,<br>IN = 0 V or 5 V                                                                                                                     | -    | -    | 100  | μА   |

| I <sub>QBS2</sub>    | v <sub>BS</sub> supply current                                                    | static mode, V <sub>BS</sub> = 18 V,<br>IN = 0 V or V <sub>CC</sub>                                                                                                         | -    | -    | 200  | μА   |

| ΔV <sub>BS</sub>     | V <sub>BS</sub> drop due to output turn-on                                        | $V_{BS} = 17 \text{ V}, C_{BS} = 1 \mu\text{F}, \\ td_{IG-IN} = 3 \mu\text{s}, t_{TEST} = 100 \mu\text{s}$                                                                  | -    | -    | 210  | mV   |

| Gate drive           | er characteristics                                                                |                                                                                                                                                                             |      | •    |      |      |

| I <sub>PKSo1</sub>   |                                                                                   | $V_{BS} = 10 \text{ V}$ , $T_j = 25 ^{\circ}\text{C}$ $PW \leq 10 \mu\text{s}$                                                                                              | 120  | 250  | -    |      |

| I <sub>PKSo2</sub>   | Dock cuttout course outwork                                                       | $V_{BS} = 10 \text{ V}$<br>PW $\leq 10  \mu\text{s}$                                                                                                                        | 70   | 150  | -    | A    |

| I <sub>PKSo3</sub>   | Peak output source current                                                        | $V_{BS}$ = 17 V, $T_j$ = 25 °C PW $\leq$ 10 $\mu s$                                                                                                                         | 250  | 500  | -    | mA   |

| I <sub>PKSo4</sub>   |                                                                                   | $V_{BS} = 17 \text{ V},$<br>$PW \le 10  \mu\text{s}$                                                                                                                        | 150  | 300  | -    |      |

| I <sub>HOH,off</sub> | HOH off-state leakage current                                                     | Guaranteed by design                                                                                                                                                        | -    | -    | 1    | μА   |

| t <sub>r1</sub>      |                                                                                   | $V_{BS} = 10 \text{ V}, T_j = 25^{\circ}\text{C}$                                                                                                                           | -    | 0.2  | 0.4  | μs   |

| t <sub>r2</sub>      | Output rise time                                                                  | V <sub>BS</sub> = 10 V                                                                                                                                                      | -    | 0.3  | 0.5  |      |

| t <sub>r3</sub>      | Output rise time                                                                  | $V_{BS} = 17 \text{ V}, T_j = 25 ^{\circ}\text{C}$                                                                                                                          | -    | 0.1  | 0.2  |      |

| t <sub>r4</sub>      |                                                                                   | V <sub>BS</sub> = 17 V                                                                                                                                                      | -    | 0.15 | 0.3  |      |

| I <sub>PKSi1</sub>   |                                                                                   | $\begin{split} &\text{IN} = \text{V}_{\text{CC}},  \text{T}_{j} = 25  ^{\circ}\text{C} \\ &\text{V}_{\text{BS}} = 10   \text{V},  \text{PW} < 10   \mu\text{s} \end{split}$ | 120  | 250  | -    |      |

| I <sub>PKSi2</sub>   | Dools outrout oints ourroant                                                      | $\begin{split} &IN = V_{CC}, \\ &V_{BS} = 10V \;, \; PW < 10 \; \mu s \end{split}$                                                                                          | 70   | 150  | -    | A    |

| I <sub>PKSi3</sub>   | Peak output sink current                                                          | $IN = V_{CC}, T_j = 25  ^{\circ}C$ $V_{BS} = 17  V,  PW < 10  \mu s$                                                                                                        | 250  | 500  | -    | mA   |

| I <sub>PKSi4</sub>   |                                                                                   | $\begin{split} &\text{IN} = \text{V}_{\text{CC}}, \\ &\text{V}_{\text{BS}} = 17 \text{ V, PW} < 10  \mu\text{s} \end{split}$                                                | 150  | 300  | -    |      |

| t <sub>f1</sub>      |                                                                                   | $V_{BS} = 10 \text{ V}, T_j = 25 ^{\circ}\text{C}$                                                                                                                          | -    | 0.2  | 0.4  |      |

| t <sub>f2</sub>      | Output fall time                                                                  | V <sub>BS</sub> = 10 V                                                                                                                                                      | -    | 0.3  | 0.5  |      |

| t <sub>f3</sub>      | Output fall time                                                                  | $V_{BS} = 17 \text{ V, } T_j = 25 ^{\circ}\text{C}$                                                                                                                         | -    | 0.1  | 0.2  | μS   |

| t <sub>f4</sub>      |                                                                                   | V <sub>BS</sub> = 17 V                                                                                                                                                      | -    | 0.15 | 0.3  |      |

| t <sub>plh</sub>     | Input-to-output turn-on propogation delay (50 % input level to 10 % output level) | -                                                                                                                                                                           | -    | 0.1  | 0.3  | μs   |

Table 6. Electrical characteristics (continued)

| Symbol             | Parameter                                                                         | Test condition                                                                             | Min. | Тур. | Max. | Unit |  |

|--------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|--|

| t <sub>phl</sub>   | Input-to-output turn-off propagation delay (50 % input level to 90% output level) | -                                                                                          | -    | 0.1  | 0.2  |      |  |

| tphl_res           | RES-to-output turn-off propogation delay (50% input level to 90% output levels)   | -                                                                                          | -    | 0.1  | 0.3  | μs   |  |

| tplh_res           | RES-to-output turn-on propogation delay (50% input level to 10% output levels)    | -                                                                                          | -    | 0.1  | 0.8  |      |  |

| Input cha          | Input characteristics                                                             |                                                                                            |      |      |      |      |  |

| V <sub>INH</sub>   | High logic level input threshold                                                  | -                                                                                          | 9.5  | -    | -    | V    |  |

| V <sub>INL</sub>   | Low logic level input threshold                                                   | -                                                                                          | -    | -    | 6    | V    |  |

| R <sub>IN</sub>    | High logic level input resistance (Pull-down resistor)                            | -                                                                                          | 60   | -    | 300  | kΩ   |  |

| I <sub>IN</sub>    | Low logic level input current                                                     | V <sub>IN</sub> = 0                                                                        | -    | -    | 5    | μА   |  |

| V <sub>H_RES</sub> | High logic level RES input threshold                                              | Reset signal comes from a 5 V system!                                                      | 3.5  | -    | -    | V    |  |

| V <sub>L_RES</sub> | Low Logic Level RES input threshold                                               | R eset signal comes from a 5V system!                                                      | -    | -    | 1.4  | V    |  |

| R <sub>RES</sub>   | High logic level RES input resistance (Pull-down resistor)                        | Reset signal comes from a 5 V system with pull-up resistor 3.8 k $\Omega$ to 5 V. $^{(1)}$ | 60   | -    | 300  | kΩ   |  |

| I <sub>RES</sub>   | Low logic level input current                                                     | V <sub>RES</sub> = 0                                                                       | -    | -    | 5    | μА   |  |

<sup>1. 4</sup> HS-driver reset- inputs and other IC with their input pull-down resistors are connected in parallel with the RESET wire.

The enable input RES- is an active low input, that means a logic low turns the external Power MOSFET off. The input circuitry has to make sure, that the MOSFET is off, when the pin is open or floating. In the application the RES- pin is tied to a bipolar open collector transistor or MOSFET open drain transistor with pull-up resistor 3.8K to +5V together with other RES- inputs of other IC.

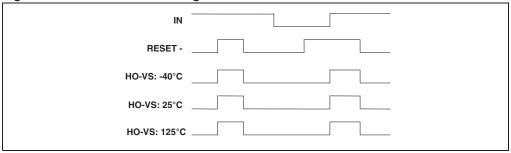

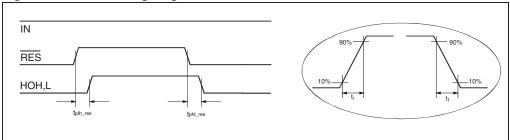

## 2.5 Reset functional diagram

The diagram is guaranteed for the following condition.  $V_{CC}$  = 10 V;  $V_{BS}$  = 10 V @ -40 °C,  $V_{CC}$  = 17 V;  $V_{BS}$  = 17 V @ +25 °C and 125 °C

Figure 3. Reset functional diagram

Timing diagrams L9857

# 3 Timing diagrams

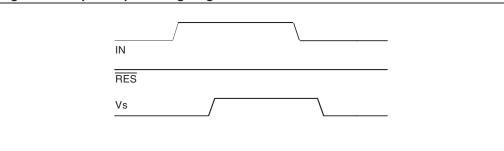

Figure 4. Input/output timing diagram

Figure 5. Reset timing diagram

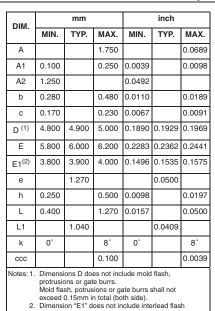

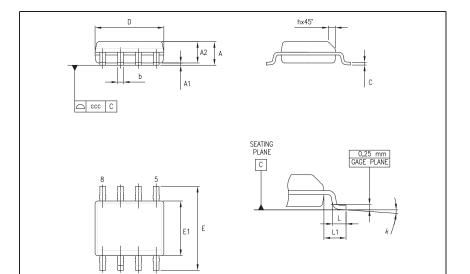

### 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

Figure 6. SO-8 mechanical data and package dimensions

or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

# OUTLINE AND MECHANICAL DATA

0016023 D

Revision history L9857

# 5 Revision history

Table 7. Document revision history

| Date         | Revision | Changes                          |  |

|--------------|----------|----------------------------------|--|

| 20-Nov-2006  | 1        | Initial release.                 |  |

| 07-Oct-2009  | 2        | Updated Table 1: Device summary. |  |

| 17-Sept-2013 | 3        | Updated Disclaimer               |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com