## **ESD Protection Diode**

# Low Capacitance Array for High Speed Data Lines

The ESD8008 is designed specifically to protect four high speed differential pairs. Ultra-low capacitance and low ESD clamping voltage make this device an ideal solution for protecting voltage sensitive high speed data lines. The flow-through style package allows for easy PCB layout and matched trace lengths necessary to maintain consistent impedance for the high speed lines.

#### Features

- Integrated 4 Pairs (8 Lines) High Speed Data

- Single Connect, Flow through Routing

- Low Capacitance (0.35 pF Max, I/O to GND)

- Protection for the Following IEC Standards: IEC 61000-4-2 Level 4 (ESD) ±15 kV (Contact) IEC 61000-4-5 (Lightning) 5 A (8/20 μs)

- UL Flammability Rating of 94 V–0

- SZ Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q101 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- V-by-One HS

- LVDS

- Display Port

#### MAXIMUM RATINGS (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                                                  | Symbol           | Value       | Unit     |

|-------------------------------------------------------------------------|------------------|-------------|----------|

| Operating Junction Temperature Range                                    | TJ               | -55 to +125 | °C       |

| Storage Temperature Range                                               | T <sub>stg</sub> | -55 to +150 | °C       |

| Lead Solder Temperature –<br>Maximum (10 Seconds)                       | ΤL               | 260         | °C       |

| IEC 61000-4-2 Contact (ESD)<br>IEC 61000-4-2 Air (ESD)                  | ESD<br>ESD       | ±15<br>±15  | kV<br>kV |

| Maximum Peak Pulse Current<br>8/20 μs @ T <sub>A</sub> = 25°C (I/O-GND) | I <sub>PP</sub>  | 5.0         | A        |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

See Application Note AND8308/D for further description of survivability specs.

### **ON Semiconductor®**

#### www.onsemi.com

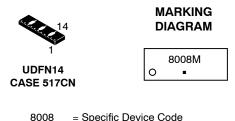

| 8008 | = Specific Device Code |

|------|------------------------|

| М    | = Date Code            |

= Pb-Free Package

#### **ORDERING INFORMATION**

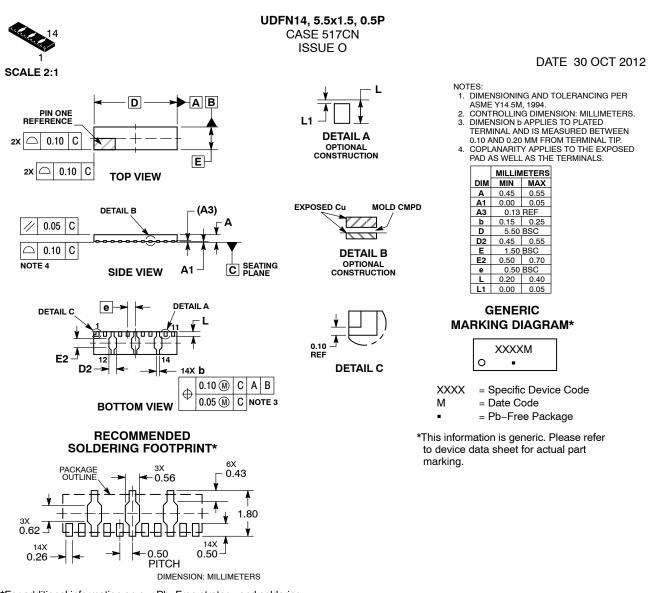

| Device         | Package             | Shipping              |

|----------------|---------------------|-----------------------|

| ESD8008MUTAG   | UDFN14<br>(Pb-Free) | 3000 / Tape &<br>Reel |

| SZESD8008MUTAG | UDFN14<br>(Pb–Free) | 3000 / Tape &<br>Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

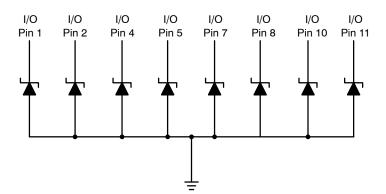

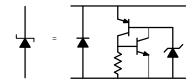

Center Pins, Pin 3, 6, 9, 12, 13, 14 Note: Common GND – Only Minimum of 1 GND connection required

Figure 1. Pin Schematic

Note: Only minimum of one pin needs to be connected to ground for functionality of all pins.

#### **ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = 25°C unless otherwise noted)

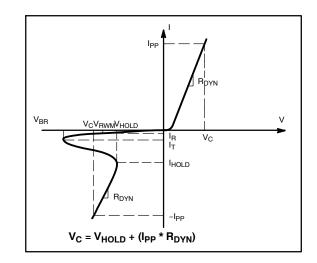

|                   | ·                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                                                        |

| V <sub>RWM</sub>  | Working Peak Voltage                                                                                             |

| I <sub>R</sub>    | Maximum Reverse Leakage Current @ V <sub>RWM</sub>                                                               |

| V <sub>BR</sub>   | Breakdown Voltage @ I <sub>T</sub>                                                                               |

| Ι <sub>Τ</sub>    | Test Current                                                                                                     |

| V <sub>HOLD</sub> | Holding Reverse Voltage                                                                                          |

| I <sub>HOLD</sub> | Holding Reverse Current                                                                                          |

| R <sub>DYN</sub>  | Dynamic Resistance                                                                                               |

| I <sub>PP</sub>   | Maximum Peak Pulse Current                                                                                       |

| V <sub>C</sub>    | Clamping Voltage @ I <sub>PP</sub><br>V <sub>C</sub> = V <sub>HOLD</sub> + (I <sub>PP</sub> * R <sub>DYN</sub> ) |

140

#### **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = $25^{\circ}C$ unless otherwise specified)

| Parameter                        | Symbol            | Conditions                                                                                                                                                                                                                                                                                                                  | Min | Тур                          | Max          | Unit |

|----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|--------------|------|

| Reverse Working Voltage          | V <sub>RWM</sub>  | I/O Pin to GND                                                                                                                                                                                                                                                                                                              |     |                              | 3.3          | V    |

| Breakdown Voltage                | V <sub>BR</sub>   | I <sub>T</sub> = 1 mA, I/O Pin to GND                                                                                                                                                                                                                                                                                       | 5.5 | 7.0                          | 8.5          | V    |

| Reverse Leakage Current          | I <sub>R</sub>    | V <sub>RWM</sub> = 3.3 V, I/O Pin to GND                                                                                                                                                                                                                                                                                    |     |                              | 0.5          | μA   |

| Holding Reverse Voltage          | V <sub>HOLD</sub> | I/O Pin to GND                                                                                                                                                                                                                                                                                                              |     | 1.19                         |              | V    |

| Holding Reverse Current          | I <sub>HOLD</sub> | I/O Pin to GND                                                                                                                                                                                                                                                                                                              |     | 25                           |              | mA   |

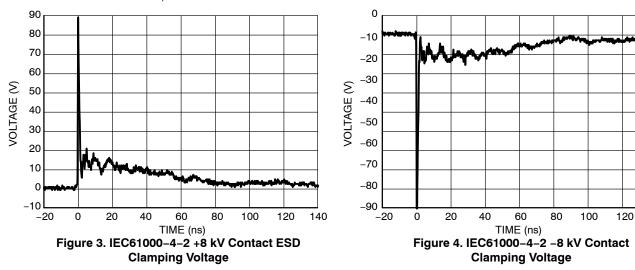

| Clamping Voltage (Note 1)        | V <sub>C</sub>    | IEC61000-4-2, ±8 KV Contact                                                                                                                                                                                                                                                                                                 | See | Figures 3 a                  | nd 4         | V    |

| Clamping Voltage                 | V <sub>C</sub>    | I <sub>PP</sub> = 1 A, Any I/O to GND (8/20 μs pulse)                                                                                                                                                                                                                                                                       |     | 1.5                          |              | V    |

| Clamping Voltage                 | V <sub>C</sub>    | I <sub>PP</sub> = 5 A, Any I/O to GND (8/20 μs pulse)                                                                                                                                                                                                                                                                       |     | 5.0                          |              | V    |

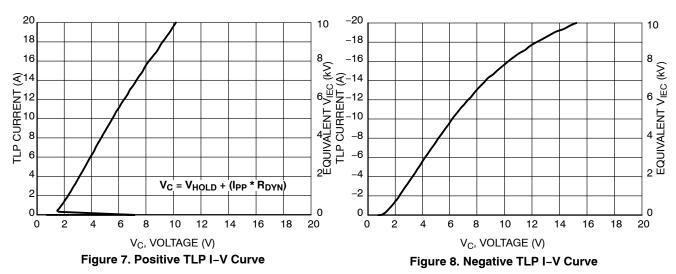

| Clamping Voltage<br>TLP (Note 2) | V <sub>C</sub>    | $ I_{PP} = 8 A  I_{PP} = -8 A $ $ IEC 61000-4-2 Level 2 equivalent  (±4 kV Contact, ±4 kV Air) $                                                                                                                                                                                                                            |     | 4.6<br>-5.1                  |              | V    |

| See Figures 7 through 10         |                   | $ I_{PP} = 16 A  I_{PP} = -16 A $ $ IEC 61000-4-2 Level 4 equivalent  (±8 kV Contact, ±15 kV Air) $                                                                                                                                                                                                                         |     | 8.1<br>-10.3                 |              |      |

| Dynamic Resistance               | R <sub>DYN</sub>  | I/O Pin to GND<br>GND to I/O Pin                                                                                                                                                                                                                                                                                            |     | 0.43<br>0.50                 |              | Ω    |

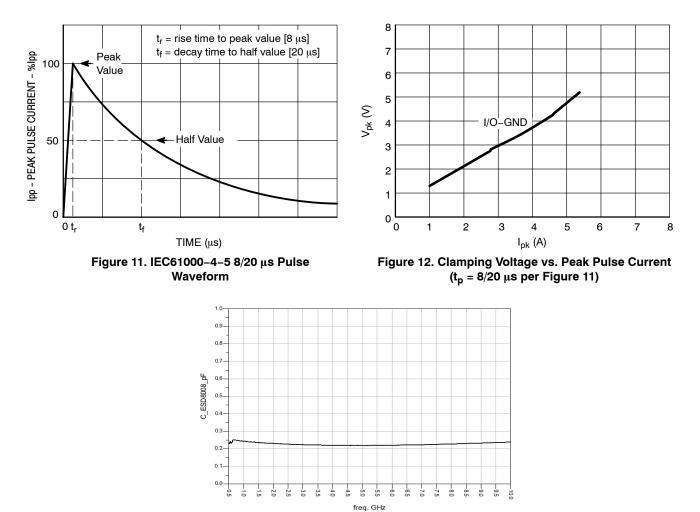

| Junction Capacitance             | Сј                | $ \begin{array}{l} V_R = 0 \; V, \; f = 1 \; MHz \; between \; I/O \; Pins \; and \; GND \\ V_R = 0 \; V, \; f = 2.5 \; GHz \; between \; I/O \; Pins \; and \; GND \\ V_R = 0 \; V, \; f = 5.0 \; GHz \; between \; I/O \; Pins \; and \; GND \\ V_R = 0 \; V, \; f = 1 \; MHz, \; between \; I/O \; Pins \\ \end{array} $ |     | 0.30<br>0.20<br>0.20<br>0.10 | 0.35<br>0.16 | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

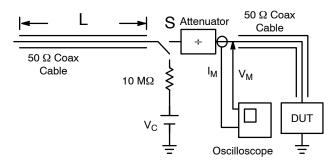

1. For test procedure see Figures 5 and 6 and application note AND8307/D.

2. ANSI/ESD STM5.5.1 – Electrostatic Discharge Sensitivity Testing using Transmission Line Pulse (TLP) Model.

TLP conditions:  $Z_0 = 50 \Omega$ ,  $t_p = 100$  ns,  $t_r = 4$  ns, averaging window;  $t_1 = 30$  ns to  $t_2 = 60$  ns.

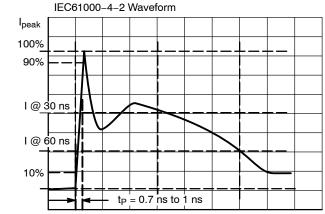

#### IEC 61000-4-2 Spec.

| Level | Test Volt-<br>age (kV) | First Peak<br>Current<br>(A) | Current at<br>30 ns (A) | Current at<br>60 ns (A) |

|-------|------------------------|------------------------------|-------------------------|-------------------------|

| 1     | 2                      | 7.5                          | 4                       | 2                       |

| 2     | 4                      | 15                           | 8                       | 4                       |

| 3     | 6                      | 22.5                         | 12                      | 6                       |

| 4     | 8                      | 30                           | 16                      | 8                       |

Figure 5. IEC61000-4-2 Spec

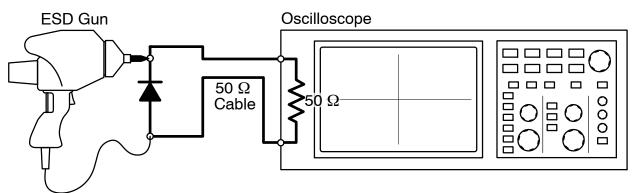

Figure 6. Diagram of ESD Clamping Voltage Test Setup

#### The following is taken from Application Note AND8307/D – Characterization of ESD Clamping Performance.

#### ESD Voltage Clamping

For sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000–4–2 waveform. Since the IEC61000–4–2 was written as a pass/fail spec for larger

systems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes. For more information on how ON Semiconductor creates these screenshots and how to interpret them please refer to AND8307/D.

NOTE: TLP parameter:  $Z_0 = 50 \Omega$ ,  $t_p = 100$  ns,  $t_r = 300$  ps, averaging window:  $t_1 = 30$  ns to  $t_2 = 60$  ns.  $V_{IEC}$  is the equivalent voltage stress level calculated at the secondary peak of the IEC 61000–4–2 waveform at t = 30 ns with 2 A/kV. See TLP description below for more information.

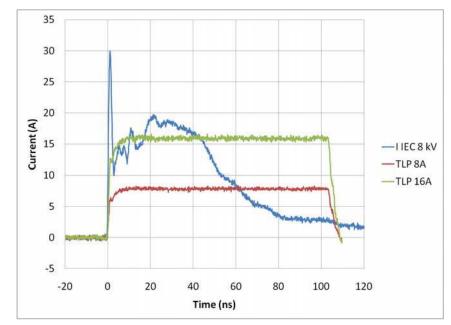

#### Transmission Line Pulse (TLP) Measurement

Transmission Line Pulse (TLP) provides current versus voltage (I–V) curves in which each data point is obtained from a 100 ns long rectangular pulse from a charged transmission line. A simplified schematic of a typical TLP system is shown in Figure 9. TLP I–V curves of ESD protection devices accurately demonstrate the product's ESD capability because the 10s of amps current levels and under 100 ns time scale match those of an ESD event. This is illustrated in Figure 10 where an 8 kV IEC 61000–4–2 current waveform is compared with TLP current pulses at 8 A and 16 A. A TLP I–V curve shows the voltage at which the device turns on as well as how well the device clamps voltage over a range of current levels. For more information on TLP measurements and how to interpret them please refer to AND9007/D.

Figure 9. Simplified Schematic of a Typical TLP System

Figure 10. Comparison Between 8 kV IEC 61000-4-2 and 8 A and 16 A TLP Waveforms

Figure 13. Junction Capacitance;  $V_R = 0$ , f = 500 MHz – 10 GHz

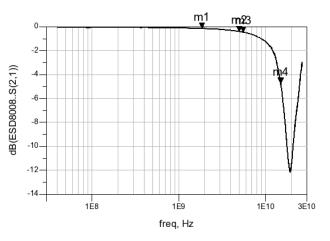

| Interface                                                          | Data Rate | Fundamental     | 3 <sup>rd</sup> Harmonic | ESD8008 Insertion        |

|--------------------------------------------------------------------|-----------|-----------------|--------------------------|--------------------------|

|                                                                    | (Gbps)    | Frequency (GHz) | Frequency (GHz)          | Loss (-dB)               |

| V-by-One HS<br>Full HD (1920 x 1080p)<br>240 Hz, 36bit color depth | 3.71      | 1.854 (m1)      | 5.562 (m3)               | m1 = 0.146<br>m3 = 0.451 |

Figure 14. ESD8008 Insertion Loss

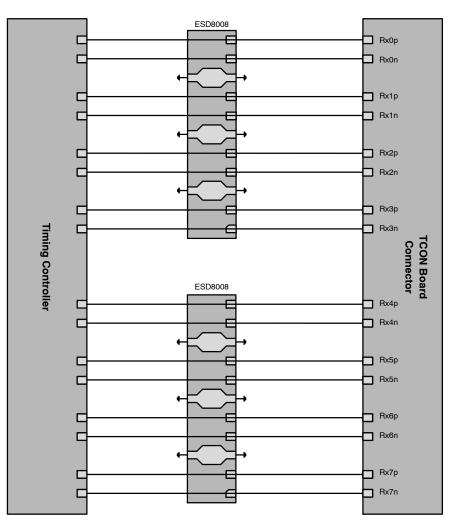

Figure 15. V-by-One HS Layout Diagram (for LCD Panel)

#### **PCB Layout Guidelines**

Steps must be taken for proper placement and signal trace routing of the ESD protection device in order to ensure the maximum ESD survivability and signal integrity for the application. Such steps are listed below.

- Place the ESD protection device as close as possible to the I/O connector to reduce the ESD path to ground and improve the protection performance.

- Make sure to use differential design methodology and impedance matching of all high speed signal traces.

- Use curved traces when possible to avoid unwanted reflections.

- Keep the trace lengths equal between the positive and negative lines of the differential data lanes to avoid common mode noise generation and impedance mismatch.

- Place grounds between high speed pairs and keep as much distance between pairs as possible to reduce crosstalk.

#### Latch-Up Considerations

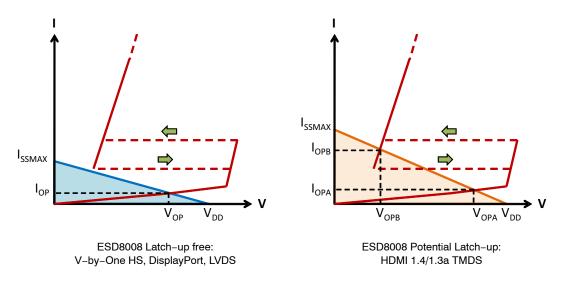

ON Semiconductor's 8000 series of ESD protection devices utilize a snap-back, SCR type structure. By using this technology, the potential for a latch-up condition was taken into account by performing load line analyses of common high speed serial interfaces. Example load lines for latch-up free applications and applications with the potential for latch-up are shown below with a generic IV characteristic of a snapback, SCR type structured device overlaid on each. In the latch-up free load line case, the IV characteristic of the snapback protection device intersects the load-line in one unique point ( $V_{OP}$  IOP). This is the only

stable operating point of the circuit and the system is therefore latch-up free. In the non-latch up free load line case, the IV characteristic of the snapback protection device intersects the load-line in two points ( $V_{OPA}$ ,  $I_{OPA}$ ) and ( $V_{OPB}$ ,  $I_{OPB}$ ). Therefore in this case, the potential for latch-up exists if the system settles at ( $V_{OPB}$ ,  $I_{OPB}$ ) after a transient. Because of this, ESD8008 should not be used for HDMI applications – ESD8104 or ESD8040 have been designed to be acceptable for HDMI applications without latch-up. Please refer to Application Note AND9116/D for a more in-depth explanation of latch-up considerations using ESD8000 series devices.

| Figure 16. Example Load Lines for Latch-u | p Free Applications and A | pplications with the Potential for Latch-up |

|-------------------------------------------|---------------------------|---------------------------------------------|

|                                           |                           |                                             |

| Application        | <b>VBR (min)</b><br>(V) | <b>IH (min)</b><br>(mA) | <b>VH (min)</b><br>(∨) | ON Semiconductor ESD8000 Series<br>Recommended PN |

|--------------------|-------------------------|-------------------------|------------------------|---------------------------------------------------|

| HDMI 1.4/1.3a TMDS | 3.465                   | 54.78                   | 1.0                    | ESD8104, ESD8040                                  |

| DisplayPort        | 3.600                   | 25.00                   | 1.0                    | ESD8004, ESD8006, ESD8008                         |

| V-by-One HS        | 1.980                   | 21.70                   | 1.0                    | ESD8008                                           |

| LVDS               | 1.829                   | 9.20                    | 1.0                    | ESD8008                                           |

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 98AON84523E Electronic versions are uncontrolled except when accessed directly from the Document Repository.   Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION: UDFN14, 5.5X1.5, 0.5P PAGE 1 OF 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |  |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others. |                                                                                                                                                                                                |  |  |  |  |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and **onsemi** makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

Email Requests to: orderlit@onsemi.com onsemi Website: www.onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative