### 4 Channel AISG Integrated Modem

#### **General Description**

The MAX11947 is an AISG v2.0 and v3.0-compliant, fully integrated modem with a 4:1 multiplexer facilitating connectivity between a single modem and up to four RF ports. The MAX11947 receiver offers a typical dynamic range of 20dB and integrates a bandpass filter that operates at the 2.176MHz carrier frequency with a narrow 200kHz bandwidth and is fully compliant with the AISG spectral emission profile. It can modulate OOK signals at the required 9.6kbps and up to 115.2kbps for back compatibility with the older AISG standard. The output power can be varied with an internal register setting from under 0dBm to over +6dBm in order to compensate for loss in the external circuitry and cabling. The receiver sensitivity threshold is also adjustable from the default -15dBm down to less than -20dBm to accommodate power loss through an external splitter. The MAX11947 also features a direction output to facilitate the RS-485 bus arbitration in tower-mounted equipment. The MAX11947 is available in a small. 4mm x 4mm 20-pin TQFN and is rated for operation in the -40°C to +105°C temperature range.

### **Applications**

- Base Station Single and Multi-Primary Controllers (SALD and MALD)

- Antenna Line Devices (ALDs)

- Antenna Arrays

- Tower-Mounted Amplifiers (TMAs)

- Smart Bias-Ts

- RS485 Half-Duplex Coaxial Links

- 2MHz OOK Modem Applications

#### **Benefits and Features**

- AISG v3.0 Compliant

- Fully Integrated Modem with 4:1 Multiplexer Facilitates Connectivity Between 1 Modem and Up to 4 Ports

- Receiver Wide Input Dynamic Range

- -23dBm to +5dBm into 50Ω

- Adjustable Receiver Sensitivity Threshold from -20.5dBm to -15dBm

- Adjustable Transmitter Output Level from -0.5dBm to +7.0dBm into 50Ω

- AISG v3.0/v2.0 Compliant Output Emission Profile

- Autodirection Output

- No Need of Microcontrollers to Handle Bus Arbitration in Tower-Mounted Equipment

- Support All AISG v2.0 Data Rates

- 9.6kbps (default) for AISG v3.0

- 38.4kbps and 115.2kbps for Backward Compatibility

- Bandpass Filter Compliant with AISG v3.0 Protocol Centered on 2.176MHz

- 3.0V to 5.5V Voltage Supply

- Independent Logic Supply

- Small, 4mm x 4mm 20-Pin TQFN Package

#### Ordering Information appears at end of data sheet.

# 4 Channel AISG Integrated Modem

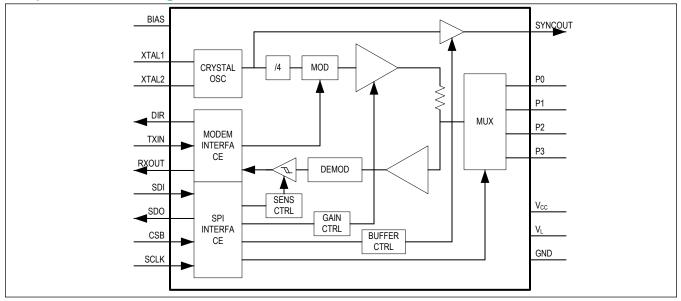

# Simplified Block Diagram

# 4 Channel AISG Integrated Modem

### **TABLE OF CONTENTS**

| General Description                                      |

|----------------------------------------------------------|

| Applications                                             |

| Benefits and Features                                    |

| Simplified Block Diagram 2                               |

| Absolute Maximum Ratings                                 |

| Package Information                                      |

| 20-Pin TQFN                                              |

| Electrical Characteristics                               |

| Typical Operating Characteristics                        |

| Pin Configuration                                        |

| MAX11947                                                 |

| Pin Description                                          |

| Functional Diagrams                                      |

| Diagram 1                                                |

| Detailed Description                                     |

| 4:1 Multiplexer                                          |

| Internal Termination                                     |

| Receiver                                                 |

| Transmitter                                              |

| Carrier Tone                                             |

| Direction Output                                         |

| Serial Peripheral Interface (SPI)                        |

| Standby and Power-Down                                   |

| Port Scanning                                            |

| Status Bits                                              |

| Register Map                                             |

| Register Map                                             |

| Register Details                                         |

| Applications Information                                 |

| Emission Output Profile                                  |

| RF Filter and Selectivity                                |

| External Low-Pass Filter and AC-Coupling to Feeder Cable |

| In-Line Attenuation                                      |

| Crystal and External Clock                               |

| Dwell Time                                               |

| Alternate Modem Interface                                |

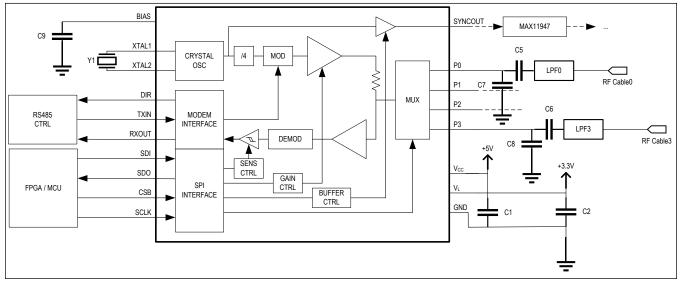

| Typical Application Circuit                              |

| Circuit 1                                                |

## TABLE OF CONTENTS (CONTINUED)

| Ordering Information | 44 |

|----------------------|----|

| Revision History     | 45 |

# 4 Channel AISG Integrated Modem

| Figure 1. SPI Timing                                               | 12 |

|--------------------------------------------------------------------|----|

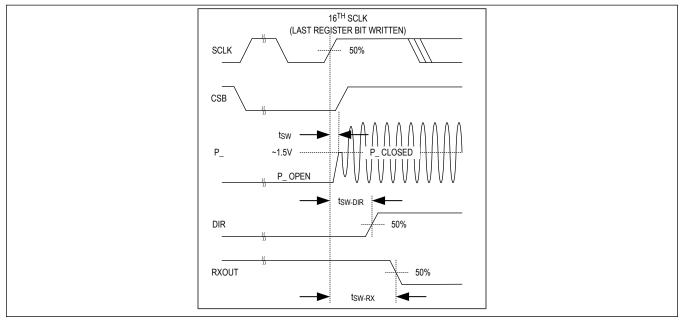

| Figure 2. MUX Port Diagram                                         | 18 |

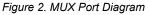

| Figure 3. Switch Timing                                            | 19 |

| Figure 4. RF Isolation                                             | 19 |

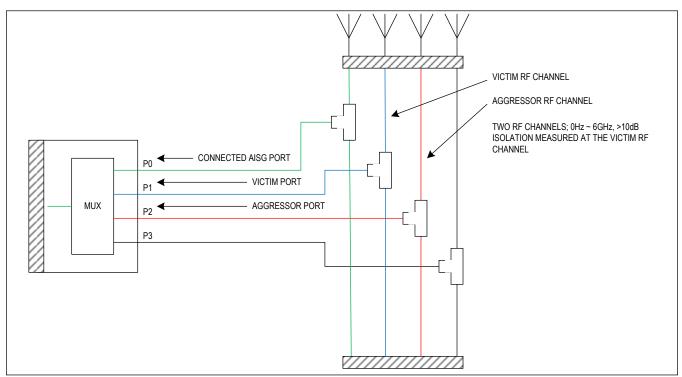

| Figure 5. AISG Isolation                                           | 20 |

| Figure 6. Modem Crosstalk                                          | 21 |

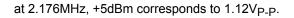

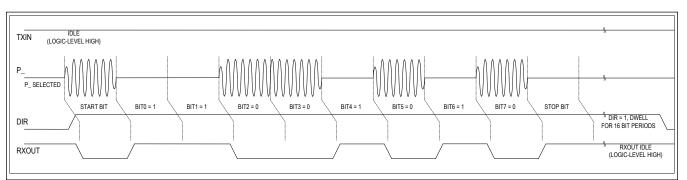

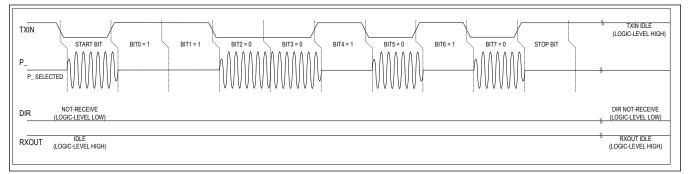

| Figure 7. Receiver Timing                                          | 22 |

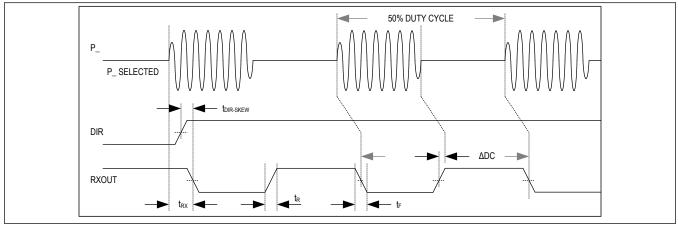

| Figure 8. Transmitter Timing                                       | 23 |

| Figure 9. Receiver Communication Flow                              | 24 |

| Figure 10. Transmitter Communication Flow                          | 24 |

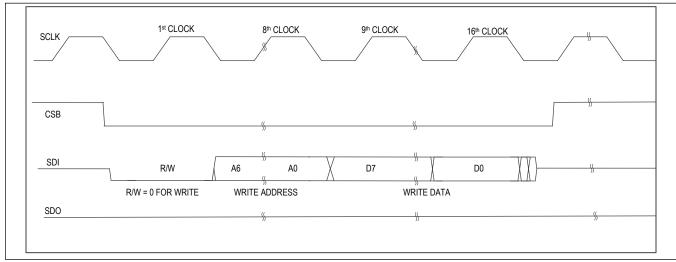

| Figure 11. SPI Write Transaction                                   | 25 |

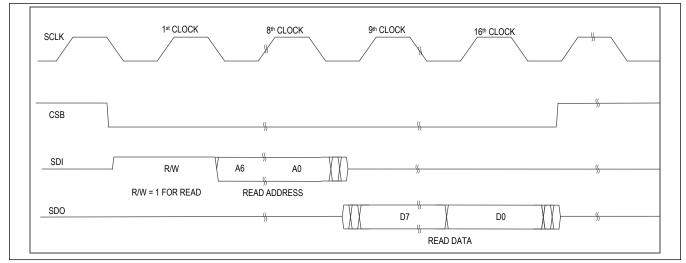

| Figure 12. SPI Read Transaction                                    | 25 |

| Figure 13. Power Modes                                             | 26 |

| Figure 14. Port Scan Flow Chart                                    | 28 |

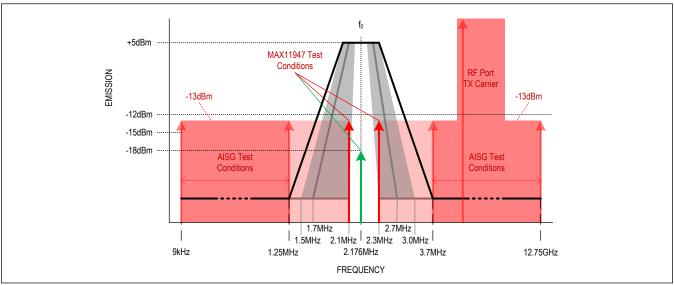

| Figure 15. AISG v3.0 Standard Modem Spectrum Emissions Mask        | 37 |

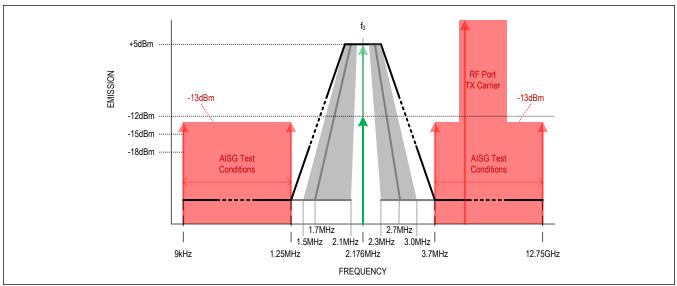

| Figure 16. AISG Selectivity No-ON Test Conditions                  | 38 |

| Figure 17. AISG Selectivity Forced-ON Test Conditions.             | 38 |

| Figure 18. AISG Selectivity No-OFF Test Conditions                 | 39 |

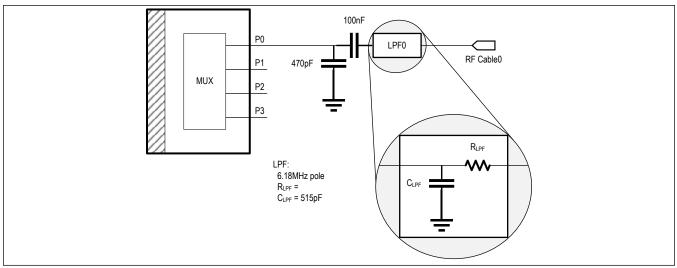

| Figure 19. RF Port Filter                                          | 39 |

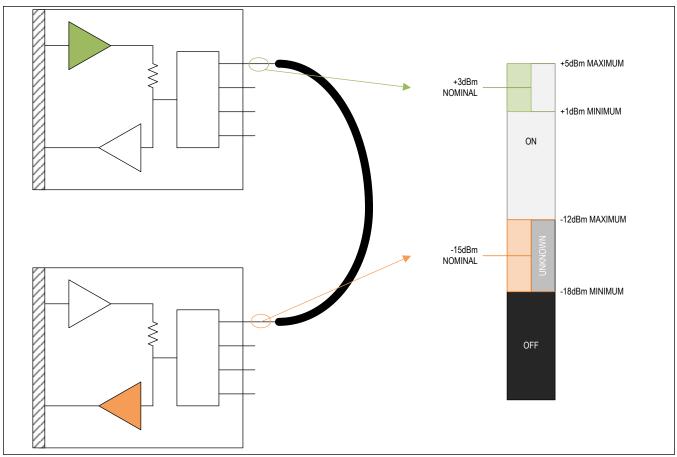

| Figure 20. Transmit and Receive Levels                             | 40 |

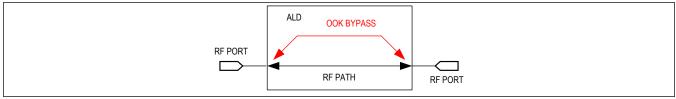

| Figure 21. AISG—OOK Bypass                                         | 40 |

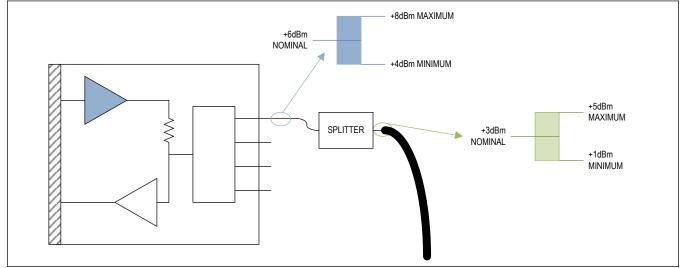

| Figure 22. Higher Power Transmitter for Splitter                   | 41 |

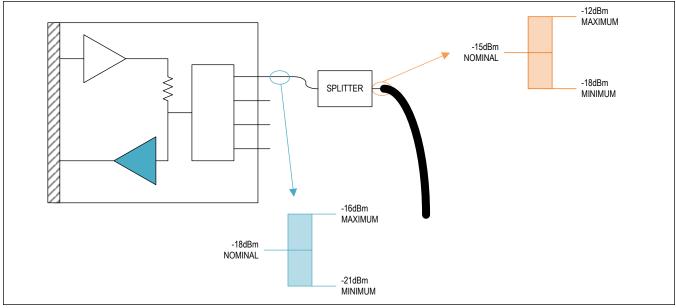

| Figure 23. Better Sensitivity Threshold for Receiver with Splitter | 41 |

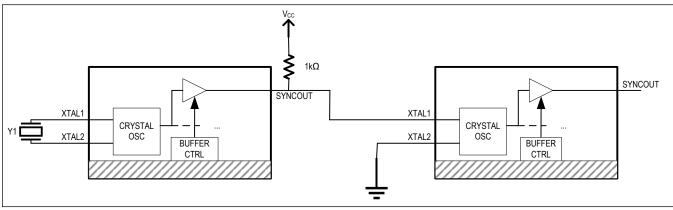

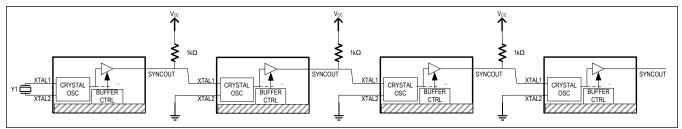

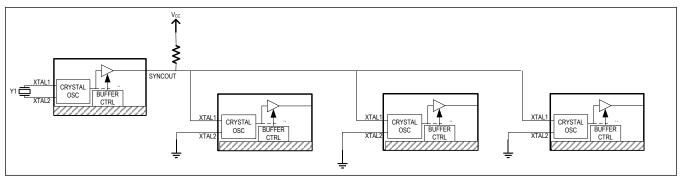

| Figure 24. Clock Master/Slave Circuit                              | 42 |

| Figure 25. Cascade Daisy-Chain                                     | 42 |

| Figure 26. Star Daisy-Chain                                        | 42 |

### LIST OF FIGURES

# 4 Channel AISG Integrated Modem

### LIST OF TABLES

| Table 1. RFPORT Register Settings   | 21 |

|-------------------------------------|----|

| Table 2. DATARATE Register Settings | 24 |

| Table 3. SPI Pins.                  | 25 |

| Table 4. SCAN_DWELL Time            | 28 |

| Table 5. User-Programmed Dwell Time | 29 |

| Table 6. Alternate Modem Interface  | 43 |

## 4 Channel AISG Integrated Modem

### **Absolute Maximum Ratings**

| $V_{CC}$ to GND                                             | All Other Pins Max In/Out Current $\pm 20$ mA<br>Continuous Power Dissipation (T <sub>A</sub> = +70°C) 20-pin TQFN (derate |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| P0, P1, P2, P3, XTAL1, XTAL2, BIAS, SYNCOUT to GND0.3V      | 30.2mW/°C)2415mW                                                                                                           |

| to +6V                                                      | Operating Temperature Range40°C to +105°C                                                                                  |

| TXIN, RXOUT, DIR, SDI, SDO, SCLK, CSB to GND -0.3V to (VL   | Junction Temperature+150°C                                                                                                 |

| +0.3)V                                                      | Storage Temperature Range65°C to +150°C                                                                                    |

| Output Short-Circuit Current P_ While Transmitting, SYNCOUT | Lead Temperature (soldering, 10s)+300°C                                                                                    |

| to V <sub>CC</sub> or GND Continuous                        | Soldering Temperature (reflow)+260°C                                                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Package Information

#### 20-Pin TQFN

| Package Code                            | T2044+4        |

|-----------------------------------------|----------------|

| Outline Number                          | <u>21-0139</u> |

| Land Pattern Number                     | <u>90-0429</u> |

| Thermal Resistance, Single-Layer Board: |                |

| Junction to Ambient ( $\theta_{JA}$ )   | 48°C/W         |

| Junction to Case ( $\theta_{JC}$ )      | 2°C/W          |

| Thermal Resistance, Four-Layer Board:   |                |

| Junction to Ambient ( $\theta_{JA}$ )   | 33°C/W         |

| Junction to Case ( $\theta_{JC}$ )      | 2°C/W          |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **Electrical Characteristics**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0x1, 1k\Omega$  resistor between SYNCOUT and  $V_{CC}$ , XTAL frequency 8.704MHz ±30ppm.  $T_A = -40^{\circ}C$  to +105°C, unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER            | SYMBOL                       | CONDITIONS                                                      |                                                 | MIN | TYP | MAX | UNITS |  |

|----------------------|------------------------------|-----------------------------------------------------------------|-------------------------------------------------|-----|-----|-----|-------|--|

| DC CHARACTERISTICS   |                              |                                                                 |                                                 |     |     |     |       |  |

| Supply Voltage       | V <sub>CC</sub>              | Guaranteed by P                                                 | SRR                                             | 3.0 |     | 5.5 | V     |  |

|                      | oply Current I <sub>CC</sub> |                                                                 | T <sub>A</sub> ≤ 85°C                           |     | 24  | 35  |       |  |

| Supply Current       |                              | $V_{TXIN} = 0V$ $T_A > 85^{\circ}C$ (typ measured at 85°C       | T <sub>A</sub> > 85°C (typ<br>measured at 85°C) |     | 26  | 37  | mA    |  |

| Logic Supply Voltage | VL                           | Guaranteed by logic supply current                              |                                                 | 1.6 |     | 5.5 | V     |  |

| Logic Supply Current | ١L                           | V <sub>TXIN</sub> = V <sub>L</sub> (logic                       | $V_{TXIN} = V_L$ (logic-high)                   |     | 236 | 380 | μA    |  |

| Standby Current      | I <sub>CC-SB</sub>           |                                                                 |                                                 |     | 13  | 20  | mA    |  |

| Standby Current      | I <sub>L-SB</sub>            | V <sub>TXIN</sub> = V <sub>L</sub> , STANDBY = 0x1              |                                                 |     | 236 | 380 | μA    |  |

| Power-Down Current   | I <sub>CC-PD</sub>           | V <sub>TXIN</sub> = V <sub>L</sub> , PWRDN = 0x1, XTALOSC = 0x0 |                                                 |     | 0.8 | 2   | mA    |  |

|                      | I <sub>L-PD</sub>            |                                                                 |                                                 |     | 60  | 120 | μA    |  |

### **Electrical Characteristics (continued)**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0x1, 1kΩ resistor between SYNCOUT and V<sub>CC</sub>, XTAL frequency 8.704MHz ±30ppm. T<sub>A</sub> = -40°C to +105°C, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)$

| PARAMETER                                    | SYMBOL                                           | COND                                                         | DITIONS                                                                    | MIN                      | TYP   | MAX                      | UNITS             |

|----------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------------------|

| Receiver Power-Supply<br>Rejection Ratio     | PSRR <sub>RX</sub>                               | $3.0V \le V_{CC} \le 5.5V,$                                  | V <sub>TXIN</sub> = V <sub>L</sub> (Note 2)                                |                          | 54    |                          | dB                |

| Transmitter Power-<br>Supply Rejection Ratio | PSRR <sub>TX</sub>                               | $3.0V \le V_{CC} \le 5.5V,$                                  | $3.0V \le V_{CC} \le 5.5V, V_{TXIN} = 0V (Note 3)$                         |                          | 42    |                          | dB                |

| LOGIC INPUTS (TXIN, SI                       | DI, CSB, SCLK)                                   |                                                              |                                                                            |                          |       |                          |                   |

| Logic-Input High<br>Threshold Voltage        | VIH                                              |                                                              |                                                                            | 0.7 x V <sub>L</sub>     |       |                          | V                 |

| Logic Input Low<br>Threshold Voltage         | VIL                                              |                                                              |                                                                            |                          |       | 0.3 x V <sub>L</sub>     | V                 |

| Input Leakage Current                        | I <sub>IH</sub> , I <sub>IL</sub>                | Shorted to GND or \                                          | /L                                                                         |                          |       | ±1                       | μA                |

| LOGIC OUTPUTS (RXOL                          | JT, SDO, DIR)                                    | •                                                            |                                                                            |                          |       |                          |                   |

| Logic-Output High Level Voltage              | V <sub>OH</sub>                                  | Sourcing 3.3mA                                               |                                                                            | 0.9 x V <sub>L</sub>     |       |                          | V                 |

| Logic-Output Low Level<br>Voltage            | V <sub>OL</sub>                                  | Sinking 3.3mA                                                |                                                                            |                          |       | 0.1 x V <sub>L</sub>     | V                 |

| SYNC INPUT (XTAL1) AI                        | ND OUTPUT (SY                                    | NCOUT)                                                       |                                                                            |                          |       |                          |                   |

| Input High Threshold<br>Voltage              | VIH-XTAL1                                        |                                                              |                                                                            | 0.7 x<br>V <sub>CC</sub> |       |                          | V                 |

| Input Low Threshold<br>Voltage               | V <sub>IL-XTAL1</sub>                            |                                                              |                                                                            |                          |       | 0.3 x<br>V <sub>CC</sub> | V                 |

| Input Leakage Current                        | I <sub>IH-XTAL1</sub> ,<br>I <sub>IL-XTAL1</sub> |                                                              |                                                                            |                          |       | ±10                      | μA                |

| Output Low Voltage                           | V <sub>OL-SYNCOUT</sub>                          | OSCBUF = 0x1, SY                                             | NCOUT sinking 5mA                                                          |                          |       | 0.4                      | V                 |

|                                              |                                                  |                                                              | OSCBUF = 0x0<br>(disabled),<br>SYNCOUT open                                | -1                       |       | +1                       | μA                |

| Output Low Current                           | I <sub>OL-SYNCOUT</sub>                          | V <sub>SYNCOUT</sub> = 0.0V                                  | OSCBUF = $0x1$<br>(default),<br>SYNCOUT $1k\Omega$<br>resistor to $V_{CC}$ |                          | 5     |                          |                   |

|                                              |                                                  | OSCBUF = 0x2,<br>SYNCOUT 500Ω<br>resistor to V <sub>CC</sub> |                                                                            | 10                       |       | mA                       |                   |

|                                              |                                                  |                                                              | OSCBUF = $0x3$ ,<br>SYNCOUT 250 $\Omega$<br>resistor to V <sub>CC</sub>    |                          | 20    |                          |                   |

| RECEIVER                                     |                                                  |                                                              |                                                                            |                          |       |                          |                   |

| Maximum Input Level                          | P <sub>IN</sub>                                  | V <sub>CC</sub> = 3.0V to 5.5V,                              | f <sub>IN</sub> = 2.176MHz                                                 | +5                       |       |                          | dBm               |

| Maximum input Level                          | V <sub>IN</sub>                                  | V <sub>CC</sub> = 3.0V to 5.5V,                              | f <sub>IN</sub> = 2.176MHz                                                 | 1.12                     |       |                          | V <sub>P-P</sub>  |

| AISG Threshold Window                        | P <sub>TH</sub>                                  | f <sub>IN</sub> = 2.176MHz, RX                               | SENS = 0xB (default)                                                       | -18                      | -15   | -12                      | dBm               |

|                                              | V <sub>TH</sub>                                  | (Note 12)                                                    |                                                                            | 79.6                     | 112.5 | 158.8                    | mV <sub>P-P</sub> |

### **Electrical Characteristics (continued)**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0x1, 1kΩ resistor between SYNCOUT and V<sub>CC</sub>, XTAL frequency 8.704MHz ±30ppm. T<sub>A</sub> = -40°C to +105°C, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)$

| PARAMETER                             | SYMBOL                                | COND                                                                                            | ITIONS                                        | MIN  | TYP                                                                                                                   | MAX   | UNITS            |

|---------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------|-------|------------------|

| Threshold Adjustment                  | D                                     | f <sub>IN</sub> = 2.176MHz, RX                                                                  | SENS ≥ 0xB                                    |      | -15                                                                                                                   |       | dDm              |

| Range                                 | P <sub>TH-ADJ</sub>                   | f <sub>IN</sub> = 2.176MHz, RXSENS = 0x0                                                        |                                               |      | -20.5                                                                                                                 |       | dBm              |

| Threshold Adjustment Resolution       | P <sub>TH-RES</sub>                   | Excluding codes ≥ 0                                                                             | xC                                            |      | 0.5                                                                                                                   |       | dB               |

| RECEIVER FILTER                       |                                       |                                                                                                 |                                               |      |                                                                                                                       |       |                  |

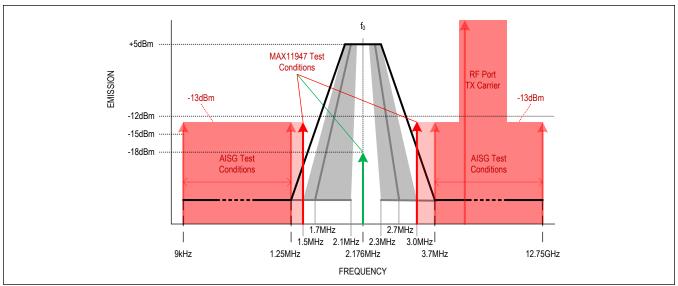

| Passband                              | f <sub>PB-L</sub> , f <sub>PB-H</sub> |                                                                                                 | IBm (the input carrier<br>ENS = 0xF (Note 13) | 1.25 |                                                                                                                       | 3.7   | MHz              |

|                                       | f <sub>IML</sub>                      |                                                                                                 | f <sub>IML</sub> = 9kHz to<br>1.5MHz          | 1.25 | 2.0                                                                                                                   |       |                  |

| Selectivity                           | fimh                                  | extra carrier<br>amplitude -13dBm,<br>DATARATE = 0x0<br>(9.6kbps),<br>RXSENS = 0xF<br>(Note 14) | f <sub>IMH</sub> = 3.0MHz to<br>10.0MHz       |      | 2.7                                                                                                                   | 3.7   | MHz              |

| TRANSMITTER                           |                                       |                                                                                                 |                                               |      |                                                                                                                       |       |                  |

| Output Frequency                      | fo                                    |                                                                                                 |                                               |      | 2.176                                                                                                                 |       | MHz              |

| Output Frequency<br>Variation         | Δf <sub>O</sub>                       | (Note 4)                                                                                        | (Note 4)                                      |      |                                                                                                                       | ±100  | ppm              |

|                                       | POUT                                  |                                                                                                 |                                               | +1.0 | +3.0                                                                                                                  | +5.0  | dBm              |

| AISG Output ON Level                  | V <sub>OUT</sub>                      |                                                                                                 | TXPWR = 0x7 (default) (Note 5)                |      | 0.893                                                                                                                 | 1.125 | V <sub>P-P</sub> |

| Output Power                          |                                       | TXPWR = 0xF (Note                                                                               | : 5)                                          |      | +7.0                                                                                                                  |       | dBm              |

| Adjustment Range                      | Pout-adj                              | TXPWR = 0x0 (Note                                                                               | 5)                                            |      | -0.5                                                                                                                  |       |                  |

| Output Power<br>Adjustment Resolution | POUT-RES                              | (Note 5)                                                                                        |                                               |      | 0.5                                                                                                                   |       | dB               |

| AISG Output OFF<br>Power              | Роит                                  | OOK off level (Note                                                                             | 5)                                            |      | -65                                                                                                                   | -40   | dBm              |

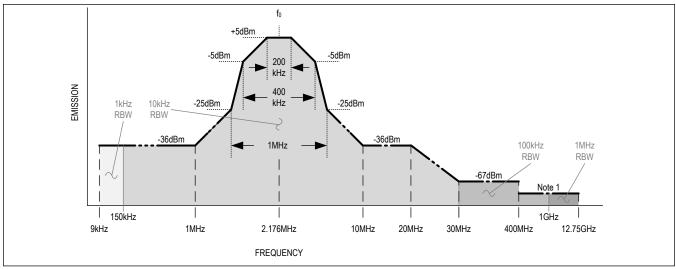

| AISG Output Emission<br>Profile       |                                       | (Note 6)                                                                                        |                                               |      | Conform<br>s to<br>AISG<br>v3.0<br>Spectru<br>m<br>Emission<br>s Mask<br>3GPP<br>TS<br>25.461,<br>See<br>Figure<br>15 |       |                  |

| Amplifier Gain<br>Bandwidth           | GBW                                   |                                                                                                 |                                               |      | 54                                                                                                                    |       | MHz              |

### **Electrical Characteristics (continued)**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0x1, 1kΩ resistor between SYNCOUT and V<sub>CC</sub>, XTAL frequency 8.704MHz ±30ppm. T<sub>A</sub> = -40°C to +105°C, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)$

| PARAMETER                                        | SYMBOL                          | COND                                                                                                | ITIONS                                                                       | MIN | TYP  | MAX  | UNITS |

|--------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|------|------|-------|

| RF Port Short-Circuit<br>Current                 | I <sub>SC</sub>                 | Short to GND or $V_{CC}$<br>V <sub>CC</sub> range, limited b                                        |                                                                              |     |      | ±100 | mA    |

| SWITCHING CHARACTE                               | RISTICS                         |                                                                                                     |                                                                              |     |      |      |       |

|                                                  |                                 |                                                                                                     | DATARATE = 0x0<br>(9.6kbps, default)                                         |     | 6.5  | 11   | μs    |

| Receiver Propagation<br>Delay                    | t <sub>RX</sub>                 | Selected RF Port<br>P_ to RXOUT                                                                     | DATARATE = 0x1<br>(38.4KBPS)                                                 |     | 3.1  | 11   |       |

|                                                  |                                 |                                                                                                     | DATARATE = 0x2<br>(115.2kbps)                                                |     | 3.1  | 11   | _     |

| Receiver Output Rise<br>and Fall Time            | t <sub>R</sub> , t <sub>F</sub> | 10% to 90%, R <sub>L</sub> = 1                                                                      | «Ω, C <sub>L</sub> = 10ρF                                                    |     | 20   |      | ns    |

| Transmitter Propagation Delay                    | t <sub>TX</sub>                 | TXIN to selected RF                                                                                 | port P_                                                                      |     | 1.8  | 5    | μs    |

| DIR to RXOUT Delay<br>(Note 7)                   | t <sub>DIR-SKEW</sub>           |                                                                                                     |                                                                              | 270 | 345  |      | ns    |

|                                                  |                                 | DATARATE = 0x0 (9.6kbps, default)                                                                   |                                                                              |     | 1667 |      |       |

| DIR Dwell Time                                   | <sup>t</sup> DWELL              | DATARATE = 0x1 (3                                                                                   | 38.4kbps)                                                                    |     | 417  |      | μs    |

|                                                  |                                 | DATARATE = 0x2 (1                                                                                   | 15.2kbps)                                                                    |     | 137  |      |       |

|                                                  |                                 | P_ fed by an OOK                                                                                    | P_ = 0dBm                                                                    |     | -7.5 | ±10  | %     |

| Receiver Output Data<br>Duty-Cycle Variation ΔDC | 400                             | 2.176MHz<br>sinusoidal signal<br>with 50% duty<br>cycle (Note 8)                                    | P_ = -10dBm                                                                  |     | +2   | ±10  |       |

|                                                  | ADC                             |                                                                                                     | DATARATE = 0x2<br>(115.2kbps)                                                |     | +11  | ±15  |       |

| RF PORT MUX                                      |                                 |                                                                                                     | 1 1                                                                          |     |      |      | 1     |

| Input Impedance                                  | Z <sub>IN</sub>                 | f = 2.176MHz                                                                                        |                                                                              |     | 50   |      | Ω     |

| Return Loss                                      | S <sub>11</sub>                 | f = 2.176MHz, with a                                                                                | 470pF capacitor                                                              |     | 16   |      | dB    |

| RF Port Isolation                                | S <sub>RFVA</sub>               |                                                                                                     | <sub>V</sub> measured at victim<br>P <sub>A</sub> = +10dBm, f <sub>A</sub> = |     | -45  |      | dBc   |

| AISG Port Isolation                              | S <sub>MVA</sub>                | Scatter parameter P<br>port, aggressor port<br>2.176MHz                                             | V measured at victim<br>$P_A = +5dBm, f_A =$                                 |     | -60  |      | dBc   |

| Modem Crosstalk                                  | XTLK <sub>RX</sub>              | Aggressor port $P_A$ = +5dBm, $f_A$ =<br>2.176MHz, Victim port RXSENS = 0x0<br>(-20.5dBm) (Note 11) |                                                                              |     | -42  |      | dBc   |

|                                                  | XTLK <sub>TX</sub>              | TXPWR = 0xF (+7dBm) (Note 11)                                                                       |                                                                              |     | -65  |      | 1     |

| Switch Time                                      | t <sub>SW</sub>                 | Carrier $P_0$ = +3dBm, f <sub>0</sub> = 2.176MHz<br>(Note 10)                                       |                                                                              |     | 345  |      | ns    |

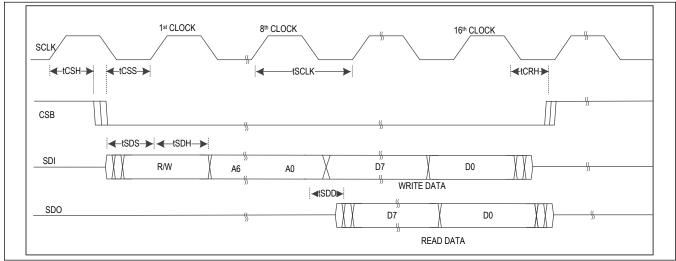

| SERIAL INTERFACE (Fig                            | <u>ure 1)</u>                   |                                                                                                     | I                                                                            |     |      |      |       |

|                                                  | f.,                             | 1/t <sub>SCLK</sub> , sensitive                                                                     | V <sub>L</sub> = ≥ 2.0V                                                      |     | 20   | 10   | N/11- |

| SCLK Frequency                                   | <b>f</b> SCLK                   | to VL                                                                                               |                                                                              |     | 8    | 5    | MHz   |

### **Electrical Characteristics (continued)**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0x1, 1k\Omega resistor between SYNCOUT and V<sub>CC</sub>, XTAL frequency 8.704MHz ±30ppm. T<sub>A</sub> = -40°C to +105°C, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)$

| PARAMETER                         | SYMBOL               |                      | CONDITIONS                    | MIN                  | TYP                  | MAX                  | UNITS                |          |          |                      |                      |           |                            |  |     |  |    |

|-----------------------------------|----------------------|----------------------|-------------------------------|----------------------|----------------------|----------------------|----------------------|----------|----------|----------------------|----------------------|-----------|----------------------------|--|-----|--|----|

| SCLK to CSB Setup<br>Time         | tcss                 |                      |                               |                      | 20                   |                      | ns                   |          |          |                      |                      |           |                            |  |     |  |    |

| SCLK to CSB Hold Time             | t <sub>CSH</sub>     |                      |                               |                      | 0                    |                      | ns                   |          |          |                      |                      |           |                            |  |     |  |    |

| SDI to SCLK Hold Time             | <sup>t</sup> SDH     | Data-write           |                               |                      | 0                    |                      | ns                   |          |          |                      |                      |           |                            |  |     |  |    |

| SDI to SCLK Setup<br>Time         | t <sub>SDS</sub>     | Data-write           |                               |                      | 20                   |                      | ns                   |          |          |                      |                      |           |                            |  |     |  |    |

| Minimum SCLK to SDO               | <b>4</b>             | Data-read            | 10pF load from<br>SDO to GND  |                      | 1.5                  |                      | 20                   |          |          |                      |                      |           |                            |  |     |  |    |

| Data Delay                        | 'SDD-MIN             | <sup>I</sup> SDD-MIN | 'SDD-MIN                      | <sup>i</sup> SDD-MIN | <sup>I</sup> SDD-MIN | <sup>I</sup> SDD-MIN | <sup>I</sup> SDD-MIN | 'SDD-MIN | 'SDD-MIN | <sup>I</sup> SDD-MIN | <sup>t</sup> SDD-MIN | Data-read | 100pF load from SDO to GND |  | 3.5 |  | ns |

| Maximum SCLK to SDO<br>Data Delay | mum SCLK to SDO      | Data-read            | 10pF load from<br>SDO to GND  |                      | 8                    |                      | 20                   |          |          |                      |                      |           |                            |  |     |  |    |

|                                   | <sup>t</sup> SDD-MAX | Data-read            | 100pF load from<br>SDO to GND |                      | 11                   |                      | ns                   |          |          |                      |                      |           |                            |  |     |  |    |

**Note 1:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Specification over temperature limits are guaranteed by design.

**Note 2:** Defined as  $20 \cdot \log(\Delta V_{CC}/\Delta V_{TH})$ .

**Note 3:** Defined as  $20 \cdot \log(\Delta V_{CC}/\Delta V_{OUT})$ , this value is impacted by the internal resistor voltage and temperature coefficient.

Note 4: Output frequency variation determined by external crystal tolerance. Not production tested, guaranteed by design and characterization.

Note 5: Measured at selected RF port, P\_. See Output Power Control in the <u>Transmitter</u> section for power setting details.

Note 6: Guaranteed by design, with a recommended 470pF capacitor between the RF port (P\_) and ground. Results above 150MHz are influenced by setup.

Note 7: See Figure 7.

Note 8: ±2µs envelope rise/fall.

Note 9: Excludes external LPF on the input of the aggressor port, see the *External Lowpass Filter and AC-Coupling to Feeder Cable* section.

Note 10: Switch time is defined from the rising edge of 16th SCLK during a change to the RFPORT register to the settled DC bias on the selected RF port. See Figure 3.

Note 11: Receive modem crosstalk is measured with the most sensitive (lowest dBm level) setting and a high-power aggressor signal applied to any unselected port. Transmit modem crosstalk is measured with a power meter connected to any unselected port with the transmitter set to the highest power level and the TX\_ON bit set to 1 in the CFG register (0x00).

Note 12: AISG specifies an input power window with defined thresholds: above -12dBm is a recognized ON state, below -18dBm is a recognized OFF state (-15dBm ±3dB), in between signal power levels are undefined. The MAX11947 nominal threshold is -15dBm.

Note 13: A tighter receiver filter passband provides better receiver performance and improved extra carrier rejection (selectivity) outside of that band. The device meets AISG v3.0.0.10 section 10.3.12.1 Device Selectivity requirements with a typical passband of 2.0MHz to 2.7MHz where AISG requires 1.25MHz to 3.7MHz. See the <u>*RF Filter and Selectivity*</u> section for more information.

# 4 Channel AISG Integrated Modem

Figure 1. SPI Timing

## 4 Channel AISG Integrated Modem

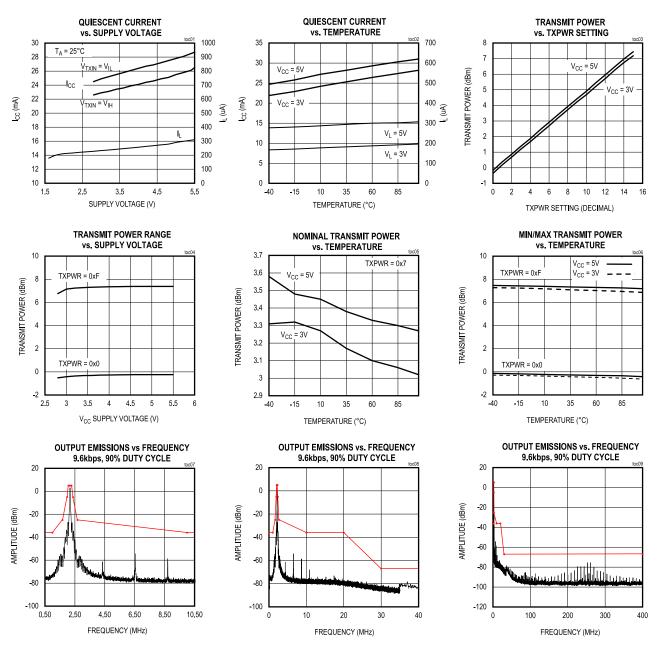

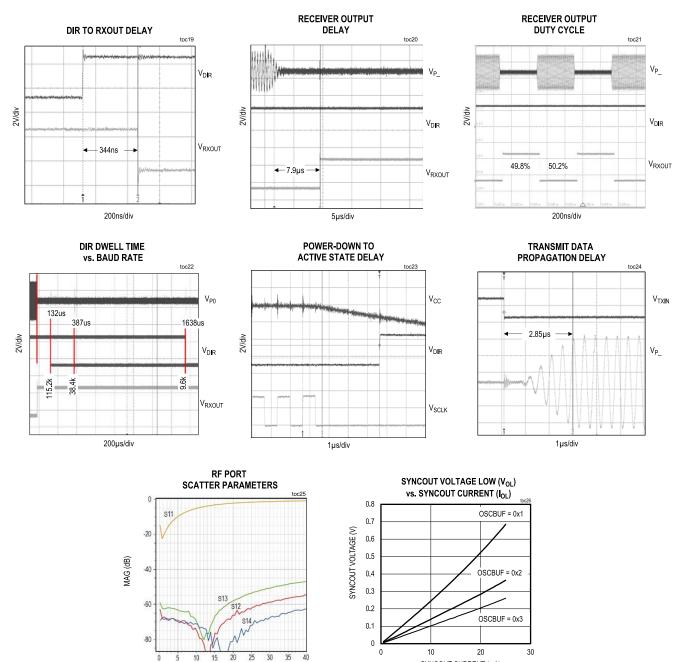

### **Typical Operating Characteristics**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0.0, pullup on SYNCOUT with 1k\Omega to V<sub>L</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise specified.)$

### 4 Channel AISG Integrated Modem

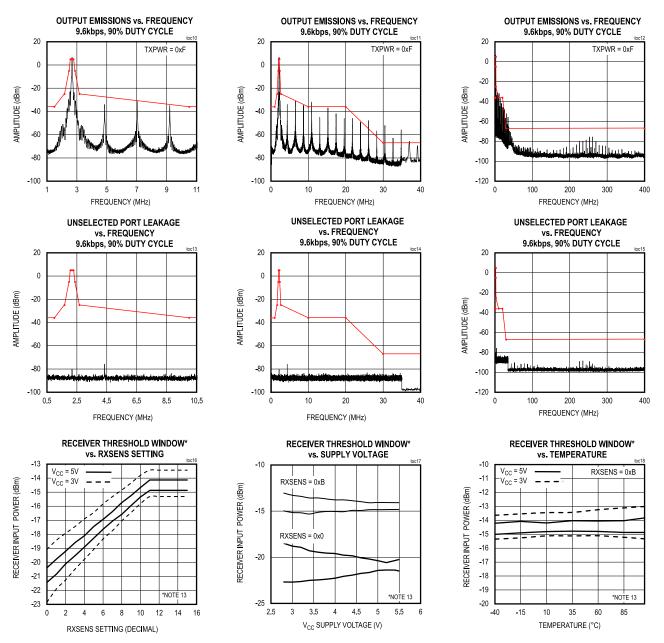

### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 5V, V<sub>L</sub> = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0.0, pullup on SYNCOUT with 1k $\Omega$  to V<sub>L</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise specified.)

# 4 Channel AISG Integrated Modem

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, V_L = 3.3V, TXPWR = 0x7 (+3dBm), RXSENS = 0xB (-15dBm), DATARATE = 0x0 (9.6kbps), OSCBUF = 0.0, pullup on SYNCOUT with 1k\Omega to V_L, T_A = T_{MIN}$  to T<sub>MAX</sub>, unless otherwise specified.)

SYNCOUT CURRENT (mA)

FREQUENCY (MHz)

# 4 Channel AISG Integrated Modem

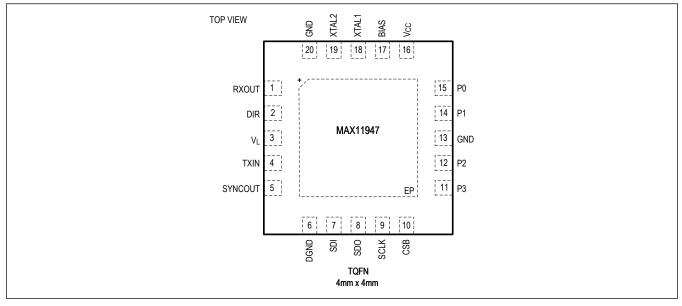

# **Pin Configuration**

#### MAX11947

## **Pin Description**

| PIN | NAME            | IE FUNCTION                                                                          |                 |  |  |  |

|-----|-----------------|--------------------------------------------------------------------------------------|-----------------|--|--|--|

| 1   | RXOUT           | Modem Rx Digital Signal Output                                                       | VL              |  |  |  |

| 2   | DIR             | Direction Output. DIR is asserted high when the data stream is seen at the receiver. | VL              |  |  |  |

| 3   | VL              | Logic Supply Voltage                                                                 |                 |  |  |  |

| 4   | TXIN            | Modem Tx Digital Signal Input                                                        | VL              |  |  |  |

| 5   | SYNCOUT         | Sync Output. Open-drain output of the 8.704MHz clock to synchronize other devices.   | Pullup          |  |  |  |

| 6   | DGND            | Ground                                                                               |                 |  |  |  |

| 7   | SDI             | SPI Bus Serial Data Input                                                            | VL              |  |  |  |

| 8   | SDO             | SPI Bus Serial Data Output                                                           | VL              |  |  |  |

| 9   | SCLK            | SPI Bus Serial Clock Input                                                           | VL              |  |  |  |

| 10  | CSB             | Active-Low, SPI Bus Chip Enable                                                      | VL              |  |  |  |

| 11  | P3              | RF MUX Port 3                                                                        | V <sub>CC</sub> |  |  |  |

| 12  | P2              | RF MUX Port 2                                                                        | V <sub>CC</sub> |  |  |  |

| 13  | GND             | Ground                                                                               |                 |  |  |  |

| 14  | P1              | RF MUX Port 1                                                                        | V <sub>CC</sub> |  |  |  |

| 15  | P0              | RF MUX Port 0                                                                        | V <sub>CC</sub> |  |  |  |

| 16  | V <sub>CC</sub> | Analog Supply Voltage                                                                |                 |  |  |  |

| 17  | BIAS            | Output Bias Reference. Decouple BIAS with 1µF to GND.                                | VCC             |  |  |  |

# 4 Channel AISG Integrated Modem

## **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                               |                 |  |  |

|-----|-------|--------------------------------------------------------------------------------------------------------|-----------------|--|--|

| 18  | XTAL1 | External Crystal Input Terminal. Feed with 8.704MHz (±30ppm) input clock for external synchronization. | V <sub>CC</sub> |  |  |

| 19  | XTAL2 | External Crystal Input Terminal. Connect to GND for external synchronization.                          | V <sub>CC</sub> |  |  |

|     | EP    | Exposed Pad. Must be left open or connected to GND.                                                    |                 |  |  |

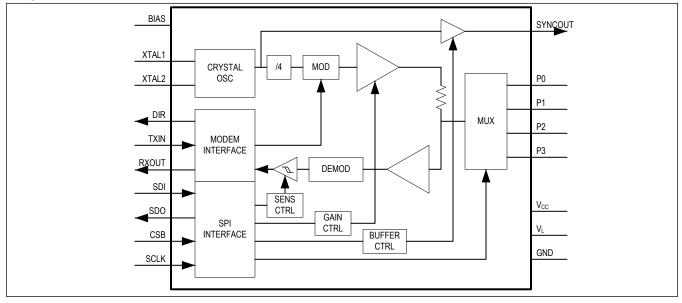

### **Functional Diagrams**

### Diagram 1

### **Detailed Description**

The MAX11947 is an AISG v2.0 and v3.0-compliant, fully integrated modem with a 4:1 multiplexer facilitating connectivity between a single modem and up to four RF ports.

The MAX11947 receiver includes a narrow 200kHz bandwidth bandpass filter centered at the 2.176MHz carrier frequency. It also includes an OOK demodulator and a comparator that reconstructs the digital signal. The typical sensitivity threshold of the receiver is -15dBm (when set to the default value 0xB), in compliance with the AISG standard specifications. This threshold is adjustable through an internal register setting (RXSENS) from a -20.5dBm to -15dBm level.

The MAX11947 transmitter includes an OOK modulator, a bandpass filter that is compliant with the AISG spectral emission profile, and an output amplifier. The output power can be varied with an internal register setting (TXPWR) from under 0dBm to over +6dBm (measured at the MUX-selected RF port) to compensate for loss in the external circuitry and cabling. The OOK carrier is generated from an external crystal at 8.704MHz connected to the XTAL1 and XTAL2 pins. An external clock source at the same frequency can also be applied to XTAL1 from the SYNCOUT pin of another MAX11947.

The MAX11947 also features a DIR output to facilitate the RS-485 bus arbitration in tower-mounted equipment.

#### 4:1 Multiplexer

The integrated 4:1 multiplexer allows the AISG system designer to connect a single modem to as many as four RF ports, simplifying implementation of a multi-primary or ALD PING-capable design. The MUX uses a CMOS analog switch architecture to provide a bidirectional signal, switchable between one common internal modem port and the four RF ports.

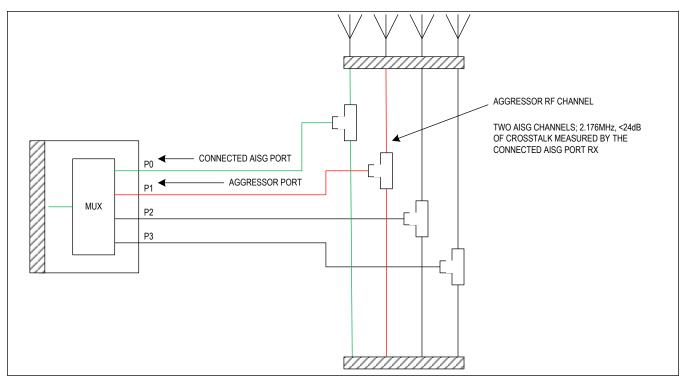

The 4:1 MUX provides both isolation and minimal crosstalk, allowing all four ports to be connected to a single modem without impacting the connected RF channels. To address the MUX performance, the port separation is characterized by three forms of isolation or crosstalk, which are primarily related to the frequencies involved: RF isolation, AISG isolation, and modem crosstalk.

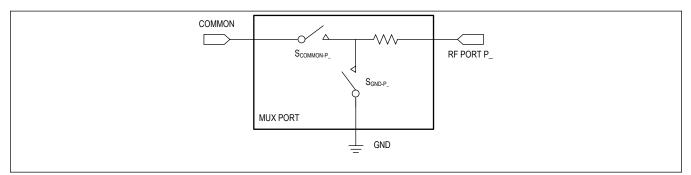

<u>Figure 2</u> shows a simplified block diagram of a single MUX RF port. A 50Ω series resistor is integrated into each RF port and the MUX common node is internally biased to approximately 1.5V DC.

The 4:1 MUX can be configured to either have all of the P\_ RF ports internally terminated and the common node not connected, or any single P\_ RF port can be connected to the MUX common node. All switch changes occur in a break-before-make sequence. When an RF port is not connected to the MUX common node, that P\_ port is internally terminated through the 50 $\Omega$  resistor to ground. When a port is selected, any previous selected port is terminated to GND prior to the new port connection being made. The process of connecting a P\_ RF port to the common port is measured by the t<sub>SW</sub> time. This switching time is measured by monitoring the CSB and SCLK signals of the SPI interface and the DC level on the RF port. The time starts when the port change message is programmed into the RFPORT [1:0] bits in the MUX (0x1) register and is triggered by the 16th SCLK rising edge (last register bit is written). The switch time ends when a 1.5V DC bias level is measured on the selected RF port. It should be noted that this timing can vary due to delays with transitioning

# 4 Channel AISG Integrated Modem

between the SPI clock domain and the internal operational clock domain. Figure 3 shows how the MUX switch time is measured from the 16th SCLK transition to the measured 1.5V DC bias on the RF port ( $t_{SW}$ ), to the DIR output transition ( $t_{SW-DIR}$ ), and to the first RXOUT bit ( $t_{SW-RX}$ ).

Figure 3. Switch Timing

Figure 4. RF Isolation

### 4 Channel AISG Integrated Modem

#### **RF** Isolation

The first form of separation to address is radio frequency signal isolation between RF ports. The primary implementation of the MAX11947 in a cellular tower application would have multiple RF frequencies in the cellular bands connected to separate ports on the 4:1 MUX. RF isolation describes how much of a high-frequency (cellular) signal on one RF port is detectable on another RF port. In Figure 4, an aggressor signal is applied to the coax cable tap of the P2 channel and the coax cable tap of P1 is measured for any impact on the victim channel. A majority of this isolation is provided by the lowpass filters on the P2 and P1 connections (LPF2 and LPF1, respectively).

#### **AISG** Isolation

The next form of separation to address is AISG carrier signal isolation between RF ports. Implementation of AISG v3.0 allows for the possibility of each RF port to carry either a multi-primary AISG signal or a PING signal. AISG isolation describes how much a 2.176MHz carrier signal on one RF port is detectable on another RF port. In <u>Figure 5</u>, an aggressor AISG signal is applied to the coax cable tap of the P2 channel and the coax cable tap of P1 is measured for any impact on the victim channel. A majority of this isolation is provided by 4:1 MUX switch within the MAX11947.

Figure 5. AISG Isolation

#### Modem Crosstalk

The last form of separation to address is modem crosstalk between RF ports. Again, implementation of AISG v3.0 allows for the possibility of each RF port to carry either a multi-primary AISG signal or a PING signal. Modem crosstalk describes how much a modulated AISG signal on a nonselected RF port is detectable by the MAX11947's internal receiver while connected to a different, selected RF port. In Figure 6, an aggressor AISG signal is applied to the coax cable tap of the P1 channel and the 4:1 MUX is connected to the P0 RF port. The aggressor signal is set to the maximum allowed power of +5dBm and the receiver threshold is set to the minimum programmed level of 0x0 (about -20.5dBm) and is monitored for any indication of a detected signal on the DIR or RXOUT pins. A majority of this isolation is provided by 4:1 MUX switch within the MAX11947.

### 4 Channel AISG Integrated Modem

Figure 6. Modem Crosstalk

#### **Register Programming**

The multiplexer is programmed through two register settings. In the MUX register (address 0x01), the OPEN bit internally disconnects the modem from the common port of the MUX, and the default condition (0x0) connects. In the same MUX register, the two RFPORT bits are used to select which external RF port the common port is connected to.

#### Table 1. RFPORT Register Settings

| RFPORT VALUE | COMMON CONNECTION    |

|--------------|----------------------|

| 0x0          | Connected to port P0 |

| 0x1          | Connected to port P1 |

| 0x2          | Connected to port P2 |

| 0x3          | Connected to port P3 |

#### **Internal Termination**

The MAX11947 modem works in conjunction with a 4:1 multiplexer and an internal 50 $\Omega$  termination. The termination is connected serially between the internal PA and the common MUX port. This resistor acts as series source for the transmit path (data flowing from TXIN to the selected RF port) and acts as parallel termination when data is being received on the internal receive path. The output of the transmitter is biased at 1.5V to maximize the power-supply rejection ratio and minimize any spurious emissions. It is recommended that the device be AC-coupled to the feeder cable through either an external RF filter or a series 100nF capacitor.

#### Receiver

The modem receiver consists of an LNA, a demodulator, and a sensitivity threshold adjustment system to convert the 2.176MHz OOK modulated signal into a digital output at RXOUT.

The maximum OOK input power at the internal LNA into the 50Ω internal termination is +5dBm. For a single-tone signal

Figure 7. Receiver Timing

#### Input Range and Sensitivity Threshold Control

The MAX11947 internal threshold is set to -15dBm (112.5mV<sub>P-P</sub>) by default (RXSENS set to 0xB). This centers the receive sensitivity threshold in the -12dBm to -18dBm undefined window specified by the AISG standard. This threshold sets the minimum input signal power recognized as an OOK ON carrier (asserting DIR level, logic-high and setting the RXOUT bit, logic-low).

Consider a corner case where the OOK signal at 2.176MHz present at the selected RF port, is at the minimum power of -15dBm ±3dB. To avoid saturation of the receiver input stage, any other adjacent carrier with power up-to +5dBm must be at a frequency below 1.25MHz or above 3.7MHz.

Referencing section 10.3.13 of the AISG v3.0 specification, ALD system designers are permitted to include splitters and/ or combiners with an insertion loss of 4.5dB for a two-way split or as much as 6.3dB for a three-way split. With an outgoing transmission the MAX11947's adjustable transmitter power allows the designer to increase the modem output up to over +6dBm, which would result in an effective level of +1.7dBm or more after a two-way split (falling within the +3dBm ±2dB window). Similarly, an incoming transmission with a maximum signal power of +5dBm would have no issues being decoded at the modem receiver. However, the potentially minimum receive power of -12dBm may not be properly decoded after the 4.5dB splitter attenuation. The adjustable threshold of the MAX11947 allows the AISG designer to move the target from -15dBm to as low as -20.5dBm, effectively allowing a drop of 5.5dB which can accommodate the 4.5dB attenuation from a two-way splitter. See the <u>In-Line Attenuation</u> section for additional information.

The MAX11947 receiver sensitivity threshold can be varied with an internal register setting (RXSENS) from a default level of -15dBm down to -20.5dBm in about 0.5dB steps. To obtain the nominal sensitivity threshold of -15dBm at the RF port as the AISG standard requires, set RXSENS to 0xB (default value). For additional setting values and their equivalent threshold, see the <u>RXTX</u> register details.

#### Transmitter

The modem transmitter consists of a local oscillator (LO) circuit, an on-off-keyed (OOK) modulator, and an adjustable power amplifier (PA).

### 4 Channel AISG Integrated Modem

Figure 8. Transmitter Timing

#### **Output Power Control**

The MAX11947 output power can be varied with an internal register setting (TXPWR) from < 0dBm to over +6dBm (measured at the MUX selected RF port: P0, P1, P2, or P3) to compensate for loss in the external circuitry and cabling. The maximum voltage available at the MUX selected RF port is about  $1.29V_{P-P}$ . Assuming that the feeder cable is terminated into a 50 $\Omega$  impedance, the external filter is lossless at 2.176MHz, where a series 50 $\Omega$  termination is being used internally, the output level of  $1.29V_{P-P}$  corresponds to +6.2dBm at the feeder cable. See the *External Low-Pass Filter and AC-Coupling to Feeder Cable* section for more details.

The P\_ voltage level can be varied according to the following equation:

P<sub>OUT</sub> (at P\_ in dBm) = TXPWR (decimal) x 0.5 (dB) - 0.5dBm

The output power has a soft ceiling around +6.0dBm at code 0x0D and rolls off the 0.5dB per code rate with the last two settings of 0x0E and 0x0F. The maximum PA output power is governed by the  $V_{CC}$  supply and when using 5.0V the MAX11947 can likely achieve transmitter output power levels up to +7.0dBm.

To obtain the nominal power level of +3dBm at the feeder cable as the AISG standard requires, set TXPWR to 0x7 (default value), which provides about  $0.89V_{P-P}$  at the MUX selected RF port P\_.

#### **Carrier Tone**

For a diagnostic tool, the transmitter can be held in a constant transmit mode by setting an internal register bit. By setting the TX\_ON bit to a 1 value in the CFG (0x00) register, the transmitter sends a 2.176MHz carrier without a need to send a data stream through the TXIN pin. This bit is used for various production test and can be used on an AISG system to generate a carrier tone on the RF port selected with the MUX.

#### **Direction Output**

The MAX11947 provides a direction output pin (DIR) that indicates the direction of the data flow. This feature is very useful in the tower that acts as a slave in the AISG protocol. In most applications the base is the master and it controls the flow of data by performing bus arbitration. The output DIR allows the equipment in the tower to avoid any involvement in the bus arbitration. The <u>Typical Application Circuit</u> shows how the MAX11947 can be used in the tower in conjunction with the RS-485 transceiver such as the MAX13485E or MAX13486E.

Typically, the DIR output drives the DE (driver output enable) and RE\_ (receiver output enable) of the RS-485 transceiver.

Whenever the data flows from the selected RF port (P0, P1, P2, or P3) to RXOUT, the DIR output is asserted high. When the MAX11947 is located in the tower, the data flow is being sent from the base (master) to the tower (slave). On the

### 4 Channel AISG Integrated Modem

other side, when the data flows in the opposite direction, from TXIN to the selected RF port, the DIR output is deasserted low. However, the MAX11947 internal state machine is sensing both the TXIN and the status of the internal LNA, it can recognize the correct flow of data and avoid asserting the DIR high.

<u>Figure 9</u> and <u>Figure 10</u> show the timing diagrams of the DIR functionality. When the data flows from the selected RF port to RXOUT, DIR remains high for 16 bit times after the last logic-level low bit within the 8-bit protocol data (DIR dwell time). This is compliant with the AISG specification saying that the RS-485 transmitter stops driving the bus within 20 bit-times after the last stop bit is sent.

The DATARATE register value defines the duration of the bit time, as shown in Table 2.

| DATARATE<br>VALUE | DATA RATE<br>(kbps) | BIT TIME<br>(µs) | DIR DWELL<br>TIME (ms) |

|-------------------|---------------------|------------------|------------------------|

| 0x0 (default)     | 9.6                 | 104.16           | 1.667                  |

| 0x1               | 38.4                | 26.04            | 0.416                  |

| 0x2               | 115.2               | 8.68             | 0.139                  |

| 0x3               | N/A                 | N/A              | N/A                    |

### Table 2. DATARATE Register Settings

Figure 9. Receiver Communication Flow

Figure 10. Transmitter Communication Flow

#### Serial Peripheral Interface (SPI)

The MAX11947 utilizes a 4-wire SPI protocol for programming its registers, configuring and controlling the operation of the modem. The register contents can be read back through the SDO pin. The digital I/Os in <u>Table 3</u>. control the operation of the SPI.

## 4 Channel AISG Integrated Modem

#### **Table 3. SPI Pins**

| PIN  | DIRECTION | DESCRIPTION               |

|------|-----------|---------------------------|

| SCLK | Input     | Serial Clock              |

| SDI  | Input     | Serial Data Input (MOSI)  |

| CSB  | Input     | Chip-Select Bar           |

| SDO  | Output    | Serial Data Output (MISO) |

Figure 11 shows a general SPI write transaction. Figure 12 show the format of a SPI read transaction. As shown in the diagrams, the R/W bit is set to 0 for a write transaction and the R/W bit is set to 1 for a read transaction.

Figure 11. SPI Write Transaction

Figure 12. SPI Read Transaction

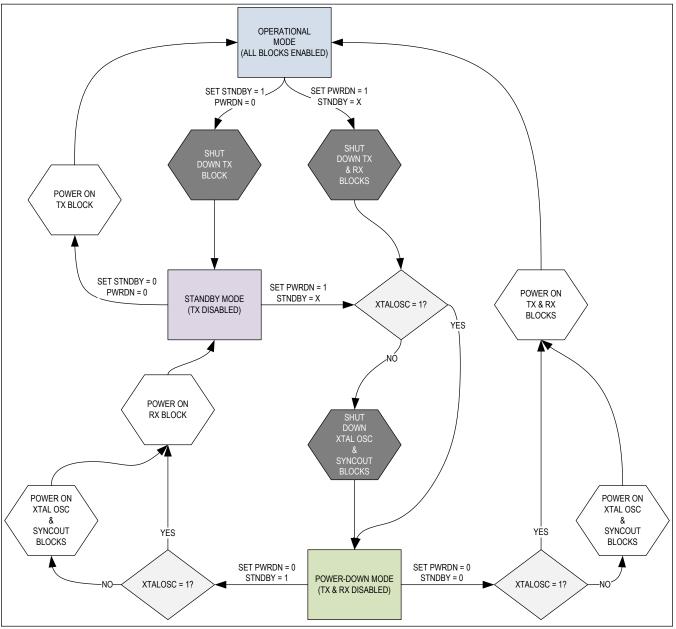

#### Standby and Power-Down Operational Modes

The MAX11947 has three modes of operation that include two power-saving modes. Each power-saving mode shuts

## 4 Channel AISG Integrated Modem

down various internal blocks to save on current and reduce the overall power consumption of the modem. The SPI interface always remains operational, and the internal register values are always retained as long as the  $V_{CC}$  and  $V_L$  supplies remain within specified voltage limits.

Figure 13. Power Modes

#### Standby Mode

Setting the STANDBY bit in the CFG (0x00) register places the modem in standby mode. This configuration shuts down the transmitter signal chain including the TXIN interface, the modulator, the power amplifier, and all associated filtering blocks. While in the STANDBY state, the modem consumes less power and thus has a lower supply current. All other modem functions, including the receiver signal chain (RXOUT) and the DIR signal, continue to operate normally.

#### Power-Down Mode

Setting the PWRDN bit in the CFG (0x00) register places the MAX11947 modem into power-down mode. This configuration shuts down the transmitter signal chain as well as the receiver signal chain including the LNA, the demodulator, the RXOUT interface, and the DIR system.

Depending on the state of the XTALOSC bit in the CFG (0x00) register, the power-down mode maintains the crystal oscillator and SYNCOUT operation or shuts down those blocks as well. By default, the XTALOSC bit is set to 1 and the 8.704MHz system remains operational for cascaded master/slave clocking. See the <u>Crystal and External Clock</u> section. If the XTALOSC bit is set to 0 prior to or during the same write command as the PWRDN bit, the crystal oscillator and SYNCOUT blocks are also shut down while in power-down mode.

While in the PWRDN state, the modem consumes minimal power yet still retains values programmed in the registers and keeps the SPI interface operational for further programming and mode selection.

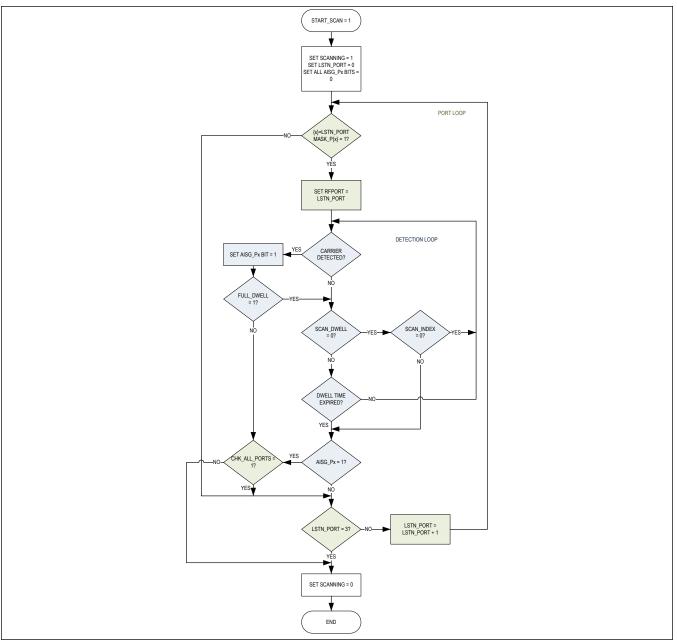

#### Port Scanning

The SCAN (0x02) register bits are used to configure the port scanning feature of the MAX11947. This state machine allows the modem to automatically listen for a carrier tone and/or the ping message on any of the RF ports sequentially. By setting the MASK\_Px bits to 1 or 0, the individual RF ports can be included or excluded from the scan sequence, respectively. The default port scan process includes all RF ports (PINGCFG = 0x0F by default).

The automatic scanning process is initiated by setting the START\_SCAN bit to 1; this is a self-clearing bit and reverts back to a 0 if the register is read back. While the modem is actively scanning the RF ports, the SCANNING bit asserts (1) and the LSTN\_PORT bits indicate which port is connected to the modem through the 4:1 MUX.

# 4 Channel AISG Integrated Modem

Figure 14. Port Scan Flow Chart

The port scanning dwell time is either a manually controlled delay or is based on a combination of the SCAN\_DWELL setting and the programmed DATARATE setting described in the *Direction Output* section. This dwell time defines how long the receiver listens to each RF port in order to detect a 2.176MHz carrier signal.

### Table 4. SCAN\_DWELL Time

|       | SCAN_DWELL            | DWELL TIME                 |                              |                               |  |  |

|-------|-----------------------|----------------------------|------------------------------|-------------------------------|--|--|

| VALUE | BIT PERIOD MULTIPLIER | DATA RATE =<br>0x0/9.6kbps | DATA RATE =<br>0x1/38.4kbps* | DATA RATE =<br>0x2/115.2kbps* |  |  |

### Table 4. SCAN\_DWELL Time (continued)

| 0x0 | NA                      | Manual mode: Sequenced by SCAN_INDEX Bit |                                                                                     |         |  |  |  |  |

|-----|-------------------------|------------------------------------------|-------------------------------------------------------------------------------------|---------|--|--|--|--|

| 0x1 | 1x                      | 0.104ms                                  | 0.026ms                                                                             | 0.009ms |  |  |  |  |

| 0x2 | 16x (Same as DIR Dwell) | 1.667ms                                  | 0.416ms                                                                             | 0.139ms |  |  |  |  |

| 0x3 | User programmed         | Based on upper-nibble of PO              | Based on upper-nibble of PORTCFG (0x04) register and the DWELL_MULT (0x05) register |         |  |  |  |  |

\*Nonstandard setting for AISG v3.0

When SCAN\_DWELL is set to 0x0, the dwell time is controlled by the user and does not increment to the next RF port until the SCAN\_INDEX bit is set to 1 or a carrier signal is detected and FULL\_DWELL is set to 0. This mode gives the user external, asynchronous control of the port scanning dwell time. When SCAN\_DWELL is set to a value of 0x1 or 0x2, the scan dwell time is based on a fixed number of bit periods (1 or 16) based a combination of the SCAN\_DWELL multiplier and the programmed data rate of the modem. When SCAN\_DWELL is set to 0x3, a user-defined bit period multiplier between 1x to 4096x is used. The user defined DWELL multiplier is a 12-bit value spread across the PINGCFG (0x04) and DWELL\_MULT (0x05) registers with the upper-nibble (bits 11:8) being programmed into the PINGCFG register and the remaining eight bits of the DWELL multiplier being programmed into the DWELL\_MULT register.

### Table 5. User-Programmed Dwell Time

| PARAMETER         | DWELL VALUE |            |            |  |  |  |

|-------------------|-------------|------------|------------|--|--|--|

| REGISTER / BITS   | BITS [11:8] | BITS [7:4] | BITS [3:0] |  |  |  |

| PINGCFG (0x04)    | [7:4]       | _          | —          |  |  |  |

| DWELL_MULT (0x05) | —           | [7:4]      | [3:0]      |  |  |  |

The DATARATE value should be set prior to initiating the scan. See <u>Table 4</u> and <u>Table 5</u> for the available port scanning dwell times.

The port scanning engine indexes to the next port under three conditions:

- After the dwell time has expired.

- The SCAN INDEX bit has been asserted by the user (in manual mode, SCAN DWELL = 0x0).

• An AISG carrier signal has been detected, FULL\_DWELL = 0, and the CHK\_ALL\_PORTS = 1.

After one of the above conditions are met, the next unmasked RF port is selected and programmed into the MUX.

Each port is scanned in sequence from P0, to P1, P2, and P3 based on the mask selection. If the matching MASK\_Px bit is set to 1 then that RF port Px is included in the scan sequence. If the MASK\_Px bit is cleared 0, then that RF port will not be included in the sequence.

Once all the unmasked ports have been scanned, the SCANNING bit is set to 0 and the port scanning process is complete.

The port scanning process uses the sensitivity threshold programmed into the RXSENS bits of the RXTX (0x03) register. A signal is reported as a valid detection when the power level exceeds the programmed sensitivity threshold (i.e., the DIR pin indicates an AISG signal). See Input Range and Sensitivity Threshold Control in the <u>Receiver</u> section for more information. The RXSENS threshold should be set prior to initiating the scan.

When a carrier signal is detected, the port scanning engine continues to listen to that RF port if the FULL\_DWELL bit is set to 1. This allows the user to decode a full message received at that port. The Rx channel remains active during port scanning thus the RXOUT pin indicates the received signal as in normal operation. For example, the AISG v3.0 ping packet is expected to have a length of 82 bits, assuming the DWELL time is set to 82x the bit period, the port scan routine remains on the selected RF port for the full time needed to decode such a ping message. See the <u>Dwell Time</u> section for for more information.

Results from the automatic port scanning are reported in the PORTSTAT (0x06) register. When an AISG carrier was detected during the scan, each port with a detected signal is marked with a 1 bit in the appropriate location (AISG\_Px bit). If no carrier was detected during the dwell time on that port or by the time the SCAN\_INDEX bit was asserted, the appropriate PORTSTAT bit has a 0 value.

The AISG\_Px bits are only cleared when initiating a new scan. Results from previous scans are held and can be read from the PORTSTAT (0x06) register up until a new scan is started by setting the START\_SCAN bit to 1.

#### **Status Bits**

The STATUS register (0x07) can be used to determine the state of various internal modem blocks. This read-only register indicates the status of the internal TXACTIVE signal, the RXOUT signal, and the DIR signal through the SPI interface rather than having to sense the three modem pins themselves.

The status of the PA can be determined by reading the TXACTIVE bit in the STATUS register. This bit provides the transmission status of the PA rather than the same logic value of the TXIN pin-effectively inverted from the pin logic. That is, when the TXIN pin is driven to a logic-low or 0 value OR the TX\_ON bit of the CFG (0x00) register is set to 1, the transmitter generates a 2.176MHz carrier on the connected RF port and the TXACTIVE bit reads back as a 1.

The DIR bit [1] of the STATUS register provides a duplicate value of the DIR pin. That is, when the DIR pin is being driven to a logic-high or 1 value by the modem, indicating the receiver has detected a 2.176MHz carrier on the connected RF port, the DIR bit reads back as a 1.

The RXOUT bit [0] of the STATUS register also provides a duplicate value of the RXOUT pin. For example, when the receiver is detecting a 2.176MHz carrier on the connected RF port, the RXOUT pin is driven to a logic-low or 0 value by the modem and the RXOUT bit is also read back as a 0.

# 4 Channel AISG Integrated Modem

## **Register Map**

### **Register Map**

| ADDRESS | NAME             | MSB                   |                |             |              |              |             |                | LSB            |

|---------|------------------|-----------------------|----------------|-------------|--------------|--------------|-------------|----------------|----------------|

| AISG    |                  | ·                     |                |             |              |              |             |                |                |

| 0x00    | <u>CFG[7:0]</u>  | XTALOS<br>C           | PWRDN          | STANDB<br>Y | TX_ON        | OSCBI        | JF[1:0]     | DATARATE[1:0]  |                |

| 0x01    | <u>MUX[7:0]</u>  | -                     | -              | -           | -            | -            | OPEN        | RFPOI          | RT[1:0]        |

| 0x02    | <u>SCAN[7:0]</u> | CHK_AL<br>L_PORT<br>S | FULL_D<br>WELL | SCAN_D      | WELL[1:0]    |              |             | SCAN_I<br>NDEX | START_<br>SCAN |

| 0x03    | <u>RXTX[7:0]</u> |                       | RXSEI          | NS[3:0]     |              | TXPWR[3:0]   |             |                |                |

| 0x04    | PINGCFG[7:0]     |                       | DWEL           | L[11:8]     |              | MASK_P<br>3  | MASK_P<br>2 | MASK_P<br>1    | MASK_P<br>0    |

| 0x05    | DWELL_MULT[7:0]  |                       |                |             | DWEL         | L[7:0]       |             |                |                |

| 0x06    | PORTSTAT[7:0]    | -                     | LSTN_P         | ORT[1:0]    | SCANNI<br>NG | AISG_P3      | AISG_P2     | AISG_P1        | AISG_P0        |

| 0x07    | STATUS[7:0]      | -                     |                |             | _            | TXACTI<br>VE | RXOUT       | DIR            |                |

| 0x08    | <u>ID1[7:0]</u>  |                       | PARTNUM[7:0]   |             |              |              |             |                |                |

| 0x09    | <u>ID2[7:0]</u>  |                       |                |             | REVN         | JM[7:0]      |             |                |                |

### **Register Details**

### <u>CFG (0x0)</u>

| BIT            | 7           | 6           | 5                                                                                                        | 4           | 3               | 2                                                                                                                                    | 1             | 0                 |  |      |

|----------------|-------------|-------------|----------------------------------------------------------------------------------------------------------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|--|------|

| Field          | XTALOSC     | PWRDN       | STANDBY                                                                                                  | TX_ON       | OSCE            | BUF[1:0]                                                                                                                             | DATARATE[1:0] |                   |  |      |