SCES286F - OCTOBER 1999 - REVISED APRIL 2003

- TI-OPC™ Circuitry Limits Ringing on **Unevenly Loaded Backplanes**

- **OEC™** Circuitry Improves Signal Integrity and Reduces Electromagnetic Interference

- Bidirectional Interface Between GTLP Signal Levels and LVTTL Logic Levels

- Split LVTTL Port Provides a Feedback Path for Control and Diagnostics Monitoring

- **LVTTL Interfaces Are 5-V Tolerant**

- **High-Drive GTLP Outputs (100 mA)**

- LVTTL Outputs (-24 mA/24 mA)

- Variable Edge-Rate Control (ERC) Input Selects GTLP Rise and Fall Times for **Optimal Data-Transfer Rate and Signal Integrity in Distributed Loads**

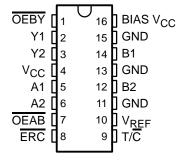

- - - D, DGV, OR PW PACKAGE (TOP VIEW)

- Ioff, Power-Up 3-State, and BIAS VCC Support Live Insertion

- **Polarity Control Selects True or Complementary Outputs**

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- **ESD Protection Exceeds JESD 22**

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

#### description/ordering information

#### ORDERING INFORMATION

| TA            | PACKAGE <sup>†</sup> |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|---------------|----------------------|---------------|--------------------------|---------------------|

|               | QFN – RGY            | Tape and reel | SN74GTLP1394RGYR         | GP1394              |

| -40°C to 85°C | SOIC - D             | Tube          | SN74GTLP1394D            | GTLP1394            |

|               |                      | Tape and reel | SN74GTLP1394DR           | GILF 1394           |

|               | TSSOP – PW           | Tape and reel | SN74GTLP1394PWR          | GP394               |

|               | TVSOP – DGV          | Tape and reel | SN74GTLP1394DGVR         | GP394               |

<sup>†</sup>Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

OEC, TI, and TI-OPC are trademarks of Texas Instruments

SCES286F - OCTOBER 1999 - REVISED ÁPRIL 2003

#### description/ordering information (continued)

The SN74GTLP1394 is a high-drive, 2-bit, 3-wire bus transceiver that provides LVTTL-to-GTLP and GTLP-to-LVTTL signal-level translation. It allows for transparent and inverted transparent modes of data transfer with separate LVTTL input and LVTTL output pins, which provides a feedback path for control and diagnostics monitoring. The device provides a high-speed interface between cards operating at LVTTL logic levels and a backplane operating at GTLP signal levels, and is especially designed to work with the Texas Instruments (TI) 1394 backplane physical-layer controllers. High-speed (about three times faster than standard LVTTL or TTL) backplane operation is a direct result of GTLP reduced output swing (<1 V), reduced input threshold levels, improved differential input, OEC<sup>TM</sup> circuitry, and TI-OPC<sup>TM</sup> circuitry. Improved GTLP OEC and TI-OPC circuitry minimizes bus-settling time and have been designed and tested using several backplane models. The high drive allows incident-wave switching in heavily loaded backplanes with equivalent load impedance down to 11 Ω.

GTLP is the TI derivative of the Gunning Transceiver Logic (GTL) JEDEC standard JESD 8-3. The ac specification of the SN74GTLP1394 is given only at the preferred higher noise margin GTLP, but the user has the flexibility of using this device at either GTL ( $V_{TT} = 1.2 \text{ V}$  and  $V_{REF} = 0.8 \text{ V}$ ) or GTLP ( $V_{TT} = 1.5 \text{ V}$  and  $V_{REF} = 1.5 \text{ V}$ ) signal levels.

Normally, the B port operates at GTLP signal levels. The A-port and control inputs operate at LVTTL logic levels, but are 5-V tolerant and are compatible with TTL and 5-V CMOS inputs.  $V_{REF}$  is the B-port differential input reference voltage.

This device is fully specified for live-insertion applications using  $I_{off}$ , power-up 3-state, and BIAS  $V_{CC}$ . The  $I_{off}$  circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict. The BIAS  $V_{CC}$  circuitry precharges and preconditions the B-port input/output connections, preventing disturbance of active data on the backplane during card insertion or removal and permits true live-insertion capability.

This GTLP device features TI-OPC circuitry, which actively limits the overshoot caused by improperly terminated backplanes, unevenly distributed cards, or empty slots during low-to-high signal transitions. This improves signal integrity, which allows adequate noise margin to be maintained at higher frequencies.

High-drive GTLP backplane interface devices feature adjustable edge-rate control ( $\overline{\text{ERC}}$ ). Changing the  $\overline{\text{ERC}}$  input voltage between GND and  $V_{CC}$  adjusts the B-port output rise and fall times. This allows the designer to optimize system data-transfer rate and signal integrity to the backplane load.

When  $V_{CC}$  is between 0 and 1.5 V, the device is in the high-impedance state during power up or power down. However, to ensure the high-impedance state above 1.5 V, the output-enable ( $\overline{OE}$ ) input should be tied to  $V_{CC}$  through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

#### functional description

The output-enable  $(\overline{OEAB})$  input controls the activity of the B port. When  $\overline{OEAB}$  is low, the B-port outputs are active. When  $\overline{OEAB}$  is high, the B-port outputs are disabled.

Separate LVTTL input and output pins provide a feedback path for control and diagnostics monitoring. The  $\overline{OEBY}$  input controls the Y outputs. When  $\overline{OEBY}$  is low, the Y outputs are active. When  $\overline{OEBY}$  is high, the Y outputs are disabled.

The polarity-control  $(T/\overline{C})$  input is provided to select polarity of data transmission in both directions. When  $T/\overline{C}$  is high, data transmission is true, and A data goes to the B bus and B data goes to the Y bus. When  $T/\overline{C}$  is low, data transmission is complementary, and inverted A data goes to the B bus and inverted B data goes to the Y bus.

SCES286F - OCTOBER 1999 - REVISED APRIL 2003

#### **Function Tables**

#### **OUTPUT CONTROL**

|     | INPUTS |      | OUTPUT                                                | MODE                                    |

|-----|--------|------|-------------------------------------------------------|-----------------------------------------|

| T/C | OEAB   | OEBY | OUTPUT                                                | MODE                                    |

| Х   | Н      | Н    | Z                                                     | Isolation                               |

| Н   | L      | Н    | A data to B bus                                       | True transparent                        |

| Н   | Н      | L    | B data to Y bus                                       | True transparent                        |

| Н   | L      | L    | A data to B bus, B data to Y bus                      | True transparent with feedback path     |

| L   | L      | Н    | Inverted A data to B bus                              | Inverted transparent                    |

| L   | Н      | L    | Inverted B data to Y bus                              | inverted transparent                    |

| L   | L      | L    | Inverted A data to B bus,<br>Inverted B data to Y bus | Inverted transparent with feedback path |

#### **OUTPUT EDGE-RATE CONTROL (ERC)**

| INPU           | T ERC              | OUTPUT              |

|----------------|--------------------|---------------------|

| LOGIC<br>LEVEL | NOMINAL<br>VOLTAGE | B-PORT<br>EDGE RATE |

| L              | GND                | Slow                |

| Н              | Vcc                | Fast                |

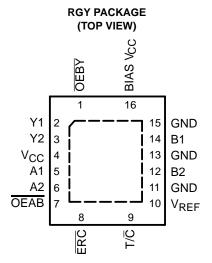

# logic diagram (positive logic)

SCES286F - OCTOBER 1999 - REVISED APRIL 2003

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> and BIAS V <sub>CC</sub>                   |                 |

|----------------------------------------------------------------------------------|-----------------|

| B port and V <sub>REF</sub>                                                      |                 |

| Voltage range applied to any output in the high-impedance or power-off state, VO |                 |

| (see Note 1): Y outputs                                                          | 0.5 V to 7 V    |

| B port                                                                           | –0.5 V to 4.6 V |

| Current into any output in the low state, IO: Y outputs                          |                 |

| B port                                                                           |                 |

| Current into any output in the high state, I <sub>O</sub> (see Note 2)           |                 |

| Continuous current through each V <sub>CC</sub> or GND                           |                 |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ )                                      |                 |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)                       |                 |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3): D package               |                 |

| (see Note 3): DGV package                                                        |                 |

| (see Note 3): PW package                                                         |                 |

| (see Note 4): RGY package                                                        |                 |

| Storage temperature range, T <sub>stg</sub>                                      |                 |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. This current flows only when the output is in the high state and  $V_O > V_{CC}$ .

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

- 4. The package thermal impedance is calculated in accordance with JESD 51-5.

ŚCES286F – OCTOBER 1999 – REVISED APRIL 2003

#### recommended operating conditions (see Notes 5 through 8)

|                                           |                                    |                       | MIN                    | NOM | MAX                    | UNIT           |  |

|-------------------------------------------|------------------------------------|-----------------------|------------------------|-----|------------------------|----------------|--|

| V <sub>CC</sub> ,<br>BIAS V <sub>CC</sub> | Supply voltage                     |                       | 3.15                   | 3.3 | 3.45                   | ٧              |  |

|                                           | Toursination valte as              | GTL                   | 1.14                   | 1.2 | 1.26                   | V              |  |

| VTT                                       | Termination voltage                | GTLP                  | 1.35                   | 1.5 | 1.65                   | l <sup>v</sup> |  |

| V                                         | Poforance voltage                  | GTL                   | 0.74                   | 0.8 | 0.87                   | V              |  |

| VREF                                      | Reference voltage                  | GTLP                  | 0.87                   | 1   | 1.1                    | ]              |  |

| V.                                        | lanut voltage                      | B port                |                        |     | $V_{TT}$               | V              |  |

| VI                                        | Input voltage                      | Except B port         |                        | Vcc | 5.5                    | ٧              |  |

|                                           | High-level input voltage           | B port                | V <sub>REF</sub> +0.05 |     |                        |                |  |

| VIH                                       |                                    | ERC                   | V <sub>CC</sub> -0.6   | Vcc | 5.5                    | V              |  |

|                                           |                                    | Except B port and ERC | 2                      |     |                        |                |  |

|                                           | Low-level input voltage            | B port                |                        |     | V <sub>REF</sub> -0.05 | V              |  |

| $V_{IL}$                                  |                                    | ERC                   |                        | GND | 0.6                    |                |  |

|                                           |                                    | Except B port and ERC |                        |     | 0.8                    |                |  |

| lıK                                       | Input clamp current                |                       |                        |     | -18                    | mA             |  |

| loн                                       | High-level output current          | Y outputs             |                        |     | -24                    | mA             |  |

| 1                                         | Law law law day day day            | Y outputs             |                        |     | 24                     | A              |  |

| lOL                                       | Low-level output current           | B port                |                        |     | 100                    | mA             |  |

| Δt/Δν                                     | Input transition rise or fall rate | Outputs enabled       |                        |     | 10                     | ns/V           |  |

| Δt/ΔV <sub>CC</sub>                       | Power-up ramp rate                 | •                     | 20                     |     |                        | μs/V           |  |

| TA                                        | Operating free-air temperature     |                       | -40                    |     | 85                     | °C             |  |

- NOTES: 5. All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

- 6. Proper connection sequence for use of the B-port I/O precharge feature is GND and BIAS V<sub>CC</sub> = 3.3 V first, I/O second, and V<sub>CC</sub> = 3.3 V last, because the BIAS V<sub>CC</sub> precharge circuitry is disabled when any V<sub>CC</sub> pin is connected. The control and V<sub>REF</sub> inputs can be connected anytime, but normally are connected during the I/O stage. If B-port precharge is not required, any connection sequence is acceptable, but generally, GND is connected first.

- 7. V<sub>TT</sub> and R<sub>TT</sub> can be adjusted to accommodate backplane impedances if the dc recommended I<sub>OL</sub> ratings are not exceeded.

- 8. VREF can be adjusted to optimize noise margins, but normally is two-thirds VTT. TI-OPC circuitry is enabled in the A-to-B direction and is activated when VTT > 0.7 V above VREF. If operated in the A-to-B direction, VREF should be set to within 0.6 V of VTT to minimize current drain.

SCES286F - OCTOBER 1999 - REVISED APRIL 2003

# electrical characteristics over recommended operating free-air temperature range for GTLP (unless otherwise noted)

| PA                 | RAMETER                   | TEST CONDITIONS                                                                                              |                             |                      | TYP <sup>†</sup> | MAX  | UNIT |

|--------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|------------------|------|------|

| VIK                |                           | V <sub>CC</sub> = 3.15 V,                                                                                    | I <sub>I</sub> = -18 mA     |                      |                  | -1.2 | V    |

|                    |                           | V <sub>CC</sub> = 3.15 V to 3.45 V,                                                                          | I <sub>OH</sub> = -100 μA   | V <sub>CC</sub> -0.2 |                  |      |      |

| Vон                | Y outputs                 | V                                                                                                            | I <sub>OH</sub> = -12 mA    | 2.4                  |                  |      | V    |

|                    |                           | VCC = 3.15 V                                                                                                 | I <sub>OH</sub> = -24 mA    | 2                    |                  |      |      |

|                    |                           | V <sub>CC</sub> = 3.15 V to 3.45 V,                                                                          | I <sub>OL</sub> = 100 μA    |                      |                  | 0.2  |      |

|                    | Y outputs                 | V== - 2.45 V                                                                                                 | I <sub>OL</sub> = 12 mA     |                      |                  | 0.4  |      |

| \/a:               |                           | V <sub>CC</sub> = 3.15 V                                                                                     | I <sub>OL</sub> = 24 mA     |                      |                  | 0.5  | V    |

| VOL                |                           |                                                                                                              | I <sub>OL</sub> = 10 mA     |                      |                  | 0.2  | V    |

|                    | B port                    | V <sub>CC</sub> = 3.15 V                                                                                     | $I_{OL} = 64 \text{ mA}$    |                      |                  | 0.4  |      |

|                    |                           |                                                                                                              | I <sub>OL</sub> = 100 mA    |                      |                  | 0.55 |      |

| lį                 | A-port and control inputs | V <sub>CC</sub> = 3.45 V                                                                                     | V <sub>I</sub> = 0 to 5.5 V |                      |                  | ±10  | μΑ   |

| . +                | Y outputs                 | V 245 V                                                                                                      | VO = VCC                    |                      | -                | 10   | 4    |

| lozh‡              | B port                    | V <sub>CC</sub> = 3.45 V                                                                                     | V <sub>O</sub> = 1.5 V      |                      |                  | 10   | μΑ   |

| loz <sub>L</sub> ‡ | Y outputs and<br>B port   | V <sub>CC</sub> = 3.45 V,                                                                                    | V <sub>O</sub> = GND        |                      |                  | -10  | μА   |

|                    |                           | V <sub>CC</sub> = 3.45 V, I <sub>O</sub> = 0,                                                                | Outputs high                |                      |                  | 20   |      |

| Icc                | Y outputs and<br>B port   | $V_I$ (A-port or control inputs) = $V_{CC}$ or GND,                                                          | Outputs low                 |                      |                  | 20   | mA   |

|                    | D poit                    | $V_I$ (B port) = $V_{TT}$ or GND                                                                             | Outputs disabled            |                      |                  | 20   |      |

| ΔICC§              |                           | $V_{CC}$ = 3.45 V, One A-port or control input at $V_{CC}$ Other A-port or control inputs at $V_{CC}$ or GND | C - 0.6 V,                  |                      |                  | 1.5  | mA   |

| <u> </u>           | A-port inputs             |                                                                                                              |                             |                      | 3.5              | 4.5  | ~F   |

| Ci                 | Control inputs            | V <sub>I</sub> = 3.15 V or 0                                                                                 |                             |                      | 4                | 5    | pF   |

| Co                 | Y outputs                 | $V_{O} = 3.15 \text{ V or } 0$                                                                               |                             |                      | 4.5              | 5    | pF   |

| C <sub>io</sub>    | B port                    | V <sub>O</sub> = 1.5 V or 0                                                                                  |                             |                      | 9                | 10.5 | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

# hot-insertion specifications for A inputs and Y outputs over recommended operating free-air temperature range

| PARAMETER        |                                         | TEST CONDITIONS               |                               |  | MAX | UNIT |

|------------------|-----------------------------------------|-------------------------------|-------------------------------|--|-----|------|

| l <sub>off</sub> | $V_{CC} = 0$ ,                          | BIAS $V_{CC} = 0$ ,           | $V_I$ or $V_O = 0$ to 5.5 $V$ |  | 10  | μΑ   |

| IOZPU            | $V_{CC} = 0 \text{ to } 1.5 \text{ V},$ | $V_0 = 0.5 \text{ V to 3 V},$ | OE = 0                        |  | ±30 | μΑ   |

| lozpd            | $V_{CC} = 1.5 \text{ V to } 0,$         | $V_0 = 0.5 \text{ V to 3 V},$ | OE = 0                        |  | ±30 | μΑ   |

<sup>‡</sup> For I/O ports, the parameters IOZH and IOZL include the input leakage current.

<sup>§</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

SCES286F - OCTOBER 1999 - REVISED APRIL 2003

## live-insertion specifications for B port over recommended operating free-air temperature range

| PARAMETER        | TEST CONDITIONS                         |                                                     |                                                            | MIN  | MAX  | UNIT |

|------------------|-----------------------------------------|-----------------------------------------------------|------------------------------------------------------------|------|------|------|

| l <sub>off</sub> | $V_{CC} = 0$ ,                          | BIAS $V_{CC} = 0$ ,                                 | $V_I$ or $V_O = 0$ to 1.5 $V$                              |      | 10   | μΑ   |

| lozpu            | $V_{CC} = 0 \text{ to } 1.5 \text{ V},$ | BIAS $V_{CC} = 0$ ,                                 | $V_0 = 0.5 \text{ V to } 1.5 \text{ V}, \overline{OE} = 0$ |      | ±30  | μΑ   |

| IOZPD            | $V_{CC} = 1.5 \text{ V to } 0,$         | BIAS $V_{CC} = 0$ ,                                 | $V_0 = 0.5 \text{ V to } 1.5 \text{ V}, \overline{OE} = 0$ |      | ±30  | μΑ   |

| Ica (PIAS Voc)   | $V_{CC} = 0 \text{ to } 3.15 \text{ V}$ | BIAS V <sub>CC</sub> = 3.15 V to 3.45 V,            | \/= (D nort)                                               |      | 5    | mA   |

| ICC (BIAS VCC)   | V <sub>CC</sub> = 3.15 V to 3.45 V      | DIAS VCC = 3.15 V to 3.45 V,                        | $V_O$ (B port) = 0 to 1.5 V                                |      | 10   | μΑ   |

| VO               | $V_{CC} = 0$ ,                          | BIAS $V_{CC} = 3.3 \text{ V}$ ,                     | IO = 0                                                     | 0.95 | 1.05 | V    |

| IO               | $V_{CC} = 0$ ,                          | BIAS $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V}$ , | V <sub>O</sub> (B port) = 0.6 V                            | -1   |      | μΑ   |

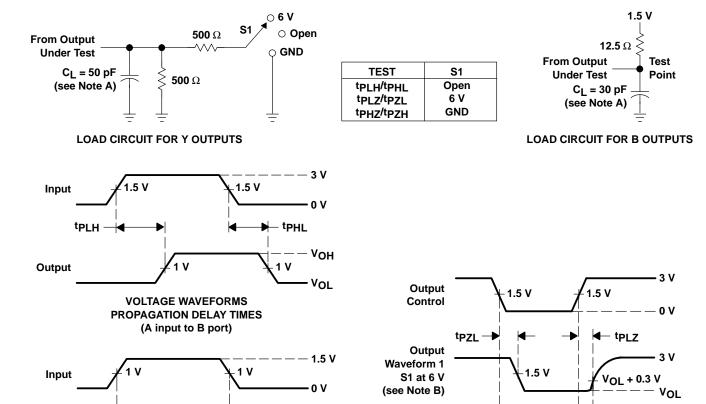

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $V_{TT}$ = 1.5 V and $V_{REF}$ = 1 V for GTLP (see Figure 1)

| PARAMETER        | FROM<br>(INPUT)    | TO<br>(OUTPUT)                    | EDGE RATET | MIN | түр‡ | MAX | UNIT |  |

|------------------|--------------------|-----------------------------------|------------|-----|------|-----|------|--|

| <sup>t</sup> PLH | А                  | В                                 | Slow       | 3.3 |      | 5.9 | ns   |  |

| <sup>t</sup> PHL | ^                  | В                                 | Siow       | 3   |      | 6.6 | 115  |  |

| <sup>t</sup> PLH | А                  | В                                 | Fast       | 2.5 |      | 5.2 | ns   |  |

| <sup>t</sup> PHL | ^                  | В                                 | l ast      | 1.9 |      | 4.8 | 113  |  |

| <sup>t</sup> PLH | А                  | Y                                 | Slow       | 5.4 |      | 9   | ns   |  |

| <sup>t</sup> PHL | ^                  | •                                 | Siow       | 4.9 |      | 8.6 | 115  |  |

| <sup>t</sup> PLH | А                  | Y                                 | Fast       | 4.3 |      | 7.9 | ns   |  |

| <sup>t</sup> PHL | ^                  | •                                 | l ast      | 3.9 |      | 7.5 | 115  |  |

| <sup>t</sup> PLH | T/C                | В                                 | Slow       | 3   |      | 6.5 |      |  |

| <sup>t</sup> PHL | 1/0                | Ь                                 | Siow       | 3.1 |      | 6.6 | ns   |  |

| <sup>t</sup> PLH | T/C                | В                                 | Fast       | 2.3 |      | 5.6 |      |  |

| <sup>t</sup> PHL | 1/0                | Ь                                 | Fasi       | 1.7 | 4.9  |     | ns   |  |

| t <sub>en</sub>  |                    | В                                 | Slow       | 3.2 |      | 6.2 | ns   |  |

| <sup>t</sup> dis | OEAB               | Ь                                 | Siow       | 3.2 |      | 6.4 | 115  |  |

| t <sub>en</sub>  | <del>OEAB</del>    | В                                 | Fast       | 1.9 |      | 5.3 | ns   |  |

| <sup>t</sup> dis | OEAB               | В                                 | i ast      | 2.4 |      | 5.7 | 115  |  |

| •                | Pico timo R outo   | Rise time, B outputs (20% to 80%) |            |     | 2.7  |     | ns   |  |

| t <sub>r</sub>   | Nise time, is outp | Fast                              |            | 1.5 |      | 115 |      |  |

| +.               | Fall time, B outpu | uto (909/ to 209/)                | Slow       | 3.2 |      |     |      |  |

| t <sub>f</sub>   | Fail time, B outpu | JIS (80% 10 20%)                  | Fast       |     | 2.1  |     | ns   |  |

| <sup>t</sup> PLH | В                  | Y                                 |            | 1.6 |      | 4.6 |      |  |

| <sup>t</sup> PHL | D                  | Ť                                 | _          | 1.4 |      | 3.9 | ns   |  |

| <sup>t</sup> PLH | - <del></del>      | Y                                 |            | 1   |      | 4.5 | no   |  |

| <sup>t</sup> PHL | T/C                | T T                               |            | 1.2 |      | 4.1 | ns   |  |

| t <sub>en</sub>  |                    | Y                                 |            | 1   |      | 4.1 |      |  |

| <sup>t</sup> dis | OEBY               | Ť                                 | _          | 1.3 |      | 4.6 | ns   |  |

<sup>†</sup> Slow ( $\overline{ERC} = GND$ ) and Fast ( $\overline{ERC} = V_{CC}$ )

<sup>‡</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

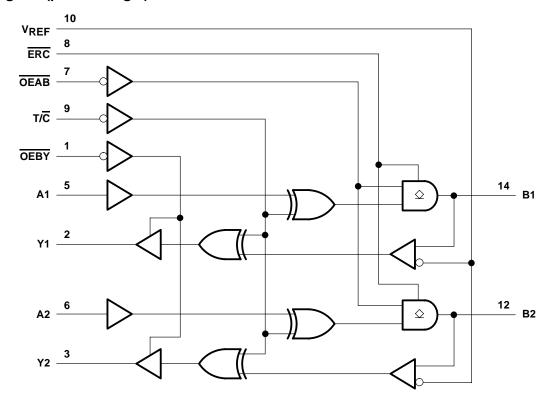

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

1.5 V

**VOLTAGE WAVEFORMS**

PROPAGATION DELAY TIMES

(B port to Y output)

<sup>t</sup>PLH

Output

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\approx$  10 MHz,  $Z_{O}$  = 50  $\Omega$ ,  $t_{f}$   $\approx$  2 ns,  $t_{f}$   $\approx$  2 ns.

tPZH →

1.5 V

**VOLTAGE WAVEFORMS**

**ENABLE AND DISABLE TIMES**

(A input)

Output

Waveform 2

(see Note B)

S1 at GND

· tPHZ

V<sub>OH</sub> - 0.3 V

− VOH

≈0 V

D. The outputs are measured one at a time with one transition per measurement.

<sup>t</sup>PHL

- V<sub>ОН</sub>

VOL

Figure 1. Load Circuits and Voltage Waveforms

SCES286F - OCTOBER 1999 - REVISED APRIL 2003

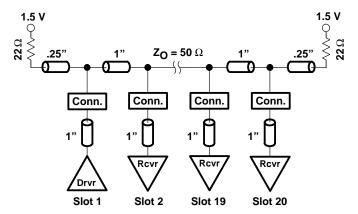

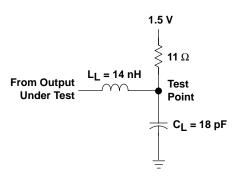

#### DISTRIBUTED-LOAD BACKPLANE SWITCHING CHARACTERISTICS

The preceding switching characteristics table shows the switching characteristics of the device into a lumped load (Figure 1). However, the designer's backplane application probably is a distributed load. The physical representation is shown in Figure 2. This backplane, or distributed load, can be approximated closely to a resistor inductance capacitance (RLC) circuit, as shown in Figure 3. This device has been designed for optimum performance in this RLC circuit. The following switching characteristics table shows the switching characteristics of the device into the RLC load, to help the designer better understand the performance of the GTLP device in this typical backplane. See www.ti.com/sc/gtlp for more information.

Figure 2. High-Drive Test Backplane

Figure 3. High-Drive RLC Network

# **SN74GTLP1394**

# 2-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER WITH SPLIT LYTTL PORT, FEEDBACK PATH, AND SELECTABLE POLARITY SCES286F - OCTOBER 1999 - REVISED APRIL 2003

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $V_{TT}$ = 1.5 V and $V_{REF}$ = 1 V for GTLP (see Figure 3)

| PARAMETER        | FROM<br>(INPUT)     | TO<br>(OUTPUT)       | EDGE RATET | түр‡ | UNIT |

|------------------|---------------------|----------------------|------------|------|------|

| <sup>t</sup> PLH | А                   | В                    | Slow       | 4.2  | ns   |

| t <sub>PHL</sub> | A                   | В                    | 210W       | 4.2  | TIS  |

| <sup>t</sup> PLH | А                   | В                    | Fast       | 3.6  | ns   |

| t <sub>PHL</sub> | A                   | Ь                    | rasi       | 3.6  | 115  |

| <sup>t</sup> PLH | А                   | Υ                    | Slow       | 5.8  | ns   |

| t <sub>PHL</sub> | ^                   | ,                    | Slow       | 5.8  | 115  |

| <sup>t</sup> PLH |                     | Y                    | Fast       | 5.2  | ns   |

| t <sub>PHL</sub> | A                   | ı                    | Fasi       | 5.2  | 115  |

| <sup>t</sup> PLH | T/C                 | В                    | Slow       | 4.4  | 20   |

| t <sub>PHL</sub> | 1/0                 | В                    | Slow       | 4.4  | ns   |

| <sup>t</sup> PLH | T/C                 | В                    | Fast       | 3.8  | ns   |

| <sup>t</sup> PHL | 1/0                 | Ь                    | i ast      | 3.8  | 113  |

| t <sub>en</sub>  | OEAB                | В                    | Slow       | 4.2  | ns   |

| <sup>t</sup> dis | OEAB                | Б                    | Slow       | 4.3  | 115  |

| t <sub>en</sub>  | <del></del> OEAB    | В                    | Fast       | 3.6  | ns   |

| <sup>t</sup> dis | OEAB                | Б                    | i ast      | 3.3  | 113  |

| t <sub>r</sub>   | Rise time, B outp   | uts (20% to 80%)     | Slow       | 2    | ns   |

| ч                | Nise time, b outp   | uts (2070 to 0070)   | Fast       | 1.2  | 115  |

| t <sub>f</sub>   | Fall time, B outpu  | its (80% to 20%)     | Slow       | 2.5  | ns   |

| Ч                | r all time, b outpo | 113 (00 /0 to 20 /0) | Fast       | 1.8  |      |

<sup>†</sup> Slow ( $\overline{ERC} = GND$ ) and Fast ( $\overline{ERC} = V_{CC}$ )

<sup>‡</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . All values are derived from TI-SPICE models.

ŚCES286F – OCTOBER 1999 – REVISED APRIL 2003

#### **APPLICATION INFORMATION**

#### operational description

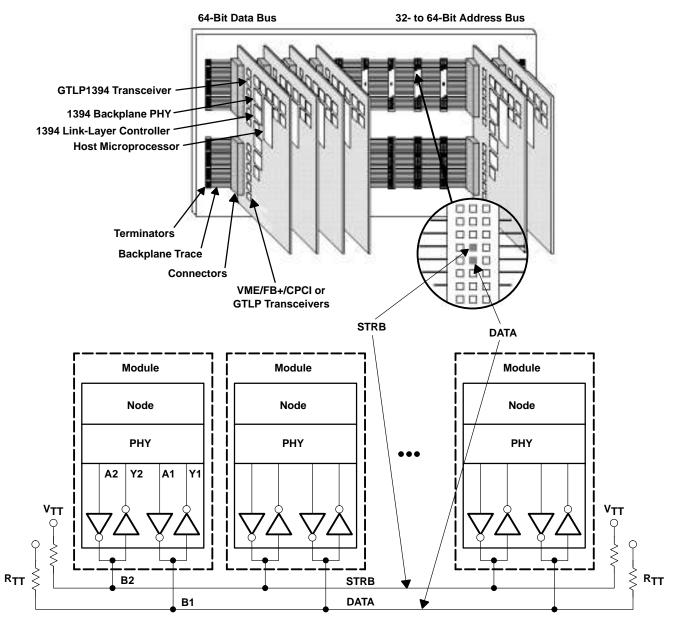

The GTLP1394 is designed specifically for use with the TI 1394 backplane layer controller family to transmit the 1394 backplane serial bus across parallel backplanes. But, it is a versatile 2-bit device that also is being used to provide multiple single-bit clocks or ATM read and write clock in multislot parallel backplane applications.

The 1394–1995 is an IEEE designation for a high-performance serial bus. This serial bus defines both a backplane (e.g., GTLP, VME, FB+, CPCI, etc.) physical layer and a point-to-point cable-connected virtual bus. The backplane version operates at 25, 50, or 100 Mbps, whereas the cable version supports data rates of 100, 200, and 400 Mbps. Both versions are compatible at the link layer and above. The interface standard defines the transmission method, media in the cable version, and protocol. The primary application of the cable version is the interconnection of digital A/V equipment and integration of I/O connectivity at the back panel of personal computers using a low-cost, scalable, high-speed serial interface. The primary application of the backplane version is to provide a robust control interface to each daughter card. The 1394 standard also provides new services, such as real-time I/O and live connect/disconnect capability for external devices.

#### electrical

The 1394 standard is a transaction-based packet technology for cable- or backplane-based environments. Both chassis and peripheral devices can use this technology. The 1394 serial bus is organized as if it were memory space interconnected between devices, or as if devices resided in slots on the main backplane. Device addressing is 64 bits wide, partitioned as ten bits for bus ID, six bits for node ID, and 48 bits for memory addresses. The result is the capability to address up to 1023 buses, with each having up to 63 nodes, each with 281 terabytes of memory. Memory-based addressing, rather than channel addressing, views resources as registers or memory that can be accessed with processor-to-memory transactions. Each bus entity is termed a unit, to be individually addressed, reset, and identified. Multiple nodes can reside physically in a single module, and multiple ports can reside in a single node.

Some key features of the 1394 topology are multimaster capabilities, live connect/disconnect (hot plugging) capability, genderless cabling connectors on interconnect cabling, and dynamic node address allocation as nodes are added to the bus. A maximum of 63 nodes can be connected to one network.

The cable-based physical interface uses dc-level line states for signaling during initialization and arbitration. Both environments use dominant mode addresses for arbitration. The backplane environment does not have the initialization requirements of the cable environment because it is a physical bus and does not contain repeaters. Due to the differences, a backplane-to-cable bridge is required to connect these two environments.

The signals transmitted on both the cable and backplane environments are NRZ with data-strobe (DS) encoding. DS encoding allows only one of the two signal lines to change each data bit-period, essentially doubling the jitter tolerance, with very little additional circuitry overhead in the hardware.

#### **APPLICATION INFORMATION**

#### protocol

Both asynchronous and isochronous data transfers are supported. The asynchronous format transfers data and transaction-layer information to an explicit address. The isochronous format broadcasts data based on channel numbers rather than specific addressing. Isochronous packets are issued on the average of each 125  $\mu$ s in support of time-sensitive applications. Providing both asynchronous and isochronous formats on the same interface allows both non-real-time and real-time critical applications on the same bus. The cable environment's tree topology is resolved during a sequence of events, triggered each time a new node is added or removed from the network. This sequence starts with a bus reset phase, where previous information about a topology is cleared. The tree ID sequence determines the actual tree structure, and a root node is dynamically assigned, or it is possible to force a particular node to become the root. After the tree is formed, a self-ID phase allows each node on the network to identify itself to all other nodes. During the self-ID process, each node is assigned an address. After all the information has been gathered on each node, the bus goes into an idle state, waiting for the beginning of the standard arbitration process.

The backplane physical layer shares some commonality with the cable physical layer. Common functions include: bus state determination, bus access protocols, encoding and decoding functions, and synchronization of received data to a local clock.

#### backplane features

- 25-, 50-, and 100-Mbps data rates for backplane environments

- Live connection/disconnection possible without data loss or interruption.

- Configuration ROM and status registers supporting plug and play

- Multidrop or point-to-point topologies supported.

- Specified bandwidth assignments for real-time applications

#### applicability and typical application for IEEE 1394 backplane

The 1394 backplane serial bus (BPSB) plays a supportive role in backplane systems, specifically GTLP, FutureBus+, VME64, and proprietary backplane bus systems. This supportive role can be grouped into three categories:

- Diagnostics

- Alternate control path to the parallel backplane bus

- Test, maintenance, and troubleshooting

- Software debug and support interface

- System enhancement

- Fault tolerance

- Live insertion

- CSR access

- Auxiliary 2-bit bus with a 64-bit address space to the parallel backplane bus

- Peripheral monitoring

- Monitoring of peripherals (disk drives, fans, power supplies, etc.) in conjunction with another externally wired monitor bus, such as defined by the Intelligent Platform Management Interface (IPMI).

The 1394 backplane physical layer (PHY) and the SN74GTLP1394 provide a cost-effective way to add high-speed 1394 connections to every daughter card in almost any backplane. More information on the backplane physical layer devices and how to implement the 1394 standard in backplane and cable applications can be found at: <a href="https://www.ti.com/sc/1394">www.ti.com/sc/1394</a>.

ŚCES286F – OCTOBER 1999 – REVISED APRIL 2003

#### APPLICATION INFORMATION

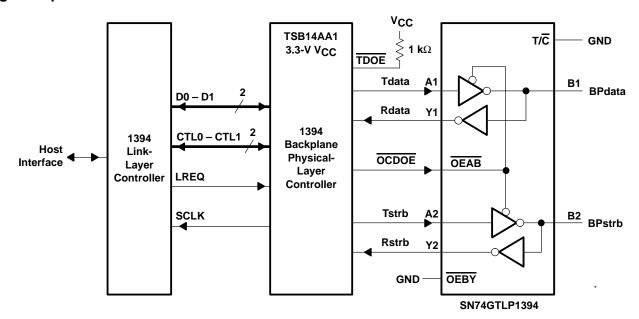

### SN74GTLP1394 interface with the TSB14AA1 1394 backplane PHY

- A1, B1, and Y1 are used for the PHY data signals.

- A2, B2, and Y2 are used for the PHY strobe signals.

- PHY N\_OEB\_D or OCDOE connects to OEAB, which controls the PHY transmit signals.

- OEBY is connected to GND since the transceiver always must be able to receive signals from the backplane and relay them to the PHY.

- T/C is connected to GND for inverted signals.

- V<sub>CC</sub> is nominal 3.3 V.

- BIAS V<sub>CC</sub> is connected to nominal 3.3 V to support live insertion.

- V<sub>REF</sub> normally is 2/3 of V<sub>TT</sub>.

- ERC normally is connected to GND for slow edge-rate operation because frequencies of only 50 MHz (S100) and 25 MHz (S50) are required.

## **APPLICATION INFORMATION**

# logical representation

SCES286F - OCTOBER 1999 - REVISED APRIL 2003

#### **APPLICATION INFORMATION**

# physical representation

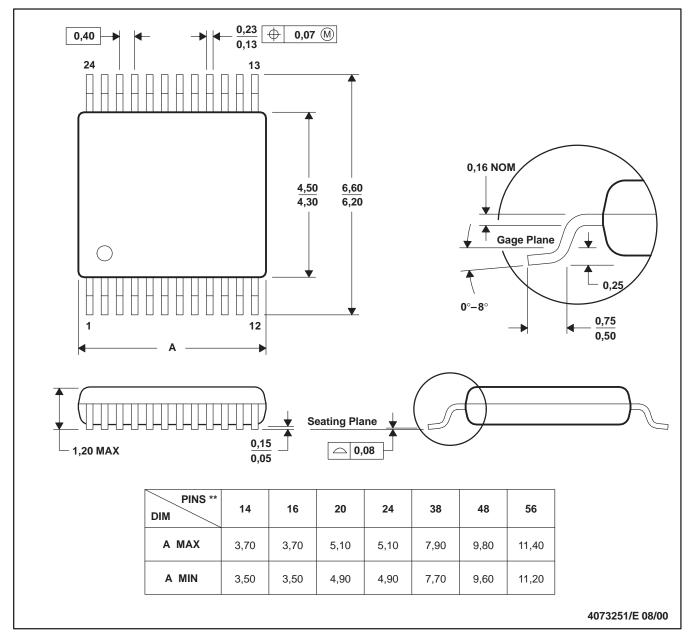

## DGV (R-PDSO-G\*\*)

#### **24 PINS SHOWN**

#### **PLASTIC SMALL-OUTLINE**

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15 per side.

D. Falls within JEDEC: 24/48 Pins – MO-153 14/16/20/56 Pins – MO-194

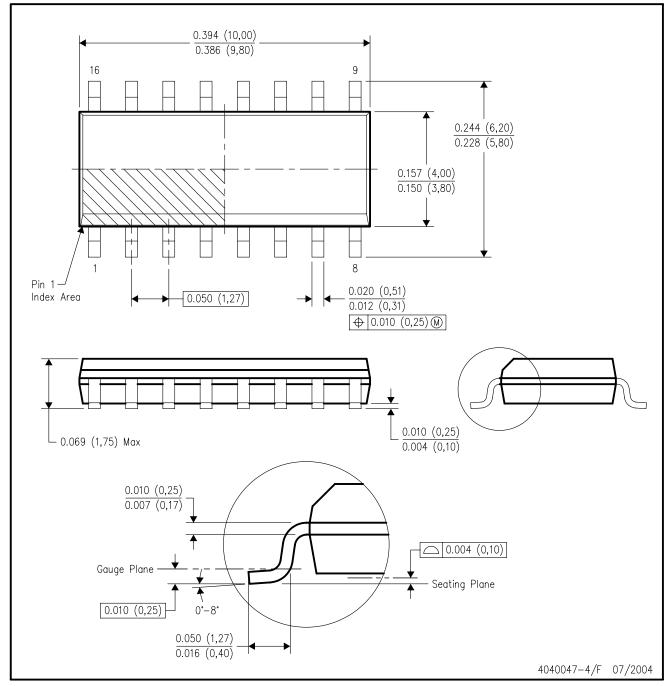

# D (R-PDSO-G16)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012 variation AC.

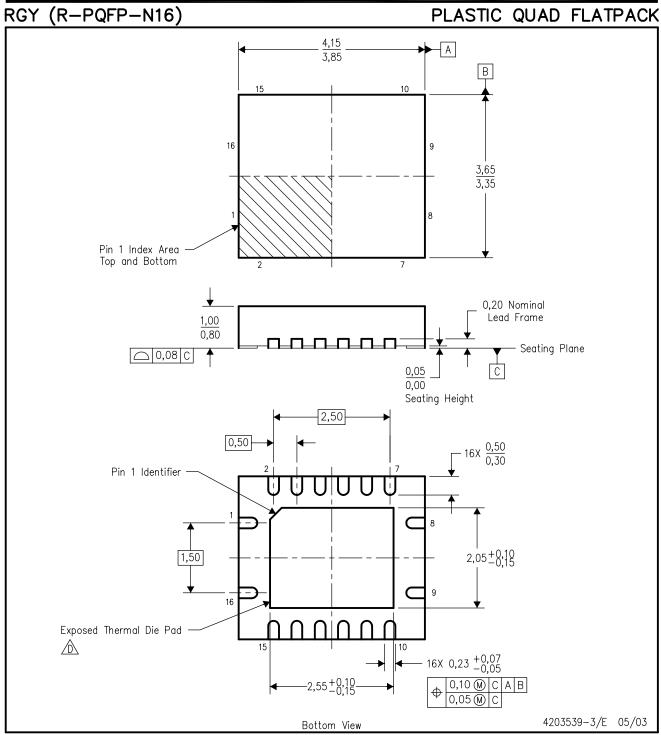

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) package configuration.

- The package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane.

This pad is electrically and thermally connected to the backside of the die and possibly selected ground leads.

- E. Package complies to JEDEC MO-241 variation BB.

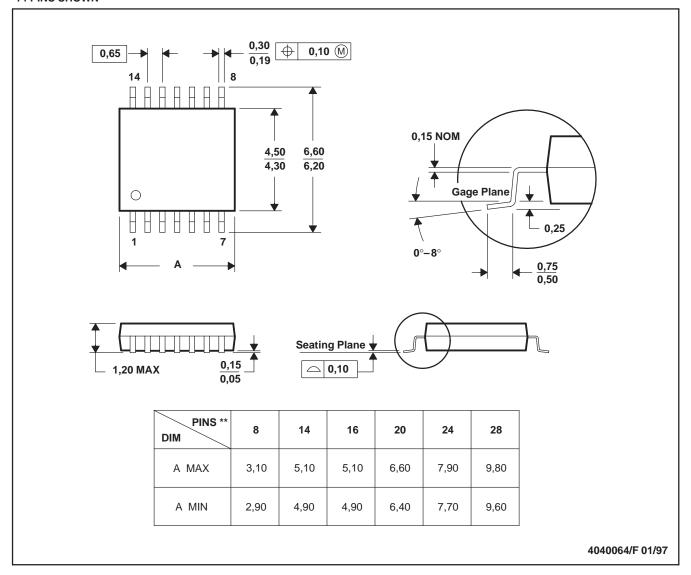

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated