# HSP45256

January 1994

#### **Binary Correlator**

#### Features

- Reconfigurable 256 Stage Binary Correlator

- 1-Bit Reference x 1, 2, 4, or 8-Bit Data

- Separate Control and Reference Interfaces

- · 25.6, 33MHz Versions

- . Configurable for 1-D and 2-D Operation

- · Double Buffered Mask and Reference

- · Programmable Output Delay

- Cascadable

- Standard Microprocessor Interface

#### **Applications**

- Radar/Sonar

- · Spread Spectrum Communications

- · Pattern/Character Recognition

- · Error Correction Coding

#### Ordering Information

| PART NUMBER   | TEMPERATURE<br>RANGE | PACKAGE      |

|---------------|----------------------|--------------|

| HSP45256JC-25 | 0°C to +70°C         | 84 Lead PLCC |

| HSP45256JC-33 | 0°C to +70°C         | 84 Lead PLCC |

| HSP45256GC-25 | 0°C to +70°C         | 85 Lead PGA  |

| HSP45256GC-33 | 0°C to +70°C         | 85 Lead PGA  |

#### Description

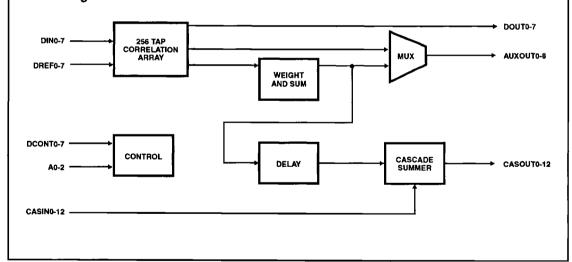

The Harris HSP45256 is a high-speed, 256 tap binary correlator. It can be configured to perform one- or two-dimensional correlations of selectable data precision and length. Multiple HSP45256's can be cascaded for increased correlation length. Unused taps can be masked out for reduced correlation length.

The correlation array consists of eight 32-tap stages. These may be cascaded internally to compare 1, 2, 4 or 8-bit input data with a 1-bit reference. Depending on the number of bits in the input data, the length of the correlation can be up to 256, 128, 64, or 32 taps. The HSP45256 can also be configured as two separate correlators with window sizes from 4 by 32 to 1 by 128 each. The mask register can be used to prevent any subset of the 256 bits from contributing to the correlation score.

The output of the correlation array (correlation score) feeds the weight and sum logic, which gives added flexibility to the data format. In addition, an offset register is provided so that a preprogrammed value can be added to the correlation score. This result is then passed through a user programmable delay stage to the cascade summer. The delay stage simplifies the cascading of multiple correlators by compensating for the latency of previous correlators.

The Binary Correlator is configured by writing a set of control registers via a standard microprocessor interface. To simplify operation, both the control and reference registers are double buffered. This allows the user to load new mask and reference data while the current correlation is in progress.

#### Block Diagram

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper i.C. Handling Procedures. Copyright © Harris Corporation 1994

7-21

SPECIAL FUNCTION

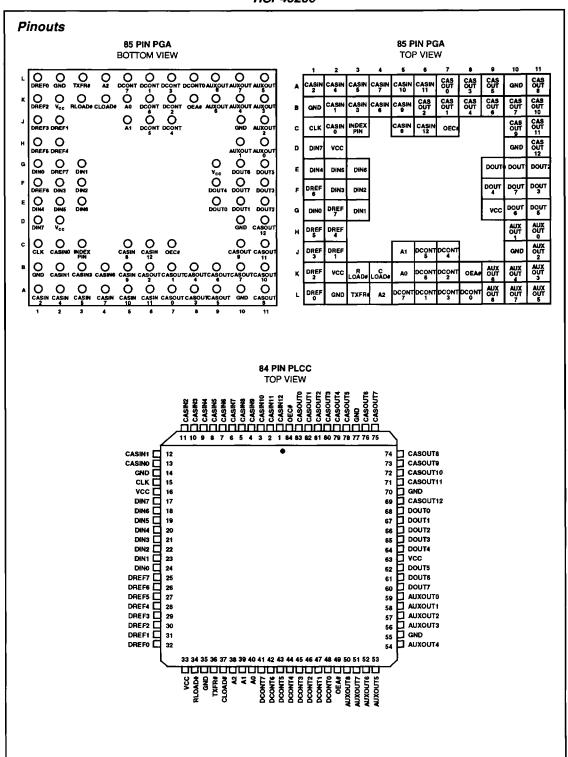

## Pin Description

| SYMBOL          | PLCC PIN NUMBER    | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>cc</sub> | 16, 33, 63         |        | The +5V power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| GND             | 14, 35, 55, 70, 77 |        | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DIN0-7          | 17-24              | Ī      | The DIN0-7 bus consists of eight single data input pins. The assignment of the active pins is determined by the configuration. Data is loaded synchronous to the rising edg of CLK. DIN0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| DOUT0-7         | 60-62, 64-68       | 0      | The DOUT0-7 bus is the data output of the correlation array. The format of the output is dependent on the window configuration and bit weighting. DOUT0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CLK             | 15                 | 1      | System clock. Positive edge triggered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| CASIN0-12       | 1-13               | l      | CASIN0-12 allows multiple correlators to be cascaded by connecting CASOUT0-12 one correlator to CASIN0-12 of another. The CASIN bus is added internally to the correlation score to form CASOUT. CASIN0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CASOUT0-12      | 69, 71-76, 78-83   | 0      | CASOUT0-12 is the output correlation score. This value is the delayed sum of all the 256 taps of one chip and CASIN0-12. When the part is configured to act as two independent correlators, CASOUT0-8 represents the correlation score for the first correlator while the second correlation score is available on the AUXOUT0-8 bus. In this configuration, the cascading feature is no longer an option. CASOUT0 is the LSE                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| OEC#            | 84                 | I      | OEC# is the output enable for CASOUT0-12. When OEC# is high, the output is three stated. Processing is not interrupted by this pin. (Active low.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| TXFR#           | 36                 | I      | TXFR# is a synchronous clock enable signal that allows the loading of the reference and mask inputs from the preload register to the correlation array. Data is transferred on the rising edge of CLK while TXFR# is low. (Active low.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DREF0-7         | 25-32              | I      | DREF0-7 is an 8-bit wide data reference input. This is the input data bus used to loa the reference data. RLOAD# going active initiates the loading of the reference registers. This input bus is used to load the reference registers of the correlation array. The maner in which the reference data is loaded is determined by the window configuration. the window configuration is 1 x 256, the reference bits are loaded one at a time over DREF7. When the HSP45256 is configured as an 8 x 32 array, the data is loaded intall stages in parallel. In this case, DREF7 is the reference data for the first stage and DREF0 is the reference data for the contents of the reference data registers are not affected by changing the window configuration. DREF0 is the LSB. |  |  |  |  |

| RLOAD#          | 34                 | į.     | RLOAD# enables loading of the reference registers. Data on DREF0-7 is loaded into the preload registers on the rising edge of RLOAD#. This data is transferred into the correlation array by TXFR#. (Active low.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| DCONT0-7        | 41-48              | l<br>I | DCONT0-7 is the control data input, which is used to load the mask bit for each tap a well as the configuration registers. The mask data is sequentially loaded into the eight stages in the same manner as the reference data. DCONT0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| CLOAD#          | 37                 | 1      | CLOAD# enables the loading of the data on DCONT0-7. The destination of this data i controlled by A0-2. (Active low.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| A0-2            | 38-40              | ı      | I A0-2 is a 3-bit address that determines what function will be performed when CLI is active. This address bus is set up with respect to the rising edge of the load si CLOAD#. A0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 8-OTUOXUA       | 50-54, 56-59       | 0      | AUXOUTO-8 is a 9-bit bus that provides either the data reference output or the 9-bit correlation score of the second correlator, depending on the configuration. When the user programs the chip to be two separate correlators, the score of the second correl tor is output on this bus. When the user has programmed the chip to be one correlator AUXOUTO-7 represents the reference data out, with the state of AUXOUTO-8 undefined. AUXOUTO is the LSB.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| OEA#            | 49                 | ١      | The OEA# signal is the output enable for the AUXOUT0-8 output. When OEA# is high the output is disabled. Processing is not interrupted by this pin. (Active low.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

#### Functional Description

The correlation array consists of eight 32-bit stages. The first stage receives data directly from input pin DIN7. The other seven stages receive input data from either an external data pin, DIN0-6, or from the shift register output of the previous stage, as determined by the Configuration Register. When the part is configured as a single correlator the sum of correlation score, offset register and cascade input appears on CASOUT0-12. Delayed versions of the data and reference inputs appear on DOUT0-7 and AUXOUT0-7, respectively. The input and output multiplexers of the correlation array are controlled together; for example, in a 1 x 256 correlation, the input data is loaded into DIN7 and the output appears on DOUT7. The configuration of the data bits, the length of the correlation (and in the two- dimensional data, the number of rows), is commonly called the correlation window.

#### Correlator Array

The core of the HSP45256 is the correlation array, which consists of eight 32-tap stages. A single correlator cell consists of an XNOR gate for the individual bit comparison; i.e., if the data and reference bits are either both high or both low, the output of the correlator cell is high. In addition, two latches, one for the reference and one for the control data path are contained in this cell. These latches are loaded from the preload registers on the rising edge of CLK when TXFR# is low so that the reference and mask values are updated without interrupting data processing.

The mask function is implemented with an AND gate. When a mask bit is a logic low, the corresponding correlator cell output is low.

The function performed by one correlation cell is:

$(D_{i,n} XNOR R_{i,n}) AND M_{i,n}$  where:

D<sub>i,n</sub> = Bit i of data register n

R<sub>i,n</sub> = Bit i of reference register n

M<sub>i,n</sub> = Bit i of mask register n

The reference and mask bits are loaded sequentially, N bits at a time, where N depends on the current configuration (See Table 3). New reference data is loaded on the rising edge of RLOAD# and new mask data is loaded on the rising edge of CLOAD#. The mask and reference bits are stored internally in shift registers, so that the mask and reference information that was loaded most recently will be used to process the newest data. When new information is loaded in, the previous contents of the mask and reference bits are shifted over by one sample, and the oldest information is lost. There are no registers in the multiplexer array (Figure 1), so the data on DOUTO-7 corresponds to the data in the last element of the correlation array. When monitoring DOUTO-7, AUXOUTO-8, and REFOUTO-7, only those bits listed in Table 3 are valid.

#### Weight and Sum Logic

The Weight and Sum Logic provides the bit weighting and final correlator score from the eight stages of the correlation array. For a 1 x 256 1-D configuration, the outputs of each of the stages are given a weight of 1 and then added together. In a 8 x 32 (8-bit data) configuration, the output of each stage will be shifted so that the output data represents an 8-bit word, with stage seven being the MSB.

The 13-bit offset register is loaded from the control data bus. Its output is added to the correlation score obtained from the correlator array. This sum then goes to the programmable delay register data input.

When the chip is configured as dual correlators, the user has the capability of loading two different offset values for the two correlators

The Programmable Delay Register sets the number of pipeline stages between the output of the weight and sum logic and the input of the Cascade Summer. This delay register is used to align the output of multiple correlators in cascaded configurations (See Applications). The number of delays is programmable from 1 to 16, allowing for up to 16 correlators to be cascaded. When the HSP45256 is configured as dual correlators, the delay must be set to 0000, which specifies a delay of 1.

#### Cascade Summer

This is used for cascading several correlators together. This value on this bus represents the correlation score from the previous HSP45256 that will be summed with the current score to provide the final correlation score. When several correlators are cascaded, the CASOUT0-12 of each of the other correlators is connected to the CASIN0-12 of the next correlator in the chain. The CASIN0-12 of the first chip is tied low. The following function represents the correlation score seen on CASOUT0-12 of each correlator:

CASOUT(n) = (W7 x CO7)(n-Delay) + (W6 x CO6)(n-Delay) + (W5 x CO5)(n-Delay) + (W4 x CO4)(n-Delay) + (W3 x CO3)(n-Delay) + (W2 x CO2)(n-Delay) + (W1 x CO1)(n-Delay) + (W0 x CO0)(n-Delay) + Offset (n-Delay) + CASIN.

where:

CO0-CO7 are the correlation score outputs out of the correlation stages; W0-W7 is the weight given to each stage; n-Delay represents the delay on the weighted and summed correlation score through the Programmable Delay Register; Offset is the value programmed into the Offset register; CASIN is the cascade input.

RLOAD# TXFR#

DIN7

DIN6

DREF6

DINO

DREFO.

MASK#

CONFIG# .

OFFAL# OFFAM#

OFFBL#

OFFBM#

DCONT0-7

CASINO-12 -

R07 [

RO1 |

DO

DO1

REG

DREF7

### **Control Registers**

The 3-bit address value, A0-2, is used to determine which internal register will be loaded with the data on DCONT0-7. The function is initiated when CLOAD# is brought low, and the register is loaded on the rising edge of CLOAD#. Table 1 indicates the function associated with each address. Table 2 shows the function of the bits in each of the registers.

#### TABLE 1. ADDRESS MAPPING

| A2 | <b>A</b> 1 | A0 | DESTINATION                              |

|----|------------|----|------------------------------------------|

| 0  | 0          | 0  | Mask Register                            |

| 0  | 0          | 1  | Configuration Register                   |

| 0  | 1          | 0  | Offset Register A-Most Significant Bits  |

| 0  | 1          | 1  | Offset Register A-Least Significant Bits |

| 1  | 0          | 0  | Programmable Delay Register              |

| 1  | 0          | 1  | Offset Register B-Most Significant Bits  |

| 1  | 1          | 0  | Offset Register B-Least Significant Bits |

| 1  | 1          | 1  | Reserved                                 |

|                                                                              |                                                                                      | TA                                                                                                                             | ABLE 2. CONTR                                                                | OL REGISTER B                                                   | ITS                                 |                                        |                   |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------|----------------------------------------|-------------------|

| A0-2 = 000 Mas                                                               | sk Register                                                                          |                                                                                                                                |                                                                              |                                                                 |                                     |                                        |                   |

| MR7                                                                          | MR6                                                                                  | MR5                                                                                                                            | MR4                                                                          | MR3                                                             | MR2                                 | MR1                                    | MR0               |

|                                                                              |                                                                                      | sk register bit N =<br>g register on the ri                                                                                    |                                                                              |                                                                 |                                     |                                        |                   |

| A0-2 = 001 Co                                                                | ofiguration Regis                                                                    | ster                                                                                                                           |                                                                              |                                                                 |                                     | _                                      |                   |

| -                                                                            | •                                                                                    | тс                                                                                                                             | CONFIG4                                                                      | CONFIG3                                                         | CONFIG2                             | CONFIG1                                | CONFIG0           |

| TC: Configures<br>current configu                                            |                                                                                      | 's complement inp                                                                                                              | out. Inverts the MS                                                          | 6B of the input da                                              | ta, where the pos                   | ition of the MSB o                     | lepends on the    |

| as one correlate<br>with the first cor-<br>dual correlators<br>CONFIG2-3: Co | or with the correlat<br>rrelator's score av<br>, the Programmal<br>ontrol the number | sets up the HSP4<br>ion score available<br>railable on CASOU<br>ble Delay must be<br>of data bits to be<br>NFIGO represent the | on CASOUT0-12<br>JT0-8 and the sec<br>set to 0000 for a<br>correlated. See T | !. When CONFIG-<br>cond score availal<br>delay of 1,<br>able 3. | 4 = 1, the HSP452<br>ble on AUXOUTO | 56 is configured a<br>8. When the chip | s dual correlator |

| A0-2 = 010 MS                                                                | Offset Register                                                                      | Α                                                                                                                              |                                                                              |                                                                 |                                     |                                        |                   |

| -                                                                            |                                                                                      |                                                                                                                                | OFFA12                                                                       | OFFA11                                                          | OFFA10                              | OFFA9                                  | OFFA8             |

| OFFA8-12: Mo:                                                                | st significant bits                                                                  | of Offset Register                                                                                                             | A. This is the regi                                                          | ster used in singl                                              | e correlator mode                   |                                        | _                 |

| A0-2 = 011 LS                                                                | Offset Register                                                                      | A                                                                                                                              |                                                                              |                                                                 |                                     |                                        |                   |

| OFFA7                                                                        | OFFA6                                                                                | OFFA5                                                                                                                          | OFFA4                                                                        | OFFA3                                                           | OFFA2                               | OFFA1                                  | OFFA0             |

| OFFA0-7: Leas                                                                | t significant bits o                                                                 | f Offset Register /                                                                                                            | ٨.                                                                           | <b>.</b>                                                        | ·                                   |                                        |                   |

| A0-2 = 100 Pro                                                               | grammable Dela                                                                       | ıy                                                                                                                             |                                                                              |                                                                 |                                     | _                                      |                   |

|                                                                              | -                                                                                    |                                                                                                                                |                                                                              | PDELAY3                                                         | PDELAY2                             | PDELAY1                                | PDELAY0           |

|                                                                              |                                                                                      | delay from the we                                                                                                              |                                                                              |                                                                 |                                     | per of delays is 1-                    | 16, with PDELA    |

| A0-2 = 101 MS                                                                | Offset Register                                                                      | В                                                                                                                              |                                                                              |                                                                 |                                     |                                        |                   |

| -                                                                            | -                                                                                    |                                                                                                                                | -                                                                            |                                                                 | -                                   | -                                      | OFFSETB8          |

| OFFB8: Most s<br>the AUXOUT p                                                |                                                                                      | fset Register B. In                                                                                                            | dual correlator m                                                            | ode, this register                                              | is used for the co                  | rrelator whose ou                      | itput appears on  |

| A0-2 = 110 LS                                                                | Offset Register                                                                      | B                                                                                                                              |                                                                              |                                                                 |                                     |                                        |                   |

| OFFB7                                                                        | OFFB6                                                                                | OFFB5                                                                                                                          | OFFB4                                                                        | OFFB3                                                           | OFFB2                               | OFFB1                                  | OFFB0             |

| OFFB0-7: Leas                                                                | t significant bits o                                                                 | f Offset Register i                                                                                                            | 3.                                                                           |                                                                 |                                     |                                        |                   |

|   | TABLE 3. CONFIGURATION SETUP |       |       |    |                  |              |      |        |                 |              |              |              |             |           |     |     |     |        |        |        |     |        |

|---|------------------------------|-------|-------|----|------------------|--------------|------|--------|-----------------|--------------|--------------|--------------|-------------|-----------|-----|-----|-----|--------|--------|--------|-----|--------|

|   | CON                          | FIGUR | ATION |    | NO.<br>OF        |              |      |        |                 | ACTIVE       | INPUTS       | AC           | TIVE OUTPU  | TS        |     |     | ου  | TPUT V | VEIGHT | ING    |     |        |

| 4 | 3                            | 2     | 1     | 0  | CORRE-<br>LATORS | DATA<br>BITS | ROWS | LENGTH | CORRE-<br>LATOR | DIN          | DREF         | DOUT         | AUXOUT      | CASOUT    | CO7 | CO6 | COS | CO4    | СОЗ    | CO2    | CO1 | COO    |

| 0 | 0                            | 0     | 0     | 0  | 1                | 1            | 1    | 256    |                 | 7            | 7            | 7            | 7           | 12-0      | 1   | 1   | 1   | 1      | 1      | 1      | 1   | 1      |

| 0 | 0                            | ٥     | 0     | 1  | 1                | 1            | 2    | 128    | •               | 7, 3         | 7, 3         | 7, 3         | 7, 3        | 12-0      | 1   | 1   | 1   | 1      | 1      | 1      | 1   | 1      |

| 0 | 0                            | 0     | 1     | 0  | 1                | 1            | 4    | 64     | •               | 7, 5, 3, 1   | 7, 5, 3, 1   | 7, 5, 3, 1   | 7, 5, 3 , 1 | 12-0      | 1   | 1   | 1   | 1      | 1      | 1      | 1   | 1      |

| 0 | 0                            | 0     | 1     | 1  | 1                | 1            | 8    | 32     | •               | 7-0          | 7-0          | 7-0          | 7-0         | 12-0      | 1   | 1   | 1   | -      | 1      | 1      | 1   | 1      |

| 0 | 0                            | 1     | 0     | 1_ | 1                | 2            | 1    | 128    | •               | 7, 3         | 7            | 7, 3         | 7, 3        | 12-0      | 2   | 2   | 2   | 2      | 1      | 1      | 1   | 1      |

| 0 | 0                            | 1     | 1     | 0  | 1                | 2            | 2    | 64     |                 | 7, 5, 3, 1   | 7, 5         | 7, 5, 3, 1   | 7, 5, 3, 1  | 12-0      | 2   | 2   | 2   | 2      | 1      | -      | 1   | 1      |

| 0 | 0                            | 1     | 1     | 1  | 1                | 2            | 4    | 32     |                 | 7-0          | 7, 6, 5, 4   | 7-0          | 7-0         | 12-0      | 2   | 2   | 2   | 2      | 1      | 1      | 1   | 1      |

| 0 | 1                            | 0     | 1     | 0  | 1                | 4            | 1    | 64     |                 | 7, 5, 3, 1   | 7            | 7, 5, 3, 1   | 7, 5, 3, 1  | 12-0      | 8   | 8   | 2   | 2      | 4      | 4      | 1   | 1      |

| 0 | 1                            | 0     | 1     | 1  | 1                | 4            | 2    | 32     | -               | 7-0          | 7, 6         | 7-0          | 7-0         | 12-0      | 8   | 8   | 2   | 2      | 4      | 4      | 1   | 1      |

| 0 | 1                            | 1     | 1     | 1  | 1                | 8            | 1    | 32     |                 | 7-0          | 7            | 7-0          | 7-0         | 12-0      | 128 | 8   | 32  | 4      | 64     | 2      | 16  | 1      |

| 1 | 0                            | 0     | 0     | 1  | 2                | 1            | 1    | 128    | A<br>B          | 7<br>3       | 7<br>3       | 7<br>3       | -<br>8-0    | 12-0<br>- | 1   | 1   | 1 - | 1 -    | 1      | 1      | 1   | -<br>1 |

| 1 | 0                            | 0     | 1     | 0  | 2                | 1            | 2    | 64     | A<br>B          | 7, 5<br>3, 1 | 7, 5<br>3, 1 | 7, 5<br>3, 1 | -<br>8-0    | 12-0      | 1 - | 1   | 1 - | 1 -    | 1      | 1      | 1   | 1      |

| 1 | 0                            | 0     | 1     | 1  | 2                | 1            | 4    | 32     | A<br>B          | 7-4<br>3-0   | 7-4<br>3-0   | 7-4<br>3-0   | 8-0         | 12-0      | 1   | 1 - | 1 - | 1 -    | 1      | 1      | 1   | 1      |

| 1 | 0                            | 1     | 1     | 0  | 2                | 2            | 1    | 64     | A<br>B          | 7, 5<br>3, 1 | 7            | 7, 5<br>3, 1 | 8-0         | 12-0      | 5   | 2   | 1 - | 1      | 2      | 2      | 1   | 1      |

| 1 | 0                            | 1     | 1     | 1  | 2                | 2            | 2    | 32     | A<br>B          | 7-4<br>3-0   | 7, 6<br>3, 2 | 7-4<br>3-0   | 8-0         | 12-0      | 2   | 2   | 1 - | 1      | 2      | 2      | 1   | 1      |

| 1 | 1                            | 0     | 1     | 1  | 2                | 4            | 1    | 32     | A<br>B          | 7-4<br>3-0   | 7            | 7-4<br>3-0   | -<br>8-0    | 12-0      | 8   | 2   | 4   | 1      | - 8    | -<br>2 | 4   | 1      |

7-27

During reference register loading, the 8-bits, DREF0-7 are used as reference data inputs. The falling edge of RLOAD# initiates reference data loading; when RLOAD# returns high, the data on DREF0-7 is latched into the selected correlation stages. The active bits on DREF0-7 are controlled by the current configuration.

The window configuration is determined by the state of control signals upon programming the control register. Table 3 represents the programming information required for each window configuration. In Table 3, note that the data listed for Output Weighting refers to the weights given to each of the Correlation Sum Outputs (COO-7 in Figure 1).

During initialization, the loading configuration for the reference data is set by the user. Table 3 shows the loading options. These load controls specify whether the reference data for a given stage comes from the shift register output of the previous stage or from an external data pin.

#### **Applications**

#### Single HSP45256 - 1-Bit Data, 256 Samples

A 1 x 256 (1-D configuration) correlation requires only 1 HSP45256. To initialize the correlator, all the reference bits, control bits, the delay value of the variable delay, and the window configuration must be specified.

TABLE 4. REGISTER CONTENTS FOR 1 X 256 CORRELATOR WITH EQUAL WEIGHTING

| A0-2 | DCONT0-7 | NOTES                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 001  | 00000000 | 1 256-tap correlator: 1 x 256 window configuration, reference loaded from DREF7, eight stages weighted equally, DIN 7 and DOUT7 are the data input and output, respectively. |  |  |  |  |  |  |  |  |  |

| 010  | 00000000 | Offset Register A = 0                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| 011  | 00000000 |                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 100  | 00000000 | Programmable Delay = 0                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| 101  | 00000000 | Offset Register B = 0 (Loading of this                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| 110  | 00000000 | register optional in this mode.)                                                                                                                                             |  |  |  |  |  |  |  |  |  |

The loading of the reference and mask registers may be done simultaneously by setting A0-2 = 000, setting the DREF and DCONT inputs to their proper values and pulsing RLOAD# and CLOAD# low. In this configuration, DREF7 loads the reference data and DCONT7 loads the mask information; both sets of data are loaded serially. It will take 256 load pulses (RLOAD#) to load the reference array, and 256 CLOAD# pulses to load the mask array. Upon completion of the mask and register loading, TXFR# is pulsed low, which transfers the reference and control data from the preload registers to the reference and mask registers, updating the data that will be used in the correlation. Reference and mask data can be loaded more quickly by configuring the correlator as an 8 row by 32 sample array, loading the bits eight at a time, then changing the configuration back to 1 x 256 to perform the correlation.

#### Single HSP45256 - 8-Bit Data, 32 Samples

An 8  $\times$  32 correlation also requires only 1 HSP45256. To initialize the correlator, all the reference bits, control bits, the value of the programmable delay, and the window configuration must be specified.

Again, the loading of the reference and mask registers can be done simultaneously. Due to the programming initialization, DREF0-7 are used to load the reference data 8-bits at a time. It will take 32 load pulses each of RLOAD# and CLOAD# to load both arrays. Upon completion of the mask and register loading, TXFR# is pulsed low, which transfers the reference and control data from the preload registers to the registers that store the active data.

TABLE 5. REGISTER LOADING FOR 8 X 32 CORRELATOR WITH BINARY WEIGHTING

| A0-2 | DCONT0-7 | NOTES                                                                                                                                                                                                                                                                              |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 001  | 00001111 | 1 256-tap correlator; 8 x 32 window configuration, 8-bit data stream; reference register is loaded from DREF7 for all stages. Correlator score = $(128 \times CO7) + (64 \times CO3) + (32 \times CO5) + (16 \times CO1) + (8 \times CO6) + (4 \times CO4) + (2 \times CO2) + CO0$ |

| 010  | 00000000 | Offset Register A = 000000010000                                                                                                                                                                                                                                                   |

| 011  | 00010000 |                                                                                                                                                                                                                                                                                    |

| 100  | 00000000 | Programmable Delay = 0                                                                                                                                                                                                                                                             |

| 101  | 00000000 | Offset Register B = 0 (Loading optional in                                                                                                                                                                                                                                         |

| 110  | 00000000 | this mode.)                                                                                                                                                                                                                                                                        |

This configuration performs correlation of an 8-bit number with a 1-bit reference. Each byte out of the correlation array gives an 8-bit level of confidence that the data corresponds to the reference. The correlation score is the sum of these confidence levels.

# Single HSP45256 - Dual Correlators, 2-Bit Data, 64 Samples

Dual 2 x 64 correlators require only one HSP45256. To initialize the correlator, all the reference bits, control bits, the delay value of the variable delay, and the window configuration must be specified.

In this example, each of the dual correlators compares 2-bit data to a 1-bit reference. It will take 64 load pulses (RLOAD#/CLOAD#) to completely load the reference and mask registers in the array. The programmable delay must be set to 0 for the output of the two correlators to be aligned.

TABLE 6. REGISTER LOADING FOR DUAL 2 X 64

CORRELATORS WITH EQUAL WEIGHTING

| AO-2 | DCONT0-7 | NOTES                                                                                                                                                                                                                                                                                |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70-2 | DCON10-7 | NOTES                                                                                                                                                                                                                                                                                |

| 001  | 00010010 | Dual correlators: each 2 bit data, 64 taps; reference register for correlation A is loaded from DREF7 and DREF5, the reference register for correlator B is loaded from DREF3 and DREF1. Correlator #1 = 2x C07 + 2 x C06 + C05 + C04, correlator #2 = 2 x C03 + 2x C02 + C01 + C00. |

| 010  | 00000000 | Offset Register A = 000000010000                                                                                                                                                                                                                                                     |

| 011  | 00010000 |                                                                                                                                                                                                                                                                                      |

| 100  | 00000000 | Programmable Delay = 0                                                                                                                                                                                                                                                               |

| 101  | 00000000 | Offset Register B = 0                                                                                                                                                                                                                                                                |

| 110  | 00000000 | ]                                                                                                                                                                                                                                                                                    |

#### Cascading Correlators

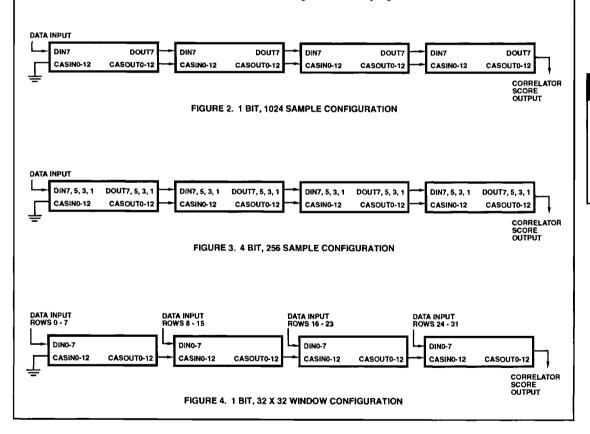

Correlators can be cascaded in either a serial or parallel fashion. Longer correlations can be achieved by connecting several correlators together as shown in Figure 2. Each correlator is in a one data bit, one row, 256 tap configuration. The number of bits of significance at the CASOUT output of each correlator builds up from one correlation to the next.

that is, the maximum score out of the first correlator is 256, the maximum output of the second correlator is 512, etc. In this configuration, the maximum length of the correlation is 4096. This would be implemented with 16 HSP45256's. The programmable delay register in the first correlator would be set for one delay, the second would be set for two, and so on, with the final HSP45256 being set for a delay of 16.

Correlations of more bits can be calculated by connecting CASOUT of each chip to the CASIN of the following chip (Figure 3). The data on the CASOUT lines accumulates in a similar manner as in the 1 x 256 mode, except that the maximum output of the first correlator is decimal 960, (hexadecimal 3C0); in the general case, the maximum number of correlators that can be cascaded in this manner is eight, since the maximum output of the last one would be 1E00, which nearly uses up the 13-bit range of the cascade summer. More parts could be cascaded together if some bits are to be masked out or if the user has a prior knowledge of the maximum value of the correlation score. As before, the delay in the first correlator would be set to one, the second correlator would be set for a delay of two, and so on.

Multiple HSP45256's can be cascaded for two dimensional one bit data (Figure 4). The maximum output for each chip is the same as in the 1 x 256 case; the only difference is in the manner in which the correlators are connected. The programmable delay registers would be set as before.

#### Reloading Data During Operation

RLOAD# and CLOAD# are asynchronous signals that are designed to be driven by the memory interface signals of a microprocessor. TXFR# is synchronized to CLK so that the mask or reference data is updated on a specific clock cycle. In the normal mode of operation, the user loads the reference and mask memories, then pulses TXFR# to use that data. The correlator uses the new mask or reference information immediately. Loading of the reference and mask data remains asynchronous as long as there is at least one cycle of CLK between the rising edge of RLOAD# or CLOAD# and the TXFR# pulse.

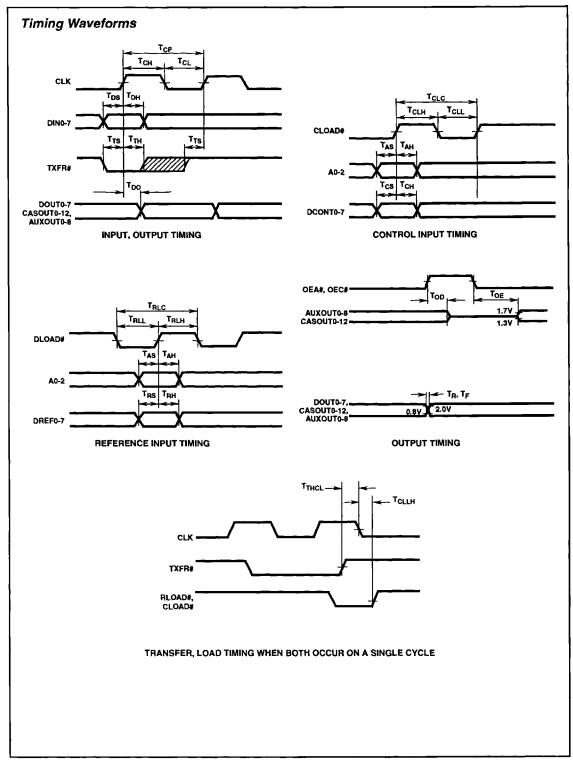

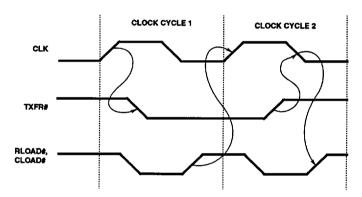

If the system timing makes it necessary for TXFR# and RLOAD# and/or CLOAD# to be active during the same clock cycle, then they must be treated as synchronous signals; the timing for this case is shown in Figure 5 and given in the AC Timing Specifications (T<sub>THCL</sub> and T<sub>CLLH</sub>). In this example, data is loaded during clock cycle 1 and transferred on the rising edge of CLK that occurs in clock cycle two. Another set of data is loaded during clock cycle 2, which will be transferred by a later TXFR# pulse. The sequence of events is as follows:

- In clock cycle 1, TXFR# becomes active at least T<sub>TH</sub> nanoseconds after the rising edge of CLK.

- RLOAD and/or CLOAD# pulses low; the timing is not critical as long as its rising edge occurs before the end of clock cycle 1. If this condition is not met, it is undetermined whether the data loaded by this pulse will be transferred by the current TXFR# pulse.

- The rising edge of TXFR# occurs while CLK is high during clock cycle 2. The margin between the rising edge of TXFR# and the falling edge of CLK is defined by T<sub>THCL</sub>.

- RLOAD# and/or CLOAD# pulses low. The rising edge of RLOAD# and CLOAD# must occur after the falling edge of CLK. The margin between the two is defined by T<sub>CLLH</sub>.

The time from the rising edge of TXFR# to the falling edge of CLK must be greater than  $T_{THCL}$ , and the time from the falling edge of CLK to the rising edge of RLOAD# or CLOAD# must be greater than  $T_{\rm s}$ . If this timing is violated, the data being transferred by the TXFR# pulse shown may or may not include the data loaded in clock cycle 2.

FIGURE 5. LOADING AND TRANSFERRING DATA DURING THE SAME CLOCK CYCLE

#### **Absolute Maximum Ratings**

| Supply Voltage+8.0V                                            | Thermal Resistance                        | $\theta_{JA}$ | $\theta_{JC}$ |

|----------------------------------------------------------------|-------------------------------------------|---------------|---------------|

| Input, Output or I/O Voltage GND-0.5V to V <sub>CC</sub> +0.5V | PLCC Package                              | 34°C/W        | 11.3°C/W      |

| Storage Temperature Range65°C to +150°C                        | PGA Package                               | 36°C/W        | 10°C/W        |

| Junction Temperature+150°C (PLCC), +175°C (PGA)                | Maximum Package Power Dissipation at +125 | °C            |               |

| Lead Temperature (Soldering 10s)+300°C                         | PLCC Package                              |               | 2.2W          |

| ESD Classification                                             | PGA Package                               |               | 2.9W          |

|                                                                | Gate Count                                | 13            | 3,000 Gates   |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Operating Conditions**

#### **DC Electrical Specifications**

| PARAMETER                      | SYMBOL           | MIN | MAX | UNITS | TEST CONDITIONS                                                                                   |

|--------------------------------|------------------|-----|-----|-------|---------------------------------------------------------------------------------------------------|

| Logical One Input Voltage      | V <sub>IH</sub>  | 2.0 |     | ٧     | V <sub>CC</sub> ≈ 5.25V                                                                           |

| Logical Zero Input Voltage     | V <sub>IL</sub>  | -   | 0.8 | V     | V <sub>CC</sub> ≈ 4.75V                                                                           |

| High Level Clock Input         | V <sub>IHC</sub> | 3.0 | -   | ٧     | V <sub>CC</sub> ≈ 5.25V                                                                           |

| Low Level Clock Input          | V <sub>ILC</sub> | -   | 0.8 | V     | V <sub>CC</sub> ≈ 4.75V                                                                           |

| Output High Voltage            | V <sub>OH</sub>  | 2.6 | -   | ٧     | I <sub>OH</sub> = 400μA, V <sub>CC</sub> = 4.75V                                                  |

| Output Low Voltage             | V <sub>OL</sub>  |     | 0.4 | V     | I <sub>OL</sub> = +2.0mA, V <sub>CC</sub> = 4.75V                                                 |

| Input Leakage Current          | l <sub>l</sub>   | -10 | 10  | μА    | V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.25V                                 |

| Output Leakage Current         | ю                | -10 | 10  | μА    | V <sub>OUT</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.25V                                |

| Standby Power Supply Current   | Iccss            | -   | 500 | μА    | V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.25V, Note 3                         |

| Operating Power Supply Current | ICCOP            | -   | 179 | mA    | f = 25.6MHz, V <sub>IN</sub> = V <sub>CC</sub> or GND, V <sub>CC</sub> = 5.25V,<br>Note 1, Note 3 |

#### Capacitance (T<sub>A</sub> = 25°C, Note 2)

| PARAMETER          | SYMBOL          | MIN | MAX | UNITS | TEST CONDITIONS                                                                               |

|--------------------|-----------------|-----|-----|-------|-----------------------------------------------------------------------------------------------|

| Input Capacitance  | C <sub>IN</sub> | -   | 10  | рF    | Frequency = 1MHz, V <sub>CC</sub> = Open<br>All measurements are referenced to device ground. |

| Output Capacitance | co              | -   | 10  | pF    |                                                                                               |

#### NOTES:

- 1. Power supply current is proportional to operating frequency. Typical rating for ICCOP is 7mA/MHz.

- 2. Not tested, but characterized at initial design and at major process/design changes.

- 3. Output load per test load circuit and  $C_L = 40 pF$ .

AC Electrical Specifications ( $V_{CC} = 5.0V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to +70°C, Note 1)

|                                   |                   | 33/ | MHz | 25.6 | MHz |       |                 |  |

|-----------------------------------|-------------------|-----|-----|------|-----|-------|-----------------|--|

| PARAMETER                         | SYMBOL            | MIN | MAX | MIN  | MAX | UNITS | TEST CONDITIONS |  |

| CLK Period                        | T <sub>CP</sub>   | 30  | -   | 39   | -   | ns    |                 |  |

| CLK High                          | T <sub>CH</sub>   | 12  | -   | 15   | -   | ns    |                 |  |

| CLK Low                           | T <sub>CL</sub>   | 12  |     | 15   | -   | ns    |                 |  |

| Set-Up Time DIN to CLK High       | Tos               | 12  | -   | 13   |     | ns    |                 |  |

| Hold Time CLK High to DIN         | T <sub>DH</sub>   | 0   |     | 0    |     | ns    |                 |  |

| TXFR# Set-Up Time                 | T <sub>TS</sub>   | 12  | -   | 13   | -   | ns    |                 |  |

| TXFR# Hold Time                   | Ттн               | 0   | -   | 0    |     | ns    |                 |  |

| Output Delay DOUT, AUXOUT, CASOUT | T <sub>DO</sub>   | -   | 15  |      | 20  | ns    |                 |  |

| CLOAD# Cycle Time                 | T <sub>CLC</sub>  | 30  | -   | 39   | -   | ns    |                 |  |

| CLOAD# High                       | T <sub>CLH</sub>  | 12  | -   | 15   | -   | ns    |                 |  |

| CLOAD# Low                        | T <sub>CLL</sub>  | 12  | -   | 15   | Γ - | ns    |                 |  |

| Set-Up Time, A to RLOAD#, CLOAD#  | T <sub>AS</sub>   | 12  | ·   | 13   | · · | ns    |                 |  |

| Hold Time, RLOAD#, CLOAD# to A    | T <sub>AH</sub>   | 0   | -   | 0    | -   | ns    |                 |  |

| RLOAD# Cycle Time                 | T <sub>RLC</sub>  | 30  | -   | 39   | -   | ns    |                 |  |

| RLOAD# High                       | T <sub>RLH</sub>  | 12  | -   | 15   | -   | ns    |                 |  |

| RLOAD# Low                        | T <sub>RLL</sub>  | 12  | -   | 15   | -   | ns    |                 |  |

| Set-Up Time, DCONT to CLOAD#      | T <sub>DCS</sub>  | 12  | -   | 13   | -   | ns    |                 |  |

| Hold Time, CLOAD# to DCONT        | T <sub>DCH</sub>  | 0   | -   | 0    | -   | ns    |                 |  |

| Set-Up Time, DREF to RLOAD#       | T <sub>RS</sub>   | 12  | -   | 13   | •   | ns    |                 |  |

| Hold Time, RLOAD# to DREF         | T <sub>RH</sub>   | 0   | -   | 0    | -   | ns    |                 |  |

| Output Enable Time                | Toe               |     | 15  |      | 15  | ns    |                 |  |

| Output Disable Time               | Top               |     | 15  |      | 15  | ns    | Note 2          |  |

| Output Rise, Fall Time            | T <sub>RF</sub>   |     | 6   |      | 6   | ns    | Note 2          |  |

| TXFR# High to CLK Low             | T <sub>THCL</sub> | 3   | -   | 3    |     | ns    | Note 2          |  |

| CLK Low to RLOAD#, CLOAD# High    | T <sub>CLLH</sub> | 1   | -   | 1    | -   | ns    | Note 2          |  |

#### NOTES:

- AC testing is performed as follows: Input levels (CLK Input) 4.0V and 0V; Input levels (all other inputs) 0V and 3.0V; Timing reference levels (CLK) 2.0V; All others 1.5V. Output load per test load circuit with C<sub>L</sub> = 40pF. Output transition is measured at V<sub>OH</sub> > 1.5V and V<sub>OL</sub> < 1.5V.</li>

- Controlled via design or process parameters and not directly tested. Characterized upon initial design and after major process and/or design changes.

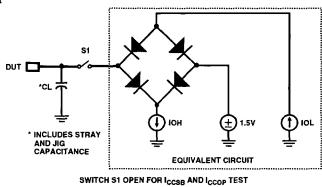

#### Test Load Circuit