# Si5388/89 Data Short

# Network Synchronizer Clocks for IEEE 1588™

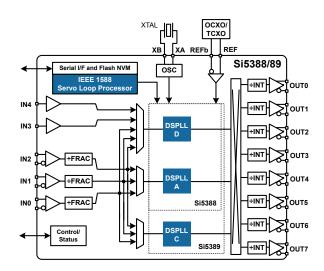

The multi-DSPLL Si5388/89 network synchronizer clocks combined with optional Accu-Time™ 1588 software offer a complete solution for IEEE 1588v2 and SyncE phase and frequency synchronization. AccuTime™ 1588 software consists of a servo algorithm internal to the Si5388/89 clock and is paired with a protocol stack that runs on the host processor.

The Si5388/89 targets compact or centralized "pizza box" architectures requiring low jitter. The device offers up to three independent DSPLLs, each capable of supporting IEEE 1588 high resolution DCO control, G.8262 SyncE clock filtering, or general-purpose clocking. The unique design of the Si5388/89 includes a dedicated TCXO/OCXO reference interface with built-in jitter cleaning that will not degrade the output performance of the clock.

The Si5388/89 supports free-run, synchronous, and holdover modes as well as enhanced hitless switching, minimizing the phase transients associated with switching between input clocks. These devices are programmable via a serial interface with in-circuit programmable non-volatile memory (NVM), so they always power up with a known frequency configuration. Configuring and programming the Si5388/89 is easy with Skyworks' ClockBuilder™ Pro software.

### **Applications**

- Telecom Boundary Clock and Telecom-Time Slave Clock (T-BC, T-TSC) ITU-T G.8273.2

- Telecom Boundary Clock for Partial Timing Support (T-BC-P, T-TSC-P) ITU-T G.8273.4

- Synchronous Ethernet (SyncE) ITU-T G.8262 and Enhanced Synchronous Ethernet (eEEC) G.8262.1

- Stratum 3/3E, G.812, G.813 network synchronization

- Frequency synchronization in packet networks ITU-T G.8261

#### **KEY FEATURES**

#### Si5388/89

- Up to three independent DSPLLs in a single IC supporting SyncE, IEEE 1588 DCO, General Clocking

- · Input frequency range:

- Dedicated External crystal input: 48–54 MHz

- Dedicated REF clock input: 5–250 MHz

- 3 Differential clock inputs: 8 kHz–750 MHz

- 2 LVCMOS clocks inputs: 1PPS, 8 kHz– 250 MHz

- · Output frequency range:

- 8 Differential outputs: 1 Hz, 100 Hz– 718.5 MHz

- 16 LVCMOS: 1 Hz, 100 Hz-250 MHz

- · Ultra-low jitter: 90 fs rms typ

- Enhanced hitless switching minimizes output phase transients

- Dedicated Input and DSPLL for Holdover Reference

## AccuTime™ 1588 Software

- · Reference Design Support

- · ORAN compliant

- Embedded IEEE 1588 servo loop processing on Si5388/89

- IEEE 1588 software protocol stack runs on host processor

- Unique servo algorithm has statistical packet selection, which dynamically adjusts to changing network load conditions to mitigate PDV effects

## 1. Pin Descriptions

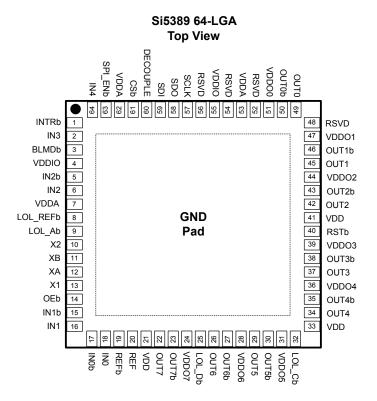

Figure 1.1. Si5389 Pins

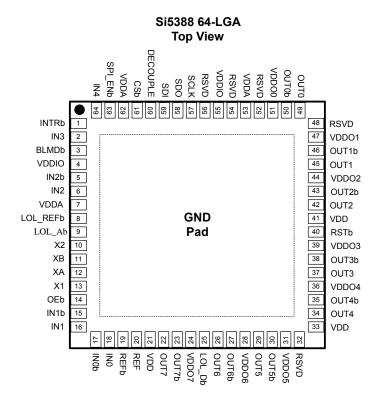

Figure 1.2. Si5388 Pins

Table 1.1. Si5388/89 Pin Descriptions

| Pin Name      | Pin Number | Pin Type | Function                                                                                                                                                                                                                |  |  |  |  |

|---------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Input Clocks  |            |          |                                                                                                                                                                                                                         |  |  |  |  |

| XA            | 12         | 1        | Crystal Input. Input pin for external crystal (XTAL).                                                                                                                                                                   |  |  |  |  |

| ХВ            | 11         | I        |                                                                                                                                                                                                                         |  |  |  |  |

| X1            | 13         | 1        | XTAL Shield. Connect these pins directly to the XTAL ground pins. The XTAL ground pins should be separated from the PCB ground plane. Refer to the Si5388/89 Reference Manual for layou guidelines.                     |  |  |  |  |

| X2            | 10         | I        |                                                                                                                                                                                                                         |  |  |  |  |

| IN0           | 18         | 1        |                                                                                                                                                                                                                         |  |  |  |  |

| IN0b          | 17         | 1        | Clock Inputs. IN0-IN2 accept an input clock for synchronizing the device. They support both differential and single-ended clock                                                                                         |  |  |  |  |

| IN1           | 16         | 1        | signals. Refer to Input Configuration and Terminations input termination options. These pins are high-impedance and must be ter-                                                                                        |  |  |  |  |

| IN1b          | 15         | 1        | minated externally. The negative side of the differential input must                                                                                                                                                    |  |  |  |  |

| IN2           | 6          | 1        | be grounded through a capacitor when accepting a single-ended clock. IN3 and IN4 only support single ended LVCMOS signals.                                                                                              |  |  |  |  |

| IN2b          | 5          | 1        | These pins are high-impedance and must be terminated externally. INO-IN2 can be disabled by register configuration and the pins                                                                                         |  |  |  |  |

| IN3           | 2          | I        | left unconnected if unused. IN3 and IN4 must be externally pulled                                                                                                                                                       |  |  |  |  |

| IN4           | 64         | I        | low when unused.                                                                                                                                                                                                        |  |  |  |  |

| REF           | 20         | I        | Reference Input. This input accepts a reference clock from a                                                                                                                                                            |  |  |  |  |

| REFb          | 19         | ı        | stable source (e.g., TCXO or OCXO) that is used to determine free-run frequency accuracy and stability during free-run or hold over of the DSPLL or DCO. These inputs can accept differential single-ended connections. |  |  |  |  |

| Output Clocks |            |          |                                                                                                                                                                                                                         |  |  |  |  |

| OUT0          | 49         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT0b         | 50         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT1          | 45         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT1b         | 46         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT2          | 42         | 0        | Output Clocks. These output clocks support a programmable                                                                                                                                                               |  |  |  |  |

| OUT2b         | 43         | 0        | signal amplitude and common mode voltage. Desired output signal format is configurable using register control. Termination rec-                                                                                         |  |  |  |  |

| OUT3          | 37         | 0        | ommendations are provided in . Unused outputs should be left unconnected.                                                                                                                                               |  |  |  |  |

| OUT3b         | 38         | 0        | 1 Hz/1PPS only available on outputs 5 and 7. Some restrictions                                                                                                                                                          |  |  |  |  |

| OUT4          | 34         | 0        | apply to output 6 when using outputs 5 and 7 for the special 1 Hz/1PPS output function. Please review section carefully before                                                                                          |  |  |  |  |

| OUT4b         | 35         | 0        | assigning output clocks                                                                                                                                                                                                 |  |  |  |  |

| OUT5          | 29         | 0        | If OUT1 is not used, it is recommended to connect its pin to test                                                                                                                                                       |  |  |  |  |

| OUT5b         | 30         | 0        | points that can be used for advanced factory diagnostic features useful in technical support.                                                                                                                           |  |  |  |  |

| OUT6          | 26         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT6b         | 27         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT7          | 22         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| OUT7b         | 23         | 0        |                                                                                                                                                                                                                         |  |  |  |  |

| Pin Name                | Pin Number | Pin Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------------------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Serial Interface        |            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| SPI_ENb                 | 63         | ı        | <b>SPI Enable</b> . This pin should always be tied low to GND to enable the serial interface. Do not connect this pin to VDD or leave it unconnected.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| SDI                     | 59         | I        | Serial Data Interface. The serial data input (SDI) pin.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SDO                     | 58         | 0        | Serial Data Output. The serial data output (SDO) pin.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| SCLK                    | 57         | I        | Serial Clock Input. The serial clock input for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| CSb                     | 61         | I        | Serial Interface Chip Select. The SPI chip select input pin (active low).                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Control/Status          |            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| INTRb                   | 1          | 0        | Interrupt. This pin is asserted low when a change in device status has occurred. It should be left unconnected when not in use.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| RSTb                    | 40         | I        | <b>Device Reset.</b> To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. Drivers with large leakage current may require the use of an external pullup to VDDIO. Regardless of the pullup used (internal vs. external) users should ensure the driver can tolerate +3.3V levels (VDDIO).                                                                            |  |  |  |

|                         |            |          | The RSTb pin includes an internal pull-up resistor to VDDIO and can therefore be left unconnected if no external reset source is required. Also connected to the RSTb line is a low-pass filter which prevents noise glitches from causing unintended resets.  Note: To apply an external reset source to this pin, drive this pin low during reset. The internal pull-up ensures that the reset is released. This pin should not be connected to an external pull-up or disease. |  |  |  |

| OEb                     | 14         | I        | driven high while the device is unpowered, as this could damage the device.  Output Enable. This output enable pin has a programmable register mask which allows it to control any of the output clocks. By default the OEb pin enables all output clocks. This pin must be externally pulled low when not in use.                                                                                                                                                                |  |  |  |

| LOL_Ab                  | 9          | 0        | Loss of Lock A/C/D and REF. These output pins indicate when                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| LOL_REFb                | 8          | 0        | DSPLL A, C, D and reference DSPLL are out-of-lock (low) or locked (high). These pins should be pulled up with a 4.7 k $\Omega$ resis-                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| LOL_Cb<br>(Si5389 only) | 32         | 0        | tor to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| LOL_Db                  | 25         | 0        | LOL_Cb: On the Si5388, pin 32 is reserved and should be treated as a No Connect.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| BLMDb                   | 3          | I        | <b>Bootloader Mode.</b> This pin should be pulled low on reset negation to enable bootloader mode. Under normal operation this pin should always be high.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Power                   |            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VDD                     | 21         |          | Core Supply Voltage. The device core operates from a 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                         | 33         |          | supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                         | 41         | Р        | Note: This supply is decoupled internally and does not require an external decoupling capacitor.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                         |            |          | See section for important power up supply information.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Pin Name          | Pin Number     | Pin Type | Function                                                                                                                                                                                                                                                                              |  |  |

|-------------------|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDDA              | 7              |          | Core Supply Voltage 3.3 V. This core supply pin requires a 3.3 V                                                                                                                                                                                                                      |  |  |

|                   | 53             |          | power source.                                                                                                                                                                                                                                                                         |  |  |

|                   |                | P        | A 10uf bulk capacitor should be placed near each of these pins on the PCB.                                                                                                                                                                                                            |  |  |

|                   | 62             |          | Note: VDDA voltage must be ramped and maintained at or above VDDIO voltage for proper operation. See section for more information.                                                                                                                                                    |  |  |

|                   | 4              |          | Control/Status IO Voltage. The voltage on these pins and the                                                                                                                                                                                                                          |  |  |

| VDDIO             |                | P        | part number grade determine the control/status I/O voltage. Connect to either 3.3V or 1.8V based on the grade of the part ordered (see Table 2.1).                                                                                                                                    |  |  |

|                   | 55             |          | Pin 4: A 10uf bulk capacitor should be placed near this pin on the PCB.                                                                                                                                                                                                               |  |  |

|                   |                |          | Pin 55: A 10uf bulk capacitor should be placed near this pin on the PCB.                                                                                                                                                                                                              |  |  |

|                   |                |          | Note: VDDA voltage must be ramped and maintained at or above VDDIO voltage for proper operation. See section for more information.                                                                                                                                                    |  |  |

| VDD00             | 51             | Р        |                                                                                                                                                                                                                                                                                       |  |  |

| VDDO1             | 47             | Р        | Output Clock Supply Voltage 0-7. Supply voltage (3.3 V, 2.5 V,                                                                                                                                                                                                                        |  |  |

| VDDO2             | 44             | Р        | and 1.8 V) for OUTn outputs. Leave VDDO pins of unused output drivers unconnected. An alternate option is to connect the VDDO                                                                                                                                                         |  |  |

| VDDO3             | 39             | Р        | pin to a power supply and disable the output driver to minimize                                                                                                                                                                                                                       |  |  |

| VDDO4             | 36             | Р        | current consumption.                                                                                                                                                                                                                                                                  |  |  |

| VDDO5             | 31             | Р        | Note: These supplies are decoupled internally and do not require                                                                                                                                                                                                                      |  |  |

| VDDO6             | 28             | Р        | an external decoupling capacitor.                                                                                                                                                                                                                                                     |  |  |

| VDD07             | 24             | Р        |                                                                                                                                                                                                                                                                                       |  |  |

| DECOUPLE          | 60             | Р        | <b>LDO Decouple.</b> Decouple output for on-chip voltage regulator (output of the internal digital LDO and digital logic power supply). The decouple pin requires a 2.2 μF capacitor as close to the pin as possible.                                                                 |  |  |

| GND PAD           | _              | Р        | <b>Ground Pad.</b> This pad provides connection to ground and must be connected for proper operation. Use as many vias as practical and keep the via length to an internal ground plane as short as possible.                                                                         |  |  |

| Pin One Indicator | _              | Р        | Pin One Orientation Indicator. This small metal pad is connected to the GND PAD. This can be soldered to ground, but it is recommended to leave this pin unconnected and to enforce a keep-out area so that it is not inadvertently connected to a conductor (e.g., a PCB trace via). |  |  |

| Reserved Pins     |                |          |                                                                                                                                                                                                                                                                                       |  |  |

| RSVD              | 48, 52, 54, 56 | _        | Reserved. Leave reserved pins unconnected.                                                                                                                                                                                                                                            |  |  |

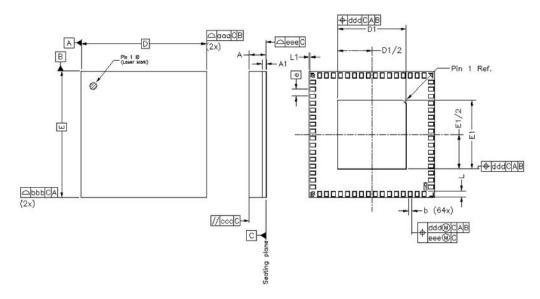

## 2. Package Outline

The figure below illustrates the package details for the Si5388/89. The table below lists the values for the dimensions shown in the illustration.

Figure 2.1. Si5388/89 9x9 mm 64-Pin LGA

Table 2.1. Package Dimensions

| Dimension | Min      | Nom   | Max   |  |

|-----------|----------|-------|-------|--|

| А         | _        | _     | 1.03  |  |

| A1        | 0.45 REF |       |       |  |

| b         | 0.20     | 0.25  | 0.30  |  |

| D         | 9.00 BSC |       |       |  |

| D1        | 4.80     | 4.9   | 5.0   |  |

| е         | 0.50 BSC |       |       |  |

| E1        | 4.80     | 4.9   | 5.0   |  |

| E         | 9.00 BSC |       |       |  |

| L         | 0.313    | 0.363 | 0.413 |  |

| L1        | 0.955    | 0.105 | 0.155 |  |

| aaa       | _        | _     | 0.15  |  |

| bbb       | _        | _     | 0.15  |  |

| ccc       | _        | _     | 0.10  |  |

| ddd       | _        | _     | 0.15  |  |

| eee       | _        | _     | 0.05  |  |

## Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-220.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

www.skyworksinc.com/CBPro

**Quality** www.skyworksinc.com/quality

**Support & Resources** www.skyworksinc.com/support

## Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5®, SkyOne®, SkyBlue™, Skyworks Green™, Clockbuilder®, DSPLL®, ISOmodem®, ProSLIC®, and SiPHY® are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.