**IC Card Interface ICs**

# IC card interface ICs with Built-in DC / DC Converter

BD8904F, BD8904FV, BD8905F, BD8906F, BD8906FV, BD8907F

No.09056EAT02

#### Overview

BD8904F, BD8904FV, BD8905F, BD8906FV and BD8907F are an interface IC for a 3V or 5V smart card. It works as a bidirectional signal buffer between a smart card and a controller. Also, it supplies 3V or 5V power to a smart card. With electrostatic breakdown voltage of more than HBM: ±6000V, it protects the card contact pins.

#### Features

- 1) 3 half duplex bidirectional buffers

- 2) Protection against short-circuit for all the card contact pins

- 3) Card power source (VREG) of 3V or 5V

- 4) Overcurrent protection for card power source

- 5) Built-in thermal shutdown circuit

- 6) Built-in supply voltage detector

- 7) Automatic start-up/shutdown sequence function for card contact pin Start-up sequence: driven by a signal from controller (CMDVCCB↓) Shutdown sequence: driven by a signal from controller (CMDVCCB↑) and fault detection (card removal, short circuit of card power, IC overheat detection, VDD or VDDP drop)

- 8) Card contact pin ESD voltage ≥ ±6000V

- 9) 2MHz 26MHz integrated crystal oscillator

- 10) Programmable for clock division of output signal by 1, 1/2, 1/4, and 1/8

- 11) RST output control by RSTIN input signal (positive output)

- 12) One multiplexed card status output by OFFB signal

#### Line up matrix

| Part No. | Resistor to set VDD | Input V     | oltage/     | Operating     | Package  |  |

|----------|---------------------|-------------|-------------|---------------|----------|--|

| Fait No. | voltage detector    | VDD         | VDDP        | temperature   | i ackage |  |

| BD8904F  | External            | 2.7V - 5.5V | 3.0V - 5.5V | -40°C - +85°C | SOP28    |  |

| BD8904FV | External            | 2.7V - 5.5V | 3.0V - 5.5V | -40°C - +85°C | SSOP-B28 |  |

| BD8905F  | External            | 2.7V - 5.5V | 3.0V - 5.5V | -25°C - +85°C | SOP28    |  |

| BD8906F  | Built-in            | 3.0V - 5.5V | 3.0V - 5.5V | -25°C - +85°C | SOP28    |  |

| BD8906FV | Built-in            | 3.0V - 5.5V | 3.0V - 5.5V | -25°C - +85°C | SSOP-B28 |  |

| BD8907F  | Built-in            | 3.0V - 5.5V | 3.0V - 5.5V | -40°C - +85°C | SOP28    |  |

# Application

Interface for smart cards Interface for B-CAS cards ● Absolute maximum ratings (Ta=25°C)

| Para            | Parameter               |                                  | Rating       | Unit | Note                                                                                         |  |

|-----------------|-------------------------|----------------------------------|--------------|------|----------------------------------------------------------------------------------------------|--|

| VDD Input Vo    | VDD Input Voltage       |                                  | -0.3 - 6.5   | V    |                                                                                              |  |

| VDDP Input      | Voltage                 | $V_{\text{DDP}}$                 | -0.3 - 6.5   | V    |                                                                                              |  |

| I/O Pin Voltage |                         | $V_{\text{IN}}$ $V_{\text{OUT}}$ | -0.3 - +6.5  | V    | Pin: XTAL1, XTAL2, VSEL, RSTIN, AUX1C, AUX2C, IO CLKDIV1, CLKDIV2, CMDVCCB, OFFB, PORADJ, S2 |  |

| Card Contac     | t Pin Voltage           | $V_{REG}$                        | -0.3 - +6.5  | V    | Pin: PRES, PRESB, CLK, RST, IO, AUX1, AUX2                                                   |  |

| Charge Pum      | Charge Pump Pin Voltage |                                  | -0.3 - +14.0 | V    | Pin: VCH, S1                                                                                 |  |

| Junction Tem    | perature                | T <sub>jmax</sub>                | +150         | °C   |                                                                                              |  |

| Storage Tem     | perature                | $T_{stg}$                        | -55 - +150   | °C   |                                                                                              |  |

|                 | BD8904F                 |                                  |              |      | Ta=-40 - +85°C                                                                               |  |

|                 | BD8905F                 |                                  | 750          |      | Ta=-25 - +85°C                                                                               |  |

| Power           | Power BD8906F           |                                  | 750          |      | Ta=-25 - +85°C * Refer to the following package power                                        |  |

| Dissipation     | BD8907F                 | P <sub>tot</sub>                 |              | mW   | Ta=-40 - +85°C dissipation                                                                   |  |

| a a pomore      | BD8904FV                |                                  | 1060         |      | Ta=-40 - +85°C                                                                               |  |

|                 | BD8906FV                |                                  | 1060         |      | Ta=-25 - +85°C                                                                               |  |

<sup>·</sup>This product is not designed to be radiation tolerant.

# Operating Conditions

| Deremeter             | Cumple of        | Limits |     | Unit | Nata |                                                |

|-----------------------|------------------|--------|-----|------|------|------------------------------------------------|

| Parameter             | Symbol           | MIN    | TYP | MAX  | Unit | Note                                           |

| Operating temperature | т                | -40    | ı   | +85  | °C   | BD8904F, BD8904FV, BD8907F                     |

| Operating temperature | $T_{opr}$        | -25    | 1   | +85  | °C   | BD8905F,BD8906F, BD8906FV                      |

| VDD Input Voltage     | V <sub>DD</sub>  | 2.7    | -   | 5.5  | V    | BD8904F, BD8904FV, BD8905F                     |

| VDD Input Voltage     | V <sub>DD</sub>  | 3.0    | -   | 5.5  | V    | BD8906F,BD8906FV, BD8907F                      |

|                       | V <sub>DDP</sub> | 4.5    | 5.0 | 5.5  | V    | VREG=5V; Ivreg ≤ 60mA                          |

|                       |                  | 3.0    | -   | 4.5  | V    | VREG=5V; Ivreg ≤ 20mA, Except BD8904FV         |

| VDDP Input Voltage    |                  | 3.1    | -   | 4.5  | V    | VREG=5V; Ivreg ≤ 25mA, Application to BD8904FV |

|                       |                  | 3.0    | ı   | 3.1  | V    | VREG=5V; Ivreg ≤ 20mA, Application to BD8904FV |

|                       |                  | 3.0    | 5.0 | 5.5  | V    | VREG=3V; Ivreg ≤ 60mA                          |

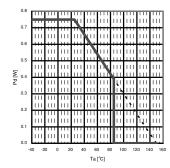

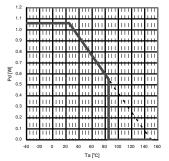

# Package Power Dissipation

The power dissipation of the package will be as follows in case that ROHM standard PCB is used. Use of this device beyond the following the power dissipation may cause permanent damage.

BD8904F, BD8905F, BD8906F, BD8907F: Pd=750mW; however, reduce 6mW per 1°C when used Ta $\geq$ 25°C. BD8904FV, BD8906FV : Pd=1060mW; however, reduce 8.5mW per 1°C when used Ta $\geq$ 25°C.

ROHM standard PCB: Size: 70×70×1.6 (mm<sup>3</sup>), Material: FR4 glass epoxy board (copper plate area of 3% or less)

Fig. 1 Power Dissipation of BD8904F, BD8905F, BD8906F, BD8907F

Fig. 2 Power Dissipation of BD8904FV, BD8906FV

<sup>·</sup> Absolute maximum ratings are not meant for guarantee of operation.

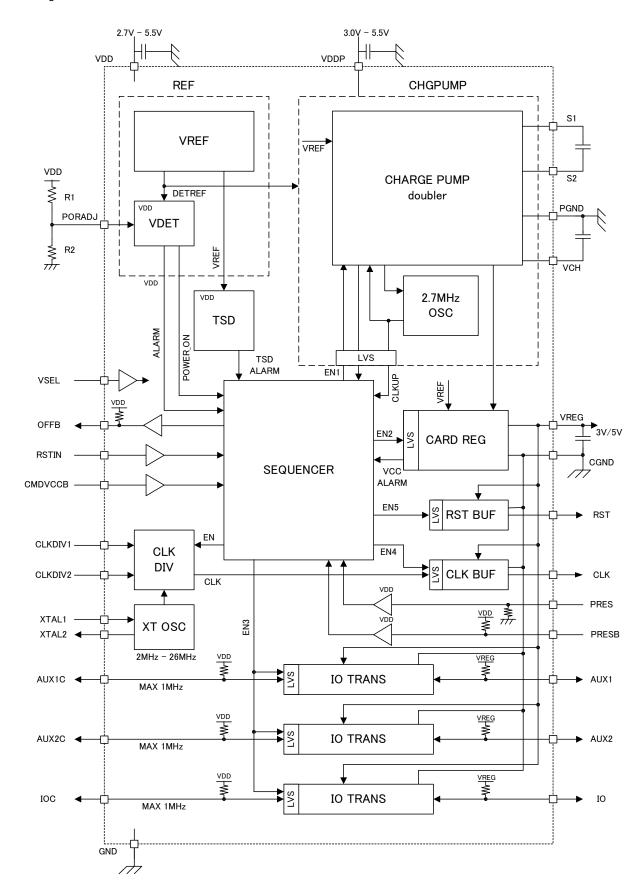

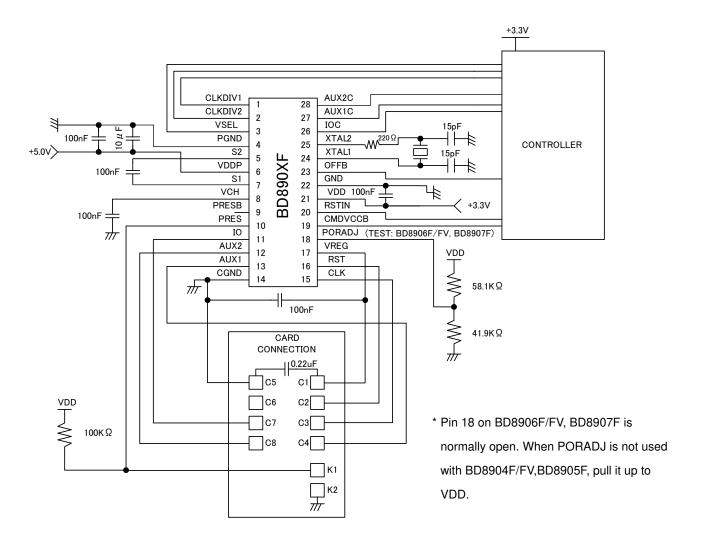

# ●Block Diagram

Fig. 3

| Pin Descriptio<br>Pin No.                  | Pin Name | I/O | Signal Level | Pin Function                                                                                                                                                                                                       |

|--------------------------------------------|----------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                          | CLKDIV1  | I   | VDD          | Clock frequency selection input 1                                                                                                                                                                                  |

| 2                                          | CLKDIV2  | ı   | VDD          | Clock frequency selection input 2                                                                                                                                                                                  |

| 3                                          | VSEL     | I   | VDD          | Card supply voltage selection input; "H": VREG=5V, "L": VREG=3V                                                                                                                                                    |

| 4                                          | PGND     | S   | GND          | GND for charge pump                                                                                                                                                                                                |

| 5                                          | S2       | I/O | -            | Capacitor connection for charge pump (between S1/S2): C = 100nF (ESR < 100mΩ)                                                                                                                                      |

| 6                                          | VDDP     | S   | VDDP         | Power supply for charge pump                                                                                                                                                                                       |

| 7                                          | S1       | I/O | -            | Capacitor connection for charge pump (between S1/S2): C = 100nF (ESR < 100mΩ)                                                                                                                                      |

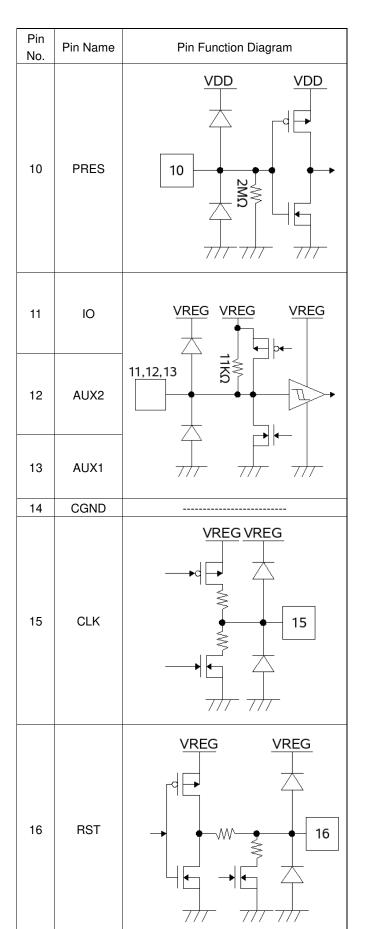

| 8                                          | VCH      | I/O | -            | Charge pump output: Decoupling capacitor; Connect C = 100nF (ESR < 100mΩ) between VCH and PGND Card presence contact input (active "L")                                                                            |

| 9                                          | PRESB    | I   | VDD          | When PRES or PRESB is active, the card is considered 'present' and a built-in debounce feature of 8ms (typ.) is activated. Pulled up to VDD with a $2M\Omega$ resistor.                                            |

| 10                                         | PRES     | I   | VDD          | Card presence contact input (active "H") When PRES or PRESB is active, the card is considered 'present' and a built-in debounce feature of 8ms (typ.) is activated. Pulled down to GND with a $2M\Omega$ resistor. |

| 11                                         | Ю        | I/O | VREG         | Card contact I/O data line; Pulled up to VREG with a $11k\Omega$ resistor                                                                                                                                          |

| 12                                         | AUX2     | I/O | VREG         | Card contact I/O data line; Pulled up to VREG with a 11kΩ resistor                                                                                                                                                 |

| 13                                         | AUX1     | I/O | VREG         | Card contact I/O data line; Pulled up to VREG with a $11k\Omega$ resistor                                                                                                                                          |

| 14                                         | CGND     | S   | GND          | GND                                                                                                                                                                                                                |

| 15                                         | CLK      | 0   | VREG         | Card clock output                                                                                                                                                                                                  |

| 16                                         | RST      | 0   | VREG         | Card reset output                                                                                                                                                                                                  |

| 17                                         | VREG     | 0   | VREG         | Card supply voltage; Connect a capacitor (ESR < $100m\Omega$ ) of $100nF$ - $220nF$ between VREG and CGND                                                                                                          |

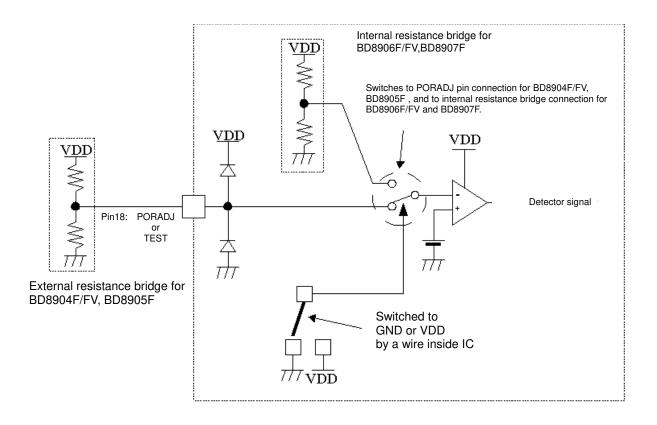

| 18<br>(BD8904F)<br>(BD8904FV)<br>(BD8905F) | PORADJ   | - 1 | -            | Power-on reset threshold adjustment voltage input; set with an external resistor bridge                                                                                                                            |

| (BD8906F)<br>(BD8906FV)<br>(BD8907F)       | TEST     |     |              | Normally used OPEN. Input voltage range: 0V - VDD voltage Can also be used at VDD or GND potential.                                                                                                                |

| 19                                         | CMDVCCB  | ı   | VDD          | Activation sequence command input; The activation sequence starts by signal input (H→L) from the host                                                                                                              |

| 20                                         | RSTIN    | I   | VDD          | Card reset signal input                                                                                                                                                                                            |

| 21                                         | VDD      | S   | VDD          | Input power source pin                                                                                                                                                                                             |

| 22                                         | GND      | S   | GND          | GND                                                                                                                                                                                                                |

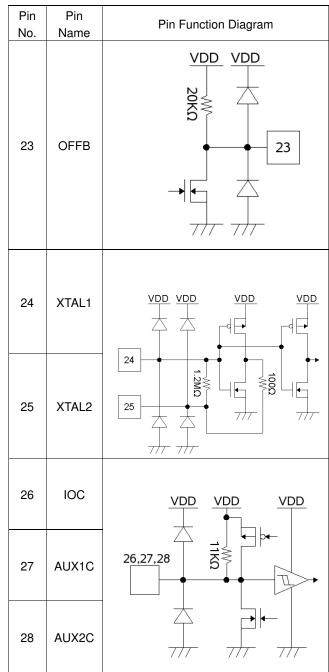

| 23                                         | OFFB     | 0   | VDD          | Alarm output pin (active "L") NMOS output pulled up to $V_{DD}$ with a $20k\Omega$ resistor                                                                                                                        |

| 24                                         | XTAL1    | I   | VDD          | Crystal connection or input for external clock                                                                                                                                                                     |

| 25                                         | XTAL2    | 0   | VDD          | Crystal connection (leave open pin when external clock source is used)                                                                                                                                             |

| 26                                         | IOC      | I/O | VDD          | Host data I/O line; Pulled up to VDD with a 11kΩ resistor                                                                                                                                                          |

| 27                                         | AUX1C    | I/O | VDD          | Host data I/O line; Pulled up to VDD with a 11kΩ resistor                                                                                                                                                          |

| 28                                         | AUX2C    | I/O | VDD          | Host data I/O line; Pulled up to VDD with a 11kΩ resistor                                                                                                                                                          |

|            | n Function Diagram |                                         |  |  |  |  |  |

|------------|--------------------|-----------------------------------------|--|--|--|--|--|

| Pin<br>No. | Pin Name           | Pin Function Diagram                    |  |  |  |  |  |

| 1          | CLKDIV1            | VDD VDD                                 |  |  |  |  |  |

| 2          | CLKDIV2            | 1,2,3                                   |  |  |  |  |  |

| 3          | VSEL               |                                         |  |  |  |  |  |

| 4          | PGND               |                                         |  |  |  |  |  |

|            |                    | VDDP VDDP                               |  |  |  |  |  |

| 5          | S2                 | 5                                       |  |  |  |  |  |

| 6          | VDDP               |                                         |  |  |  |  |  |

| 7          | S1                 | VDDP VDDP VDDP 7                        |  |  |  |  |  |

| 8          | VCH                | 17                                      |  |  |  |  |  |

| 9          | PRESB              | 9 P P P P P P P P P P P P P P P P P P P |  |  |  |  |  |

| Pin<br>No. | Pin Name    | Pin Function Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17         | VREG        | VCH VCH  TO THE TOTAL TO |

| 18         | PORADJ      | VDD<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| .0         | TEST        | VDD VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19         | CMDVCC<br>B | 19,20 VDD VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20         | RSTIN       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21         | VDD         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22         | GND         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

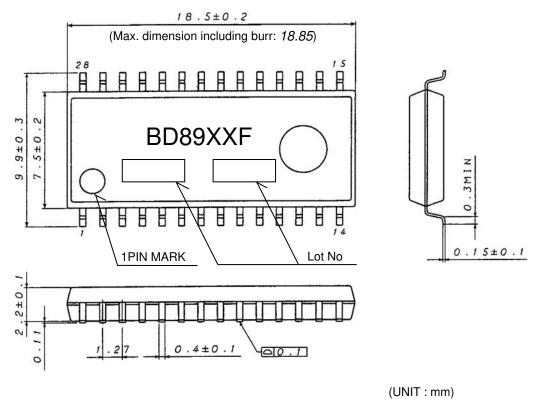

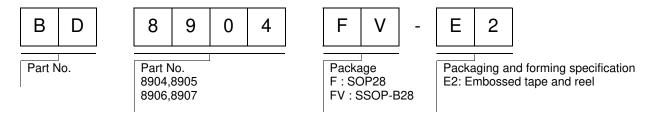

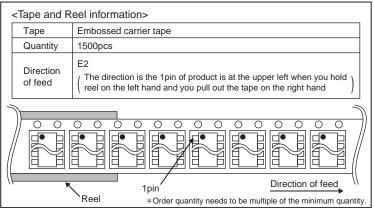

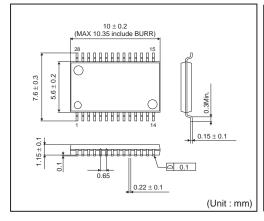

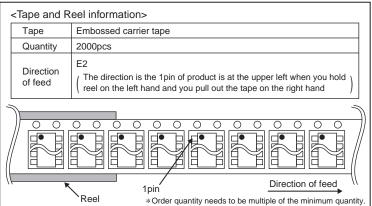

# Package

For "XX" in the product name below, substitute 04 for BD8904, 05 for BD8905, 06 for BD8906 and 07 for BD8907.

Package Name: SOP28

Fig. 4 SOP28 Package Outer Dimension

Package Name: SSOP-B28

Fig. 5 SSOP-B28 Package Outer Dimension

#### Function

#### 1) Power Supply

Power supply pins are VDD and VDDP. Set VDD at the same voltage as the signal from the system controller. VDDP and PGND are the power source and GND for the charge pump circuit, respectively, and the power source for the card. The VSEL pin setting determines the supply voltage of 3V (VSEL: L) or 5V (VSEL: H) from the VREG pin to the card.

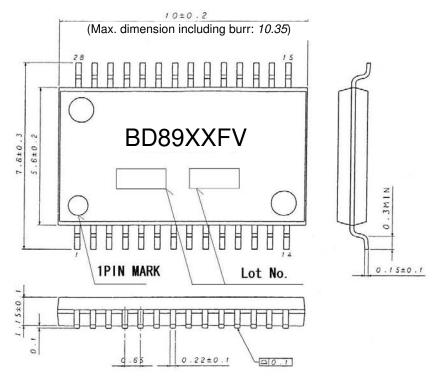

#### 2) VDD input voltage detector

By connecting the resistance bridge (R1, R2: Fig. 3) to the PORADJ pin, you can set the VDD supply voltage detector ( $V_{\text{DETR}}$ ,  $V_{\text{DETF}}$ : Fig.5). Approximately 16ms (BD8904F/FV, BD8905F) or 8ms (BD8906F/FV, BD8907F) after VDD voltage becomes higher than  $V_{\text{DETR}}$  (internal reset), power-on reset (alarm) will be cancelled and the IC will go into sleep mode until the CMDVCCB signal turns from H to L.

The IC will initiate the shutdown sequence toward the card contact pin if VDD voltage is decreased below V<sub>DETF</sub>.

# Calculating resistance bridge R1 and R2 for supply voltage detector

(Applicable to BD8904F, BD8904FV and BD8905F; excludes BD8906F, BD8906FV and BD8907F)

The following equations can be used to calculate the alarm reset voltage ( $V_{\text{DETR}}$ ) and low voltage detection voltage ( $V_{\text{DETF}}$ ): Please ensure that  $V_{\text{DETF}}$  is set at over 2.3V.

PORADJ pin voltage at VDD startup: VDD<sub>THR</sub>

PORADJ pin voltage at VDD shutdown: VDD<sub>THF</sub>

Fig. 6 VDD Input Voltage Detection

# 3) Operation sequence

# 3-1) Wait mode

When VDD voltage becomes higher than  $V_{DTER}$ , power-on reset (alarm) is released and the IC will be in wait mode until the CMDVCCB signal turns from H to L.

In this mode, the VDD supply voltage detector (VDET), thermal shutdown circuit (TSD), reference circuit (VREF), crystal oscillation circuit (XT OSC) and internal oscillator circuit (OSC) are activated.

IOC, AUX1C and AUX2C are pulled up to VDD with an  $11k\Omega$  resistor and all the card contact pins are at Lo level.

# 3-2) Card insertion

Card presence is detected by PRES pin or PRESB pin. When either of the PRES pin or PRESB pin is active, a card is assumed to be present.

| Table 1 |               |  |  |  |  |

|---------|---------------|--|--|--|--|

| PRES    | "High" active |  |  |  |  |

| PRESB   | "Lo" active   |  |  |  |  |

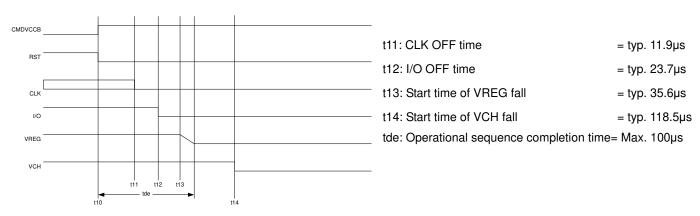

When a card is present in sleep mode, either one of the card presence identification pins, PRES ("H" active) or PRESB ("L" active) becomes active. OFFB will become "H" after approximately 8ms (debounce time).

If a card is present before the VDD power source is applied and the internal reset is released, it is internally reset and OFFB becomes "H" after the debounce time.

The PRES pin is pulled down to GND with a  $2M\Omega$  resistor and the PRESB pin is pulled up to VDD with a  $2M\Omega$  resistor.

#### 3-3) Activation sequence

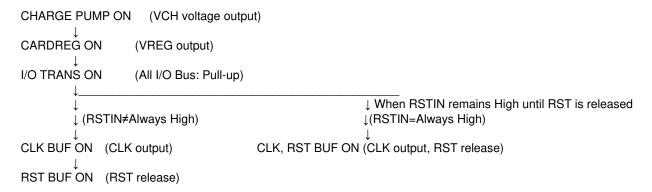

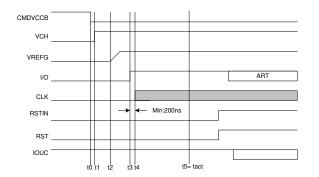

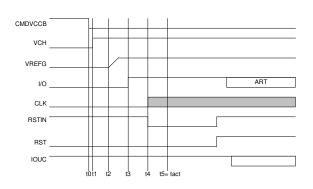

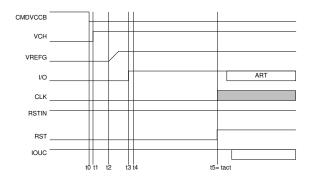

When OFFB is in the "High" state and the CMDVCCB signal from the controller turns from H to L, the activation sequence starts to activate each functional block in the following order:

The RST outputs signals based on the RSTIN input, being reset approximately 200µsec after the CMDVCCB signal turns from H to L. The RSTIN input becomes effective approximately 300ns after I/O TRANS turns ON. If RSTIN becomes Lo after RSTIN becomes effective and before RST output is released, the CLK signal is output. If RSTIN is High when the RST output is released, the CLK signal is output as soon as the RST output is released. (Refer to Fig. 6-1, Fig. 6-2 and Fig. 6-3)

# [Activation sequence under different RSTIN input timings]

Fig. 7 Activation sequence 1

Fig.8 Activation sequence 2

t1: VCH startup time = typ 21.4 $\mu$ s, (max. 30 $\mu$ s) t2: VREG startup time = typ 57 $\mu$ s, (max. 80 $\mu$ s) t3: I/O ON time = typ 116.2 $\mu$ s, (max. 150 $\mu$ s) t4: CLK output release time (t4-t3)= Min 200ns, (max. 450 $\mu$ s) t5: RST release time = typ 187.4 $\mu$ s, (max. 240 $\mu$ s)

Fig.9 Activation sequence 3 (not supported by ISO7816-3)

(activation time)

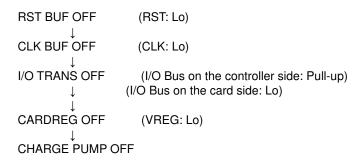

#### 3-4) Deactivation sequence

When the CMDVCCB input turns from L to H or the alarm signal (described later) is detected, the following deactivation sequence is initiated in the following order transitioning to the wait mode.

Fig.10 Deactivation sequence

# 4) CHARGE PUMP

The charge pump circuit is the power supply for CARD REG output. It activates when the CMDVCCB input turns from H to L. It functions as a voltage doubler or voltage follower by the VDDP voltage.

The VCH output becomes a power source for the CARDREG circuit.

As the charge pump circuit takes a high charge current, place two capacitors (one between S1-S2, and the other between VCH-PGND) as close as possible to the IC so that the ESR becomes less than  $100m\Omega$ . Also, place a capacitor between VDDP and PGND as close as possible to the IC so that the ESR becomes less than  $100m\Omega$ .

#### 5) CARD REG

CARD REG supplies power to the IC card through the VREG pin.

The VREG output voltage can be switched between 3V and 5V by the VSEL pin setting.

Table 2 VSEL pin setting

| VSEL | VREG output voltage | VDDP Input Voltage | MAX current | Remark                  |

|------|---------------------|--------------------|-------------|-------------------------|

| 0    | 3V                  | 3.0V ≤ VDDP ≤ 5.5V | 60mA        |                         |

|      |                     | 3.0V ≤ VDDP < 4.5V | 20mA        | Except BD8904FV         |

|      | 5V                  | 3.0V ≤ VDDP < 3.1V | 20mA        | Application to DD0004EV |

| '    |                     | 3.1V ≤ VDDP < 4.5V | 25mA        | Application to BD8904FV |

|      |                     | 4.5V ≤ VDDP ≤ 5.5V | 60mA        |                         |

This regulator has an over-current limiter circuit. It generates an internal alarm with a load current of approximately 140mA or more and enters into the deactivation sequence. Also, the output voltage is regarded as abnormal if it becomes less than 0.6V in the case where VREG is 3V or becomes less than 1V in the case where VREG is 5V, and the output current is shut off. At this point, an internal alarm signal is generated and the deactivation sequence is initiated.

Connect a capacitor of 100nF, 220nF or 330nF between VREG and CGND as close as possible to the VREG pin, in order to reduce the output voltage variation as much as possible. Also, ensure that ESR is kept at less than  $100m\Omega$ .

CARD REG output is also a power source for the CLK and RST output. Therefore, the CLK and RST output level is the same as the VREG output level.

#### 6) I/O data transitions

Three data lines, IOC - IO, AUX1C - AUX1 and AUX2C - AUX2 transmit two-way data independently of each other. Pins for the controller side, IOC, AUX1C and AUX2C are pulled up with an  $11k\Omega$  resistor to High (VDD voltage) and card contact pins, IO, AUX1 and AUX2 are set to Lo until I/O TRANS becomes ON during the activation sequence. When I/O TRANS becomes On, IC becomes idle mode and all the I/O pins are pulled up with an  $11k\Omega$ . The IOC, AUX1C and AUX2C pins keep VDD voltage (High) and the IO, AUX1 and AUX2 pins go to' VREG voltage (High).

The pin which turns from H to L first becomes the master and the other output side becomes the slave between the pins on the controller side and card contact pins. Then the data are transferred from the master side to the slave side. When both signal levels become High, they become idle.

When the signal transits from L to H and it passes over a threshold, an active pull-up (100 ns or less) works to drive the data High at high speed. After the active pull-up is completed, the pin is pulled up with an  $11k\Omega$  resistor. This function enables signal transmission up to 1MHz. Also, an over-current limiter of 15mA works in the card contact pins, IO, AUX1 and AUX2.

#### 7) Card clock supply

Card clock is supplied from the CLK pin divides the input frequency of XTAL1 pin by 1, 1/2, 1/4 and 1/8 with the CLKDIV1 and CLKDIV2 pin setting. The clock division switching time is within the 8 clocks of the XTAL1 signal (refer to Table 3). The input signal to the XTAL1 pin is made by a crystal oscillator (2MHz - 26MHz) between the XTAL1 pin and XTAL2 pin or external pulse signal.

To ensure the duty factor of 45% - 55% at the CLK pin, the duty of the XTAL1 pin should be 48% - 52% and the transition time should be within 5% of the frequency.

To guarantee a 45% - 55% duty, use it with a clock division of 1/2, 1/4 or 1/8 depending on the wiring layout on the PCB.

| Table 3 Clock freque | ncy selection | (f <sub>XTAL</sub> : Frequency of XTAL1) |

|----------------------|---------------|------------------------------------------|

| CLKDIV1              | CLKDIV2       | ${\sf f}_{\sf clk}$                      |

| 0                    | 0             | f <sub>XTAL</sub><br>8                   |

| 0                    | 1             | f <sub>XTAL</sub><br>4                   |

| 1                    | 1             | f <sub>XTAL</sub><br>2                   |

| 1                    | 0             | f <sub>XTAL</sub><br>1                   |

#### 8) RSTIN input, RST output

The RSTIN input becomes effective after the CMDVCCB signal input turns from H to L, activation sequence is initiated and approximately 300ns after I/O TRANS turns ON. The RST output is released in approximately 200µsec after the CMDVCCB signal turns from H to L to output signal based on the RSTIN input.

# 9) Fault detection

When the following fault state is detected, the circuit enters the wait mode after it generates an internal alarm signal and is deactivated.

If a card is not present, it remains in the wait mode.

- When the VREG pin becomes less than 1V (VSEL=H) or 0.6V (VSEL=L), or is loaded high current(TYP: 150mA)

- When the VDD voltage is less than the threshold voltage (detected by supply voltage detector)

- · When an overheating is detected by the thermal shutdown circuit

- When VCH pin voltage drops to an abnormal level

- · When the card is removed during operation or the card is not present from the beginning (PRES=L and PRESB=H)

#### 10) OFFB output

The OFFB output pin indicates that the IC is ready to operate. It is pulled up to VDD with a  $20k\Omega$  resistor.

When the IC is in ready state, OFFB is High.

The OFFB outputs OFF state (Lo) when a fault state is detected.

When a card is present, the fault state is released and CMDVCCB becomes High, the internal alarm is released and the OFFB output becomes High.

Fig. 11 OFFB, CMDVCCB, PRES, VREG operation

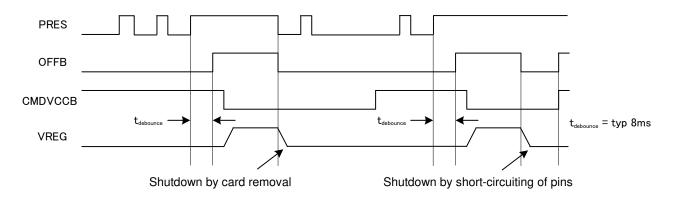

# An example of software control

Fig. 12 An example of software control

# Application examples

Fig. 13

# • Function of pin 18 on different devices

The function of pin 18 (PORADJ/TEST) for BD8904F/FV and BD8905F is different from BD8906F/FV and BD8907F; switched as indicated in the following diagram but the common chip is used.

Fig. 14

# ●Notes for use

- 1) Two capacitors for a charge pump should be placed as close as possible to the IC between S1 and S2 and between VCH and PGND so that the ESR becomes less than  $100m\Omega$ .

- 2) The capacitor for the VREG pin should be placed as close as possible to the IC between VREG and CGND so that the ESR becomes less than  $100m\Omega$ .

- 3) Connect capacitors of over  $10\mu\text{F}+0.1\mu\text{F}$  between VDD and GND and between VDDP and GND as close as possible to the IC so that the ESR becomes less than  $100\text{m}\Omega$  to reduce the power line noise. We recommend the use of capacitors with the largest possible capacitance.

# Ordering part number

# SOP28

# SSOP-B28

# **Notice**

#### **Precaution on using ROHM Products**

Our Products are designed and manufactured for application in ordinary electronic equipments (such as AV equipment, OA equipment, telecommunication equipment, home electronic appliances, amusement equipment, etc.). If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment (Note 1), transport equipment, traffic equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

(Note1) Medical Equipment Classification of the Specific Applications

| JÁF | PAN  | USA      | EU         | CHINA     |

|-----|------|----------|------------|-----------|

| CLA | SSⅢ  | CLACCIII | CLASS II b | CL ACCIII |

| CLA | SSIV | CLASSⅢ   | CLASSIII   | CLASSⅢ    |

- 2. ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3. Our Products are designed and manufactured for use under standard conditions and not under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [c] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (even if you use no-clean type fluxes, cleaning residue of flux is recommended); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4. The Products are not subject to radiation-proof design.

- 5. Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6. In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse. is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 7. De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 8. Confirm that operation temperature is within the specified range described in the product specification.

- 9. ROHM shall not be in any way responsible or liable for failure induced under deviant condition from what is defined in this document.

#### Precaution for Mounting / Circuit board design

- 1. When a highly active halogenous (chlorine, bromine, etc.) flux is used, the residue of flux may negatively affect product performance and reliability.

- 2. In principle, the reflow soldering method must be used; if flow soldering method is preferred, please consult with the ROHM representative in advance.

For details, please refer to ROHM Mounting specification

# **Precautions Regarding Application Examples and External Circuits**

- If change is made to the constant of an external circuit, please allow a sufficient margin considering variations of the characteristics of the Products and external components, including transient characteristics, as well as static characteristics.

- You agree that application notes, reference designs, and associated data and information contained in this document are presented only as guidance for Products use. Therefore, in case you use such information, you are solely responsible for it and you must exercise your own independent verification and judgment in the use of such information contained in this document. ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of such information.

#### **Precaution for Electrostatic**

This Product is electrostatic sensitive product, which may be damaged due to electrostatic discharge. Please take proper caution in your manufacturing process and storage so that voltage exceeding the Products maximum rating will not be applied to Products. Please take special care under dry condition (e.g. Grounding of human body / equipment / solder iron, isolation from charged objects, setting of lonizer, friction prevention and temperature / humidity control).

# **Precaution for Storage / Transportation**

- 1. Product performance and soldered connections may deteriorate if the Products are stored in the places where:

- [a] the Products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [b] the temperature or humidity exceeds those recommended by ROHM

- the Products are exposed to direct sunshine or condensation

- [d] the Products are exposed to high Electrostatic

- 2. Even under ROHM recommended storage condition, solderability of products out of recommended storage time period may be degraded. It is strongly recommended to confirm solderability before using Products of which storage time is exceeding the recommended storage time period.

- 3. Store / transport cartons in the correct direction, which is indicated on a carton with a symbol. Otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

- Use Products within the specified time after opening a humidity barrier bag. Baking is required before using Products of which storage time is exceeding the recommended storage time period.

#### **Precaution for Product Label**

QR code printed on ROHM Products label is for ROHM's internal use only.

#### **Precaution for Disposition**

When disposing Products please dispose them properly using an authorized industry waste company.

#### **Precaution for Foreign Exchange and Foreign Trade act**

Since our Products might fall under controlled goods prescribed by the applicable foreign exchange and foreign trade act, please consult with ROHM representative in case of export.

#### **Precaution Regarding Intellectual Property Rights**

- 1. All information and data including but not limited to application example contained in this document is for reference only. ROHM does not warrant that foregoing information or data will not infringe any intellectual property rights or any other rights of any third party regarding such information or data. ROHM shall not be in any way responsible or liable for infringement of any intellectual property rights or other damages arising from use of such information or data.:

- 2. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third parties with respect to the information contained in this document.

# **Other Precaution**

- 1. This document may not be reprinted or reproduced, in whole or in part, without prior written consent of ROHM.

- 2. The Products may not be disassembled, converted, modified, reproduced or otherwise changed without prior written consent of ROHM.

- 3. In no event shall you use in any way whatsoever the Products and the related technical information contained in the Products or this document for any military purposes, including but not limited to, the development of mass-destruction weapons.

- The proper names of companies or products described in this document are trademarks or registered trademarks of ROHM, its affiliated companies or third parties.

Notice - GE © 2014 ROHM Co., Ltd. All rights reserved. Rev.002

#### **General Precaution**

- 1. Before you use our Products, you are requested to care fully read this document and fully understand its contents. ROHM shall not be in any way responsible or liable for failure, malfunction or accident arising from the use of a ny ROHM's Products against warning, caution or note contained in this document.

- 2. All information contained in this docume nt is current as of the issuing date and subject to change without any prior notice. Before purchasing or using ROHM's Products, please confirm the latest information with a ROHM sale s representative.

- 3. The information contained in this document is provided on an "as is" basis and ROHM does not warrant that all information contained in this document is accurate an d/or error-free. ROHM shall not be in an y way responsible or liable for any damages, expenses or losses incurred by you or third parties resulting from inaccuracy or errors of or concerning such information.

lotice – WE Rev.001