#### HIGH FIDELITY CLASS D AUDIO AMPLIFIER SOLUTION

#### **DESCRIPTION**

The ZXCD1000 provides complete control and modulation functions at the heart of a high efficiency high performance Class D switching audio amplifier solution. In combination with Zetex HDMOS MOSFET devices, the ZXCD1000 provides a high performance audio amplifier with all the inherent benefits of Class D.

The ZXCD1000 solution uses proprietary circuit design to realise the true benefits of Class D without the traditional drawback of poor distortion performance. The combination of circuit design, magnetic component choice and layout are essential to realising these benefits.

The ZXCD1000 reference designs give output powers up to 100W rms with typical open loop (no feedback) distortion of less than 0.2% THD + N over the entire audio frequency range at 90% full output power. This gives an extremely linear system. The addition of a minimum amount of feedback (10dB) further reduces distortion figures to give < 0.1 % THD + N typical at 1kHz.

From an acoustic point of view, even more important than the figures above, is that the residual distortion is almost totally free of any crossover artifacts. This allows the ZXCD1000 to be used in true hi-fi applications. This lack of crossover distortion, sets the ZXCD1000 solutions quite apart from most other presently available low cost solutions, which in general suffer from severe crossover distortion problems.

#### **FEATURES**

- >90% efficiency

- 4 / 8 Ω drive capability

- Noise Floor -115dB for solution

- Flat response 20Hz 20kHz

- High gate drive capability (2200pF)

- Very low THD + N 0.2% typical full 90% power, full band ( for the solution)

- · Complete absence of crossover artifacts

- OSC output available for sync in multi-channel applications

- Available in a 16 pin exposed pad QSOP package

#### **APPLICATIONS**

- DVD Players

- Automotive audio systems

- Home Theatre

- Multimedia

- Wireless speakers

- Portable audio

- Sub woofer systems

- Public Address system

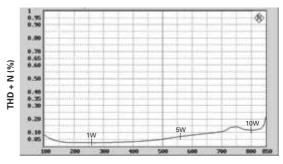

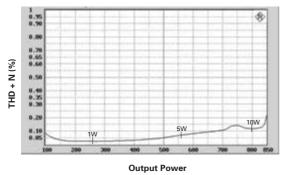

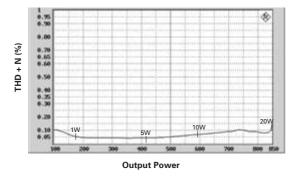

#### **Distortion v Power**

$8\Omega$  open loop at 1kHz.

**Output Power**

The plot shows Distortion v Power into an  $8\Omega$  load at 1kHz. This plot clearly demonstrates the unequalled performance of the Zetex solution. Typical distortion of 0.05% at 1W can be seen with better than 0.15% at 10W. Truly world class performance.

#### **ABSOLUTE MAXIMUM RATINGS**

Terminal Voltage with respect to  $\mathsf{G}_{\mathsf{ND}}$

$\begin{array}{lll} \text{V}_{\text{CC}} & 20\text{V} \\ \text{Power Dissipation} & 1\text{W} \\ \text{Package Thermal Resistance } (\theta_{ja}) & 54^{\circ}\text{C/W} \\ \text{Operating Temperature Range} & -40^{\circ}\text{C to } 70^{\circ}\text{C} \\ \text{Maximum Junction Temperature} & 125^{\circ}\text{C} \\ \text{Storage Temperature Range} & -50^{\circ}\text{C to } 85^{\circ}\text{C} \end{array}$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

TEST CONDITIONS (unless otherwise stated)  $V_{CC} = 16V$ ,  $T_A = 25^{\circ}C$

| SYMBOL             | PARAMETER                                        | CONDITIONS                                          | LIMITS |      |          | UNITS    |

|--------------------|--------------------------------------------------|-----------------------------------------------------|--------|------|----------|----------|

| STIVIBOL           |                                                  |                                                     | MIN    | TYP  | MAX      |          |

| Vcc                | Operating Voltage Range                          |                                                     | 12     | 16   | 18       | V        |

| I <sub>SS</sub>    | Operating Quiescent<br>Current                   | V <sub>CC</sub> = 12V<br>V <sub>CC</sub> = 18V, 16V |        |      | 45<br>50 | mA<br>mA |

| Fosc               | Switching Frequency                              | C <sub>OSC</sub> = 330pF                            | 150    | 200  | 250      | kHz      |

| Fosc(tol)          | Frequency Tolerance                              | C <sub>OSC</sub> = 330pF                            |        |      | +/-25    | %        |

| Vol OutA/B         | Low level output voltage                         | No load                                             |        |      | 100      | mV       |

| Voh OutA/B         | High level output voltage                        | No load                                             | 7.5    |      |          | V        |

| T <sub>Drive</sub> | Output Drive Capability<br>(OUT A / B Rise/Fall) | Load Capacitance<br>= 2200pF                        |        | 50   |          | ns       |

| 5V5tol             | Internal Rail Tolerance                          | 1µF Decoupling                                      | 5.23   | 5.5  | 5.77     | V        |

| 9VA/Btol           | Internal Rail Tolerance                          | 1µF Decoupling                                      | 8.32   | 8.75 | 9.18     | V        |

| Audio A / B        | Input Impedence                                  |                                                     | 1.35k  | 1.8k | 2.3k     | Ω        |

| Triangle<br>A / B  | Input Impedence                                  |                                                     | 1.35k  | 1.8k | 2.3k     | Ω        |

| Audio A / B        | Bias Level                                       |                                                     | 2.95   | 3.1  | 3.25     | V        |

| Triangle<br>A / B  | Bias Level                                       |                                                     | 2.95   | 3.1  | 3.25     | V        |

| Osc A / B          | Amplitude                                        |                                                     | 0.89   | 1.05 | 1.2      | V        |

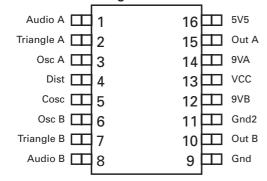

### **Pin Connection Diagram**

Figure 1

#### **Pin Description**

| Pin number | Pin Name   | Pin Description                                                 |

|------------|------------|-----------------------------------------------------------------|

| 1          | Audio A    | Audio Input for Channel A                                       |

| 2          | Triangle A | Triangle Input for Channel A                                    |

| 3          | Osc A      | Triangle Output                                                 |

| 4          | Dist       | No connection                                                   |

| 5          | Cosc       | External timing capacitor node (to set the switching frequency) |

| 6          | Osc B      | Triangle Output (for slave ZXCD1000 in stereo application)      |

| 7          | Triangle B | Triangle Input for Channel B                                    |

| 8          | Audio B    | Audio Input for Channel B                                       |

| 9          | Gnd        | Small Signal GND                                                |

| 10         | OUT B      | Channel B PWM Output to drive external Bridge MOSFETs           |

| 11         | Gnd2       | Power GND (for Output Drivers)                                  |

| 12         | 9VB        | Internal Supply Rail (Decouple with 1µF Cap)                    |

| 13         | vcc        | Input Supply Pin (Max = 18V)                                    |

| 14         | 9VA        | Internal Supply Rail (Decouple with 1µF Cap).                   |

| 15         | OUT A      | Channel A PWM Output to drive external Bridge MOSFETs           |

| 16         | 5V5        | Internal Supply Rail (Decouple with 1µF Cap)                    |

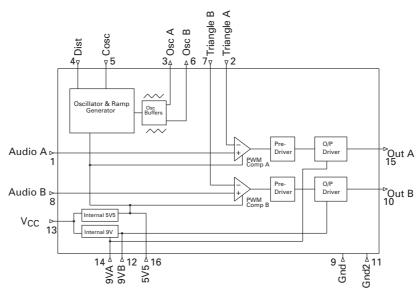

#### **ZXCD1000 Class D controller IC**

A functional block diagram of the ZXCD1000 is shown in Figure 2. The on chip series regulators drop the external  $V_{CC}$  supply (12V-18V) to the approximate 9V (9VA/9VB) and 5.5V (5V5) supplies required by the internal circuitry.

A triangular waveform is generated on chip and is brought out at the OscA and OscB outputs. The frequency of this is set (to  $\sim\!200\text{kHz})$  by an external capacitor (Cosc) and on chip resistor. The triangular waveform must be externally AC coupled back into the ZXCD1000 at the TriangleA and TriangleB inputs.

AC coupling ensures symmetrical operation resulting in minimal system DC offsets. TriangleA is connected to one of the inputs of a comparator and TriangleB is connected to one of the inputs of a second comparator. The other inputs of these two comparators are connected to the AudioA and AudioB inputs, which are anti-phase signals externally derived from the audio input. The triangular wave is an order higher in frequency than the audio input (max 20kHz). The outputs of the comparators toggle every time the TriangleA/B and the (relatively slow) AudioA/B signals cross

Figure 2. Functional Block Diagram

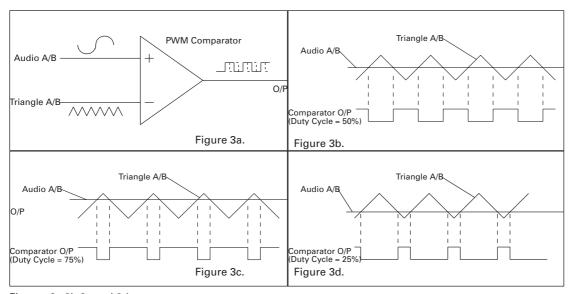

Figures 3a,3b,3c and 3d The audio input Pulse Width Modulates the comparator output.

With no audio input signal applied, the AudioA/B inputs are biased at the mid-point of the triangular wave, and the duty cycle at the output of the comparators is nominally 50%. As the Audio A/B signal ascends towards the peak level, the crossing points with the (higher frequency) triangular wave also ascend. The comparator monitoring these signals exhibits a corresponding increase in output duty cycle. Similarly, as the AudioA/B signal descends, the duty cycle is correspondingly reduced. Thus the audio input Pulse Width Modulates the comparator outputs. This principle is illustrated in Figures 3a, b, c and d. The comparator outputs are buffered and used to drive the OutA and OutB outputs. These in turn drive the speaker load (with the audio information contained in the PWM signal) via the off chip output bridge and single stage L-C filter network.

The ramp amplitude is approximately 1V. The AudioA, AudioB, TriangleA and TriangleB inputs are internally biased to a DC voltage of approximately VCC/5. The mid - point DC level of the OscA and OscB triangular outputs is around 2V. The triangular wave at the Cosc pin traverses between about 2.7Vand 3.8V and the dist pin exhibits a roughly square wave from about 1.4V to 2V. (The above voltages may vary in practice and are included for guidance only).

**ZETEX**

ISSUE 2 - APRIL 2002

Figure 4

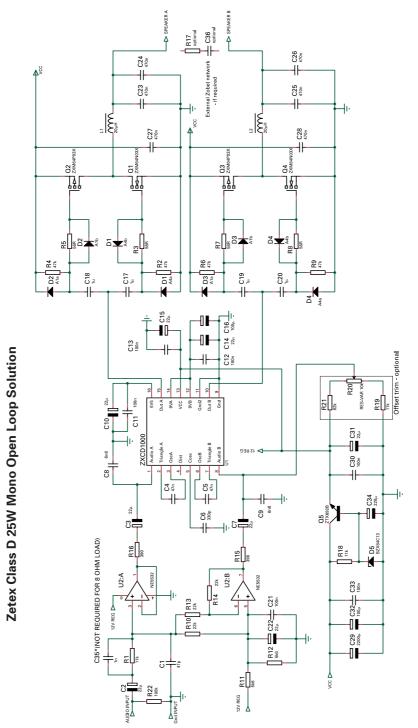

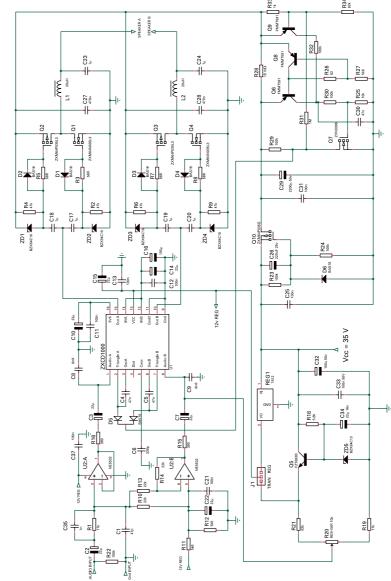

#### Class D 25W Mono Open Loop (Bridge Tied Load - BTL) Solution - Circuit Description

Proprietary circuit design and high quality magnetics are necessary to yield the high THD performance specified. Deviation from the Zetex recommended solution could significantly degrade performance.

The speaker is connected as a Bridge Tied Load (BTL). This means that both sides of the speaker are driven from the output bridge and therefore neither side of the speaker connects to ground. This allows maximum power to be delivered to the load, from a given supply voltage. The supply voltage for this solution is nominally 16V for 25W into a  $4\Omega$  load.

A schematic diagram for the solution is shown in Figure 4. The audio input is AC coupled and applied to a low pass filter and a phase splitter built around the NE5532 dual op-amp. One of these op-amps is configured as a voltage follower and the other as a X1 inverting amplifier. This produces in phase and inverted signals for application to the ZXCD1000. The op-amp outputs are AC coupled into the ZXCD1000 Audio A and Audio B inputs via simple R-C low pass filters (R16/C3 and R15/C7). The op-amps are biased to a DC level of approximately 6V by R11 and R12.

The Pulse Width Modulated (PWM) outputs, OutA and OutB, which contain the audio information, are AC coupled and DC restored before driving the Zetex ZXM64P03X and ZXM64N03X PMOS and NMOS output bridge FET's. AC coupling is via C17, C18, C19 and C20. DC restoration is provided by the D2(A1a)/R4, D1(A4a)/R2 and D3(A1a)/R6, D4(A4a)/R9 components. This technique allows the output stage supply voltage to be higher than the high level of the OutA and OutB outputs (approximately 8.5V), whilst still supplying almost the full output voltage swing to the gates of the bridge FET's (thereby ensuring good turn on). This can be exploited to yield higher power solutions with higher supply voltages – this is discussed later.

The resistor/diode combinations (R5/D2(A16b), R3/D1(A4b), R7/D3(A1b) and R8/D4(A4b)) in series with the bridge FET gates, assist in controlling the switching of the bridge FET's. This design minimises shoot through currents whilst still achieving the low distortion characteristics of the system.

The purpose of the special inductors in conjunction with the output capacitors C23, C24, C25 and C26 is to low pass filter the high frequency switching PWM signal that comes from the bridge. Thus the lower frequency audio signal is recovered and is available at the speakerA and speakerB outputs across which the speaker should be connected. Zetex can offer advice on suitable source for the specialist magnetics.

The optional components R17 and C3 form a Zobel network. The applicability of these depends upon the application and speaker characteristics. Suggested values are 47nF and 10 ohms

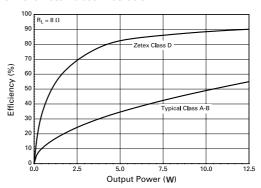

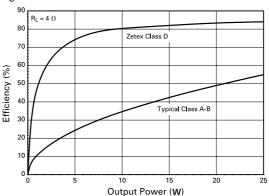

#### Efficiency

The following plots show the measured efficiency of the Zetex solution at various power levels into both  $4\Omega$  and  $8\Omega$  loads. As a comparison, typical efficiency is plotted for a class A-B amplifier. They clearly demonstrate the major efficiency benefits available from the Zetex class D solution.

Output Stage Efficiency v Power with  $4\Omega$  and  $8\Omega$  loads

Figure 5

#### Class D Mono Open Loop solution (Bridge Tied Load - BTL) Solution - Demonstration board

The circuit design shown in figure 4 is available as a demonstration board to enable evaluation of the circuit excellent performance. Full bill of materials (BOM) and Gerber files are also available. The demonstration board part number is ZXCD1000EVMOL. Layout and component selection are critical to maximising performance from this solution, the demonstration board and circuit can be used as a guide to facilitate design of production circuits. Zetex applications can advise if any circuit modifications are required for specific requirements.

The board can be used to demonstrate the ZXCD amplifier capability with output power typically of 25W into  $4\Omega$  or  $8\Omega$  load depending on chosen supply voltage. Operating instructions are included in the demonstration board literature.

Figure 6

Mono solution demonstration board

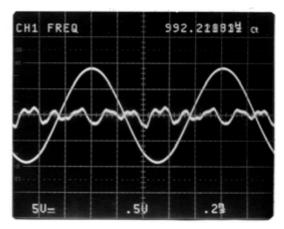

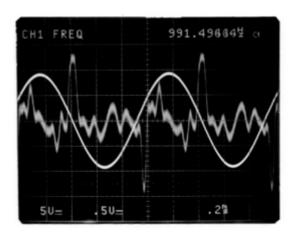

A very important feature of the Zetex solution is that the residual distortion is almost totally free of any crossover artifacts. This lack of crossover distortion sets the ZXCD1000 solutions quite apart from most other presently available low cost solutions, which in general suffer from severe crossover distortion problems.

It is well known that this kind of distortion is particularly unpleasant to the listener. The two scope traces of Figure 7 clearly show the lack of such artifacts with the Zetex solution

Figure 7a ZETEX Class D Solution. (10W into  $4\Omega$ ) Note lack of Crossover Artifacts

Figure 7b Typical Class D Solution. Note Large Crossover Artifacts

#### Other Solutions - Stereo, Closed Loop and Higher Powers.

#### **STEREO**

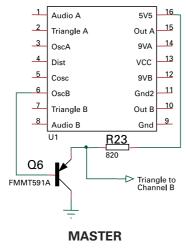

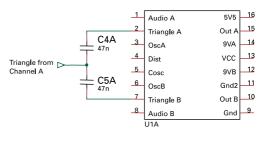

It is possible to duplicate the above solution to give a 2 channel stereo solution. However if the oscillator frequencies are not locked together, a beat can occur which is acoustically audible. This is undesirable. A stereo solution which avoids this problem can be achieved by synchronising the operating frequencies of both ZXCD1000's class D controller IC's, by slaving one device from the other. This is illustrated in Figure 8.

Great care must be taken when linking the triangle from the master to the slave. Any pickup can cause slicing errors and result in increased distortion. The best connection method is to run two tracks, side by side, from the master to the slave. One of these tracks would be the triangle itself, and the other would be the direct local ground linking the master pin9 ground to the slave pin 9 ground.

A demonstration board, ZXCD1000EVSOL, is available for a stereo 25W solution.

**SLAVE**

Figure 8 Frequency synchronisation for stereo applications

Figure 9

ISSUE 2 - APRIL 2002

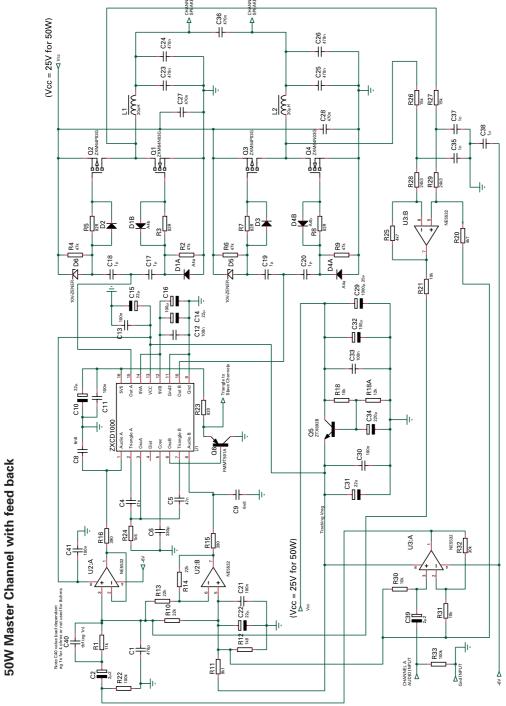

#### Class D 50W Mono Bridge Tied Load (BTL) Solution with Feedback – Circuit Description

With the addition of feedback (hence closed loop solution) it is possible to obtain even better THD performance. A schematic diagram for this is shown in Figure 9. Again proprietary circuit and special magnetic design is necessary to yield the high THD performance and deviation from this could significantly reduce performance.

Much of the circuitry is the same as described for the open loop solution. The main differences being a consequence of using the feedback circuitry. The audio input is ac coupled and applied to an op-amp (1/2 of U3) configured as a non-inverting amplifier with a gain of approximately 4. Feedback is applied differentially from the bridge outputs via the other half of U3 op-amp. A portion of the single ended output from this op-amp is subtracted from the output of the non-inverting op-amp output above. Overall negative feedback is applied due to the polarity and connection of the signals involved.

The audio signal from the above circuitry is applied to a phase splitter as was done for the open loop solution. This is built around the other 5532 dual op-amp (U2). One of these op-amps is configured as a voltage follower and the other as a X1 inverting amplifier. This produces in phase and inverted signals for application to the ZXCD1000 Audio A and Audio B inputs respectively.

The output circuitry downstream of the ZXCD1000 is as described for the open loop solution. In order to support the 50W output power of this solution a 25V rail is required for a  $4\Omega$  load. The MOSFETs used are SOT223 packaged (ZXM64N035G and ZXM64P035).

Further information on this design is available through Zetex applications.

#### **Higher Power Solutions**

With some modifications the applications solutions can be extended to give output power up to 100W. The main differences being the supply voltage, the TO220 MOSFETs, and the output magnetics. The magnetics for 100W are necessarily larger than required for 25/50W in order to handle the higher load currents. For 100W operation the supply voltage to the circuit is nominally 35V with a  $4\Omega$  load. However the maximum supply voltage to the ZXCD1000 class D controller IC is 18V, hence a voltage dropper is required. This could be done, for example, as in the open loop solution described previously. A 100W circuit is shown on figure 10. This features a 35V bridge supply TO220 MOSFETs (ZXM64N035L3 and ZXM64P035L3) and also proposed protection circuits for over current and over temperature and an alternative anti pop circuit. Further information on this 100W reference design can be obtained through Zetex applications.

The ZXCD1000 class D controller IC is inherently capable of driving even higher power solutions, with the appropriate external circuitry. However as stated above the maximum supply voltage to the ZXCD1000 class D controller IC is 18V and the higher supply voltages must therefore be dropped. Also due consideration must be given to the ZXCD1000 output drive levels and the characteristics of the bridge MOSFET's. The latter must be sufficiently enhanced by the OutA and OutB outputs to ensure the filter and load network is driven properly. If the gate drive of the ZXCD1000 is too low for the chosen MOSFET then the OUTA and OUTB signal must be buffered using an appropriate MOSFET driver circuit. Additionally, suitable magnetics are essential to achieve good THD performance.

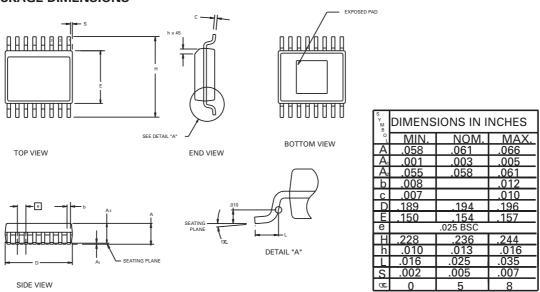

#### Package details

The ZXCD1000 is available in a 16 pin exposed pad QSOP package. The exposed pad on the underside of the package should be soldered down to an area of copper on the PCB, to function as a heatsink. The PCB should have plated through vias to the underside of the board, again connecting to an area of copper.

100W Mono Class D Solution

Figure 10

#### **ZXCD1000 Solution performance figures**

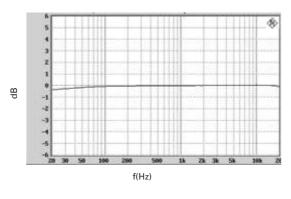

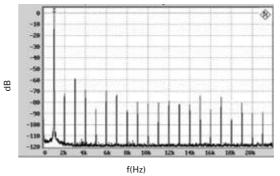

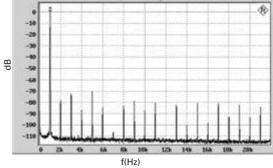

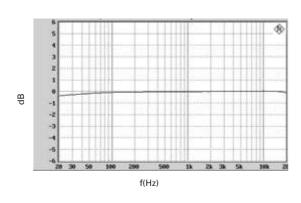

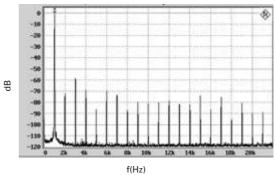

Typical performance graphs for the Zetex 25W open loop solution are shown here for both 4 and  $8\Omega$  loads. These graphs further demonstrate the true high fidelity performance achieved by the Zetex solutions.

THD v Power into 8 at 1kHz

FFT of distortion and noise floor at 1W (8 load)

Frequency response (8 load)

FFT of distortion and noise floor at 10W (8 load)

THD v Power into 4 at 1kHz

FFT of distortion and noise floor at 1W (4 load)

Frequency response (4 load)

Note roll off. This can be corrected by using an alternative values for output filter components.

FFT of distortion and noise floor at 20W (4 load)

#### **PACKAGE DIMENSIONS**

#### **ORDERING INFORMATION**

| Device       | Description       | Package | T&R Suffix |

|--------------|-------------------|---------|------------|

| ZXCD1000EQ16 | Class D modulator | eQSOP16 | TA, TC     |

$Information \ on \ Zetex \ reference \ designs, \ MOSFETs \ and \ demonstration \ boards \ can be \ obtain \ by \ contacting \ Zetex \ applications \ or \ by \ visiting \ www.zetex.com/audio$

#### © Zetex plc 2001

| Zetex plc                   | Zetex GmbH                  | Zetex Inc                 | Zetex (Asia) Ltd            |

|-----------------------------|-----------------------------|---------------------------|-----------------------------|

| Fields New Road             | Streitfeldstraße 19         | 700 Veterans Memorial Hwy | 3701-04 Metroplaza, Tower 1 |

| Chadderton                  | D-81673 München             | Hauppauge, NY11788        | Hing Fong Road              |

| Oldham, OL9 8NP             |                             |                           | Kwai Fong                   |

| United Kingdom              | Germany                     | USA                       | Hong Kong                   |

| Telephone (44) 161 622 4422 | Telefon: (49) 89 45 49 49 0 | Telephone: (631) 360 2222 | Telephone: (852) 26100 611  |

| Fax: (44) 161 622 4420      | Fax: (49) 89 45 49 49 49    | Fax: (631) 360 8222       | Fax: (852) 24250 494        |

These offices are supported by agents and distributors in major countries world-wide.

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.

For the latest product information, log on to **www.zetex.com**

ISSUE 2 - APRIL 2002