Technical documentation

Support & training

ADS58J64 SBAS807B – JANUARY 2017 – REVISED DECEMBER 2021

# ADS58J64 Quad-Channel, 14-Bit, 1-GSPS Telecom Receiver Device

# 1 Features

- Quad Channel

- 14-Bit Resolution

- Maximum Sampling Rate: 1 GSPS

- Maximum Output Sample Rate: 500 MSPS

- Analog Input Buffer With High-Impedance Input

- Input 3-dB Bandwidth: 1 GHz

- Output Options:

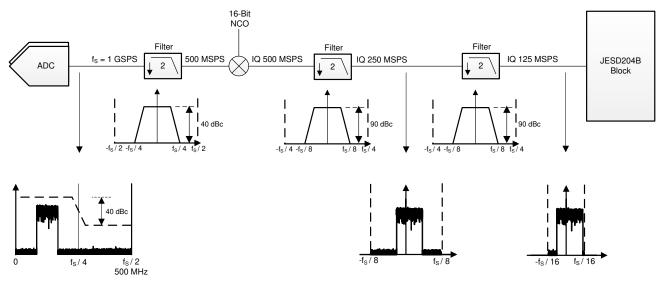

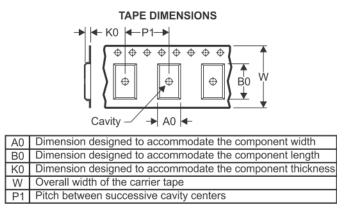

- Rx: Decimate-by-2 and -4 Options With Low-Pass Filter

- 200-MHz Complex Bandwidth or 100-MHz Real Bandwidth Support

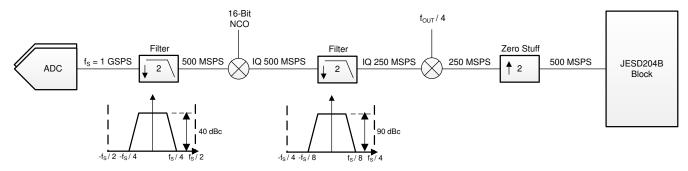

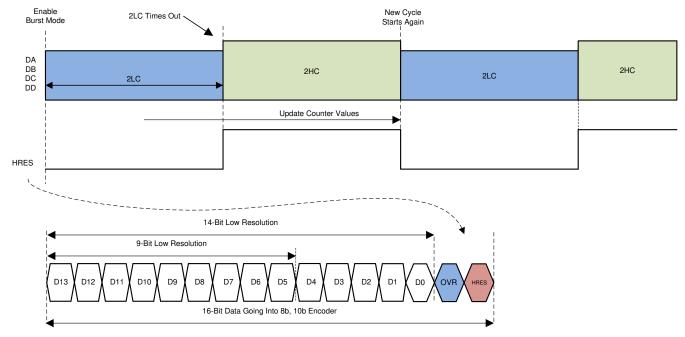

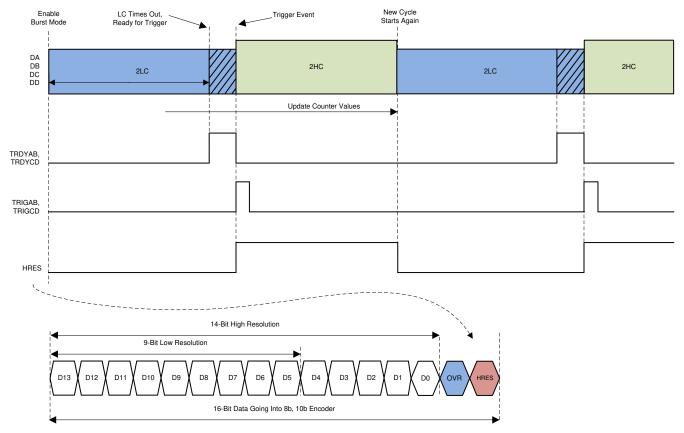

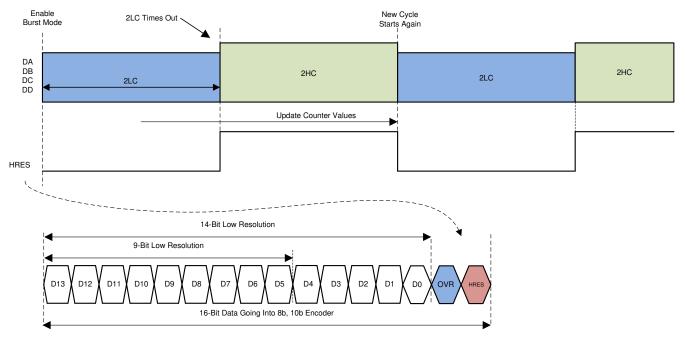

- DPD FB: 2x Decimation With 14-Bit Burst Mode Output

- 1.1-V<sub>PP</sub> Differential Full-Scale Input

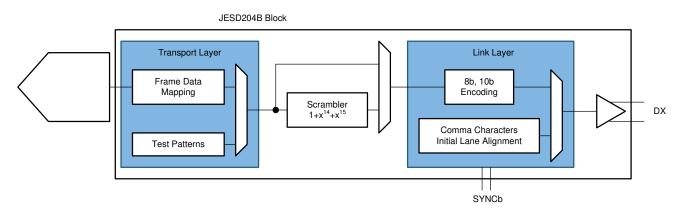

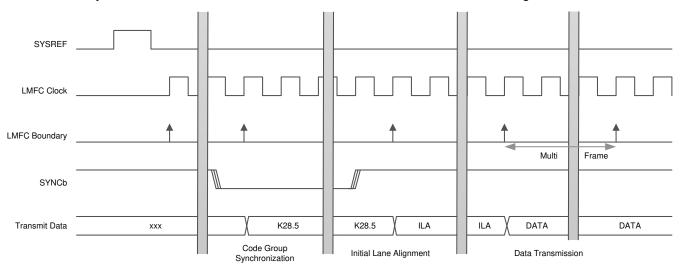

- JESD204B Interface:

- Subclass 1 Support

- 1 Lane per ADC Up to 10 Gbps

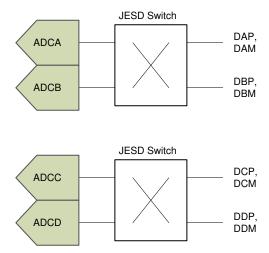

- Dedicated SYNC Pin for Pair of Channels

- Support for Multi-Chip Synchronization

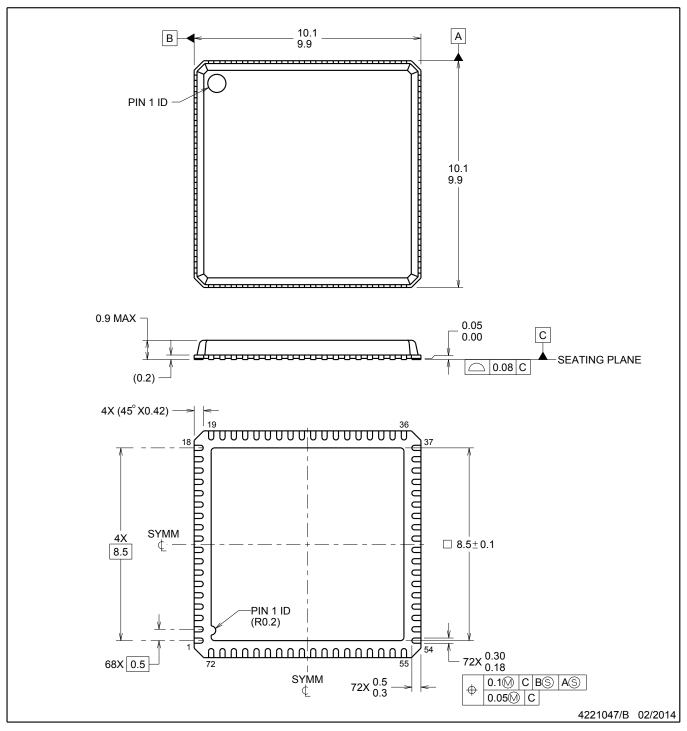

- 72-Pin VQFN Package (10 mm × 10 mm)

- Power Dissipation: 625 mW/Ch

- Spectral Performance

- (Burst Mode, High Resolution):

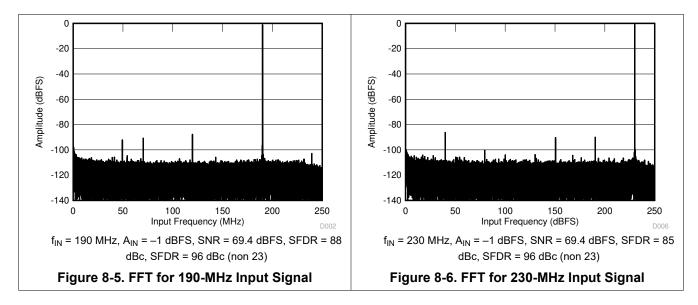

- f<sub>IN</sub> = 190 MHz IF at -1 dBFS:

- SNR: 69 dBFS

- NSD: –153 dBFS/Hz

- SFDR: 86 dBc (HD2, HD3), 95 dBFS (Non HD2, HD3)

- f<sub>IN</sub> = 370 MHz IF at -3 dBFS:

- SNR: 68.5 dBFS

- NSD: -152.5 dBFS/Hz

- SFDR: 80 dBc (HD2, HD3), 86 dBFS (Non HD2, HD3)

# 2 Applications

- Multi-Carrier GSM Cellular Infrastructure Base Stations

- Multi-Carrier Multi-Mode Cellular Infrastructure Base Stations

- Telecommunications Receivers

- Telecom DPD Observation Receivers

# **3 Description**

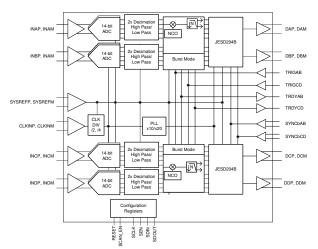

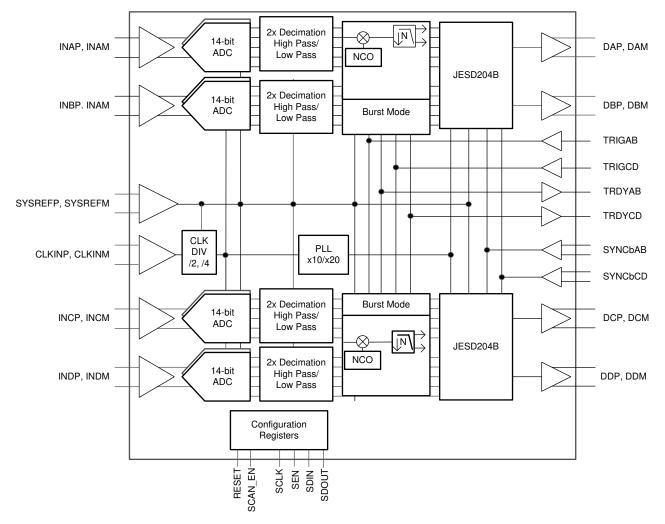

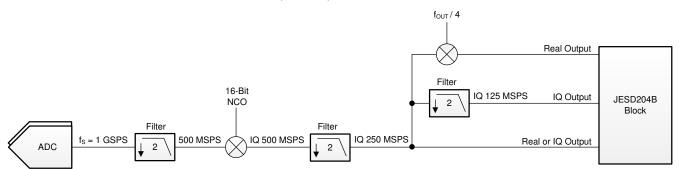

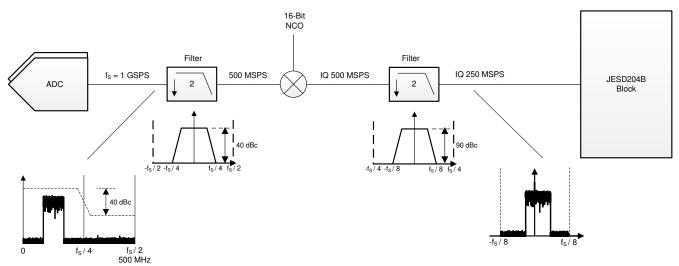

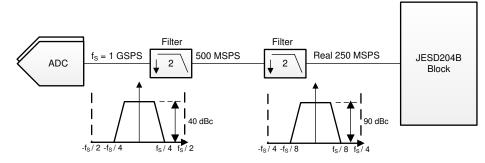

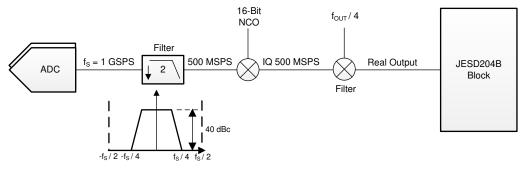

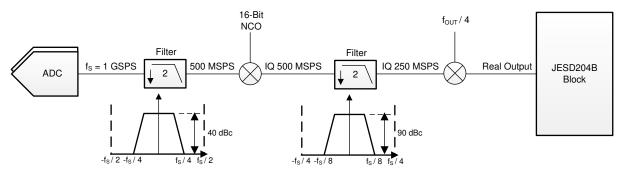

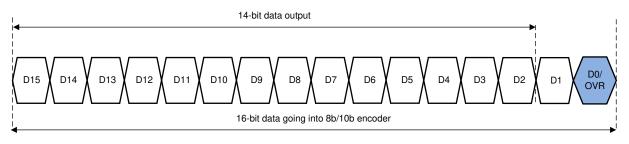

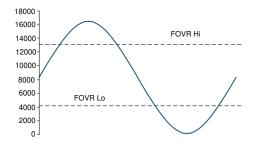

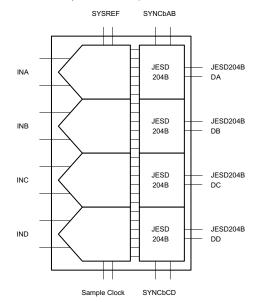

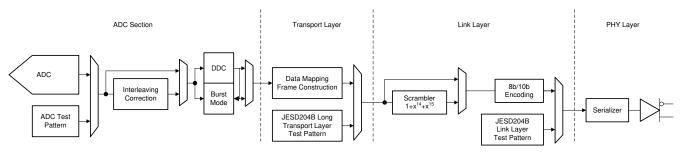

The ADS58J64 is a low-power, wide-bandwidth, 14bit, 1-GSPS, quad-channel, telecom receiver device. The ADS58J64 supports a JESD204B serial interface with data rates up to 10 Gbps with one lane per channel. The buffered analog input provides uniform input impedance across a wide frequency range and minimizes sample-and-hold glitch energy. The ADS58J64 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with very low power consumption. The digital signal processing block includes complex mixers followed by low-pass filters with decimate-by-2 and -4 options supporting up to a 200-MHz receive bandwidth. The ADS58J64 also supports a 14-bit, 500-MSPS output in burst mode, making the device suitable for a digital pre-distortion (DPD) observation receiver.

The JESD204B interface reduces the number of interface lines, thus allowing high system integration density. An internal phase-locked loop (PLL) multiplies the incoming analog-to-digital converter (ADC) sampling clock to derive the bit clock that is used to serialize the 14-bit data from each channel.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| ADS58J64    | VQFN (72) | 10.00 mm × 10.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## Simplified Block Diagram

# **Table of Contents**

| 1 Features                                     | 1              |

|------------------------------------------------|----------------|

| 2 Applications                                 | 1              |

| 3 Description                                  | 1              |

| 4 Revision History                             | 2              |

| 5 Pin Configuration and Functions              |                |

| 6 Specifications                               | <mark>5</mark> |

| 6.1 Absolute Maximum Ratings                   |                |

| 6.2 ESD Ratings                                |                |

| 6.3 Recommended Operating Conditions           |                |

| 6.4 Thermal Information                        |                |

| 6.5 Electrical Characteristics                 | 7              |

| 6.6 AC Performance                             | 8              |

| 6.7 Digital Characteristics                    | 10             |

| 6.8 Timing Characteristics                     | 11             |

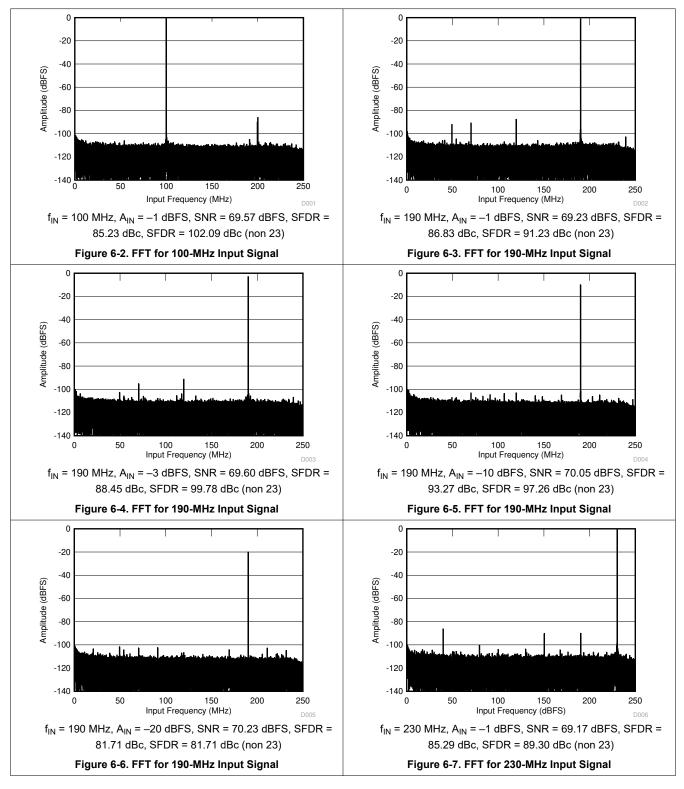

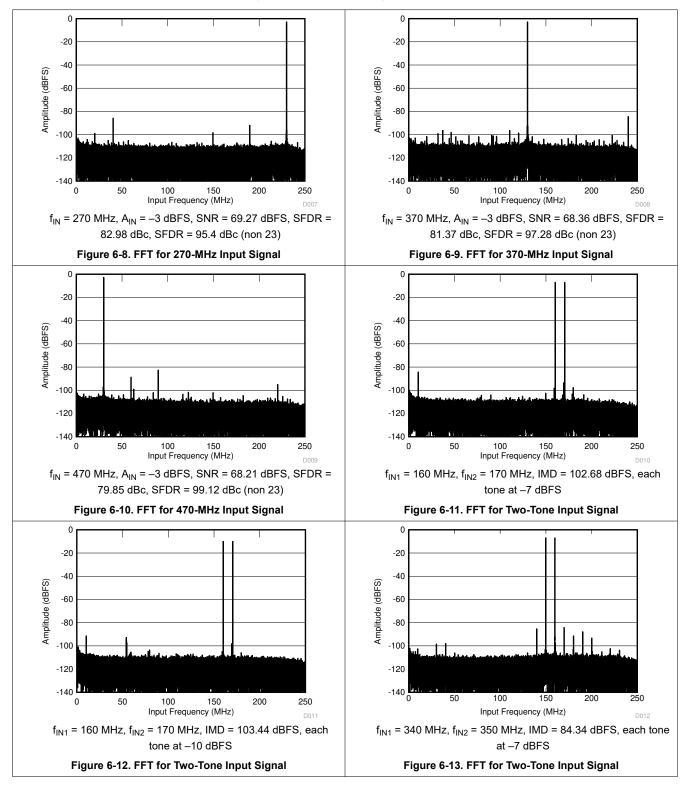

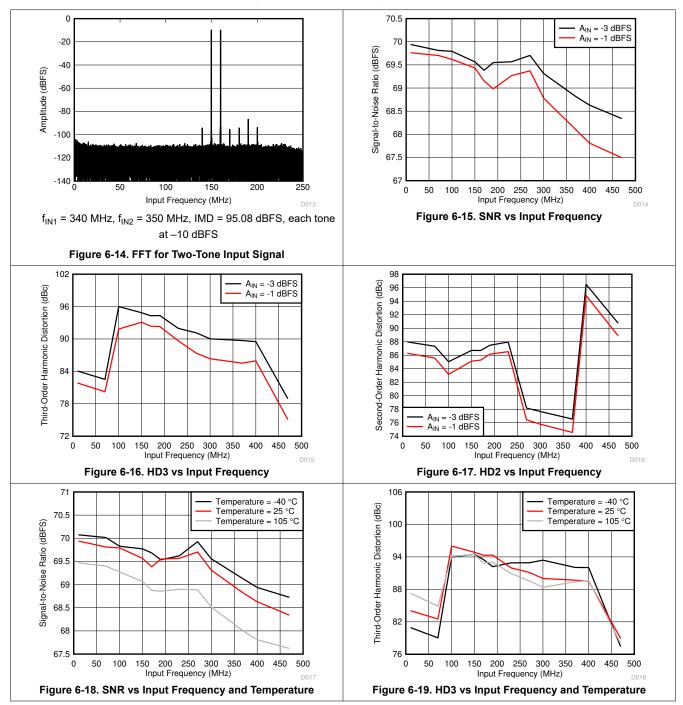

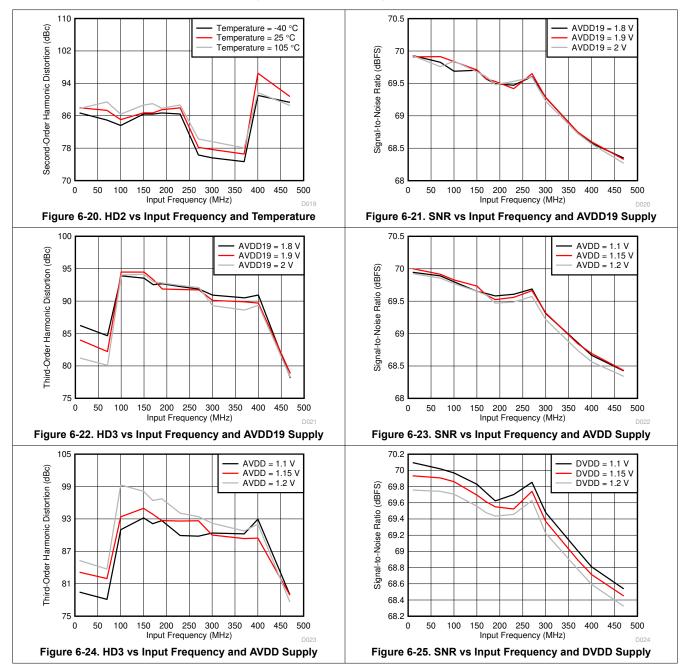

| 6.9 Typical Characteristics: 14-Bit Burst Mode |                |

| 6.10 Typical Characteristics: Mode 2           | 18             |

| 6.11 Typical Characteristics: Mode 0           |                |

| 7 Detailed Description                         |                |

| 7.1 Overview                                   |                |

| 7.2 Functional Block Diagram                   | 20             |

| 7.3 Feature Description                               | .21 |

|-------------------------------------------------------|-----|

| 7.4 Device Functional Modes                           |     |

| 7.5 Programming                                       | 32  |

| 7.6 Register Maps                                     | .39 |

| 8 Application and Implementation                      |     |

| 8.1 Application Information                           |     |

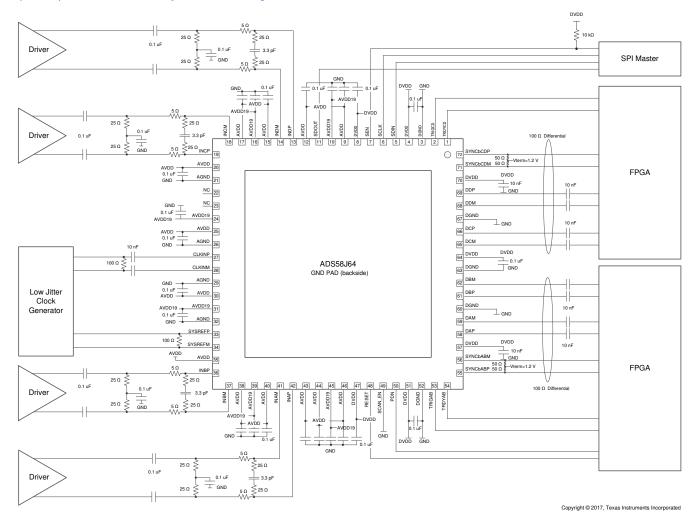

| 8.2 Typical Application                               | 73  |

| 9 Power Supply Recommendations                        |     |

| 10 Layout                                             |     |

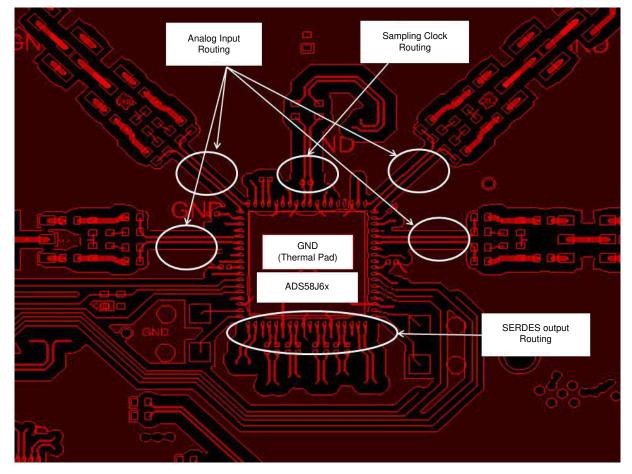

| 10.1 Layout Guidelines                                |     |

| 10.2 Layout Example                                   |     |

| 11 Device and Documentation Support                   |     |

| 11.1 Receiving Notification of Documentation Updates. |     |

| 11.2 Support Resources                                |     |

| 11.3 Trademarks                                       |     |

| 11.4 Electrostatic Discharge Caution                  |     |

| 11.5 Glossary                                         |     |

| 12 Mechanical, Packaging, and Orderable               |     |

| Information                                           | 77  |

|                                                       |     |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision A (January 2017) to Revision B (December 2021)                                                     | Page                  |

|---|-------------------------------------------------------------------------------------------------------------------------|-----------------------|

| • | Updated the numbering format for tables, figures, and cross-references throughout the document                          | 1                     |

| • | Added RHH (VQFN) package option                                                                                         | 3                     |

| • | Changed description for GAINWORD                                                                                        |                       |

| • | Added the text Also need to enable OVR_ON_LSB bit in DIGTOP page to register 3 and 1 of Register 2 CHX page.            |                       |

| С | hanges from Revision * (January 2017) to Revision A (January 2017)                                                      | Page                  |

| • | Changed Sample to Sampling in third Features bullet                                                                     | 1                     |

| • | Changed Bandwitdth: 250 MHz to Sample Rate: 500 MSPS in fourth Features bullet                                          |                       |

| • | Added Input 3-dB Bandwidth bullet to Features section                                                                   | 1                     |

| • | Changed plot and SNR and SFDR conditions of Figure 9                                                                    | 12                    |

| • | Added for loading trims to description of bit 1 in Register 64h Field Descriptions                                      | 44                    |

| • | Changed select to set in description of bits 7-0 in Register 8Dh Field Descriptions and Register 8Eh Fiel Descriptions  | ld<br><mark>44</mark> |

| • | Changed select to set in description of bits 7-0 in Register 8Fh Field Descriptions and Register 90h Field Descriptions | d                     |

| • | Added Others: Do not use to Description column of Register 71h Field Descriptions and Register 72h Fi<br>Descriptions   | ield                  |

| • | Changed Others: Do not use to Description column of Register 93h Field Descriptions and Register 94h Descriptions       | r Field               |

| • | Added Valid only when CTRL_LID = 1 to description of bits 7-4 in Register 2Dh Field Descriptions                        | 57                    |

| • | Changed Description column of Register 41h Field Descriptions                                                           |                       |

| • | Changed 1 : to 3 : and added Others: Do not use to Description column of Register 42h Field Descriptio                  |                       |

| • | Changed description of bits 7-0 in Register 07h Field Descriptions                                                      | 65                    |

| • | Changed description of bits 7-0 in Register 08h Field Descriptions                                                      |                       |

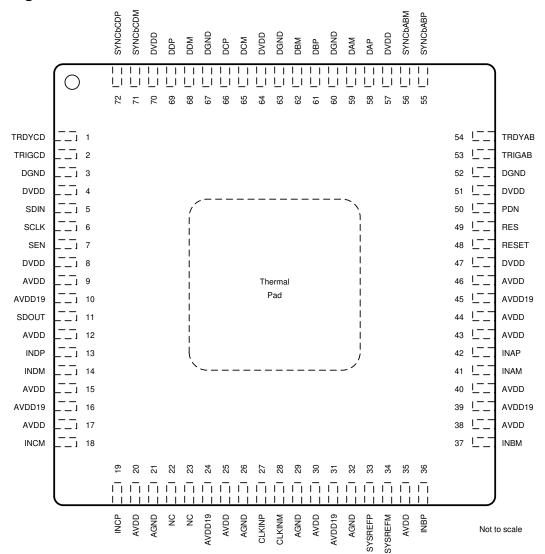

# **5** Pin Configuration and Functions

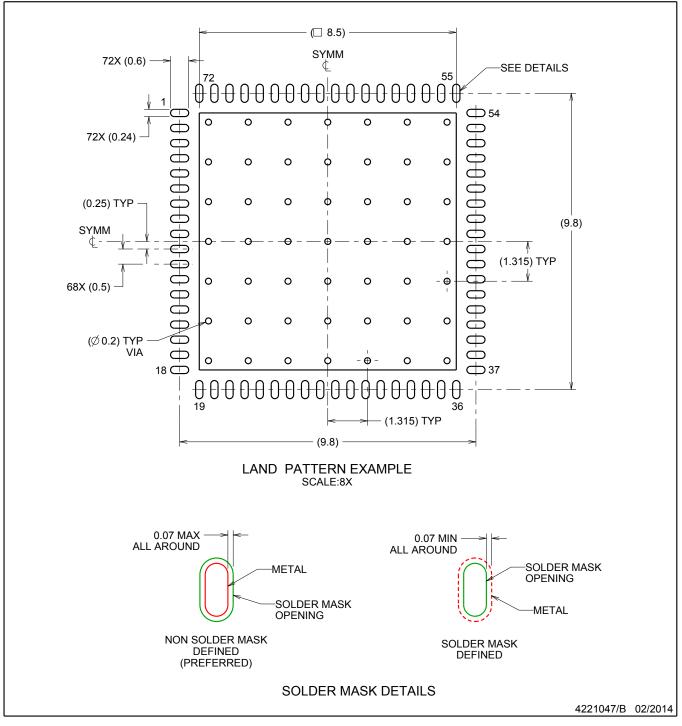

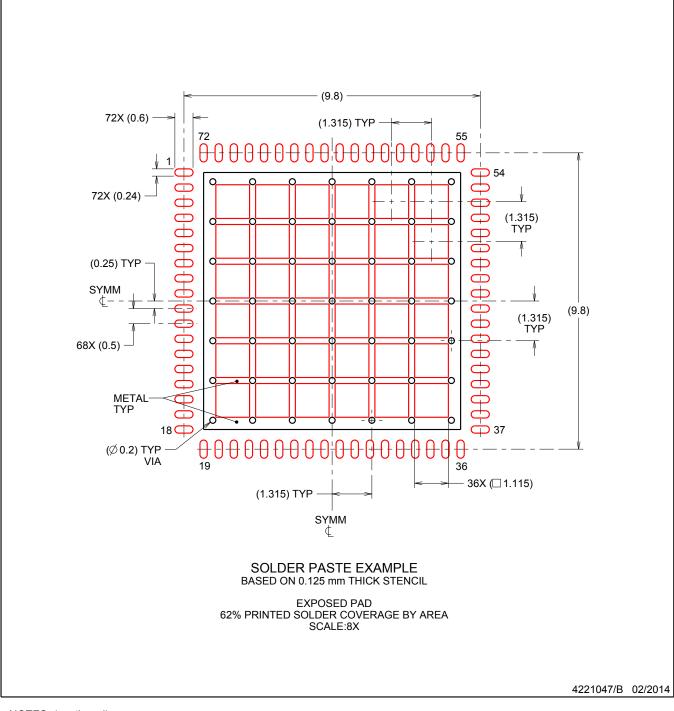

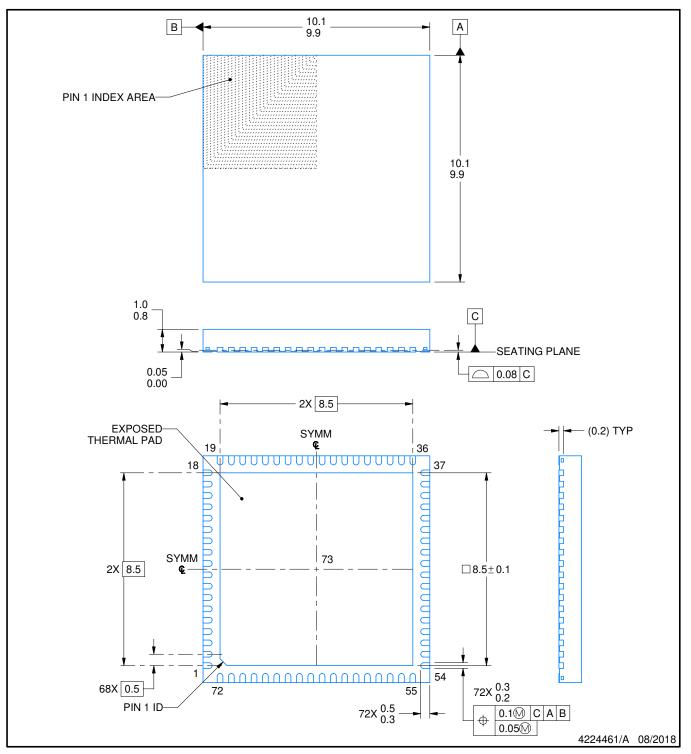

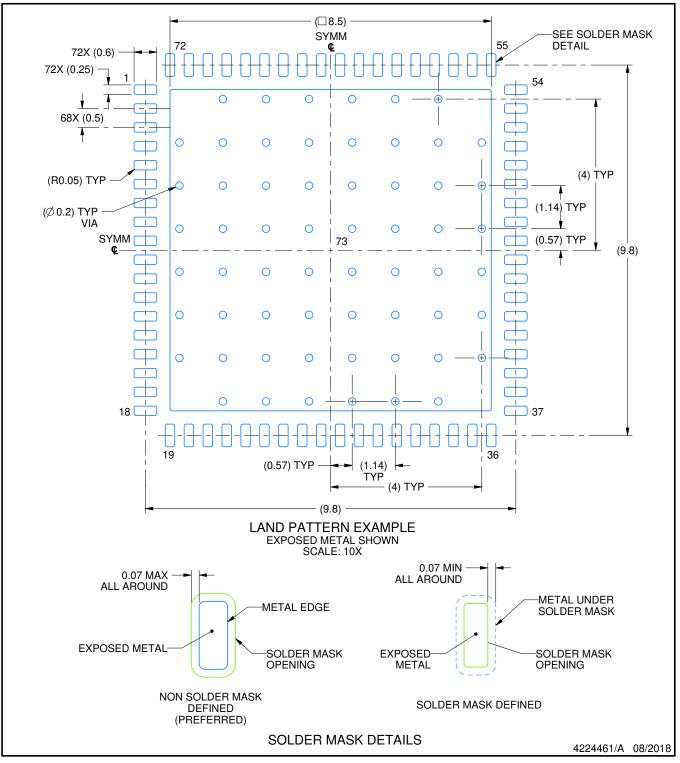

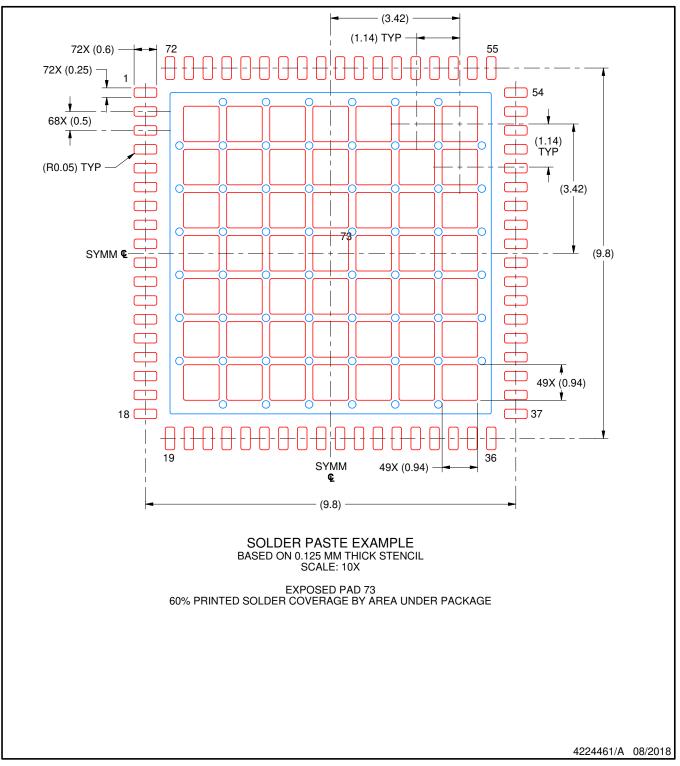

Figure 5-1. RMP or RHH Package 72-Pin VQFN Top View

Table 5-1. Pin Functions

| PIN           |                  | 1/0 | DESCRIPTION                                                                                                          |  |  |  |

|---------------|------------------|-----|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME          | NO.              | 1/0 | DESCRIPTION                                                                                                          |  |  |  |

| INPUT, REFERI | IPUT, REFERENCE  |     |                                                                                                                      |  |  |  |

| INAM          | 41               |     |                                                                                                                      |  |  |  |

| INAP          | 42               |     | Differential analog input pin for channel A, internal bias via a 2-k $\Omega$ resistor to V <sub>CM</sub>            |  |  |  |

| INBM          | 37               |     |                                                                                                                      |  |  |  |

| INBP          | 36               |     | Differential analog input pin for channel B, internal bias via a 2-k $\Omega$ resistor to V <sub>CM</sub>            |  |  |  |

| INCM          | 18               |     | Differential engling input his for channel C, internal historia 2 kO register to V                                   |  |  |  |

| INCP          | 19               |     | Differential analog input pin for channel C, internal bias via a 2-k $\Omega$ resistor to V <sub>CM</sub>            |  |  |  |

| INPUT, REFERI | ENCE (continued) |     |                                                                                                                      |  |  |  |

| INDM 14       |                  |     |                                                                                                                      |  |  |  |

| INDP          | 13               |     | Differential analog input pin for channel D, internal bias via a 2-k $\Omega$ resistor to V <sub>CM</sub>            |  |  |  |

| CLOCK, SYNC   |                  |     |                                                                                                                      |  |  |  |

| CLKINM        | 28               |     |                                                                                                                      |  |  |  |

| CLKINP        | 27               |     | Differential clock input pin for the ADC with internal 100-Ω differential termination, requires external ac coupling |  |  |  |

Copyright © 2021 Texas Instruments Incorporated

# Table 5-1. Pin Functions (continued)

| NAME         NO.         I/O         DESCRIPTION           SYSREFM         34         I         External SYSREF input, requires dc coupling and external termination           SYSREFP         33         I         External SYSREF input, requires dc coupling and external termination           CONTROL, SERIAL         No         22, 23         —         No connection           PDN         50         I/O         Power down. This pin can be configured via an SPI register setting. This pin has an internal           RES         49         —         Reserved pin, connect to GND           RESET         48         I         Hardware reset; active high. This pin has an internal 10-kΩ pulldown resistor.           SDIN         5         I         Serial interface clock input. This pin has an internal 10-kΩ pulldown resistor.           SDUT         11         O         1.8-V logic serial interface data output           SEN         7         I         Serial interface enable. This pin has an internal 10-kΩ pulldown resistor.           SDUT         11         O         1.8-V logic serial interface data output           TRDYAB         54         O         Trigger-ready output for burst mode for channels A and B. This pin can be configured via SPI tignal for all four channels in burst mode, and can be left open if not used.           TRIGAB         53         <                                                                                                                                                                                        | PIN                        |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|

| SYSREFP         33         I         External SYSREF input, requires dc coupling and external termination           CONTROL, SERIAL         No         Pomer down. This pin can be configured via an SPI register setting. This pin has an internal resistor.           RES         49          Reserved pin, connect to GND           SCLK         6         I         Serial interface class input. This pin has an internal 10-kΩ pulldown resistor.           SDOUT         11         0         1.8-V logic serial interface data output           SEN         7         I         Serial interface data output           TRDYAB         54         0         Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.           TRDYCD         1         0         Trigger-ready output                                                                                                                                                                                                                                                                                                               |                            |  |  |  |  |  |

| SYSREP       33       Instruction         CONTROL, SERIAL       NC       22, 23        No connection         PDN       50       I/O       Power down. This pin can be configured via an SPI register setting. This pin has an internal resistor.         RES       49        Reserved pin, connect to GND         RESET       48       I       Hardware reset; active high. This pin has an internal 10-kΩ pulldown resistor.         SCLK       6       I       Serial interface clock input. This pin has an internal 10-kΩ pulldown resistor.         SDUT       11       O       1.8-V logic serial interface data output.         SEN       7       I       Serial interface enable. This pin has an internal 10-kΩ pulldown resistor.         SDUT       11       O       1.8-V logic serial interface enable. This pin has an internal 10-kΩ pulldown resistor.         SDUT       11       O       1.8-V logic serial interface enable. This pin can be for pen if not used.         TRDYAB       54       O       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       Q       Trigger-ready output for burst mode for channels A and B. This pin can be configured via SPI to signal for all four channels in burst mode, and can be and can be connected to GND if not used. This pin puld/                                                                                                                                                               |                            |  |  |  |  |  |

| NC         22,23         —         No connection           PDN         50         I/O         Power down. This pin can be configured via an SPI register setting. This pin has an internal resistor.           RES         49         —         Reserved pin, connect to GND           RESET         48         I         Hardware reset; active high. This pin has an internal 10-kΩ pulldown resistor.           SCLK         6         I         Serial interface clock input. This pin has an internal 10-kΩ pulldown resistor.           SDIN         5         I         Serial interface data input. This pin has an internal 10-kΩ pulldown resistor.           SDUT         11         O         1.8-V logic serial interface data output           SEN         7         I         Serial interface enable. This pin has an internal 10-kΩ pulldown resistor.           SDUT         11         O         1.8-V logic serial interface data output           SEN         7         I         Serial interface enable. This pin has an internal 10-kΩ pulldown resistor.           TRDYAB         54         O         Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.           TRDYCD         1         O         Iffaur channels in burst mode, and can be left open if not used. This pin can be configured via SPI t signal for all four                                                                                                                                       |                            |  |  |  |  |  |

| PDN       50       I/O       Power down. This pin can be configured via an SPI register setting. This pin has an internal resistor.         RES       49        Reserved pin, connect to GND         RESET       48       I       Hardware reset; active high. This pin has an internal 10-KΩ pulldown resistor.         SCLK       6       I       Serial interface clock input. This pin has an internal 10-KΩ pulldown resistor.         SDIN       5       I       Serial interface data input. This pin has an internal 10-KΩ pulldown resistor.         SDOUT       11       0       1.8-V logic serial interface data output         SEN       7       I       Serial interface enable. This pin has an internal 10-KΩ pulldown resistor.         SDOUT       11       0       1.8-V logic serial interface data output         SEN       7       I       Serial interface data output         TRDYAB       54       0       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       0       all four channels in burst mode, and can be connected to GND if not used. This pin can be configured via S all four channels in burst mode, and can be connected to GND if not used. This pin dan be configured via S all four channels in burst mode, and can be connected to GND if not used. This pin dan be configured via S pulldown resistor.                                                                                                                 |                            |  |  |  |  |  |

| PDN       50       I/O       resistor.         RES       49        Reserved pin, connect to GND         RESET       48       1       Hardware reset; active high. This pin has an internal 10-kΩ pulldown resistor.         SCLK       6       1       Serial interface clock input. This pin has an internal 10-kΩ pulldown resistor.         SDIN       5       1       Serial interface data input. This pin has an internal 10-kΩ pulldown resistor.         SDOUT       11       0       1.8-V logic serial interface data output         SEN       7       1       Serial interface enable. This pin has an internal 10-kΩ pullup resistor to DVDD.         TRDYAB       54       0       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       0       Trigger-ready output for burst mode, and can be left open if not used.         TRBCRD       2       1       Manual burst mode trigger input for channels A and B. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This pin face are be connected to GND if not used. This pin pulldown resistor.         TRIGAB       53       1       Manual burst mode trigger input for channels C and D. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This                                                                                                   |                            |  |  |  |  |  |

| RESET       48       I       Hardware reset; active high. This pin has an internal 10-kΩ pulldown resistor.         SCLK       6       I       Serial interface clock input. This pin has an internal 10-kΩ pulldown resistor.         SDIN       5       I       Serial interface data input. This pin has an internal 10-kΩ pulldown resistor.         SDUT       11       0       1.8-V logic serial interface data output         SEN       7       I       Serial interface enable. This pin has an internal 10-kΩ pullup resistor to DVDD.         TRDYAB       54       0       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       0       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       0       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRIGAB       53       I       signal for all four channels in burst mode, and can be connected to GND if not used. This pulldown resistor.         DAM       59       0       JESD204B serial data output pin for channel A         DAP       58       0       JESD204B serial data output pin for channel B <td< td=""><td>nal 10-kΩ pulldown</td></td<>                                                                               | nal 10-kΩ pulldown         |  |  |  |  |  |

| SCLK       6       I       Serial interface clock input. This pin has an internal 10-kΩ pulldown resistor.         SDIN       5       I       Serial interface data input. This pin has an internal 10-kΩ pulldown resistor.         SDOUT       11       O       1.8-V logic serial interface data output         SEN       7       I       Serial interface enable. This pin has an internal 10-kΩ pulldown resistor.         SEN       7       I       Serial interface enable. This pin has an internal 10-kΩ pullup resistor to DVDD.         TRDYAB       54       O       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRIGAB       53       I       Manual burst mode trigger input for channels A and B. This pin can be configured via SPI to signal for all four channels in burst mode, and can be connected to GND if not used. This pulldown resistor.         DATA INTERFACE       Manual burst mode trigger input for channels C and D. This pin can be configured via SPI to signal for all four channels in burst mode, and can be connected to GND if not used. This pulldown resistor.         DAM       59       O       JESD204B serial data output pin for channel A         DAP       58                                                               |                            |  |  |  |  |  |

| SDIN       5       1       Serial interface data input. This pin has an internal 10-kΩ pulldown resistor.         SDOUT       11       O       1.8-V logic serial interface data output         SEN       7       1       Serial interface enable. This pin has an internal 10-kΩ pulldown resistor.         TRDYAB       54       O       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRIGAB       53       1       signal for all four channels in burst mode, and can be connected to GND if not used. This p pulldown resistor.         TRIGCD       2       1       Manual burst mode trigger input for channels C and D. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This p pulldown resistor.         DAM       59       0       JESD204B serial data output pin for channel A         DAP       58       0       JESD204B serial data output pin for channel B         DBP       61       0                                                                                          |                            |  |  |  |  |  |

| SDOUT       11       O       1.8-V logic serial interface data output         SEN       7       I       Serial interface enable. This pin has an internal 10-kΩ pullup resistor to DVDD.         TRDYAB       54       O       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRIGAB       53       I       Manual burst mode trigger input for channels A and B. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This p pulldown resistor.         DATA INTERFACE       DAM       59       O       JESD204B serial data output pin for channel A         DBM       62       O       JESD204B serial data output pin for channel B       Descented to GND if not used.         DCM       65       O       JESD204B serial data output pin for channel B       Descented to GND if not used.         DP       61       O       JESD204B serial data output pin for channel A       Descented to GND if not used.                                                                                     |                            |  |  |  |  |  |

| SEN       7       I       Serial interface enable. This pin has an internal 10-kΩ pullup resistor to DVDD.         TRDYAB       54       0       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYAB       54       0       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       0       Trigger-ready output for burst mode for channels C and D. This pin can be configured via SPI t signal for all four channels in burst mode, and can be left open if not used.         TRIGAB       53       I       Manual burst mode trigger input for channels A and B. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This p pulldown resistor.         TRIGCD       2       I       Manual burst mode trigger input for channels C and D. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This p pulldown resistor.         DATA INTERFACE       DAM       59       0       JESD204B serial data output pin for channel A         DBM       62       0       JESD204B serial data output pin for channel A       Descented to GND if not used.         DCM       65       0       JESD204B serial data output pin for channel B       Descented to GND if not used.       <                |                            |  |  |  |  |  |

| TRDYAB       54       O       Trigger-ready output for burst mode for channels A and B. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRDYCD       1       O       Trigger-ready output for burst mode for channels C and D. This pin can be configured via S all four channels in burst mode, and can be left open if not used.         TRIGAB       53       1       Manual burst mode trigger input for channels A and B. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This pinuldown resistor.         TRIGCD       2       1       Manual burst mode trigger input for channels C and D. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This pulldown resistor.         DATA INTERFACE       Manual burst mode trigger input for channels C and D. This pin can be configured via SPI t signal for all four channels in burst mode, and can be connected to GND if not used. This pulldown resistor.         DAM       59       0       JESD204B serial data output pin for channel A         DBM       62       0       JESD204B serial data output pin for channel A         DEM       65       0       JESD204B serial data output pin for channel C         DCP       66 |                            |  |  |  |  |  |

| TRDYAB54Oall four channels in burst mode, and can be left open if not used.TRDYCD10Trigger-ready output for burst mode for channels C and D. This pin can be configured via S<br>all four channels in burst mode, and can be left open if not used.TRIGAB531Manual burst mode trigger input for channels A and B. This pin can be configured via SPI to<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.TRIGCD21Manual burst mode trigger input for channels C and D. This pin can be configured via SPI to<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.DATA INTERFACEManual burst mode trigger input for channel ADMDAP580JESD204B serial data output pin for channel ADBM620JESD204B serial data output pin for channel BDCM650JESD204B serial data output pin for channel CDCP660JESD204B serial data output pin for channel DDDM680JESD204B serial data output pin for channel DSYNCbABM561Synchronization input pin for JESD204B port channels A and B. This pin can be configured<br>signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                           |                            |  |  |  |  |  |

| TRDYCD10all four channels in burst mode, and can be left open if not used.TRIGAB531Manual burst mode trigger input for channels A and B. This pin can be configured via SPI to<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.TRIGCD21Manual burst mode trigger input for channels C and D. This pin can be configured via SPI to<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.DATA INTERFACEManual burst mode trigger input for channels C and D. This pin can be configured via SPI to<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.DATA INTERFACEManual burst mode trigger input for channel ADAP58ODBM62ODEP61ODCP66ODESD204B serial data output pin for channel BDDM68ODDP69OSYNCbABM56ISYNCbABP55ISYNCbABP55SYNCbABP55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SPI to a TRDY signal for   |  |  |  |  |  |

| TRIGAB53Isignal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.TRIGCD2IManual burst mode trigger input for channels C and D. This pin can be configured via SPI t<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.DATA INTERFACEIManual burst mode trigger input for channels C and D. This pin can be configured via SPI t<br>signal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.DATA INTERFACEIManual burst mode trigger input for channel A<br>pulldown resistor.DAM59<br>DAPOJESD204B serial data output pin for channel ADBM62<br>DBPOJESD204B serial data output pin for channel BDCM65<br>DCPOJESD204B serial data output pin for channel CDCP66OJESD204B serial data output pin for channel DDDM68<br>SYNCbABMOJESD204B serial data output pin for channel DSYNCbABP55ISynchronization input pin for JESD204B port channels A and B. This pin can be configured<br>signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                          | I SPI to a TRDY signal for |  |  |  |  |  |

| TRIGCD2Isignal for all four channels in burst mode, and can be connected to GND if not used. This p<br>pulldown resistor.DATA INTERFACEDAM59<br>DAP0JESD204B serial data output pin for channel ADBM62<br>DBP0JESD204B serial data output pin for channel BDCM65<br>DCP0JESD204B serial data output pin for channel CDDM66<br>DDP0JESD204B serial data output pin for channel DDDM68<br>DDP0JESD204B serial data output pin for channel DSYNCbABM56<br>Sf1Synchronization input pin for JESD204B port channels A and B. This pin can be configured<br>signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |  |  |  |  |  |

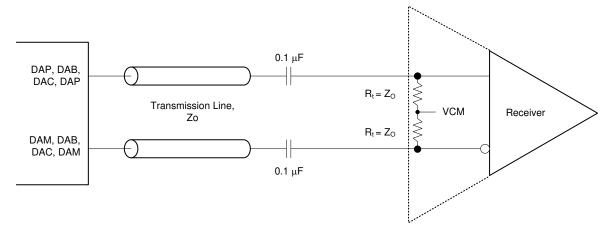

| DAM       59       O       JESD204B serial data output pin for channel A         DAP       58       O       JESD204B serial data output pin for channel A         DBM       62       O       JESD204B serial data output pin for channel B         DBP       61       O       JESD204B serial data output pin for channel B         DCM       65       O       JESD204B serial data output pin for channel C         DCP       66       O       JESD204B serial data output pin for channel C         DDM       68       O       JESD204B serial data output pin for channel D         DDP       69       O       JESD204B serial data output pin for channel D         SYNCbABM       56       I       Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |  |  |  |  |  |

| DAP58OJESD204B serial data output pin for channel ADBM62OJESD204B serial data output pin for channel BDBP61OJESD204B serial data output pin for channel BDCM65OJESD204B serial data output pin for channel CDCP66OJESD204B serial data output pin for channel CDDM68OJESD204B serial data output pin for channel DDDP69OJESD204B serial data output pin for channel DSYNCbABM56ISynchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |  |  |  |  |  |

| DAP       58       JESD204B serial data output pin for channel B         DBP       61       O       JESD204B serial data output pin for channel B         DCM       65       O       JESD204B serial data output pin for channel C         DCP       66       O       JESD204B serial data output pin for channel C         DDM       68       O       JESD204B serial data output pin for channel D         DDP       69       O       JESD204B serial data output pin for channel D         SYNCbABM       56       I       Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |  |  |  |  |  |

| DBP       61       O       JESD204B serial data output pin for channel B         DCM       65       O       JESD204B serial data output pin for channel C         DCP       66       O       JESD204B serial data output pin for channel C         DDM       68       O       JESD204B serial data output pin for channel D         DDP       69       O       JESD204B serial data output pin for channel D         SYNCbABM       56       I       Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |  |  |

| DBP     61     A       DCM     65     O       DCP     66     O       DDM     68     O       DDP     69     O       SYNCbABM     56     I       SYNCbABP     55     I   Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |  |  |  |  |  |

| DCP       66       O       JESD204B serial data output pin for channel C         DDM       68       O       JESD204B serial data output pin for channel D         DDP       69       O       JESD204B serial data output pin for channel D         SYNCbABM       56       I       Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |  |  |  |  |  |

| DCP     66       DDM     68       DDP     69       SYNCbABM     56       SYNCbABP     55       I     Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |  |  |

| DDP       69       O       JESD204B serial data output pin for channel D         SYNCbABM       56       I       Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.         SYNCbABP       55       74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |  |  |  |  |  |

| DDP     69       SYNCbABM     56       SYNCbABP     55       Synchronization input pin for JESD204B port channels A and B. This pin can be configured signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |  |  |  |  |  |

| SYNCbABP         55         I         Synchronization input pin for dESD204D por channels A and D. This pin can be computed signal for all four channels. This pin has an internal differential termination of 100 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |  |  |  |  |  |

| SYNCbABP 55 signal for all four channels. This pin has an internal differential termination of 100 Ω.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ed via SPI to a SYNCb      |  |  |  |  |  |

| SYNCbCDM 71 Synchronization input his for JESD204B part channels C and D. This his can be configurate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | red via SPI to a SYNCb     |  |  |  |  |  |

| SYNCbCDP 72 ' signal for all four channels. This pin has an internal differential termination of 100 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |  |  |  |  |  |

| POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |  |  |  |  |  |

| AGND 21, 26, 29, 32 I Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |  |  |  |  |  |

| AVDD         9, 12, 15, 17, 20,<br>25, 30, 35, 38,<br>40, 43, 44, 46         I         Analog 1.15-V power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |  |  |  |  |  |

| AVDD19 10, 16, 24, 31,<br>39, 45 I Analog 1.9-V supply for analog buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |  |  |  |  |  |

| DGND 3, 52, 60, 63, 67 I Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |  |  |

| DVDD         4, 8, 47,51, 57,<br>64, 70         I         Digital 1.15-V power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |  |  |  |  |  |

| Thermal pad — Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |  |  |  |  |  |

# **6** Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                                        | MIN  | MAX          | UNIT |

|---------------------------------------|------------------------------------------------------------------------|------|--------------|------|

|                                       | AVDD19                                                                 | -0.3 | 2.1          |      |

| Supply voltage                        | AVDD                                                                   | -0.3 | 1.4          | V    |

|                                       | DVDD                                                                   | -0.3 | 1.4          | v    |

|                                       | IOVDD                                                                  | -0.2 | 1.4          |      |

| Voltage between AGND and DGND         |                                                                        | -0.3 | 0.3          | V    |

| Voltage applied to input pins         | INAP, INBP, INAM, INBM, INCP, INDP, INCM, INDM                         | -0.3 | 2.1          |      |

|                                       | CLKINP, CLKINM                                                         | -0.3 | AVDD + 0.3   |      |

|                                       | SYSREFP, SYSREFM, TRIGAB, TRIGCD                                       | -0.3 | AVDD + 0.3   | V    |

|                                       | SCLK, SEN, SDIN, RESET, SYNCbABP,<br>SYNCbABM, SYNCbCDP, SYNCbCDM, PDN | -0.2 | AVDD19 + 0.3 |      |

| Storage temperature, T <sub>stg</sub> |                                                                        | -65  | 150          | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                                                                 |                       | MIN | NOM  | MAX                  | UNIT            |

|----------------------|---------------------------------------------------------------------------------|-----------------------|-----|------|----------------------|-----------------|

|                      | AVDD19                                                                          |                       | 1.8 | 1.9  | 2                    |                 |

| Supply voltage renge | AVDD                                                                            |                       | 1.1 | 1.15 | 1.2                  | V               |

| Supply voltage range | DVDD                                                                            |                       | 1.1 | 1.15 | 1.2                  | v               |

|                      | IOVDD                                                                           |                       | 1.1 | 1.15 | 1.2                  |                 |

|                      | Differential input voltage range                                                |                       |     | 1.1  |                      | V <sub>PP</sub> |

| Analog inputs        | Input common-mode voltage (VCM                                                  | 1)                    |     | 1.3  |                      | V               |

|                      | Input clock frequency, device clock                                             | requency              | 400 |      | 1000                 | MHz             |

|                      | Input clock amplitude differential                                              | Sine wave, ac-coupled |     | 1.5  |                      | V <sub>PP</sub> |

| Clock inputs         | (V <sub>CLKP</sub> – V <sub>CLKM</sub> )                                        | LVPECL, ac-coupled    |     | 1.6  |                      |                 |

|                      |                                                                                 | LVDS, ac-coupled      |     | 0.7  |                      |                 |

|                      | Input device clock duty cycle, defa                                             | ult after reset       | 45% | 50%  | 55%                  |                 |

|                      | Operating free-air, T <sub>A</sub>                                              |                       | -40 |      | 100 <sup>(3)</sup>   |                 |

| Temperature          | Operating junction, T <sub>J</sub>                                              |                       |     | 105  | 125 <mark>(1)</mark> | °C              |

|                      | Specified maximum, measured at on the printed circuit board, T <sub>P-MAX</sub> |                       |     |      | 104.5 <sup>(2)</sup> | U               |

(1) Prolonged use above this junction temperature can increase the device failure-in-time (FIT) rate.

(2) The recommended maximum temperature at the PCB footprint thermal pad assumes the junction-to-package bottom thermal resistance, R<sub>0JC(bot)</sub> = 0.2°C/W, the thermal resistance of the device thermal pad connection to the PCB footprint is negligible, and the device power consumption is 2.5 W.

(3) Assumes system thermal design meets the T<sub>J</sub> specification.

# 6.4 Thermal Information

|                       |                                                             | ADS         |            |      |

|-----------------------|-------------------------------------------------------------|-------------|------------|------|

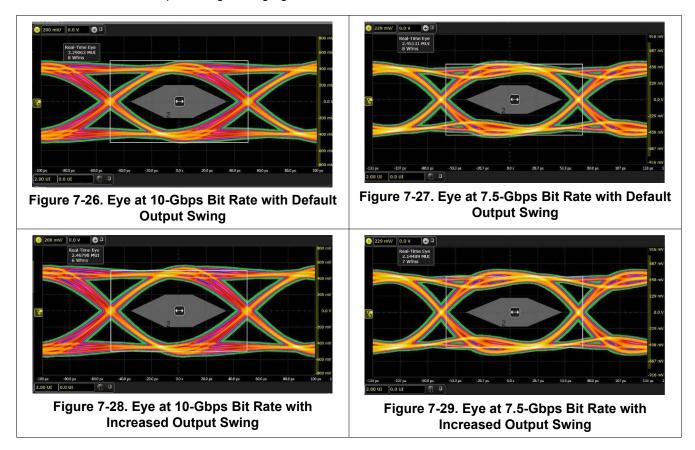

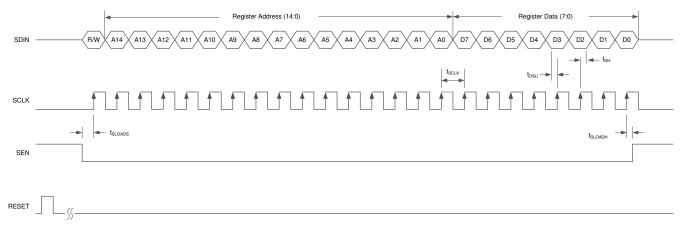

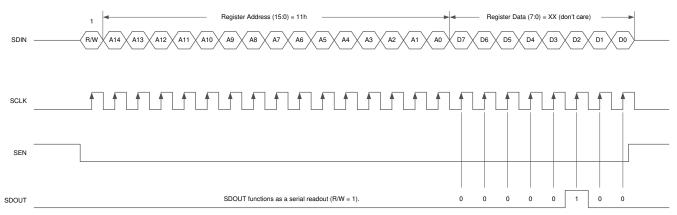

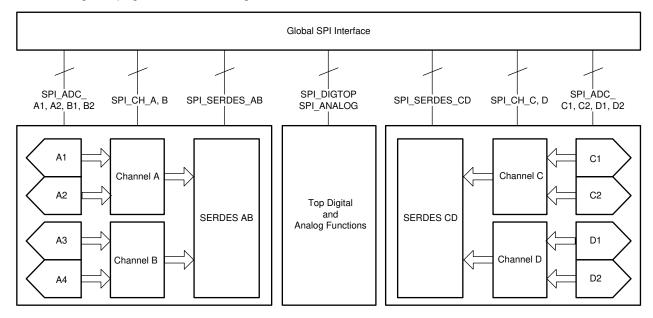

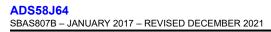

|                       | THERMAL METRIC <sup>(1)</sup>                               | RMP (VQFNP) | RHH (VQFN) | UNIT |