# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 598 EVALUATION CARD FOR THE LTC2051 IN THE DFN PACKAGE

# LTC2051CDD

## DESCRIPTION

Demonstration circuit 598 simplifies the evaluation of the LTC2051CDD op amp in the tiny,  $3\text{mm} \times 3\text{mm}$ , DFN (**D**ual in-line, **F**lat, **N**o-leads) chip-scale package. Electrical performance of this LTC2051 is the same as previous versions. This version is only a packaging enhancement.

An evaluation circuit can easily be built on this board without handling the tiny DFN device. Pads are provided for adding external components and holes are available for jumpers, signal I/O and supply wires. Supply bypass capacitors are already on the board. Alternatively adding two 4-pin headers (0.1" spacing) converts the board to a standard 8-pin DIP format for use with a socket on a second circuit board.

The backside of this evaluation board is void of metal to allow wiring into an existing system with the board resting on top of other components.

### About the LTC2051CDD

The LTC2051 is a Precision Dual, Zero-Drift Op Amp

- □ Maximum Input Offset Voltage of 3µV

- ☐ Maximum Offset Voltage Drift of 30nV/°C

- □ 750µA Supply Current per Amplifier, 25mA Output Current

- $\square$  Low Noise, 1.5 $\mu$ V<sub>P-P</sub> (0.01Hz to 10Hz)

- ☐ No Supply Sequencing Problems

- □ Output Swings to Within 2mV of V<sup>-</sup> and 20mV of V<sup>+</sup>

- □ 7.5KHz Internal Sampling Frequency

- ☐ Total Supply Voltage Range: 2.7V to 11V

Table 1. Typical Performance Summary (Single 3V Supply, T<sub>a</sub>=25°C) Visit www.linear.com for complete data sheet.

| PARAMETER                       | CONDITION     | VALUE      |

|---------------------------------|---------------|------------|

| Common Mode Input Voltage Range |               | 0V to 1.7V |

| Supply Current                  | Per Amplifier | 750μΑ      |

| Offset Voltage                  |               | 3μV        |

| Input Bias Current              |               | ±8pA       |

| Open Loop Voltage Gain          |               | 140dB      |

| CMRR and PSRR                   |               | 135dB      |

| Gain Bandwidth Product          |               | 3MHz       |

| Slew Rate                       |               | 2 V/μsec   |

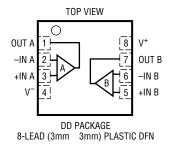

**Device Top Mark Identifier: LAAN**

# **QUICK START PROCEDURE**

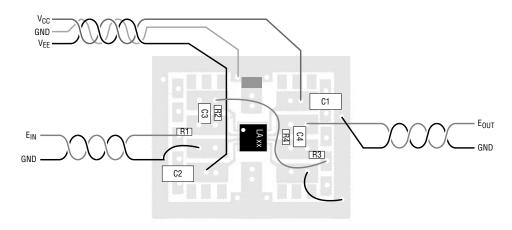

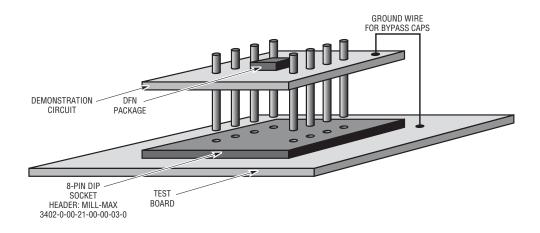

Build the evaluation circuit in one of two ways as shown in Figures 1 and 2.

Figure 1. External Components Directly on the PCB (0.1•F Bypass Capacitors: AVX 1206C104KAT). Example connections shown may not be correct for this device.

Figure 2. Convert the Board to an 8-pin DIP Format

## PACKAGE AND CONNECTION DRAWING

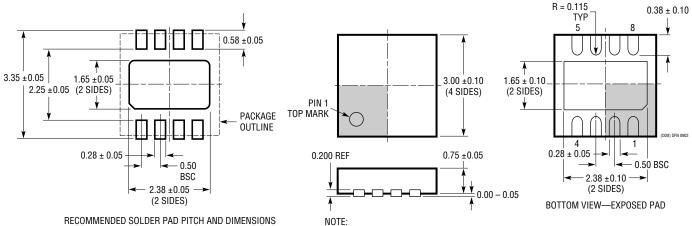

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE MO-229 VARIATION OF (WEED-1)

2. ALL DIMENSIONS ARE IN MILLIMETERS

3. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 4. EXPOSED PAD SHALL BE SOLDER PLATED

## **ASSEMBLY TIPS**

Following are the recommended procedures for soldering surface mount packages to PC boards.

☐ Reflow Soldering with Solder Paste

- Use of solder plated boards is recommended.

- Screen solder paste on board.

- Mount components on board.

- Infrared or forced hot air convection reflow is recommended for best performance. Parameters:

- Preheat peak temperature 125°C ± 15°C and 2°C to 4°C per second rise

- Activation temperature 130°C to 150°C

- Reflow begins at 183°C (63Sn/37Pb)

- Time above 183°C for 30 seconds

- Peak package body temperature 220°C to 245°C

- Dwell time at peak temperature 10 seconds max

- Cooling rate 2°C to 4°C per second

- Clean boards.

- For Vapor Phase Reflow, recommended parameter ranges for:

- Heating rate: 4°C per second max

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 598 EVALUATION CARD FOR THE LTC2051 IN THE DFN PACKAGE

Preheat temperature: 45°C to 80°C

Time above 200°C: 50 seconds to 90 seconds

Peak package temperature: 212°C to 219°C

■ Wave Soldering and Hand Soldering are not recommended.

#### **REWORK GUIDELINES FOR DFN PACKAGES**

Each package mounting site should be reworked one at a time only, to ensure maximum quality and reliability.

Linear Technology has found the following rework procedure to be effective with DFN packages but by no means excludes other methods more suited to specific manufacturing needs.

### ☐ Reflow Temperature Profile

Each package site to be reworked should be individually heated. The reflow temperature profile can be established using a hot gas tool and a thermocouple embedded in the solder joints of a sample setup unit on the PCB.

### ☐ Preheating and Package Removal

A package rework tool with vacuum pickup similar to the A.P.E. Flo-Master can be used. A bottom PCB heater is required to provide preheating of the PCB to approximately 110°C to 120°C. The rework nozzle must be centered with respect to the package in order to direct the hot gas flow over the top of the package while limiting the temperature of the adjacent components to prevent solder reflow.

#### ☐ Site Rework

With a combination on hot gas/vacuum desoldering tool and solder wick ribbons (if necessary), remove

the package and any remaining solder residues. Use a minimal amount of flux if it is required to remove solder residue. This will also assist in leaving a smooth, flat surface for the reattachment of a replacement unit. The site for the package should be thoroughly cleaned with isopropyl alcohol (IPA) and dried with clean dry air (CDA).

## ■ Solder Paste Application

Solder paste may be screen printed on to the package landing site and exposed heat sink pads. Stainless steel stencils are recommended for solder paste application. The printed solder deposits should be 100 percent inspected for uniformity of size and shape. Some applications may have severe space constraints preventing screen printing to be accomplished on the PCB. Therefore, solder paste can be directly applied to the packages landing site and exposed heatsink pad. The package is to be picked and placed using a vision aided system similar to the A.P.E. Sniper SMD 7007 Rework System.

### ☐ Reflow Process

The replacement package, once it has been placed onto the reworked PCB landing site, should be reflowed on the PCB using a hot gas tool on the top of the package and a heater on the bottom of the PCB. The reflow temperature should not exceed 240°C. Note that liquidus temperature for 63/37 Sn/Pb solder is 183°C. Make sure to limit adjacent components to below the solder reflow temperature. The solder paste manufacturer's recommended reflow temperature profile/specifications must be complied with to avoid damage to the PCB and/or adjacent components. A 100 percent post rework visual inspection for good joint wetting is recommended.