# Low-Power, Low-Noise Multichannel Sensor Signal Processor

#### **General Description**

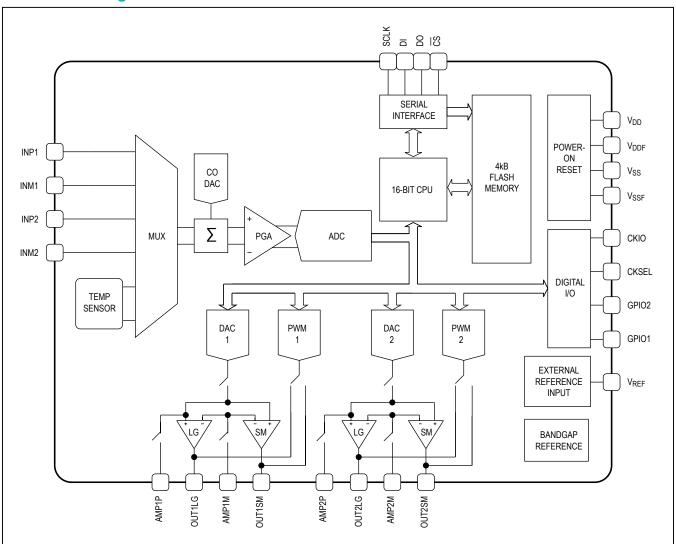

The MAX1464 is a highly integrated, low-power, low-noise multichannel sensor signal processor optimized for industrial, and process-control applications such as pressure sensing and compensation, RTD and thermocouple linearization, weight sensing and classification, and remote process monitoring with limit indication.

The MAX1464 accepts sensors with either single-ended or differential outputs. The MAX1464 accommodates sensor output sensitivities from 1mV/V to 1V/V. The MAX1464 provides amplification, calibration, signal linearization, and temperature compensation that enable an overall performance approaching the inherent repeatability of the sensor without requiring any external trim components.

Two 16-bit voltage-output DACs and two 12-bit PWMs can be used to indicate each of the temperature-compensated sensor signals independently, as a sum or difference signal, or user-defined relationship between each signal and temperature. Uncommitted op amps are available to buffer the DAC outputs, drive heavier external loads, or provide additional gain and filtering.

The MAX1464 incorporates a 16-bit CPU, user-programmable 4kB of FLASH program memory, 128 bytes of FLASH user information, one 16-bit ADC, two 16-bit DACs, two 12-bit PWM digital outputs, four rail-to-rail op amps, one SPI™-compatible interface, two GPIOs, and one on-chip temperature sensor.

The MAX1464 operates from a single 5.0V (typ) supply and is packaged for automotive, industrial, and commercial temperature ranges in a 28-pin SSOP package.

#### **Applications**

- Pressure Sensor Signal Conditioning

- Weight Measurement Systems

- Thermocouple and RTD Linearization

- Transducers and Transmitters

- · Process Indicators

- Calibrators and Controllers

- GMR and MR Magnetic Direction Sensors

<u>Functional Diagram</u> and <u>Detailed Block Diagram</u> appear at end of data sheet.

SPI is a trademark of Motorola. Inc.

#### **Features**

- Programmable Amplification, Calibration, Linearization, and Temperature Compensation

- Two Differential or Four Single-Ended ADC Input Channels

- Accommodates Sensor Output Sensitivities from 1mV/V to 1V/V

- Two DAC/PWM Output Signal Channels

- Supports 4–20mA Current Loop Applications

- 4kB of FLASH Memory for Code and Coefficients

- 128 Bytes of FLASH Memory for User Information

- Integrated Temperature Sensing

- Flexible Dual Op-Amp Block

- Programmable Sensor Input Gain and Offset

- Programmable Sensor Sampling Rate and Resolution

- No External Trim Components Required

#### **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX1464CAI  | 0°C to +70°C    | 28 SSOP     |

| MAX1464C/W* | 0°C to +70°C    | Die         |

| MAX1464EAI  | -40°C to +85°C  | 28 SSOP     |

| MAX1464AAI  | -40°C to +125°C | 28 SSOP     |

<sup>\*</sup>Dice are tested at  $T_A$  = +25°C, DC parameters only.

### **Ordering Information**

# **Absolute Maximum Ratings**

| V <sub>DD</sub> to V <sub>SS</sub>               | 0.3V to +6.0V                    | Operating Temperature Ranges     |                |

|--------------------------------------------------|----------------------------------|----------------------------------|----------------|

| V <sub>DDF</sub> to V <sub>SS</sub>              | 0.3V to +6.0V                    | MAX1464CAI                       | 0°C to +70°C   |

| V <sub>SSF</sub> to V <sub>SS</sub>              | 0.3V to +0.3V                    | MAX1464C/W                       | 0°C to +70°C   |

| All Other Pins to V <sub>SS</sub>                | 0.3V to (V <sub>DD</sub> + 0.3V) | MAX1464EAI                       | 40°C to +85°C  |

| Continuous Power Dissipation ( $T_A = +70^\circ$ | °C)                              | MAX1464AAI                       | 40°C to +125°C |

| 28-Pin SSOP (derate 9.1mW/°C above               | e +70°C)727mW                    | Junction Temperature             | +150°C         |

| ·                                                | •                                | Storage Temperature Range        | 65°C to +150°C |

|                                                  |                                  | Lead Temperature (soldering, 10s | ) +300°C       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{DDF} = V_{DD} = 4.5V \text{ to } 5.5V, V_{SSF} = V_{SS} = 0V, f_{CLK} = 4.0MHz, T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DDF} = V_{DD} = 5.0V, V_{SSF} = V_{SS} = 0V, T_{A} = +25^{\circ}C, \text{ unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER                       | SYMBOL             | CONDITIONS                                                                                                           | MIN | TYP   | MAX  | UNITS            |

|---------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------|-----|-------|------|------------------|

| SUPPLY                          |                    |                                                                                                                      |     |       |      |                  |

| Supply Voltage                  | V <sub>DD</sub>    | V <sub>SS</sub> = V <sub>SSF</sub> = 0V                                                                              | 4.5 | 5.0   | 5.5  | V                |

| FLASH Supply Voltage            | V <sub>DDF</sub>   | V <sub>SS</sub> = V <sub>SSF</sub> = 0V                                                                              | 4.5 | 5.0   | 5.5  | V                |

| Base Operating Current          | I <sub>BO</sub>    | CPU stopped (Note 2)                                                                                                 | 575 | 720   | 890  | μΑ               |

| CPU Current                     | I <sub>CPU</sub>   | All modules off, CPU = on, additive to $I_{BO}$ , $I_{CPU} = I_{DD} + I_{DDF}$ (Note 3)                              | 540 | 840   | 1240 | μA               |

| ADC Current (Note 3)            |                    | All modules off, ADC = on, ADC clk = 1MHz, additive to I <sub>BO</sub> ; the CPU and ADC are not on at the same time | 690 | 1040  | 1394 |                  |

|                                 | I <sub>ADC</sub>   | All modules off, ADC = on, ADC clk = 7kHz, additive to I <sub>BO</sub> ; the CPU and ADC are not on at the same time | 465 | 765   | 1060 | μΑ               |

| DAC Current                     | I <sub>DACn</sub>  | All modules off, DAC = on, additive to I <sub>BO</sub> (n = 1 or 2) (Note 4)                                         |     | 550   | 730  | μA               |

| Large Op-Amp Current            | I <sub>OPLGn</sub> | All modules off, CPU stopped, large op amp = on (n = 1 or 2)                                                         |     | 673   | 1020 | μA               |

| Small Op-Amp Current            | I <sub>OPSMn</sub> | All modules off, CPU stopped, small op amp = on (n = 1 or 2)                                                         |     | 190   | 265  | μΑ               |

| POWER-ON RESET                  |                    |                                                                                                                      |     |       |      |                  |

| V <sub>DDF</sub> POR Threshold  |                    | $V_{DD} > V_{DDF}$                                                                                                   | 3.6 | 4.0   | 4.3  | V                |

| V <sub>DDF</sub> POR Hysteresis |                    |                                                                                                                      |     | -0.85 |      | V                |

| ANALOG INPUT                    |                    |                                                                                                                      |     |       |      |                  |

|                                 |                    | PGA[4:0] = 00000, CLK[2:0] = 000                                                                                     |     | 430   |      |                  |

|                                 |                    | PGA[4:0] = 01010, CLK[2:0] = 000                                                                                     |     | 55    |      | kΩ               |

|                                 |                    | PGA[4:0] = 11111, CLK[2:0] = 000                                                                                     |     | 36    |      |                  |

| Differential Input Impedance    |                    | PGA[4:0] = 00000, CLK[2:0] = 011                                                                                     |     | 3.4   |      | МΩ               |

| (INP1 to INM1 and               | R <sub>DIN</sub>   | PGA[4:0] = 01010, CLK[2:0] = 011                                                                                     | 440 |       |      | l <sub>C</sub> O |

| INP2 to INM2)                   |                    | PGA[4:0] = 11111, CLK[2:0] = 011                                                                                     | 288 |       | kΩ   |                  |

|                                 |                    | PGA[4:0] = 00000, CLK[2:0] = 110                                                                                     |     | 27    |      |                  |

|                                 |                    | PGA[4:0] = 01010, CLK[2:0] = 110                                                                                     | 3.5 |       | ΜΩ   |                  |

|                                 |                    | PGA[4:0] = 11111, CLK[2:0] = 110                                                                                     |     | 2.3   |      |                  |

$(V_{DDF} = V_{DD} = 4.5 \text{V to } 5.5 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } f_{CLK} = 4.0 \text{MHz, } T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DDF} = V_{DD} = 5.0 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } T_{A} = +25 ^{\circ}\text{C, unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER                                            | SYMBOL              | CONE                                      | DITIONS                                                 | MIN                       | TYP       | MAX  | UNITS              |  |

|------------------------------------------------------|---------------------|-------------------------------------------|---------------------------------------------------------|---------------------------|-----------|------|--------------------|--|

|                                                      |                     | PGA[4:0] = 00000, CLK[2:0] = 000          |                                                         |                           | 430       |      |                    |  |

|                                                      |                     | PGA[4:0] = 01010, CLK[2:0] = 000          |                                                         |                           | 55        |      | kΩ                 |  |

|                                                      |                     | PGA[4:0] = 11111, CLK[2:0] = 000          |                                                         |                           | 36        |      | 1                  |  |

| Single-Sided Input Impedance                         |                     | PGA[4:0] = 00000, CL                      | _K[2:0] = 011                                           |                           | 3.4       |      | МΩ                 |  |

| (INP1 to V <sub>SS</sub> , INM1 to V <sub>SS</sub> , | R <sub>SIN</sub>    | PGA[4:0] = 01010, CL                      | _K[2:0] = 011                                           |                           | 440       |      | 1.0                |  |

| INP2 to $V_{SS}$ , INM2 to $V_{SS}$ )                |                     | PGA[4:0] = 11111, CL                      | K[2:0] = 011                                            |                           | 288       |      | - kΩ               |  |

|                                                      |                     | PGA[4:0] = 00000, CL                      | _K[2:0] = 110                                           |                           | 27        |      |                    |  |

|                                                      |                     | PGA[4:0] = 01010, CL                      | _K[2:0] = 110                                           |                           | 3.5       |      | ΜΩ                 |  |

|                                                      |                     | PGA[4:0] = 11111, CL                      | K[2:0] = 110                                            |                           | 2.3       |      |                    |  |

| Common-Mode Rejection Ratio                          | CMRR                | Common-mode voltag                        | ge V <sub>CM</sub> = V <sub>SS</sub> to V <sub>DD</sub> |                           | 0.008     |      | %FS                |  |

| Differential Signal-Gain Range                       |                     | Selectable in 17 steps                    | (Note 5)                                                | C                         | .99 to 24 | 4    | V/V                |  |

|                                                      |                     | PGA[4:0] = 00000                          |                                                         | 0.95                      | 0.99      | 1.05 |                    |  |

|                                                      |                     | PGA[4:0] = 00001                          |                                                         | 7.3                       | 7.7       | 8.2  | ]                  |  |

| Differential Signal Gain                             | A <sub>VDIFF</sub>  | PGA[4:0] = 01010                          |                                                         | 71                        | 77        | 82   | V/V                |  |

|                                                      |                     | PGA[4:0] = 10100                          |                                                         | 137                       | 153       | 168  |                    |  |

|                                                      |                     | PGA[4:0] = 11110                          |                                                         | 203                       | 244       | 283  |                    |  |

| Gain-Error Temperature<br>Coefficient                | GETC <sub>ADC</sub> | PGA[4:0] = 00000                          |                                                         |                           | -8        |      | ppm/°C             |  |

| COARSE-OFFSET DAC                                    |                     |                                           |                                                         |                           |           |      |                    |  |

| Resolution                                           |                     | 3-bit plus sign                           |                                                         |                           | 4         |      | Bits               |  |

|                                                      |                     |                                           |                                                         | PGA[4:0] = 00000 to 01000 | 137       | 147  | 157                |  |

|                                                      |                     | REF = V <sub>DD</sub> ,<br>CO[3:0] = 0111 | PGA[4:0] = 01010 to 10000                               | 273                       | 291       | 308  |                    |  |

|                                                      |                     |                                           | PGA[4:0] =<br>10100 to 11110                            | 525                       | 578       | 630  |                    |  |

|                                                      |                     |                                           | PGA[4:0] = 00000 to 01000                               | 57                        | 64        | 69   |                    |  |

| Effective Offset Adjustment at the ADC Input         | OA <sub>ADC</sub>   | REF = V <sub>DD</sub> ,<br>CO[3:0] = 0011 | PGA[4:0] = 01010 to 10000                               | 113                       | 126       | 136  | % of<br>ADC<br>Ref |  |

|                                                      |                     |                                           | PGA[4:0] =<br>10100 to 11110                            | 228                       | 251       | 276  |                    |  |

|                                                      |                     |                                           | PGA[4:0] = 00000 to 01000                               | -3                        | -1        | +1   |                    |  |

|                                                      |                     | REF = V <sub>DD</sub> ,<br>CO[3:0] = 0000 | PGA[4:0] = 01010 to 10000                               | -7                        | -2.4      | +2   |                    |  |

|                                                      |                     |                                           | PGA[4:0] =<br>10100 to 11110                            | -11                       | -4        | +3   |                    |  |

$(V_{DDF} = V_{DD} = 4.5 \text{V to } 5.5 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } f_{CLK} = 4.0 \text{MHz, } T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DDF} = V_{DD} = 5.0 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } T_{A} = +25 ^{\circ}\text{C, unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER                                    | SYMBOL              | CONDI                                                           | TIONS                        | MIN                    | TYP  | MAX                       | UNITS              |

|----------------------------------------------|---------------------|-----------------------------------------------------------------|------------------------------|------------------------|------|---------------------------|--------------------|

|                                              |                     |                                                                 | PGA[4:0] = 00000 to 01000    | -15                    | -10  | -4                        |                    |

|                                              |                     | REF = V <sub>DD</sub> ,<br>CO[3:0] = 1000                       | PGA[4:0] = 01010 to 10000    | -29                    | -19  | -10                       |                    |

|                                              |                     |                                                                 | PGA[4:0] =<br>10100 to 11110 | -56                    | -38  | -20                       |                    |

|                                              |                     |                                                                 | PGA[4:0] = 00000 to 01000    | -79                    | -73  | -66                       | ٠, ,               |

| Effective Offset Adjustment at the ADC Input | OA <sub>ADC</sub>   | REF = V <sub>DD</sub> ,<br>CO[3:0] = 1011                       | PGA[4:0] = 01010 to 10000    | -155                   | -145 | -135                      | % of<br>ADC<br>Ref |

|                                              |                     |                                                                 | PGA[4:0] =<br>10100 to 11110 | -317                   | -287 | -257                      | T I I I            |

|                                              |                     |                                                                 | PGA[4:0] = 00000 to 01000    | -162                   | -156 | -150                      |                    |

|                                              |                     | REF = V <sub>DD</sub> ,<br>CO[3:0] = 1111                       | PGA[4:0] = 01010 to 10000    | -327                   | -309 | -293                      |                    |

|                                              |                     |                                                                 | PGA[4:0] =<br>10100 to 11110 | -675                   | -614 | -555                      |                    |

| SMALL OP AMP                                 |                     |                                                                 |                              |                        |      |                           |                    |

| Input Offset Voltage                         | V <sub>OS_SM</sub>  |                                                                 |                              |                        | 0    | ±15                       | mV                 |

| Input Bias Current                           | $I_{B\_SM}$         |                                                                 |                              |                        | ±1   |                           | nA                 |

| DC Gain                                      | A <sub>VOL_SM</sub> | OUTnSM = 0.5V to 4.5V (n = 1 or 2),<br>R <sub>LOAD</sub> = ∞    |                              |                        | 100  |                           | dB                 |

| Gain Bandwidth Product                       | GBW_SM              | A <sub>VOL_SM</sub> = +1V/V                                     |                              |                        | 2.7  |                           | MHz                |

| Slew Rate                                    | SR_SM               | A <sub>VOL_SM</sub> = +1V/V                                     |                              |                        | 2.2  |                           | V/µs               |

| Common-Mode Input Range                      | CMR_SM              | _                                                               |                              | V <sub>SS</sub> + 0.02 |      | V <sub>DD</sub> -<br>0.02 | V                  |

| Common-Mode Rejection Ratio                  | CMRR_SM             | V <sub>CM_OPAMP</sub> = V <sub>SS</sub> to                      | $V_{DD}$                     |                        | 70   |                           | dB                 |

| Power-Supply Rejection Ratio                 | PSRR_SM             | At DC                                                           |                              |                        | 70   |                           | dB                 |

| Input-Referred Noise Voltage                 | V., -,,             | 0.1Hz to 1kHz                                                   |                              |                        | 8.5  |                           | μV <sub>RMS</sub>  |

| input-ivereneu ivoise voitage                | V <sub>N—SM</sub>   | 0.1Hz to 1MHz                                                   |                              |                        | 100  | -                         | PYRMS              |

| Output High Voltage                          | Vouceu              | R <sub>LOAD</sub> = ∞                                           |                              | V <sub>DD</sub> - 0.   | 1    |                           | V                  |

| Output riigir voitage                        | V <sub>OH</sub> _SM | $R_{LOAD} = 4.7 k\Omega$ to $V_{SS}$                            |                              | V <sub>DD</sub> - 0.   | 15   |                           | V                  |

| Output Low Voltage                           | Vol. ou             | R <sub>LOAD</sub> = ∞                                           |                              |                        |      | 0.1                       | V                  |

| Output Low Voltage Vol_SM                    |                     | $R_{LOAD} = 4.7 k\Omega$ to $V_{DD}$                            |                              |                        |      | 0.15                      | , v                |

| Output Source Current                        | I <sub>SRC_SM</sub> | $V_{OUTnSM} = V_{OH\_SM}$ , $R_{LOAD} = 4.7k\Omega$ to $V_{SS}$ |                              |                        |      | -1.04                     | mA                 |

| Output Sink Current                          | I <sub>SNK_SM</sub> | $V_{OUTnSM} = V_{OL\_SM}$ , $R_{LOAD} = 4.7k\Omega$ to $V_{DD}$ |                              |                        |      | 1.04                      | mA                 |

| Maximum Output Load Capacitance              | $C_{L\_SM}$         | R <sub>LOAD</sub> = ∞, phase mar                                | rgin > 55°                   |                        | 120  |                           | pF                 |

$(V_{DDF} = V_{DD} = 4.5 \text{V to } 5.5 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } f_{CLK} = 4.0 \text{MHz, } T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DDF} = V_{DD} = 5.0 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } T_{A} = +25 ^{\circ}\text{C, unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER                          | SYMBOL              | OL CONDITIONS                                                 |                              | YP MAX                       | UNITS             |  |

|------------------------------------|---------------------|---------------------------------------------------------------|------------------------------|------------------------------|-------------------|--|

| LARGE OP AMP                       |                     |                                                               |                              |                              |                   |  |

| Input Offset Voltage               | V <sub>OS_LG</sub>  |                                                               |                              | 0 ±6                         | mV                |  |

| Input Bias Current                 | I <sub>B_LG</sub>   |                                                               | ±2                           | 225                          | nA                |  |

| DC Gain                            | A <sub>VOL_LG</sub> | OUTnLG = 0.5V to 4.5V (n = 1 or 2),<br>R <sub>LOAD</sub> = ∞  | 1                            | 00                           | dB                |  |

| Gain Bandwidth Product             | GBW_LG              | A <sub>VOL_LG</sub> = +1V/V                                   | 4                            | .0                           | MHz               |  |

| Slew Rate                          | SR_LG               | A <sub>VOL_LG</sub> = +1V/V                                   | 3                            | .2                           | V/µs              |  |

| Common-Mode Input Range            | CMR_LG              |                                                               | V <sub>SS</sub> + 0.02       | V <sub>DD</sub> -<br>0.02    | V                 |  |

| Common-Mode Rejection Ratio        | CMRR_LG             | $V_{CM OPAMP} = V_{SS}$ to $V_{DD}$                           | 7                            | 70                           | dB                |  |

| Power-Supply Rejection Ratio       | PSRR_LG             | At DC                                                         | 7                            | 70                           | dB                |  |

| Input-Referred Noise Voltage       | V                   | 0.1Hz to 1kHz                                                 | 1                            | 19                           |                   |  |

|                                    | V <sub>N_LG</sub>   | 0.1Hz to 1MHz                                                 | 1                            | 60                           | μV <sub>RMS</sub> |  |

| Output-Voltage High                | Vouss               | R <sub>LOAD</sub> = ∞                                         | V <sub>DD</sub> - 0.1        | V <sub>DD</sub> - 0.1        |                   |  |

| Output-voltage Flight              | V <sub>OH_LG</sub>  | $R_{LOAD}$ = 1k $\Omega$ to $V_{SS}$                          | V <sub>DD</sub> - 0.125      | - 0.125                      |                   |  |

| Output-Voltage Low                 | \ \/a               | R <sub>LOAD</sub> = ∞                                         |                              | 0.03                         |                   |  |

| Output-voitage Low                 | V <sub>OL_LG</sub>  | $R_{LOAD}$ = 1k $\Omega$ to $V_{DD}$                          |                              | 0.13                         | V                 |  |

| Output Source Current              | I <sub>SRC_LG</sub> | $V_{OUTnLG} = V_{OH\_LG}$ , $R_{LOAD} = 1k\Omega$ to $V_{SS}$ |                              | -4.9                         | mA                |  |

| Output Sink Current                | I <sub>SNK_LG</sub> | $V_{OUTnLG} = V_{OL\_LG}$ , $R_{LOAD} = 1k\Omega$ to $V_{DD}$ |                              | 4.9                          | mA                |  |

| Maximum Output Load<br>Capacitance | C <sub>L_LG</sub>   | R <sub>LOAD</sub> = ∞, phase margin > 55°                     | 2                            | 00                           | pF                |  |

| OP-AMP SWITCH                      |                     |                                                               |                              |                              |                   |  |

| Analog Signal Range                | V <sub>SW</sub>     |                                                               | V <sub>SS</sub>              | $V_{DD}$                     | V                 |  |

| On-Resistance                      | R <sub>ON</sub>     |                                                               |                              | 5                            | kΩ                |  |

| Off-Isolation                      | V <sub>ISO</sub>    |                                                               | 8                            | 30                           | dB                |  |

| DIGITAL-TO-ANALOG CONVERT          | TER                 |                                                               |                              |                              |                   |  |

| Resolution                         | RES <sub>DAC</sub>  |                                                               | 1                            | 16                           | Bits              |  |

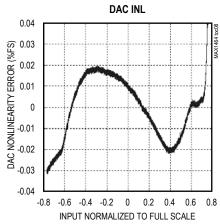

| Integral Nonlinearity              | INL <sub>DAC</sub>  |                                                               |                              | 3                            | Bits              |  |

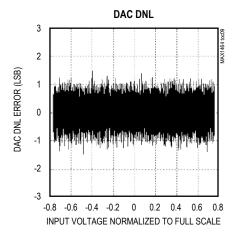

| Differential Nonlinearity          | DNL <sub>DAC</sub>  |                                                               | 1                            | ±1                           | Bits              |  |

| Offset Error                       | V <sub>DAC</sub> os | DAC ref = V <sub>DD</sub> , DAC data = 0000h                  | V <sub>DD</sub> /2<br>- 0.06 | V <sub>DD</sub> /2<br>+ 0.06 |                   |  |

| Bit Weight                         | BW <sub>DAC</sub>   | DAC ref = 5VDC                                                | 91                           | .55                          | μV/LSB            |  |

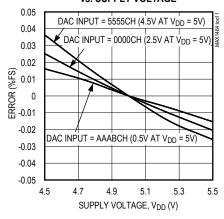

| Power-Supply Rejection             | PSR <sub>DAC</sub>  | At DC, DAC ref = V <sub>REF</sub>                             | 0.                           | 02                           | %FS               |  |

| Output Noise                       | ON <sub>DAC</sub>   | DAC buffer is the small op amp                                | £                            | :3                           | LSB               |  |

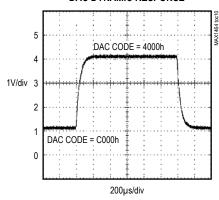

| Output Settling Time               | ST <sub>DAC</sub>   | To 0.1% of final value                                        | 2                            | 50                           | μs                |  |

| PULSE-WIDTH MODULATOR              |                     |                                                               |                              |                              |                   |  |

| Resolution                         | RES <sub>PWM</sub>  | (Note 6)                                                      | 1                            | 12                           | Bits              |  |

| Period                             | P <sub>PWM</sub>    | f <sub>CLK</sub> = 4.0MHz                                     | 8.                           | 192                          | ms                |  |

|                                    |                     |                                                               |                              |                              |                   |  |

$(V_{DDF} = V_{DD} = 4.5 \text{V to } 5.5 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } f_{CLK} = 4.0 \text{MHz, } T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DDF} = V_{DD} = 5.0 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } T_{A} = +25 ^{\circ}\text{C, unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER                                | SYMBOL                | CONDITIONS                                          | MIN  | TYP    | MAX  | UNITS  |

|------------------------------------------|-----------------------|-----------------------------------------------------|------|--------|------|--------|

| Bit Weight                               | BW <sub>PWM</sub>     |                                                     |      | 2      |      | μs/LSB |

| Offset Error                             | V <sub>PWM_OS</sub>   | PWM data = 0000h                                    |      | ±1     |      | μs     |

| Gain Error                               | GE <sub>PWM</sub>     | (Note 7)                                            |      | ±0.025 |      | %      |

| Output Jitter                            | OJ <sub>PWM</sub>     |                                                     |      | 1/4    |      | LSB    |

| <b>EXTERNAL REFERENCE INPUT</b>          |                       |                                                     |      |        |      |        |

| Reference Input Voltage Range            | V <sub>REF</sub>      |                                                     | 2.25 | 2.5    | 2.75 | V      |

| Reference Input Resistance               | R <sub>REF</sub>      | V <sub>REF</sub> = 2.5V, ADC = ON, DACs = ON        | 100  |        |      | kΩ     |

| INTERNAL VOLTAGE REFEREN                 | CE                    |                                                     |      |        |      |        |

| Internal Voltage Reference               | V <sub>IR</sub>       | (Note 8)                                            | 4.5  | 4.92   | 5.35 | V      |

| Temperature Coefficient                  | TC <sub>IR</sub>      |                                                     |      | ±110   |      | ppm/°C |

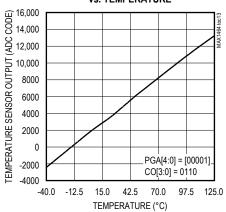

| TEMPERATURE SENSOR                       |                       |                                                     |      |        |      |        |

| Compiting                                | Como                  | PGA[4:0] = 00001, CO[3:0] = 0110                    |      | +2     |      | mV/°C  |

| Sensitivity                              | Sens <sub>TS</sub>    | PGA[4.0] = 00001, CO[3.0] = 0110                    |      | +95    |      | LSB/°C |

| Nonlinearity Error                       | INL <sub>TS</sub>     |                                                     |      | ±0.5   |      | %FS    |

| Hysteresis                               | Hist <sub>TS</sub>    |                                                     |      | ±0.1   |      | %FS    |

| ANALOG-TO-DIGITAL CONVERT                | ER                    |                                                     |      |        |      |        |

| Resolution                               | RES <sub>ADC</sub>    |                                                     |      | 16     |      | Bits   |

| Integral Nonlinearity                    | INL <sub>ADC</sub>    |                                                     |      | 2      |      | Bits   |

| Differential Nonlinearity                | DNL <sub>ADC</sub>    |                                                     |      | ±1     |      | LSB    |

| ADC Offset Error                         | V <sub>ADC_OS</sub>   | PGA[4:0] = 00000 (0.99),<br>CO[3:0] = 0000 (Note 9) | 4    |        |      | %FS    |

| Channel-to-Channel Offset Error Matching | ΔV <sub>ADC</sub> _OS |                                                     | ±1   |        | LSB  |        |

| ADC Offset-Supply Rejection              | OSR <sub>ADC</sub>    | At DC, ADC ref = V <sub>REF</sub> = 5V              |      | 0.3    |      | %FS    |

| ADC Gain-Supply Rejection                | GSR <sub>ADC</sub>    | At DC, ADC ref = V <sub>REF</sub> = 5V              |      | 0.005  |      | %FS    |

| Offset Temperature Coefficient           |                       | T <sub>A</sub> = -40°C to +125°C                    |      | 0.03   |      | %FS    |

| Ratiometricity                           |                       | PGA[4:0] = 00000 to 01000                           |      | 0.02   |      | %FS    |

$(V_{DDF} = V_{DD} = 4.5V \text{ to } 5.5V, V_{SSF} = V_{SS} = 0V, f_{CLK} = 4.0MHz, T_A = T_{MIN} \text{ to } T_{MAX}$ . Typical values are at  $V_{DDF} = V_{DD} = 5.0V, V_{SSF} = V_{DD} = 5.0V, V_{DD} = 5.0V, V_{SSF} = V_{DD} = 5.0V, V_{DD} =$ =  $V_{SS}$  = 0V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                     | SYMBOL             | CONI                                                | DITIONS                       | MIN                   | TYP | MAX                   | UNITS  |

|-------------------------------|--------------------|-----------------------------------------------------|-------------------------------|-----------------------|-----|-----------------------|--------|

| DIGITAL INPUTS (GPIO1, GPIO2, | SCLK, DI, C        | KSEL, CKIO, CS)                                     |                               |                       |     | •                     |        |

| Input High Threshold Voltage  | V <sub>IH</sub>    |                                                     |                               | 0.8 x V <sub>DD</sub> |     |                       | V      |

| Input Low Threshold Voltage   | V <sub>IL</sub>    |                                                     |                               |                       | (   | 0.2 x V <sub>DD</sub> | V      |

| Input Hysteresis              | V <sub>IHYS</sub>  |                                                     |                               |                       | 0.2 |                       | V      |

| land the class Comment        | 1                  | CKSEL, CS = V <sub>SS</sub>                         |                               |                       | 38  | -90                   | ^      |

| Input Leakage Current         | IN                 | GPIO1, GPIO2, SCL                                   | K, DI, CKIO = V <sub>DD</sub> |                       | 38  | +90                   | μA     |

| Input Capacitance             | C <sub>IN</sub>    |                                                     |                               |                       | 5   |                       | pF     |

| DIGITAL OUTPUTS (GPIO1, GPIO  | )2, DO, CKIC       | D)                                                  |                               |                       |     |                       |        |

| 0.15.13/6/65.5.155/6          | V <sub>OH</sub>    | $ R_{1} \cap AD  = \infty$                          | GPIO1, GPIO2, DO              | V <sub>DD</sub> - 0.1 |     |                       |        |

|                               |                    |                                                     | CKIO (Note 10)                |                       | 4.9 |                       | V      |

| Output-Voltage High           |                    | $R_{LOAD}$ = $2k\Omega$ to $V_{SS}$                 | GPIO1, GPIO2, DO              | V <sub>DD</sub> - 0.1 | 5   |                       | V      |

|                               |                    |                                                     | CKIO (Note 10)                |                       | 4.6 |                       |        |

|                               |                    |                                                     | GPIO1, GPIO2, DO              |                       |     | 0.05                  |        |

| Output Voltage Law            | .,                 | R <sub>LOAD</sub> = ∞                               | CKIO (Note 10)                |                       | 0.1 |                       | V      |

| Output-Voltage Low            | V <sub>OL</sub>    | $R_{LOAD} = 2k\Omega$ to                            | GPIO1, GPIO2, DO              |                       |     | 0.2                   | V      |

|                               |                    | V <sub>DD</sub>                                     | CKIO (Note 10)                |                       | 0.4 |                       |        |

| FLASH MEMORY                  |                    |                                                     | •                             |                       |     |                       |        |

| Maximum Erase Cycles          |                    | (Notes 11, 12)                                      |                               |                       | 10k |                       | Cycles |

| Minimum Erase Time            | terase             | (Notes 11, 12)                                      |                               | 4.2                   |     |                       | ms     |

| Minimum Write Time            | t <sub>WRITE</sub> | (Notes 11, 12)                                      |                               | 80                    |     |                       | μs     |

| FLASH Programming Current     | I <sub>DDFP</sub>  | Writing to the FLASH or erasing the FLASH (Note 13) |                               |                       |     | 30                    | mA     |

- Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to V<sub>SS</sub>.

- Note 2: All modules are off, except internal reference, oscillator, and power-on reset (POR) and CKSEL bit is set to zero.

- Note 3: The CPU and ADC are not on at the same time. The ADC and CPU currents are not additive.

- Note 4: I<sub>DACn</sub> does not include output buffer currents (I<sub>OPLGn</sub> or I<sub>OPSMn</sub>).

- Note 5: For gains above 240, an additional digital gain can be provided by the CPU.

- **Note 6:** The PWM input data is the 12-bit left-justified data in the 16-bit input field.

- Note 7: PWM gain error measured as:

$$GE_{PWM} = \frac{PWM_{OUT}(F00 \times h) - PWM_{OUT}(100 \times h)}{3584} \times 100\%$$

- Note 8: The internal reference voltage has a nominal value of 5V (4 x V<sub>BG</sub>) even when V<sub>DD</sub> is greater or less than 5VDC.

- Note 9: A Input-referred offset error is the ADC offset error divided by the PGA gain.

- Note 10: When the CKIO is configured in output mode to observe the internal oscillator signal, the total current is above the specified limits.

- Note 11: f<sub>CLK</sub> must be within 5% of 4MHz.

- Note 12: Allow a minimum elapsed time of 4.2ms when executing a FLASH erase command, before sending any other command. Allow a minimum elapsed time of 80µs between FLASH write commands.

- Note 13: FLASH programming current is guaranteed by design.

# **Timing Characteristics**

$(V_{DDF} = V_{DD} = 4.5 \text{V to } 5.5 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } f_{CLK} = 4.0 \text{MHz, } T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DDF} = V_{DD} = 5.0 \text{V, } V_{SSF} = V_{SS} = 0 \text{V, } T_{A} = +25 ^{\circ}\text{C, unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER                                      | SYMBOL                 | CONDITIONS                                |     | MIN | TYP  | MAX                    | UNITS                  |

|------------------------------------------------|------------------------|-------------------------------------------|-----|-----|------|------------------------|------------------------|

| Programming Temperature                        | T <sub>PROG</sub>      |                                           |     |     |      | 125                    | °C                     |

| Internal Oscillator Clock<br>Frequency         | f <sub>ICLK</sub>      | OSC[4:0] = 00000                          |     | 3.3 | 4.15 | 5.3                    | MHz                    |

| External Clock Frequency                       | f                      | V <b>-</b> 0                              | Min |     | 0.2  |                        | MHz                    |

| External Clock Frequency                       | f <sub>ECLK</sub>      | V <sub>CKSEL</sub> = 0                    | Max |     | 5    |                        | IVITIZ                 |

| External Master Clock Input Low Time           | feclkin_lo             | t <sub>ECLK</sub> = 1 / f <sub>ECLK</sub> |     | 40  |      | 60                     | %<br>t <sub>ECLK</sub> |

| External Master Clock Input High Time          | f <sub>ECLKIN</sub> HI | t <sub>ECLK</sub> = 1 / f <sub>ECLK</sub> | 40  |     | 60   | %<br>t <sub>ECLK</sub> |                        |

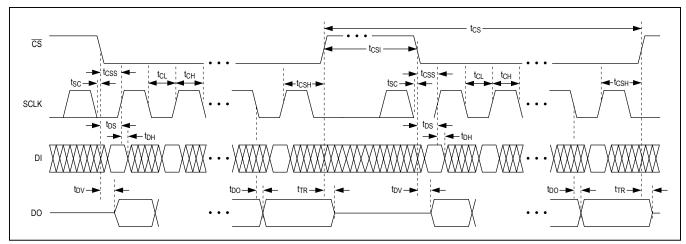

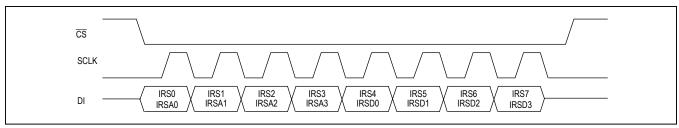

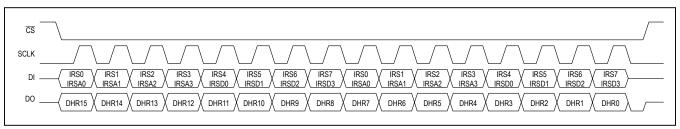

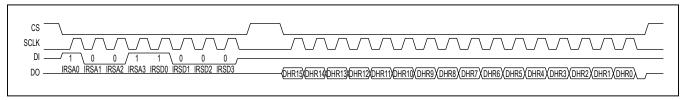

| SERIAL INTERFACE (Figure 1)                    |                        |                                           |     |     |      |                        |                        |

| SCLK Setup to Falling Edge CS                  | t <sub>SC</sub>        |                                           |     | 30  |      |                        | ns                     |

| CS Falling Edge to SCLK Rising Edge Setup Time | t <sub>CSS</sub>       |                                           |     | 30  |      |                        | ns                     |

| CS Idle Time                                   | t <sub>CSI</sub>       | f <sub>CLK</sub> = 4MHz                   |     | 1.5 |      |                        | μs                     |

| CS Period                                      | t <sub>CS</sub>        | f <sub>CLK</sub> = 4MHz                   |     | 4   |      |                        | μs                     |

| SCLK Falling Edge to Data Valid Delay          | t <sub>DO</sub>        | C <sub>LOAD</sub> = 200pF                 |     |     |      | 80                     | ns                     |

| Data Valid to SCLK Rising Edge<br>Setup Time   | t <sub>DS</sub>        |                                           |     | 30  |      |                        | ns                     |

| Data Valid to SCLK Rising Edge<br>Hold Time    | t <sub>DH</sub>        |                                           |     | 30  |      |                        | ns                     |

| SCLK High Pulse Width                          | t <sub>CH</sub>        |                                           |     | 100 |      |                        | ns                     |

| SCLK Low Pulse Width                           | t <sub>CL</sub>        |                                           |     | 100 |      |                        | ns                     |

| CS Rising Edge to SCLK Rising Edge Hold Time   | tсsн                   |                                           |     | 30  |      |                        | ns                     |

| CS Falling Edge to Output Enable               | t <sub>DV</sub>        | C <sub>LOAD</sub> = 200pF                 |     |     |      | 25                     | ns                     |

| S Rising Edge to Output Disable                | t <sub>TR</sub>        | C <sub>LOAD</sub> = 200pF                 |     |     |      | 25                     | ns                     |

Figure 1. Serial Interface Timing Diagram

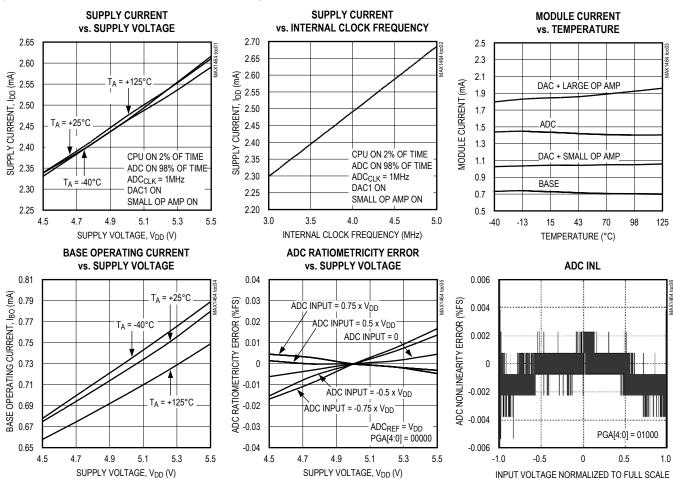

### **Typical Operating Characteristics**

$(V_{ADD} = 5.0V, T_A = +25^{\circ}C, unless otherwise noted.)$

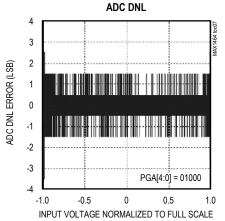

# **Typical Operating Characteristics (continued)**

(VADD = 5.0V, TA = +25°C, unless otherwise noted.)

#### DAC DYNAMIC RESPONSE

# DAC RATIOMETRICITY ERROR vs. SUPPLY VOLTAGE

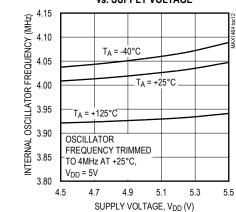

# INTERNAL OSCILLATOR FREQUENCY vs. SUPPLY VOLTAGE

# TEMPERATURE SENSOR OUTPUT vs. TEMPERATURE

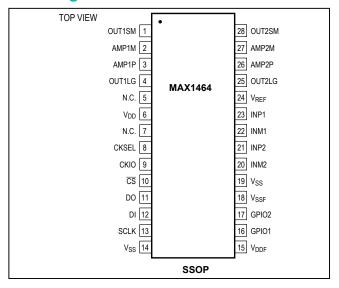

# **Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                             |

|--------|------------------|----------------------------------------------------------------------------------------------------------------------|

| 1      | OUT1SM           | Small Op Amp 1 Output                                                                                                |

| 2      | AMP1M            | Op Amp 1 Negative Input                                                                                              |

| 3      | AMP1P            | Op Amp 1 Positive Input                                                                                              |

| 4      | OUT1LG           | Large Op Amp 1 Output                                                                                                |

| 5, 7   | N.C.             | No Connection                                                                                                        |

| 6      | V <sub>DD</sub>  | Positive Supply Voltage Input. Bypass V <sub>DD</sub> to V <sub>SS</sub> with a 0.1µF ceramic capacitor.             |

| 8      | CKSEL            | Clock-Select Digital Input                                                                                           |

| 9      | CKIO             | Clock Digital Input/Output                                                                                           |

| 10     | <u>cs</u>        | SPI Chip-Select Digital Input. Active low.                                                                           |

| 11     | DO               | SPI Data Output                                                                                                      |

| 12     | DI               | SPI Data Input                                                                                                       |

| 13     | SCLK             | SPI Interface Clock                                                                                                  |

| 14, 19 | V <sub>SS</sub>  | Negative Power-Supply Input                                                                                          |

| 15     | $V_{DDF}$        | Positive Supply Voltage for FLASH Memory. Bypass V <sub>DDF</sub> to V <sub>SS</sub> with a 0.1µF ceramic capacitor. |

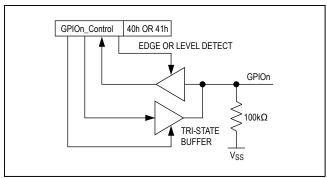

| 16     | GPIO1            | General-Purpose Digital Input/Output 1                                                                               |

| 17     | GPIO2            | General-Purpose Digital Input/Output 2                                                                               |

| 18     | V <sub>SSF</sub> | Negative Power-Supply Input for FLASH Memory                                                                         |

| 20     | INM2             | Negative Input for ADC Channel 2                                                                                     |

| 21     | INP2             | Positive Input for ADC Channel 2                                                                                     |

| 22     | INM1             | Negative Input for ADC Channel 1                                                                                     |

| 23     | INP1             | Positive Input for ADC Channel 1                                                                                     |

| 24     | V <sub>REF</sub> | External Reference Voltage Input for ADC and DACs                                                                    |

| 25     | OUT2LG           | Large Op Amp 2 Output                                                                                                |

| 26     | AMP2P            | Op Amp 2 Positive Input                                                                                              |

| 27     | AMP2M            | Op Amp 2 Negative Input                                                                                              |

| 28     | OUT2SM           | Small Op Amp 2 Output                                                                                                |

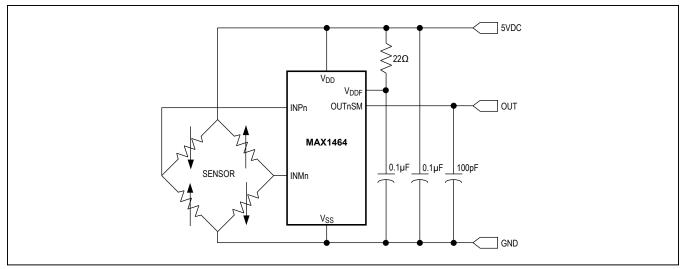

Figure 2. Basic Bridge Sensor Ratiometric Output Configuration

#### **Typical Application Circuit**

Analog ratiometric output configuration (Figure 2) provides an output that is proportional to the power-supply voltage. Ratiometricity is an important consideration for battery-operated instruments, and some industrial applications.

#### **Detailed Description**

The MAX1464 is a highly integrated, low-power, lownoise multichannel sensor signal processor optimized for industrial, and process-control applications, such as pressure sensing and compensation, RTD and thermocouple linearization, weight sensing and classification, and remote process monitoring with limit indication.

The MAX1464 incorporates a 16-bit CPU, user-programmable 4kB of FLASH memory, 128 bytes of FLASH user information, 16-bit ADC, two 16-bit DACs, two 12-bit PWM digital outputs, four rail-to-rail op amps, SPI interface, two GPIOs, and one on-chip temperature sensor.

Each sensor signal can be amplified, compensated for temperature, linearized, and the offset and full scale can be adjusted to the desired value. The MAX1464 can provide outputs as analog voltage (DAC) or digital (PWM, GPIOs), or simple on/off alarm indication (GPIOs). The uncommitted op amps can be used to implement 4–20mA current loops or for additional gain and filtering. Each DAC output is routed to either a small or large op amp. Large op amps are capable of driving heavier external loads. The unused circuit functions can be turned off to save power.

All sensor linearization and on-chip temperature compensation is done by a user-defined algorithm stored in FLASH memory. The user-defined algorithm is programmed over the serial interface and stored in 4kB of integrated FLASH memory.

The MAX1464 uses an internal 4MHz oscillator or an externally supplied 4MHz clock. CPU code execution and ADC operation is fully synchronized to minimize the noise interference of a CPU-based sensor processor system. The CPU sequentially executes instructions stored in FLASH memory.

#### **Sensor Input**

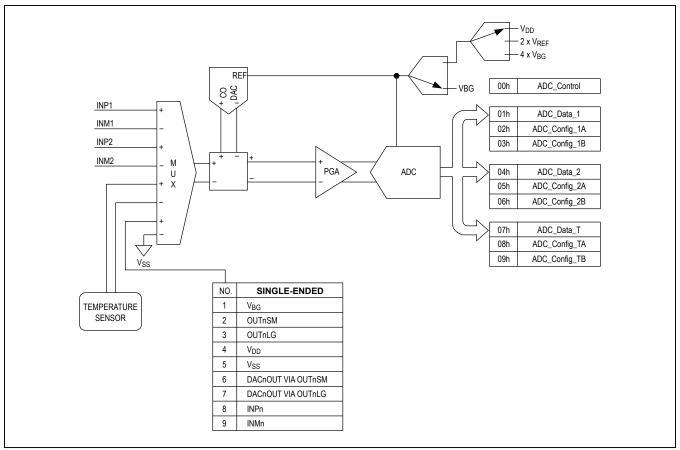

The MAX1464 provides two differential signal inputs, INP1-INM1 and INP2-INM2. These inputs can also be configured as four single-ended signals. Each input can have a common-mode range from V<sub>DD</sub> to V<sub>SS</sub> and a 0.99V/V to 244V/V programmable-gain range. The differential input signals are summed with the output of the coarse offset DAC (CO DAC) for offset correction prior to being amplified by the programmable-gain amplifier (PGA). The resulting signal is applied to the differential input of the ADC for conversion. The CPU can be programmed to measure one or two differential inputs plus the internal temperature sensor defined in user-supplied algorithm. For example, the differential inputs can be measured many times while the temperature can be measured less frequently.

#### **On-Chip Temperature Sensing**

The on-chip temperature sensor changes +2mV/°C over the operating range. The ADC converts the temperature sensor in a similar manner as the sensor inputs. During an ADC conversion of the temperature sensor, the ADC automatically uses four times the internal 1.25V reference as the ADC full-scale reference (5V). The temperature data format is 15-bit plus sign in two's-complement format. Gain offset compensation can be programmed to utilize the full-scale range of the ADC. Offset compensation by the CO DAC is provided so that the nominal temperature measurement can be centered at the ADC output value. Use the CPU to provide additional digital gain and offset correction.

#### **Output Format**

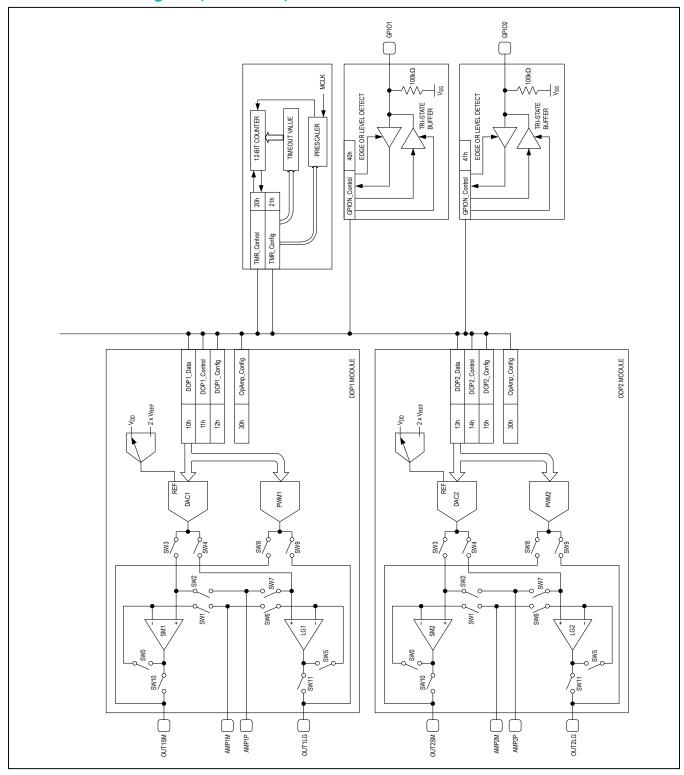

There are two output modules in the MAX1464—DOP1 (DAC Op Amp PWM 1) and DOP2 (DAC Op Amp PWM 2). Each of the DOP modules contains a 16-bit DAC, a 12-bit digital PWM converter, a small op amp, and a large op amp with high-output-drive capability. Each module can be configured in several different modes to suit a wide range of output signal requirements. Either the DAC or the PWM can be selected as the primary output signal. The DAC output signal must be routed to one of the two op amps before being made available to a device pin. See the DAC, Op Amp, PWM Modules (DPOn) section for details. Additional digital outputs are available on the GPIOs.

#### Initialization

A user-defined initialization routine is required to configure the oscillator frequency and various analog modules, e.g., PGA gain, ADC resolution, ADC clock settings, etc. After the initialization routine, the CPU can start execution of the main program.

#### Power-On Reset (POR)

The MAX1464 contains a POR circuit to disable CPU execution until adequate  $V_{DD}$  and  $V_{DDF}$  voltage are available for operation. Once the power-on state has been reached, the MAX1464 is kept under reset condition for 250 $\mu$ s before the CPU starts execution. Below the POR threshold, all internal CPU registers are set to their POR default state. Power-on control bits for internal modules are reset to the OFF condition.

#### **CPU Architecture**

The CPU provides a wide range of functionality to be incorporated in an embedded system. The CPU can compensate nonlinear and temperature-dependent sensors, check for over/underlimit conditions, output sensor or temperature data as an analog signal or pulse-widthmodulated digital signal, and execute control strategies.

The CPU can perform a limited amount of signal processing (filtering). A timer is included so that uniform sampling (equally spaced ADC conversions) of the input sensors can be performed.

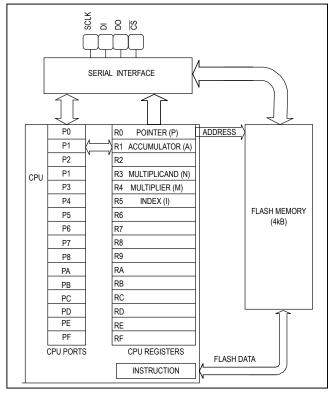

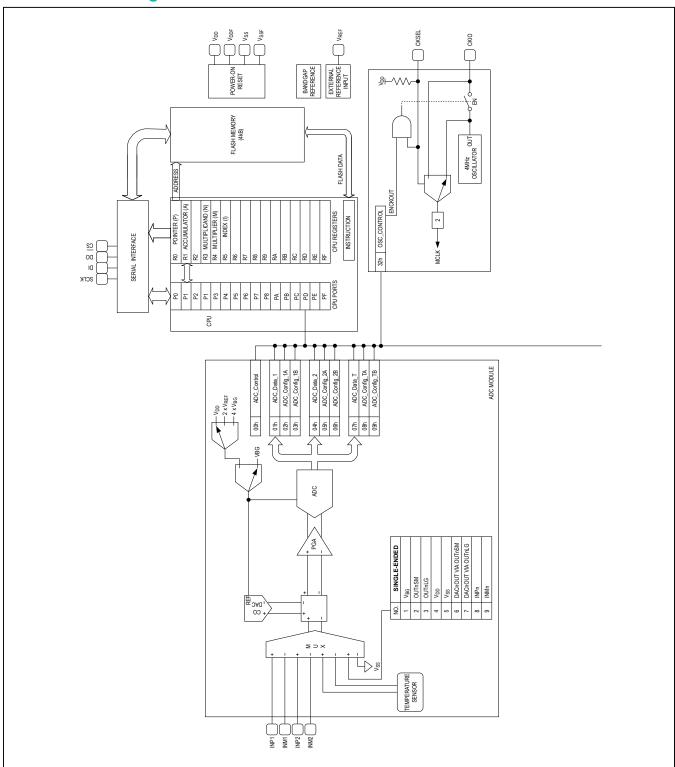

The CPU registers and ports are implemented in volatile, static memory. There are several registers contained in various peripheral modules that provide module configuration settings, control functions, and data. These module registers are accessible through an indirect addressing scheme as described in detail in the CPU Registers, CPU Ports, and Modules sections. Figure 3 shows the CPU architecture.

#### **CPU Registers**

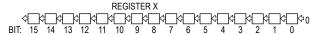

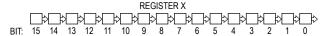

The MAX1464 incorporates a CPU with 16 internal registers. All the CPU registers have a 16-bit data word width. Five of the 16 registers have predefined functional operations that are dependent on the instruction being executed. The remaining registers are general purpose.

The CPU registers are embedded in the CPU itself and are not all directly accessible by the serial interface. The accumulator register (A), the pointer register (P), and the instruction (FLASH data) can be read through the serial interface when the CPU is halted. This enables a single-

Figure 3. CPU Architecture

step mode of code execution to ease code writing and debugging. A special program instruction sequence is required to observe the other CPU registers. Table 1 lists the CPU registers.

#### **CPU Ports**

The MAX1464 incorporates 16 CPU ports that are directly accessible by the serial interface. All the CPU ports have a 16-bit data word width. The contents of the ports can be read and written by transferring data to and from the accumulator register (A) using the RDX and WRX instructions. No other CPU instructions act on the CPU ports. Three CPU ports PD, PE, and PF have uniquely defined operation for reading and writing data to and from the peripheral modules. All CPU ports are static and volatile. Table 2 lists the CPU ports.

#### **Modules**

The MAX1464 modules are the functional blocks used to process analog and digital signals to and from the CPU. Each module is addressed through CPU ports PD, PE, and PF, as described in the *CPU Ports* section. All modules use static, volatile registers for data retention. There are three types of module registers: configuration, data, and control. They are used to put a module into a particular mode of operation. Configuration registers hold configuration bits that control static settings such as PGA gain, coarse offset, etc. Data registers hold input data such as DAC and PWM input words or output data such as the result of an ADC conversion. Control registers are used to initiate a process (such as an ADC conversion or a timer) or to turn modules on and off (such as op amps, DAC outputs, PWM outputs, etc.) Table 3 lists the module registers.

#### ADC Module

The ADC module (Figure 4) contains a 9-bit to 16-bit sigma-delta converter with multiplexed differential and single-ended signal inputs, a CO DAC, four reference voltage inputs, two differential or four single-ended external inputs, and 15 single-ended internal voltages for measurement. The ADC output data is 16-bit two's complement format. The conversion channel, modes, and reference sources are all set in ADC configuration registers. The conversion time is a function of the selected resolution and ADC clock frequency. The CPU can be programmed to convert any of the inputs and the internal temperature sensor in any desired sequence. For example, the differential inputs may be converted many times and conversions of temperature performed less frequently. See Table 4.

The ADC reference can be selected as  $V_{DD}$  for conversions ratiometric to the power supply, 2 x  $V_{REF}$  input for conversions relative to an external voltage, and  $V_{RG}$  x 4,

which is an internally generated bandgap reference voltage. Note that because  $V_{REF}$  external = 2.5V and  $V_{BG}$  = 1.25V, the ADC's reference voltage is always close to 5.0V. The ADC voltage reference is also used by the CO DAC to maintain a signal conversion that is completely ratiometric to the selected reference source.

The four analog inputs (INP1, INM1, INP2, INM2) and several internal circuit nodes can be multiplexed to the ADC for a single-ended conversion relative to  $V_{SS}$ . The selection of which circuit node is multiplexed to the ADC is controlled by the ADC\_Control register. The ADC can measure each of the op-amp output nodes with gain for converting user-defined circuits or incorporating system diagnostic test functions. The DAC outputs can be converted by the ADC with either op amp arranged as unity-gain buffers on the DAC outputs. The internal power nodes,  $V_{DD}$  and  $V_{SS}$ , and the bandgap reference,  $V_{BG}$  can be multiplexed to the ADC for conversion as well. These measurement modes are defined and initiated in the ADC\_Control register. See Tables 5 and 7 for the single-ended configuration.

#### **ADC Registers**

The ADC module has 10 registers for configuration, control, and data output. There are three conversion channels in the ADC; channel 1, channel 2, and temperature. Channels 1 and 2 are associated with the differential signal input pairs INP1-INM1 and INP2-INM2, respectively. The temperature channel is associated with the integrated temperature sensor. Each channel has two configuration registers  $(ADC\_Config\_nA \ and \ ADC\_Config\_nB \ where \ n = 1, 2, or$ T) for setting conversion resolution, reference input, coarse offsets, etc. The data output from a conversion of channel 1, 2, or T is stored in the respective data output register ADC Data n where n = 1, 2, or T. Each of the channels can be used to convert single-ended inputs as listed in Table 7. The ADC Control register controls which channel is to be converted and what single-ended input, if any, is to be directed to that channel. See Tables 8 through 13.

#### **Conversion Start**

To initiate an ADC conversion, a word is written to the ADC\_Control register with either CNVT1, CNVT2, or CNVTT bit set to a 1 (Table 6). When an ADC conversion is initiated, the CPU is halted and all CPU and FLASH activities cease. All CNVT1, CNVT2, and CNVTT bits are cleared after the ADC conversion is completed.

Upon completion of the conversion, the ADC result is latched into the respective ADC\_Data\_n register. In addition, the convert bits in control register 0 are all reset to zero. The CPU clock is then enabled and program execution continues

Figure 4. ADC Module

Single-ended inputs can be converted by either channel 1 or 2 by initiating a conversion on the appropriate channel with the SE[3:0] bits set to the desired single-ended input (Table 7). Several of the single-ended signals are converted with a fixed gain. The reduced gain of 0.7V/V allows signals at or near the supply rails to be converted without concern of saturation. Other single-ended signals can be converted with the full selectable PGA gain range.

#### Programmable-Gain Amplifier

The gain of the differential inputs and several single-ended inputs can be set to values between 0.99V/V to 244V/V as shown in Table 14. The PGA bits are set in ADC\_Config\_nA where n = 1, 2, or T. The gain setting must be selected prior to initiating a conversion.

#### **ADC Conversion Time and Resolution**

The ADC conversion time is a function of the selected resolution, ADC clock ( $f_{ADC}$ ), and system clock frequency ( $f_{CLK}$ ). The resolution can be selected from 9 bits to 16 bits in the ADC\_Config\_nA (where n = 1, 2, or T) register

by bits RESn[2:0]. The lower resolution settings (9 bit) convert faster than the higher resolution settings (16 bit). The ADC clock  $f_{ADC}$  is derived from the primary system clock  $f_{CLK}$  by a prescalar divisor. The divisor can be set from 4 to 512, producing a range of  $f_{ADC}$  from 1MHz down to 7.8125kHz when  $f_{CLK}$  is operating at 4.0MHz. Other values of  $f_{CLK}$  produce other scaled values of  $f_{ADC}$ . See Tables 15 and 16.

Systems operating with very low power consumption benefit from the reduced  $f_{ADC}$  clock rate. Slower clock speeds require less operating current. Systems operating from a larger power consumption budget can use the highest  $f_{ADC}$  clock rate to improve speed performance over power performance.

The ADC conversion times for various resolution and clock-rate settings are summarized in Table 17. The conversion time is calculated by the formula:

t<sub>CONVERT</sub> = (no. of f<sub>ADC</sub> clocks per conversion) /f<sub>ADC</sub>

#### **Coarse-Input Offset Adjustment**

Differential input signals that have an offset can be partially nulled by the input coarse-offset (CO) DAC. An offset voltage is added to the input signal prior to gaining the signal. This allows a maximum gain to be applied to the differential input signal without saturating the conversion channel. The CO signal added to the differential signal is a percentage of the full-scale ADC reference voltage as referred to the ADC inputs. Low PGA gain settings add smaller amounts of coarse offset to the differential input. Large PGA gain settings enable correspondingly larger amounts of coarse offset to be added to the input signal. The CO DAC also applies to the temperature channel enabling offset compensation of the temperature signal. See Table 18.

#### **Bias Current Settings**

The analog circuitry within the ADC module operates from a current bias setting that is programmable. The programmable levels of operation are fractions of the full bias current. The operating power consumption of the ADC can be reduced at the penalty of increased conversion times that may be desirable in very-lowpower applications. It is recommended operating the ADC at full bias when possible. The amount of bias as a fraction of full bias is shown in Table 19. The setting is controlled by the BIASn[2:0] bits in the ADC config nb registers where n = 1, 2, or T.

#### Reference Input Voltage Select

The ADC can use one of three different reference voltage inputs depending on the conversion channel and REFn setting as shown in Table 20. The differential inputs can be converted ratiometrically to the supply voltage ( $V_{DD}$ ), converted ratiometrically to an externally supplied voltage at  $V_{REF}$ , or converted nonratiometrically using a fixed voltage source derived from the internal bandgap voltage source. The temperature channel is always converted using the internal bandgapderived voltage source and therefore is not selectable.

#### **Output Sample Rate**

Generally, the sensor and temperature data are converted and calculated by an algorithm in the execution loop. The output sample rate of the data depends on the conversion time, the CPU algorithm loop time, and the time to store the result in the DOPn\_DATA register. To achieve uniform sampling, the instruction code must be written to provide a consistent algorithm loop time, including branch instruction variations. This total loop time interval should be repeatable for a uniform output rate.

The MAX1464 has a built-in timer that can be used to ensure that the sampling interval is uniform. The timeout value can be set so the CPU computations and the read-

ing of the serial interface, if required, can be completed before timeout. The GPIO pins can be utilized to interrupt an external master microcontroller when the ADC conversion is done and/or when the CPU computations are done so the serial interface can be read quickly.

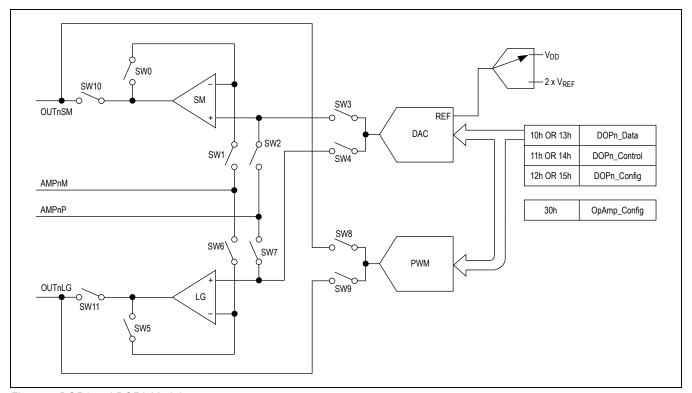

#### DAC, Op Amp, PWM Modules (DOPn)

There are two output modules in the MAX1464—DOP1 and DOP2 (Figure 5). Each of the DOP modules contains a 16-bit DAC, a 12-bit digital PWM converter, a small op amp, and a large op amp with high-outputdrive capability. Switches in the DOP module enable a range of interconnectivity among the converters, op amps, and the external pins. Either the DAC or the PWM can be selected as the primary output signal. The DAC output signal is routed to one of the op amps and made available to a device pin. The signal-switching arrangement also allows the unused op amp to be configured as an uncommitted device with all connections available to external pins.

The DAC and op amps have a power-control bit in the power module. When power is disabled, all circuits in the DAC and the op amp are disabled with inputs and outputs in a tri-state condition. The proper bits in the power module must be enabled for operation of the DAC and op amps.

The DAC input is a 16-bit two's-complement value. An input value of 0000h produces an output voltage of one half the DAC reference voltage. The DAC output voltage increases for positive two's-complement numbers, and decreases for negative two's-complement numbers.

The PWM input is a 12-bit two's complement value. It shares the same input register (DOPn\_Data) as the DAC, using the 12 MSBs of the 16-bit register. An input value of 000Xh produces a 50% duty cycle waveform at the output. The PWM output duty cycle increases for positive two's-complement numbers, and decreases for negative two's-complement numbers.

#### **DOP\_n Configuration Options**

Each of the DOP modules can be configured in several different modes to suit a wide range of output signal requirements. The Functional Diagram shows the various switch settings of the configuration and control registers. In situations where configuration settings create a conflict in switch activation, a priority is applied to the switch logic to prevent the conflict.

The DAC and/or the PWM can be selected as the output signal source. The DAC output signal is routed to one of the op amps and made available to a device pin. Selecting the large op amp as the DAC output driver device enables a robust current drive capability for driving signals into low-impedance loads or across long lengths of wire. The

Figure 5. DOP1 and DOP2 Modules

unity-gain buffer configuration is automatically selected, and it provides the DAC output signal directly to the device pin OUTnLG. With the large op amp selected, the small op amp can be used as an independent device for external circuit applications when the PWM is disabled. Alternatively, the PWM can also be enabled to drive the OUTnSM device pin, in which case the small op amp is OFF.

Selecting the small op amp as the DAC output driver device is useful for routing the output signal to other circuits in an embedded control system with high-impedance load connections. The unity-gain buffer configuration is automatically selected, and it provides the DAC output signal directly to the device pin OUTnSM. With the small op amp selected, the large op amp can be used as an independent device for external circuit applications when the PWM is disabled. Alternatively, the PWM can also be enabled to drive the OUTnLG device pin, in which case the large op amp is OFF.

The DAC has two reference voltage sources available by selection,  $V_{DD}$  and  $V_{REF}$  input. When the external reference is selected ( $V_{REF}$ ), the actual DAC reference is 2 x  $V_{REF}$ . See  $V_{REF}$  to 2.5V for nominal operation. The output of the DAC is a voltage proportional to the reference voltage selected, where the proportionality scaling (DAC input) is set in the data input register DOPn\_Data.

The DOP module also provides a 12-bit digital PWM output. At a nominal 4MHz frequency, the frequency of the PWM is 122Hz (PWM period = 8.192ms). The DAC and the PWM share the same input register, DOPn\_Data, where the PWM uses the 12 MSBs, in two's-complement format. An input of 000Xh (4 LSBs are ignored) outputs a 50% duty cycle waveform at the selected output pin (either OUTnSM or OUTnLG). The PWM bit weight is 2 $\mu$ s, at a nominal frequency of 4MHz. The minimum duty cycle is obtained when the input is 800Xh (duty cycle is 0 / 4096 = 0), and the maximum duty cycle at 7FFXh (duty cycle is 4095 / 4096 = 99.98%). A new PWM input word is only effective at the end of a current PWM cycle, therefore preventing PWM glitches on the output.

Either the small or the large op amp in the DOP module can also be selected as an uncommitted op amp in the MAX1464. The op amps can be configured as a unitygain buffer, where the output is internally connected to the negative terminal of the op amp, or a stand-alone op amp, where both AMPnM and AMPnP can be externally connected for various analog functions. In the case of a buffer, the device pin AMPnM is in high-impedance mode, as the feedback loop around the op amp is connected internally.

Every function of the DOP module can be selected individually (DAC, PWM, or op amp), or two out of the three functions of the DOP module can be selected at the same time (PWM and op amp, or DAC and PWM, or DAC and op amp), as there are only two output pins for the module, OUTnSM and OUTnLG. The various configuration options for the DOP are shown in Table 21. The PWRDAC and PWROP bits are in the power-on control register (address = 31h), and the remaining bits are in the DOP registers. See Tables 21 through 27.

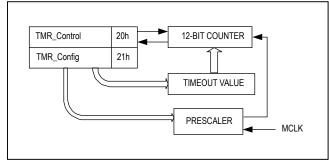

#### **Timer Module**

The timer module (Figure 6) comprises a 12-bit counter, a 4-bit prescalar, and control and configuration registers. When the timer is enabled and initiated, the system master clock, MCLK, is prescaled by the divisor set by PS[3:0] in the TMR\_Config register and the result applied to the 12- bit upcounter. When the counter value matches the timeout value TO[11:0] in register TMR\_Config, bit TMDN is set to 1. The CPU can poll the timer done bit TMDN to check its status.

The timer module provides a feature that enables the CPU to be put into a low-power halt mode for the duration of the timer interval. Setting the ENAHALT bit in the TMR\_Control register while starting the timer (setting the timer enable bit TMEN to 1), or while the timer is already enabled and counting halts the CPU at the present instruction until the TMDN bit becomes set by the counter. The CPU commences execution with the next instruction. All CPU registers and ports are fully static and retain all data during the elapsed time interval.

The time interval between TMEN being set to 1, and TMDN being set to 1 can be computed as follows:

Time Interval =  $(2 / f_{OSC}) x \{(prescale value N) x (timeout value TO[11:0]) + 1.5\}$

The maximum time interval given fOSC = 4MHz clock is 786ms.

Figure 6. Timer Module

#### **Power Control**