# acam-messelectronic gmbH is now

# Member of the ams Group

The technical content of this acam-messelectronic document is still valid.

#### **Contact information:**

#### **Headquarters:**

ams AG

Tobelbader Strasse 30 8141 Premstaetten, Austria

Tel: +43 (0) 3136 500 0

e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

## **PICO**STRAIN

Digital Amplifier for Strain Gages

PSØ21

## **Datasheet**

02<sup>ND</sup> JUNE 2006

#### acam - solutions in time

Precision Time Interval Measurement

1.1 System Overview

1.1 System Overview

#### 1. Introduction

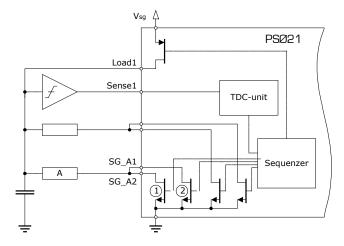

#### 1.1 System Overview

PSØ21 is the newest front-end device out of the **PICD**STRAIN® product family. **PICD**STRAIN stands for a new digital concept to measure metal strain gages (SG). It is based on TDC technology (Time-to-Digital Converter). The digital measurement principle allows a high degree of flexibility. The current consumption of the total system, including the sensor, can be reduced down to less than 100  $\mu$ A. The precision to be achieved is comparable to high-end 24-Bit A/D-converters and even surpasses them at high measurement rates. It has a serial interface, SPI® compatible, to communicate with a microcontroller or DSP.

The PSØ21 is downwardly compatible to the PSØ2. Hard-and software for PSØ2 can also be used with PSØ21.

#### **Features**

- Digital measuring principle in CMOS technology

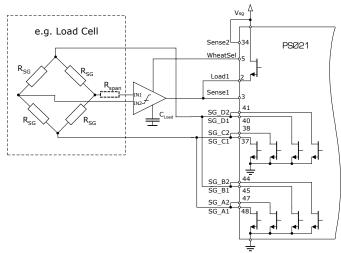

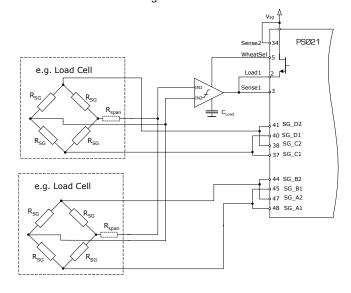

- Up to 2 full- or 4 halfbridges

- Optional mode for Wheatstone bridges

- Compensated or non-compensated bridges

- Adaptation of compensation resistor's Tk by software

- Offset and span compensation internally separated (mathematically), therefore no need to trim the bridge offset

- Capable of driving only a halfbridge without any loss in precision

- Resistance strain gauge: 350 Ohm 10 kOhm

- Programmable resolution:

Up to 19 Bit (20nV rms or 500,000 scale div)

@ 2 mV/V strain and 5 Hz update rate

- High Measurement rate:

Up to 50 kHz with high resolution

(12.4 ENOB @ 4 kHz and 2 mV/V max. strain)

- Extremely low current consumption possible: Down to 15 μA (incl. SG) at 1 Hz and 10 ENOB with 1 kOhm SG and 1000 μ strain

- High stability with temperature, low gain error (< 1 ppm/K)</li>

- No need for a pre-amplifier

- No separate supply of SG

- No separate reference voltage

- Optional Single-conversion mode

- Separate temperature measurement

- Optional capacitor measurement

- Serial interface (SPI compatible)

- Supply voltage I/O and SG: 1.8 ... 5.5 V

- Separate Supply for interface I/Os

- Supply voltage PSØ21: 1.8 ... 3.6 V

- Op. temperature range -40°C ... +120°C

- QFN48 / QFP48 package (body size 7 x 7 mm²)

#### **Applications**

- Scales and load cells

- Force sensors

- Pressure sensors (also 4 20 mA)

- SG-amplifiers in general

- Solar cell driven devices

- Battery driven devices

- Wireless applications

1.2 Index

#### 1.2 Index

| 1. | Introduction                                         | 3  |

|----|------------------------------------------------------|----|

|    | 1.1 System Overview                                  | 3  |

|    | 1.2 Index                                            | 4  |

|    | 1.3 Structure of the datasheet                       | 7  |

| 2  | Characteristics and Specifications                   | 8  |

|    | 2.1 Absolute Maximum Ratings                         | E  |

|    | 2.2 Recommended Operating Conditions                 |    |

|    | 2.3 Electrical Characteristics                       |    |

|    | 2.4 System Performance                               |    |

|    | 2.4.1 Measurement Capability                         |    |

|    | 2.4.2 Offset and Gain Error                          |    |

|    | 2.4.3 Current consumption                            |    |

|    | 2.5 Timings                                          |    |

|    | 2.6 Pin Configuration                                |    |

|    | 2.7 Package Drawings                                 |    |

|    | Recommended Foot Pattern                             |    |

|    | 2.8 Registers                                        |    |

|    | 2.8.1 Write Registers                                |    |

|    | 2.8.2 Read Registers / Ouput Data Formats            |    |

|    | 2.9 Recommended Modifications to the Default Values. |    |

|    |                                                      |    |

| 3. |                                                      | 28 |

|    | 3.1 Measuring Task                                   |    |

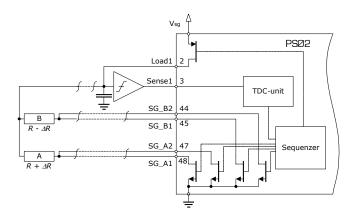

|    | 3.2 Measuring Principle                              | 28 |

|    | 3.3 High Precision                                   | 29 |

|    | 3.4 Low Current Consumption                          | 29 |

|    | 3.5 High Update Rate                                 | 30 |

| 4. | Basic Functionality                                  | 31 |

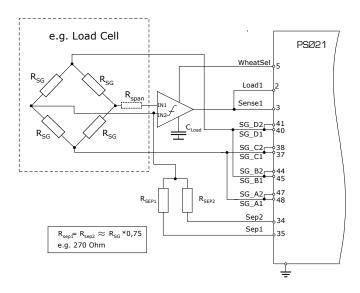

|    | 4.1 Connecting the SG                                | 3′ |

|    | 4.1.1 Halfbridge                                     | 3′ |

|    | 4. 1.2 Fullbridge                                    |    |

|    | 4.1.3 Doublebridge Mode                              |    |

|    | 4.1.4 Wheatstone Mode                                |    |

|    | 4.1.5 Long Wires (6-wires)                           |    |

|    | 4.2 The Capacitor                                    |    |

|    | 4.2.1 Capacitor Material                             |    |

|    | 4.3 The Comparator                                   |    |

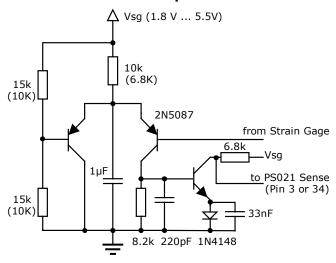

|    | 4.3.1 Standard Comparator                            |    |

|    | 4.3.2 Low Noise Comparator                           |    |

|    | 4.3.3 Switched Comparator                            |    |

|    | CompSleep                                            |    |

|    | CompCon                                              |    |

|    | CompCon<10>                                          |    |

|    | 4.3.4 Wheastone Comparator                           |    |

|    | 4.3.5 Comparator for Highest Rates.                  |    |

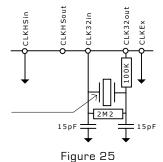

|    | 4.4 The Oscillator                                   |    |

|    | 4.4.1 High-speed Oscillator                          |    |

|    | 4.4.2 The 32kHz Oscillator                           |    |

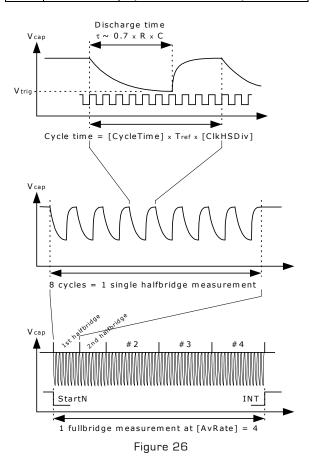

|    | 4.5 Cycle Time                                       |    |

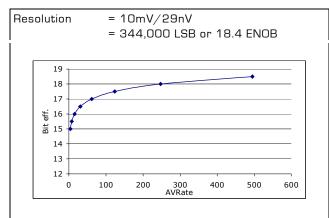

|    | 4.6 Averaging / Resolution                           | ⊿r |

#### 1.2 Index

|    | 4.6.1 Precision of a Single Measurement       | 40  |

|----|-----------------------------------------------|-----|

|    | 4.6.2 Increasing Resolution by Averaging      | 40  |

|    | 4.7 Gain Compensation                         |     |

|    | 4.7.1 Standard Compensation                   | 41  |

|    | 4.7.2 Separate Compensation                   |     |

|    | 4.8 Update Rate                               |     |

|    | 4.9 Serial Interface (SPI)                    | 43  |

|    | 4.9.1 Separate Supply Vio                     |     |

|    | 4.9.2 Write into the Chip                     |     |

|    | 4.9.3 Read from the Chip                      |     |

|    | 4.10 Controlling PSØ21                        |     |

|    | 4.10.1 Configuration                          |     |

|    | 4.10.2 Measurement Start/Control              |     |

|    | 4.10.3 Reading Data                           |     |

|    | 4.10.4 Stop Measurement                       | 45  |

| 5. | Details and Special Functions                 | 46  |

|    | 5.1 Calibration in Measurement Range 2        |     |

|    | 5.1.1 CalDel                                  |     |

|    | 5. 1. 2 CalcCycle                             |     |

|    | 5.1.3 CalcAvRate                              |     |

|    | 5.2 Rdson-Compensation                        |     |

|    | 5.2.1 RdsonAVRate                             |     |

|    | 5.2.2 RdsonModify.                            |     |

|    | 5.2.3 RD1, RD2                                |     |

|    | 5.2.4 RdsonSimple                             |     |

|    | 5.3 Temperature Measurement                   |     |

|    | 5.3.1 Precision of Temperature Measurement    |     |

|    | 5.3.2 Dimensioning                            |     |

|    | 5.4 Auto-Offset                               |     |

|    | 5.4.1 Warm-Up                                 |     |

|    | 5.5 Computing time ALU                        |     |

|    | 5.5.1 MFake                                   |     |

|    | 5.6 Current Consumption.                      | 49  |

|    | 5.6.1 Current into Strain Gage                |     |

|    | 5.6.2 Current into PSØ21                      |     |

|    | 5.6.3 Other Current Drains                    | 51  |

|    | 5.7 Port Switch                               | 51  |

|    | 5.8 Quarterbridge                             | 51  |

|    | 5.9 Anti Aliasing                             | 52  |

|    | 5.10 Tempcompensated Bridges                  | 52  |

|    | 5.10.1 General comment                        | 52  |

|    | 5.10.2 PSØ21 – New facilities                 | 53  |

|    | 5.10.3 Configuration of Span Compensation     | 54  |

|    | 5.10.4 Offset Compensation                    | 54  |

|    | 5.11 Multiplication                           | 54  |

|    | 5.12 Supply by Lithium Coin Cells             | 55  |

| e  | Special Modes                                 | 56  |

| J  | 6.1 Measurement Range 1 for High Update Rates |     |

|    | 6.1.1 Capacitor in Range1                     |     |

|    | 6.1.2 Averaging / Resolution.                 |     |

|    | 6.1.3 Current Consumption Range 1             |     |

|    | 6.3 Capacity measurement                      |     |

|    | C.O Supusity medical emone                    | 0 / |

#### 1.3 Structure of the datasheet

| 6.3.1 General Note                                                                           |    |

|----------------------------------------------------------------------------------------------|----|

| 6.3.2 Floating Capacitors  6.3.3 Grounded Capacitors  6.3.4 Compensated Capacity Measurement | 57 |

| 7. How to Get the Best out of PSØ21                                                          | 59 |

| 7.1 Default settings of adjustment registers                                                 | 59 |

| 7.2 Cycle Time / Measuring Time                                                              |    |

| 7.3 Supply Voltage                                                                           | 59 |

| 7.4 Reading Data                                                                             |    |

| 7.5 Board Layout                                                                             |    |

| 7.6 High-speed Oscillator                                                                    |    |

| 7.7 Noise1 (Reg6, Bit 16)                                                                    | 60 |

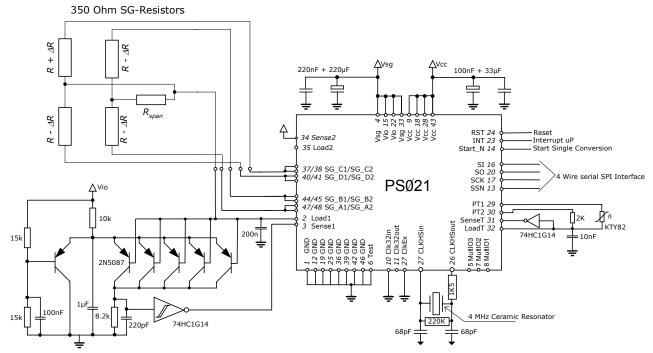

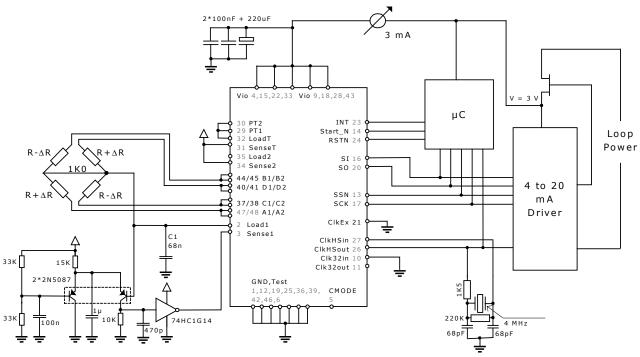

| 8. Applications                                                                              | 61 |

| 8.1 Calibrated Scale                                                                         | 61 |

| 8.2 Pressure Sensor on a 4 to 20 mA Interface                                                | 64 |

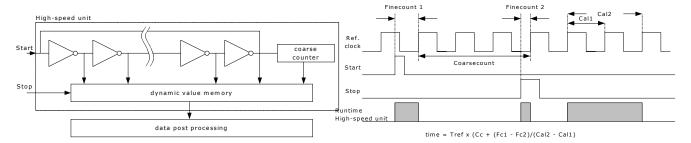

| 9. Background Knowledge                                                                      | 66 |

| 9.1 What's a TDC?                                                                            | 66 |

| 9.1.1 Measuring Range 1                                                                      | 66 |

| 9.1.2 Measurement Range 2.                                                                   | 66 |

| Contact                                                                                      | 67 |

1.3 Structure of the datasheet

#### 1.3 Structure of the datasheet

This functional description is made of several main sections for easy implementation of the PSØ21.

These main sections are:

#### 2. Technical Characteristics

This main section is for reference with all the important technical data in a brief. Pinning, operating conditions and timings are shown. Several tables give an overview about the read and write register as well as a short description of the different bits. This section provides technical reference for the engineer actually working on the design-in of this product.

#### 3. General Introduction

This main section is a general introduction into the field of measuring strain gauges. Some fundamental terms are introduced, which will be used frequently in this manual. We mainly explain the basics of the **PICO**STRAIN measuring principle and it's specialties.

#### 4. Description of Basic Functions

Here the user finds everything to successfully start a first application with PSØ21. This section is important for anyone working with PSØ21 for the first time.

#### 5. Details and Special Functions

In this section special functions and control bits are discussed. It provides information for those who want to optimize the maximum performance of the PSØ21. Things like temperature measurement and the calculation of the current consumption can be found here.

#### 6. Special Modes

This section treats mainly measurement range 1 and capacity measurement.

#### 7. How to get the best performance

This section gives hints what to do to get get the highest possible performance out of the PSØ21.

#### 8. Applications

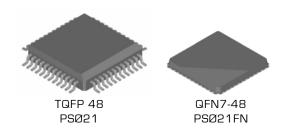

This section shows some typical application examples with schematics and configuration.

#### 9. Background

This section gives some general background information about TDCs, strain gage measurement...

2.1 Absolute Maximum Ratings

#### 2 Characteristics and Specifications

#### 2.1 Absolute Maximum Ratings

Supply voltage

Vcc vs. GND -0.3 to 4 V Vio, Vsg vs. GND -0.3 to 7 V Current into Output-Pin (lout)  $\pm 30$  mA Storage temperature (Tstg) -65 to 150 °C Junction temperature [Tj] max. 125 °C

#### 2.2 Recommended Operating Conditions

| Symbol | Parameter                    | Conditions | Min | Тур | Max | Unit |

|--------|------------------------------|------------|-----|-----|-----|------|

| Vcc    | Core supply voltage          | Vio > Vcc  | 1.8 |     | 3.6 | V    |

| Vio    | I/O supply voltage           |            | 1.8 |     | 5.5 | V    |

| Vsg    | Strain gage supply voltage   |            | 1.8 |     | 5.5 | V    |

| tri    | Normal Input Rising Time     |            |     |     | 50  | ns   |

| tfa    | Normal Input Falling Time    |            |     |     | 50  | ns   |

| tri    | Schmitt Trigger Rising Time  |            |     |     | 5   | ms   |

| tfa    | Schmitt Trigger Falling Time |            |     |     | 5   | ms   |

| Ta     | Ambient Temperature          |            | -40 |     | 120 | °C   |

#### 2.3 Electrical Characteristics

At Vcc=3.3 V  $\pm$  0.3 V, Ambient temperature -40 °C ... +85 °C unless otherwise specified

| Symbol | Parameter                             | Conditions                                                 | Min     | Тур | Max | Unit |

|--------|---------------------------------------|------------------------------------------------------------|---------|-----|-----|------|

| Iq     | Quiescent current 32 kHz              | lcc + lio, only 32kHz<br>oscillator running,<br>Vcc=Vio=3V |         | 5   |     | μΑ   |

| Iq     | Quiescent current 4 Mhz               | lcc + lio, only ClkHS running at 4MHz, Vcc=Vio=3V          |         | 150 |     | μΑ   |

| lı .   | Input Leakage Current                 |                                                            | -1      |     | +1  | μΑ   |

| Voh    | High Level Output Voltage             | Ioh= tbd mA Vio=Min.                                       | Vio-0.4 |     |     | V    |

| Vol    | Low Level Output Voltage              | IoI = tbd mA, Vio=Min                                      |         |     | 0.4 | V    |

| Vih    | High Level Input Voltage              | LVTTL Level, Vio = Max.                                    | 2.0     |     |     | V    |

| Vil    | Low Level Input Voltage               | LVTTL Level, Vio = Min.                                    |         |     | 0.8 | V    |

| Vth    | High Level Schmitt Trigger<br>Voltage |                                                            | 1.1     |     | 2.4 | V    |

| VtI    | Low Level Schmitt Trigger<br>Voltage  |                                                            | 0.6     |     | 1.8 | V    |

| Vh     | Schmitt Trigger Hysteresis            |                                                            | 0.1     |     |     | V    |

| Symbol | Parameter                    | Conditions              | Min | Тур | Max       | Unit      |

|--------|------------------------------|-------------------------|-----|-----|-----------|-----------|

| Rpu    | Pull Up Resistor             | V <sub>i</sub> =0V      | 20  |     | 200       | $k\Omega$ |

| Rpd    | Pull Down Resistor Vi=Vcc 20 |                         |     | 200 | $k\Omega$ |           |

| Ci     | Input Terminal Capacitance   | f=1MHz, Vcc=0V          |     |     | 10        | pF        |

| Co     | Output Terminal Capacitance  | f=1MHz, Vcc=0V          |     |     | 10        | pF        |

| Cio    | Input/Output Terminal Cap.   | f=1MHz, Vcc=0V          |     |     | 10        | pF        |

| t(POR) | Time delay Power-on Reset    | From rising edge of WRN |     |     | 360       | ns        |

#### 2.4 System Performance

At Vcc=3.3 V  $\pm$  0.3 V, Ambient temperature -40 °C ... +85 °C unless otherwise specified

| Symbol             | Parameter                      | Conditions                                       | Min | Тур    | Max | Units   |

|--------------------|--------------------------------|--------------------------------------------------|-----|--------|-----|---------|

| INL                | Integral Non-linearity strain  |                                                  |     | t.b.d. |     | % of FS |

|                    | Offset                         | Initial, uncalibrated                            |     | ± 50   |     | μV      |

|                    | Offset drift                   | total system, 1kOhm DMS, 5V                      |     |        |     |         |

|                    |                                | Fullbridge                                       |     | 5      |     | nV/K    |

|                    |                                | Halfbridge                                       |     | 80     |     | nV/K    |

|                    | Gain drift                     | total system, 1kOhm DMS, 5V                      |     | 1      |     | ppm /K  |

|                    | over -40°C 120°C               |                                                  |     |        |     |         |

| PSRR1 <sup>1</sup> | Power Supply Rejection Ratio   | Halfbridge <sup>2</sup>                          |     | 120    |     | dB      |

|                    | Vio                            | Vio 3 V or 5 V ±10%                              |     |        |     |         |

| PSRR2 <sup>1</sup> | Power Supply Rejection Ratio   | Fullbridge <sup>2</sup>                          |     | >140   |     | dB      |

|                    | Vio                            | Vio 3 V or 5 V ±10%                              |     |        |     |         |

| CMRR               | Common Mode Rejection<br>Ratio | Cannot be defined for PICOSTRAIN measuring prin- |     | 120    |     | dB      |

|                    | Vcc                            | ciple                                            |     |        |     |         |

<sup>1</sup> PSRR= -20\*log(dVdd/dVout)

$<sup>^{\</sup>rm 2}$  Variation Vsg from 3 V to 5 V,  $\,$  Vcc from 2.5 V to 3.3 V  $\,$

#### 2.4.1 Measurement Capability

The following tables show the measurement capabilities for different supply voltages for the strain gage and the PSØ21 core.

All data shown include a SINC3 filter. For getting the data with fast-settle mode multiply the noise values by 1.73 or reduce the #LSB values by 0.8 Bit.

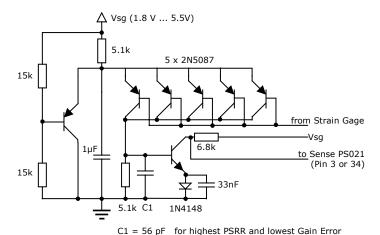

The data refer to the comparator circuit shown in Figure 21.

All measurements are done with a 1 k $\Omega$  fullbridge modified for **FICO**STRAIN.

Table 1: Measurement range 2. Vsg = 5.0 V. Vcc = 3.3 V

| Measuring Rate |          |           |             | No. of LSB's | No     | se    |

|----------------|----------|-----------|-------------|--------------|--------|-------|

| in Hz          | SG Ratio | 2 mV/V FS | 3,3 mV/V FS | @ 2 mV/V     | μV     | ppm   |

| *50.000        | 18,3     | 9,3       | 10,0        | 625          | 16.000 | 3,200 |

| *35.000        | 18,4     | 9,4       | 10,1        | 695          | 14,400 | 2,880 |

| *20.000        | 19,4     | 10,4      | 11,1        | 1.333        | 7,500  | 1,500 |

| 10.000         | 20,8     | 11,8      | 12,5        | 3.400        | 2.900  | 0,580 |

| 4.000          | 22,2     | 13,2      | 13,9        | 9.500        | 1,050  | 0,210 |

| 2.000          | 22,9     | 13,9      | 14,6        | 15.100       | 0,660  | 0,132 |

| 1.000          | 23,5     | 14,5      | 15,2        | 22700        | 0,440  | 0,088 |

| 500            | 24,0     | 15,0      | 15,7        | 32.700       | 0,305  | 0,061 |

| 250            | 24,5     | 15,5      | 16,2        | 47.600       | 0,210  | 0,042 |

| 100            | 25,3     | 16,3      | 17.0        | 83.000       | 0,120  | 0,024 |

| 50             | 25,8     | 16,8      | 17,5        | 117.000      | 0,085  | 0,017 |

| 20             | 26,5     | 17,5      | 18,2        | 192.000      | 0,055  | 0,010 |

| 10             | 27,1     | 18,1      | 18,8        | 277.000      | 0,036  | 0,007 |

| 5              | 27,5     | 18,5      | 19.2        | 384.000      | 0,028  | 0,005 |

| 2              | 28.1     | 19.1      | 19,8        | 555.000      | 0,018  | 0,004 |

SG Ratio: Resolution referred to resistance ratio of the SG

2mV/V: Resolution referred to 2mV/V maximum output (Full Scale)

3.3 mV/V: Resolution referred to 3.3mV/V maximum output (Full Scale)

\*measured in measuring range 1

Table 2: Measurement range 2, Vsg = 3.0 V, Vcc = 3.0 V

| Measuring Rate |          | ENOB      |             | No. of LSB's | No    | ise   |

|----------------|----------|-----------|-------------|--------------|-------|-------|

| in Hz          | SG Ratio | 2 mV/V FS | 3,3 mV/V FS | @ 2 mV/V     | μV    | ppm   |

| *50.000        |          |           |             |              |       |       |

| *35.000        |          |           |             |              |       |       |

| *20.000        |          |           |             |              |       |       |

| 10.000         | 20,5     | 11,5      | 12,2        | 2850         | 2,100 | 0,700 |

| 4.000          | 22.0     | 13.0      | 13.7        | 8.000        | 0,750 | 0,250 |

| 2.000          | 22.5     | 13.5      | 14.2        | 11.700       | 0,510 | 0,170 |

| 1.000          | 22.9     | 13.9      | 14.6        | 15.700       | 0,380 | 0,126 |

| 500            | 23.5     | 14.5      | 15,2        | 23.000       | 0,260 | 0,086 |

| 250            | 24,0     | 15,0      | 15.7        | 34.200       | 0,175 | 0,058 |

| 100            | 24.8     | 15.8      | 16.5        | 57.000       | 0,105 | 0,035 |

| 50             | 25.3     | 16.3      | 17.0        | 80.000       | 0,075 | 0,025 |

| 20             | 26.0     | 17.0      | 17.1        | 136.000      | 0,044 | 0,015 |

| 10             | 26.4     | 17.4      | 18.1        | 176.000      | 0,034 | 0,011 |

| 5              | 27.0     | 18.0      | 18.7        | 250.000      | 0,024 | 0,008 |

| 2              | 27.3     | 18.3      | 19.0        | 333.000      | 0,018 | 0,006 |

<sup>\*</sup> measured in measuring range 1

Table 3: Measurement range 2, Vsg = 2.0 V, Vcc = 2.0 V

| Measuring Rate | ate Eff. Bits No. of LSB's |           |             | No. of LSB's | No    | ise   |

|----------------|----------------------------|-----------|-------------|--------------|-------|-------|

| in Hz          | SG Ratio                   | 2 mV/V FS | 3,3 mV/V FS | @ 2 mV/V     | μV    | ppm   |

| 10.000         | 19,5                       | 10,5      | 11,2        | 1.430        | 2,800 | 1,400 |

| 4.000          | 21,3                       | 12,3      | 13,0        | 5.100        | 0,780 | 0,390 |

| 2.000          | 21.7                       | 12.7      | 13.4        | 7.000        | 0,570 | 0,285 |

| 1.000          | 22.0                       | 13.0      | 13.7        | 8.000        | 0,500 | 0,250 |

| 500            | 22,6                       | 13,6      | 14.3        | 12.500       | 0,320 | 0,160 |

| 250            | 23.3                       | 14.3      | 15.0        | 20.000       | 0,200 | 0,100 |

| 100            | 24.0                       | 15.0      | 15.7        | 32.000       | 0,125 | 0,062 |

| 50             | 24.5                       | 15.5      | 16.2        | 48.000       | 0,082 | 0,041 |

| 20             | 25.2                       | 16.2      | 16,9        | 77.000       | 0,052 | 0,026 |

| 10             | 25.8                       | 16.8      | 17.5        | 114.000      | 0,035 | 0,017 |

| 5              | 26.3                       | 17.3      | 18.0        | 166.000      | 0,024 | 0,012 |

| 2              | 26.7                       | 17.7      | 18.4        | 210.000      | 0,019 | 0,009 |

#### 2.4.2 Offset and Gain Error

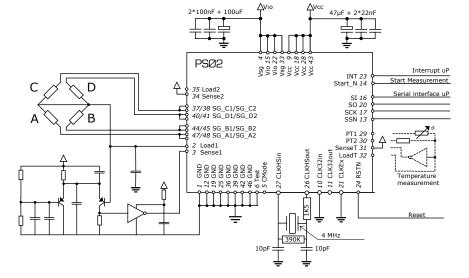

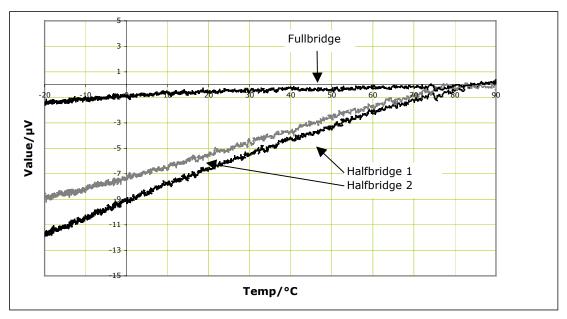

Figure 1: Offset drift of the complete electronics $^1$  in temperature range  $-20^{\circ}$ C to  $90^{\circ}$ C Vsg = Vcc = 3V, 1kOhm SG with 0 mV/V strain

Offset drift halfbridges: 55 nV/K; Offset drift fullbridge: < 2 nV/K

Figure 2: Gain+Offset drift complete electronics in ppm of max. strain in temperature range  $-20^{\circ}$ C to  $90^{\circ}$ C Vsg = Vcc = 3V, 1kOhm SG with 2,5mV/V strain Gain+Offset drift HB1: 1,02 ppm/K; HB2: 1,16 ppm/K; Fullbridge: < 2 nV/K

<sup>&</sup>lt;sup>1</sup> measured with PSA2 evaluation board, SG temperature constant

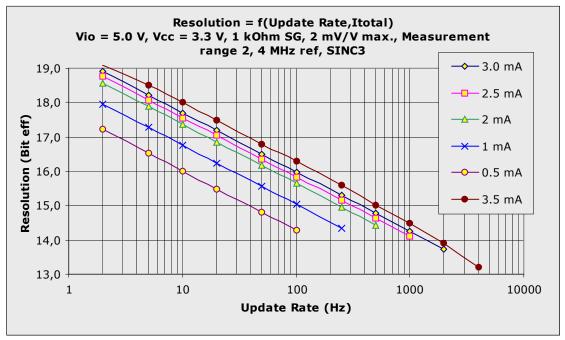

#### 2.4.3 Current consumption

The following graphs refer to the  $\underline{total}$  current, which is the current into the strain gage and into PSØ21 incl. the comparator.

Figure 3: Vsg = 5 V (Strain gage), Vcc = 3.3V (PSØ21)

2.5 Timings

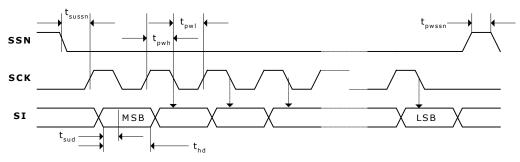

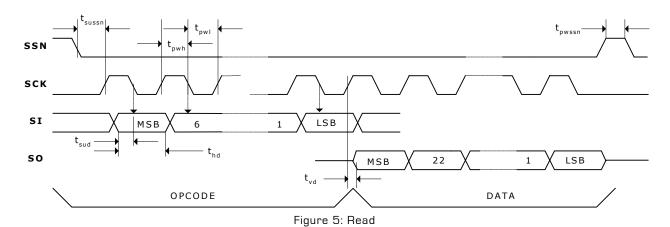

#### 2.5 Timings

At Vcc=3.3V  $\pm$  0.3V, ambient temperature -40°C ... +85°C unless otherwise specified

| Symbol | Parameter                                        | Min  | Тур   |       | Max                 | Units |

|--------|--------------------------------------------------|------|-------|-------|---------------------|-------|

| _      | Oscillator                                       |      |       |       |                     |       |

| Clk32  | 32 kHz reference oscillator                      |      | 32,   | 768   |                     | kHz   |

| toszst | Oscillator start-up time with ceramic resonator  |      | 15    | 50    |                     | μs    |

| toszst | Oscillator start-up time with crystal oszillator |      | 70    | 00    |                     |       |

| CIkHS  | High-speed reference oscillator                  | 2    | 2     | 4     | 5                   | MHz   |

| ClkEx  | External high-speed reference clock input        | 2    | 2     | 4     | 5                   | MHz   |

| -      | Serial interface                                 |      | Max @ | Vio = | =                   |       |

|        |                                                  | 1.8V | 3.    | 3V    | 5V Vio              |       |

| fclk   | Serial clock frequency                           | -    | 1     | 0     | 20                  | MHz   |

|        |                                                  |      | Min @ | Vio = | 1                   |       |

|        |                                                  | 1.8V | 2.2V  | 3.0\  | / 4.5V <sup>2</sup> |       |

| tpwh   | Serial clock, pulse width high                   | 80   | 50    | 30    | 25                  | ns    |

| tpwl   | Serial clock, pulse width low                    | 80   | 50    | 30    | 25                  | ns    |

| tsussn | SSN enable to valid latch clock                  | 20   | 10    | 8     | 7                   | ns    |

| tpwssn | SSN pulse width between write cycles             | 100  | 50    | 30    | 25                  | ns    |

| tsud   | Data set-up time prior to SCLK falling           | 15   | 7     | 6     | 5                   | ns    |

| thd    | Data hold time before SCLK falling               | 10   | 5     | 4     | 3                   | ns    |

|        |                                                  |      | Max @ | Vio = | =                   |       |

|        |                                                  | 1.8V | 2.5V  | 3.3\  | / 5V                |       |

| tvd    | Data valid after SCLK rising                     | tbd. | 40    | 26    | 18                  | ns    |

$<sup>^{\</sup>mbox{\tiny 1}}$  Worst case at supply voltages 2.5V, 3.3V and 5V

Serial Interface (SPI compatible, Clock Phase Bit =1, Clock Polarity Bit =0):

Figure 4: Write

<sup>&</sup>lt;sup>2</sup> Core-Voltage Vcc=3.3V

2.5 Timings

Table 4: OP-Codes

| <u>abie 4: U</u> | P-Codes |   |      |      |      |      |      |                                       |  |  |

|------------------|---------|---|------|------|------|------|------|---------------------------------------|--|--|

| 8 Bit OP Code    |         |   |      |      |      |      |      |                                       |  |  |

| MSB              |         |   |      |      |      |      | LSB  | Description                           |  |  |

| 1                | 0       | 0 | 0    | ADR3 | ADR2 | ADR1 | ADRO | Write into 24 Bit register at address |  |  |

| 1                | 0       | 1 | 1    | 0    | ADR2 | ADR1 | ADRO | Read 24 Bit register from address     |  |  |

| 1                | 0       | 1 | 1    | 1    | ADR2 | ADR1 | ADRO | Read 24 Bit register from address,    |  |  |

|                  |         |   |      |      |      |      |      | autoincrement address                 |  |  |

|                  |         |   |      |      |      |      |      |                                       |  |  |

| 1                | 1       | 0 | 0    | 0    | 0    | 0    | 0    | Init                                  |  |  |

| 0                | 1       | 0 | 1    | 0    | 0    | 0    | 0    | Power On Reset                        |  |  |

| 0                | 0       | 0 | 0    | 0    | 0    | 0    | 1    | Start measurement                     |  |  |

| 0                | 0       | 0 | 0    | 1    | 0    | 0    | 0    | Select Double Bridge 1                |  |  |

| 0                | 0       | 0 | 0    | 1    | 0    | 0    | 1    | Select Double Bridge 2                |  |  |

|                  |         |   |      |      |      |      |      |                                       |  |  |

| 0                | 1       | 1 | ADR4 | ADR2 | ADR3 | ADR1 | ADRO | Write {Reg4, Reg5} to RAM address     |  |  |

2.6 Pin Configuration

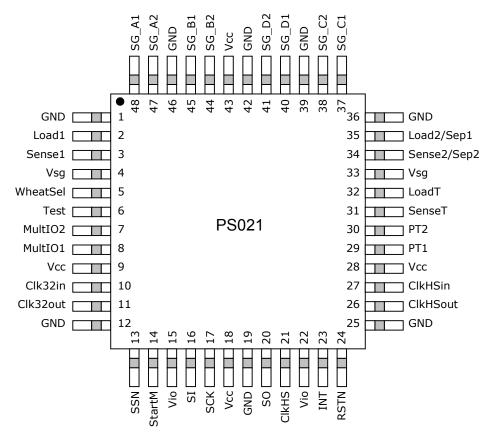

#### 2.6 Pin Configuration

Figure 6: Pinning TQFP48 / QFN7-48

Table 5: Pin Descriptions

| No. | Name     | Description                                 | Value       | If not used          |

|-----|----------|---------------------------------------------|-------------|----------------------|

| 1   | GND      | Ground                                      |             | useu                 |

| 2   | Load1    | Load output 1                               |             | Pins 44,<br>48,47,48 |

| 3   | Sense1   | Sense input 1                               |             | GND                  |

| 4   | Vsg      | Strain gage supply voltage                  |             |                      |

| 5   | WheatSel | Select for Wheatstone Mux in the comparator |             | n.c.                 |

| 6   | Testln   | Test-Pin, connect to GND                    |             | GND                  |

| 7   | MultIO2  | Multifunctional IO                          |             | n.c.                 |

| 8   | MultIO1  | Multi-funcional IO                          |             | n.c.                 |

| 9   | Vcc      | Core supply voltage                         |             |                      |

| 10  | CLK32in  | Input 32kHz clock generator                 |             | GND                  |

| 11  | CLK32out | Output 32kHz clock generator                |             | n.c.                 |

| 12  | GND      |                                             |             |                      |

| 13  | SSN      | Slave Select                                | Low active  | GND                  |

| 14  | StartM   | Start new measurement                       | High active | GND                  |

| 15  | Vio      | I/O supply voltage                          |             |                      |

| 16  | SI       | Input serial interface                      |             |                      |

#### 2.6 Pin Configuration

| 17 | SCK      | Clock serial interface                    |                 |          |

|----|----------|-------------------------------------------|-----------------|----------|

| 18 | Vcc      | Core supply voltage                       |                 |          |

| 19 | GND      | Core suppry voltage                       |                 |          |

| 20 | SO       | Output serial interface                   |                 |          |

| 21 | CIkEx    | Input external high-speed reference clock |                 | GND      |

| 22 | Vio      | I/O supply voltage                        |                 | SIVE     |

| 23 | INTN     | Interrupt Flag                            | LOW active      | n.c.     |

| 24 | RSTN     | Reset input                               | LOW active      | Vio      |

| 25 | GND      | Treact input                              | EGVV dedive     | VIO      |

| 26 | ClkHSout | Output high-speed clock generator         |                 | n.c.     |

| 27 | ClkHSin  | Input high-speed clock generator          |                 | GND      |

| 28 | Vcc      | Core supply voltage                       |                 | OND      |

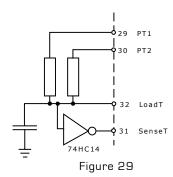

| 29 | PT1      | Port 1 temperature measurement            |                 | Pin 32   |

| 30 | PT2      | Port 2 temperature measurement            |                 | Pin 32   |

| 31 | SenseT   | Sense input temperature measurement       |                 | GND      |

| 32 | LoadT    | Load output temperature measurement       |                 | Pins 29. |

| عد | Ludui    | Load output temperature measurement       |                 | 30       |

| 33 | Vsq      | Strain gage supply voltage                |                 | 30       |

| 34 | Sense2   | Sense input 2                             |                 | Vsq      |

| 54 | Sep1     | Separate compensation                     |                 | vsy      |

| 35 | Load2    | Load output 2                             | one-sense mode: | n.c.     |

| 00 | Loade    | Load output E                             | halfbridge:     |          |

|    | Sep2     | Separate compensation                     | Hanbridge.      | 38,40,41 |

| 36 | GND      | Coparate compensation                     |                 | 00,40,41 |

| 37 | SG_C1    | Port 1 halfbridge C                       |                 | Pin 35   |

| 38 | SG_C2    | Port 2 halfbridge C                       |                 | Pin 35   |

| 39 | GND      | 1 51 0 E Hallbridge G                     |                 | 1 111 00 |

| 40 | SG_D1    | Port 1 halfbridge D                       |                 | Pin 35   |

| 41 | SG_D2    | Port 2 halfbridge D                       |                 | Pin 35   |

| 42 | GND      | 1 0.0 E Humbridge D                       |                 | 55       |

| 43 | Vcc      | Core supply voltage                       |                 | 1        |

| 44 | SG_B2    | Port 2 halfbridge B                       |                 | Pin 2    |

| 45 | SG_B1    | Port 1 halfbridge B                       |                 | Pin 2    |

| 46 | GND      | 1 0.0 1 Hallbridge D                      |                 |          |

| 47 | SG A2    | Port 2 halfbridge A                       |                 | Pin 2    |

| 48 | SG_A1    | Port 1 halfbridge A                       |                 | Pin 2    |

| +0 | JU_A I   | Trock i manuflage A                       |                 | 1 III C  |

2.7 Package Drawings

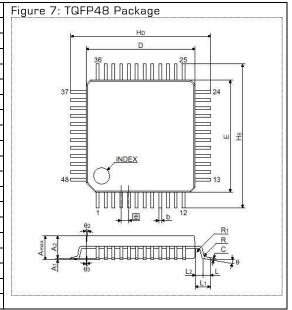

#### 2.7 Package Drawings

Table 6: Dimensions TQFP48 package

| able 6: Dimensions TUFP48 package |        |               |        |       |                |         |  |  |  |

|-----------------------------------|--------|---------------|--------|-------|----------------|---------|--|--|--|

| Symbol                            | Dimens | sion in Milli | meters | Dime  | ension in Inch | nes (*) |  |  |  |

|                                   | Min.   | Nom.          |        | Max.  | Min.           | Nom.    |  |  |  |

| Е                                 | 6,9    | 7             |        | 7,1   | (0,272)        | (0,276) |  |  |  |

| D                                 | 6,9    | 7             |        | 7,1   | (0,272)        | (0,276) |  |  |  |

| А                                 |        |               |        | 1,7   |                |         |  |  |  |

| A1                                |        | 0,1           |        |       |                | (0,004) |  |  |  |

| A2                                | 1,3    | 1,4           |        | 1,5   | (0,052)        | (0,055) |  |  |  |

| е                                 |        | 0,5           |        |       |                | (0,020) |  |  |  |

| b                                 | 0,13   | 0,18          |        | 0,28  | (0,006)        | (0,007) |  |  |  |

| С                                 | 0,1    | 0,125         |        | 0,175 | (0,004)        | (0,005) |  |  |  |

| θ                                 | O°     |               |        | 10°   | [0°]           |         |  |  |  |

| L                                 | 0,3    | 0,5           |        | 0,7   | (0,012)        | (0,020) |  |  |  |

| L1                                |        | 1             |        |       |                | (0,039) |  |  |  |

| L2                                |        | 0,5           |        |       |                | (0,020) |  |  |  |

| HE                                | 8,6    | 9             |        | 9,4   | (0,339)        | (0,354) |  |  |  |

| HD                                | 8,6    | 9             |        | 9,4   | (0,339)        | (0,354) |  |  |  |

| θ2                                |        | 7°            |        |       |                | [7°]    |  |  |  |

| θ3                                |        | 4°            |        |       |                | [4°]    |  |  |  |

| R                                 |        | 0,2           |        |       |                | (0,008) |  |  |  |

| R1                                |        | 0,2           |        |       |                | (0,008) |  |  |  |

Table 7: Dimensions QFN7-48 package

| Symbol | Dimens | ion in Milli | meters | Figure 8: QFN7-48 Package                                  |

|--------|--------|--------------|--------|------------------------------------------------------------|

|        | Min.   | Nom.         |        | Top View Bottom View                                       |

| Е      |        | 7            |        | D 13 1 24 原                                                |

| D      |        | 7            |        | 24 (a) (b) (c) (c) (c) (c) (c) (c) (c) (c) (c) (c          |

| Α      |        |              | 1.00   | 12 0 025 0                                                 |

| A1     |        |              | 0.05   | Index                                                      |

|        |        |              |        |                                                            |

| е      |        | 0,5          |        |                                                            |

| b      | 0.18   |              | 0.30   |                                                            |

|        |        |              |        |                                                            |

|        |        |              |        |                                                            |

| L      | 0.30   |              | 0.50   | $\begin{array}{c c} & & & & & & & & & & & & & & & & & & &$ |

| х      |        |              | 0.10   | 48 37 37                                                   |

| у      |        |              | 0.08   |                                                            |

|        |        |              |        | <b>5</b> /                                                 |

|        |        |              |        | <u> </u>                                                   |

|        |        |              |        |                                                            |

<sup>\*</sup> for reference

2.7 Package Drawings

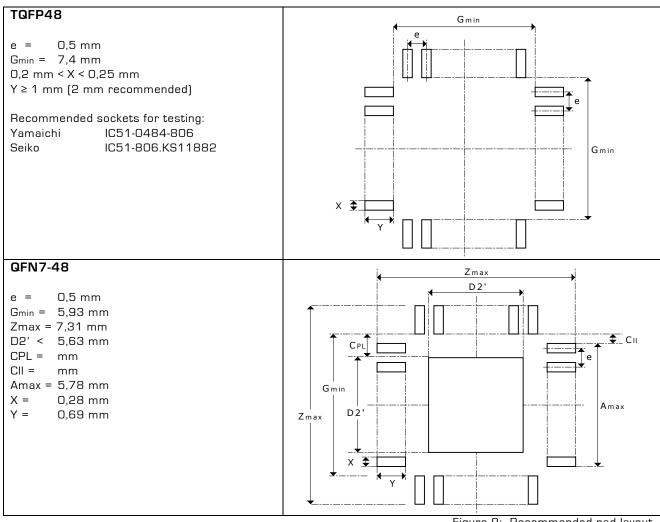

#### **Recommended Foot Pattern**

Figure 9: Recommended pad layout

#### 2.8 Registers

#### 2.8.1 Write Registers

Table 8 Write registers (Default values in second row)

| Bit | Reg O       |   | Reg 1     |   | Reg 2        |            | Reg 3      |            | Reg 4      |     | Reg 5 |     | Reg 6  |   | Reg 7           |         |        |   |      |   |

|-----|-------------|---|-----------|---|--------------|------------|------------|------------|------------|-----|-------|-----|--------|---|-----------------|---------|--------|---|------|---|

| 23  |             | 1 |           | 0 |              | 0          |            | х          |            | 1   |       | 1   | s.c.   | 0 | RunCont         | 0       |        |   |      |   |

| 22  | CalAvRate   | 0 |           | 0 | RdsonModify  | 1          |            | х          |            | 0   |       | 0   | S.C.   | 1 | Rdson<br>Filter | 0       |        |   |      |   |

| 21  | RdsonSimple | 0 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   | s.c.   | 0 | s.c.            | 0       |        |   |      |   |

| 20  | ClkHSDiv    | 0 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   | s.c.   | 1 | ClkHSring       | 0       |        |   |      |   |

| 19  | CIKHSDIV    | 0 |           | 0 |              | 1          |            | х          |            | 0   |       | 0   | s.c.   | 0 | ClkHSon         | 0       |        |   |      |   |

| 18  | Cmeasure    | 0 | CycleTime | 0 | RdsonAvRate  | 0          |            | х          |            | 0   |       | 0   | s.c.   | 0 | CIKHSON         | 1       |        |   |      |   |

| 17  | MultEN      | 0 |           | 0 | RasonAvRate  | 0          |            | х          |            | 0   |       | 0   | s.c.   | 0 | s.c.            | 0       |        |   |      |   |

| 16  | SelClk32    | 1 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   | Noise1 | 0 | s.c.            | 0       |        |   |      |   |

| 15  | SubFB       | 0 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   |        | 0 | n.c.            | $\prod$ |        |   |      |   |

| 14  | SumFB       | 0 |           | 0 |              | 1          |            | х          |            | 0   |       | 0   | 0.10.1 | 1 | s.c.            | 0       |        |   |      |   |

| 13  | NegSense2   | 0 |           | 0 |              | GainAvHate | GainAvRate | 3aINAVHate | JainAvRate | 0   |       | х   |        | 0 |                 | 0       | CalDel | 0 | s.c. | 0 |

| 12  | NegSense1   | 0 |           | 1 |              |            | 0          | Mult1      | х          | RD1 | 0     | RD2 | 0      |   | 0               | s.c.    | 0      |   |      |   |

| 11  | NegSenseT   | 1 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   | s.c.   | 0 | s.c.            | 0       |        |   |      |   |

| 10  | TD-+-       | 0 |           | 0 | GainCorRate  | 0          |            | х          |            | 0   |       | 0   | s.c.   | 1 | s.c.            | 0       |        |   |      |   |

| 9   | TempRate    | 0 |           | 0 | GainCorRate  | 0          |            | х          |            | 0   |       | 0   | s.c.   | 0 | s.c.            | 0       |        |   |      |   |

| 8   | DoubleBr    | 0 |           | 0 |              | 1          |            | х          |            | 0   |       | 0   | s.c.   | 1 | s.c.            | 0       |        |   |      |   |

| 7   | SubOffset   | 0 |           | 0 | PortFilter   | 0          |            | х          |            | 0   |       | 0   | n.c.   |   | s.c.            | 0       |        |   |      |   |

| 6   | Sinc3       | 0 | AD-4-     | 0 |              | 0          |            | х          |            | 0   |       | 0   | s.c.   | 0 | s.c.            | 0       |        |   |      |   |

| 5   | SingleCon   | 0 | AvRate    | 1 | OffsetAvRate | 1          |            | х          |            | 0   |       | 0   | s.c.   | 0 | s.c.            | 1       |        |   |      |   |

| 4   | HighRes     | 1 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   |        | 1 | s.c.            | 1       |        |   |      |   |

| 3   | Mrange2     | 1 |           | 0 |              | 0          |            | х          |            | 0   |       | 0   | WarmUp | 0 | s.c.            | 0       |        |   |      |   |

| 2   | HighSpeed   | 0 |           | 0 | C-101-       | 0          |            | х          |            | 0   |       | 0   |        | 0 | s.c.            | 1       |        |   |      |   |

| 1   | D-:         | 0 |           | 0 | CalCycle     | 1          |            | Х          |            | 0   |       | 0   | NAT-L- | 0 | s.c.            | 0       |        |   |      |   |

| 0   | Bridge      | 0 |           | 0 |              | 0          |            | Х          |            | 0   |       | 0   | MFake  | 0 | s.c.            | 1       |        |   |      |   |

s.c. = Special acam configuration bits, n.c. = not in use

| Bit | Reg 8      |   | Reg 9   |   | Reg 10        |   | Reg 11  |   | Reg 12  |   | Reg 13  |   | Reg 14  |   | Reg 15  |   |

|-----|------------|---|---------|---|---------------|---|---------|---|---------|---|---------|---|---------|---|---------|---|

| 23  | SignTG2    | 0 | s.c.    | 0 | SignMult2     | 0 |         | х |         | х |         | х |         | х |         | х |

| 22  | SignTG1    | 0 | s.c.    | 0 | SignMult1     | 0 |         | х |         | х |         | х |         | х |         | х |

| 21  | CompSleep  | 0 | s.c.    | 0 | PSØ21_Adj1    | 0 |         | х |         | х |         | х |         | х |         | х |

| 20  | CompConOn  | 0 | s.c.    | 0 | PSØ21_Adj1    | 1 |         | х |         | х |         | х |         | х |         | х |

| 19  |            | 0 | s.c.    | 0 | PSØ21_Adj1    | 0 |         | х |         | х |         | х |         | х |         | х |

| 18  |            | 0 | s.c.    | 1 | PSØ21_Adj1    | 0 |         | х |         | х |         | х |         | х |         | х |

| 17  | CompCon    | 0 | s.c.    | 1 | PSØ21_Adj1    | 0 |         | х |         | х |         | х |         | х |         | х |

| 16  |            | 0 | s.c.    | 0 | PSØ21_Adj1    | 1 |         | х |         | х |         | х |         | х |         | х |

| 15  | D+C4       | 1 | n.c.    | 0 | Quarterbridge | 0 |         | х |         | х |         | х |         | х |         | х |

| 14  | PortSw4    | 1 | n.c.    | 0 | Cal_Adjust    | 0 |         | х |         | х |         | х |         | х |         | х |

| 13  | PortSw3    | 1 | Cmeas2  | 0 | Cal_Adjust    | 0 |         | х |         | х |         | х |         | х |         | х |

| 12  | Portawa    | 0 | Cineasz | 0 | Cal_Adjust    | 0 | Mult2   | х | TKOffs1 | х | TKOffs2 | х | TKGain1 | х | TKGain2 | х |

| 11  | PortSw2    | 0 |         | 0 | Cal_Adjust    | 0 | iviuite | х | IKUIIST | х | IKUIISE | х |         | х |         | х |

| 10  | Furtawa    | 1 |         | 0 | Cal_Adjust    | 0 |         | х |         | х |         | х |         | х |         | х |

| 9   | PortSw1    | 0 |         | 0 | Cal_Adjust    | 0 |         | х |         | х |         | х |         | х |         | х |

| 8   | Portawi    | 0 |         | 0 | Cal_Adjust    | 0 |         | х |         | х |         | х |         | х |         | х |

| 7   | SpreadRng  | 0 |         | 0 | ModSpanByT    | 0 |         | х |         | х |         | х |         | х |         | х |

| 6   | Spreadking | 0 | AvRate2 | 0 | ModRSpan      | 0 |         | х |         | х |         | х |         | х |         | х |

| 5   | Canada     | 0 | AVRate2 | 0 | LoadStartDel  | 0 |         | х |         | х |         | х |         | х |         | х |

| 4   | SpreadSrc  | 0 |         | 0 | LoadStart     | 0 |         | х |         | х |         | х |         | х |         | х |

| 3   | SpreadEN   | 0 |         | 0 | PSØ21_Adj2    | 0 |         | х |         | х |         | х |         | х |         | х |

| 2   | WheatEN    | 0 |         | 0 | PSØ21_Adj2    | 0 |         | х |         | х |         | х |         | х |         | х |

| 1   | SepGain    | 0 |         | 0 | PSØ21_Adj2    | 0 |         | Х |         | Х |         | х |         | х |         | х |

| 0   | Mult2En    | 0 |         | 0 | PSØ21_Adj2    | 0 |         | Х |         | Х |         | х |         | х |         | х |

#### Note:

Registers Mult1, Mult2, TKOffs1, TKOffs2, TKGain1 and TKGain2 are not initialized when a INIT or Power-on reset is done. It is mandatory to write the correct values into these registers before switching on multiplication.

Table 9: Short description of the Bits:

| able 3. Short description | 1 01 016 0163.                       |                               |

|---------------------------|--------------------------------------|-------------------------------|

| Name                      | Description                          | Values                        |

| Reg O                     |                                      |                               |

| Bridge <1,0>:             | Select bridge mode:                  | [O,O] = Fullbridge, One-sense |

|                           | One-sense or Alternating mode        | mode                          |

|                           | Halfbridge or fullbridge             | [1,1] = Fullbridge, alt. mode |

|                           |                                      | [0,1] = BridgeO (Ports A, B)  |

|                           |                                      | [1,0] = Bridge1 (Ports C, D)  |

| HighSpeed:                | Select frequency mode in measurement | O = 32 kHz Clock              |

|                           | range 1                              | 1 = ClkHS                     |

| Mrange2                   | Switch PSØ21 to measurement range 2  | O = measurement range 1       |

|                           |                                      | 1 = measurement range 2       |

| HighRes                   | Select High-Resolution mode of the   | O = without HighRes           |

|                           | TDC time measuring unit              | 1 = with HighRes              |

| SingleCon                 | Single-conversion mode               | 1 = Single-conversion on      |

| Sinc3       | Switch-on SINC3 filter                            | O = Fast settle       |

|-------------|---------------------------------------------------|-----------------------|

|             |                                                   | 1 = SINC3-Filter on   |

| SubOffset   | Select Auto-offset calculation                    | 1 = with Auto-offset  |

| DoubleBr    | Switch to doublebridge mode                       |                       |

| TempRate    | Controls temperature measurement                  | O = off               |

|             |                                                   | 1 = each AVRate       |

|             |                                                   | 2 = each 6th AVRate   |

|             |                                                   | 3 = each 9th AVRate   |

| NegSenseT   | Negation SenseT input                             | O = falling edge      |

| NegSense1   | Negation Sense1 input                             | O = falling edge      |

| NegSense2   | Negation Sense2 input                             | O = falling edge      |

| SumFB       | Select summation in fullbridge mode               | HB1 + HB2             |

| SubFB       | Select difference in fullbridge mode              | HB2 - HB1             |

| SelClk32    | Use 32 kHz clock as cycle clock                   | 1 = on, MRange 1 only |

| MultEN      | Switch-on multiplication                          | 1 = on                |

| Cmeasure    | Switch-on capacity measurement                    | 1 = on                |

| CIkHSDiv    | Sets predivider for CLKHS                         | O = divided by 1      |

|             | Mrange2: TDC range = max. discharge               | 1 = divided by 2      |

|             | time = Tref*2 <sup>CIkHSDiv</sup> *2 <sup>8</sup> | 2 = divided by 4      |

|             | ClkHSDiv = 1 is recommended                       | 3 = divided by 8      |

| RdsonSimple | Enable simplified Rdson correction                | 1 =on                 |

| CalAvRate   | Sets the averaging rate of the calibration        | 0 = 1                 |

|             | value in measurement range 2                      | 1 = 8                 |

|             | _                                                 | 2 = 32                |

|             |                                                   | 3 = 64                |

| Reg 1     |                                          |        |

|-----------|------------------------------------------|--------|

| AVRate    | Averaging rate for a single measurement  | 1 4095 |

| CycleTime | Cycle time in multiples of the reference | 1 4095 |

|           | clock for the cycle time                 |        |

| Reg 2        |                                                                                   |                                                                            |

|--------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| CalCycle     | Sets the number of cycles before the TDC does a calibration measurement           | 1 = each cycle<br>2 = each 2nd<br><br>15 = each 15th                       |

| OffsetAVRate | Averaging rate of Auto-offset measurements                                        | 1 = 1<br>2 = 2<br>3 = 4<br><br>7 = 128                                     |

| PortFilter   | Additional Filter                                                                 | 1 = on (is recommended)                                                    |

| GainCorRate  | Sets the repetition rate of gain compensation measurements in multiples of AVRate | O = off (no gain compensation) 1 = each AVRate 2 = each 2nd 15 = each 15th |

| GainAVRate   | Averaging rate of gain compensation                                               | 1 = 1<br>2 = 2<br>3 = 4<br><br>15 = 16284                                  |

| D I A)/D :   |                                            | Ta a                                |

|--------------|--------------------------------------------|-------------------------------------|

| RdsonAVRate  | Averaging rate Rdson compensation          | 1 = 1                               |

|              |                                            | 2=2                                 |

|              |                                            | 3=4                                 |

|              |                                            |                                     |

| D   NA   116 | N 100 11 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1   | 15=16284                            |

| RdsonModify  | Modification of Rdson calculation after an | Use default value                   |

|              | INIT                                       |                                     |

| Reg 3        |                                            |                                     |

| Mult1        | Multiplication factor, fixed-point number  | Mult1 = Register3/2 <sup>16</sup> = |

| TVI CITY I   | with 8 integer and 16 fractional digits    | 0 255.9999                          |

|              | with a micegal and 10 madicinal algor      | 0 200.9999                          |

| Reg 4        |                                            |                                     |

| RD1          | Write-back register Rdson halfbridge1      | Use default value 0x800000          |

| 1.5.         | With Back regioner materinate rage r       | Coc delidati valde execces          |

| Reg 5        |                                            |                                     |

| RD2          | Write-back register Rdson halfbridge2      | Use default value 0x800000          |

|              | 3                                          | 1                                   |

| Reg 6        |                                            |                                     |

| Mfake        | Number of dummy cycles at the beginning    | 0 = 0                               |

|              | of an AVRate measurement                   | 1 = 1                               |

|              |                                            | 2 = 2                               |

|              |                                            | 3 = 4                               |

| WarmUp       | Number of dummy cycles after an INIT       | O = off                             |

|              |                                            | 1 = 16                              |

|              |                                            | 2 = 32                              |

|              |                                            | 3 = 64                              |

|              |                                            |                                     |

| 0 ID I       |                                            | 7 = 1024                            |

| CalDel       | Controls point in time of calibration in   | CalDel # of periods                 |

|              | multiples of the ClkHS/ClkEx period after  | O don't use                         |

|              | start of capacitor discharge               | 1 4                                 |

|              |                                            | 2 5                                 |

|              |                                            | <br>15 18                           |

| Noise1       | Modifies the internal noise generator      | 0 = on                              |

| 140.00 1     | Wicames the micrital holds generated       | 0 011                               |

| Reg 7        |                                            |                                     |

| ClkHSon      | Switch-on high-speed oscillator            | O = Oscillator off                  |

|              |                                            | 1 = Oscillator on                   |

|              |                                            | 2 = settling time = 640 µs          |

|              |                                            | 3 = settling time = 1280 µs         |

| ClkHSring    | Switch-on internal ring-oscillator         | 1 = ring oscillator on              |

| RdsonFilter  | Switch-on spike filter for Rdson           | 1 = Filter on                       |

|              | compensation                               |                                     |

| RunCont      | Runtime of internal ring-oscillator        | O = if required                     |

|              |                                            | 1 = continuously                    |

|              |                                            |                                     |

|              |                                            |                                     |

| Reg 8        |                                            |                                     |

| Mult2EN      | Enable 2nd multiplication factor for 2nd   | 1 = on                              |

|              | I bolthaidee on 'Ind fullbaidee            |                                     |

halfbridge or 2nd fullbridge

| SepGain   | Switch to separate gain compensation     | 1 = on, mandatory in Wheatstone |

|-----------|------------------------------------------|---------------------------------|

| •         | resistors                                | mode                            |

| WheatEN   | Switch to Wheatstone mode                | 1 = on                          |

| SpreadEN  | Enable adding noise to the cycle time    | 1 = on                          |

| SpreadSrc | Select source of noise generator         | O = each cycle                  |

|           |                                          | 1 = each 8 <sup>th</sup> cycle  |

|           |                                          | 2 = each interrupt              |

|           |                                          | 2 = interrupt                   |

| SpreadRng | Sets the range of the cycle time noise   | O = O cycle                     |

|           |                                          | 1 = add noise to 4 cycles       |

|           |                                          | 2 = add noise to 8 cycles       |

|           |                                          | 3 = add noise to 16 cycles      |

| PortSw1   | Free assignment ports to pins 48,47      | 00 = SG_A1,SG_A2                |

| PortSw2   | Free assignment ports to pins 45,44      | 01 = SG_B1,SG_B2                |

| PortSw3   | Free assignment ports to pins 41,40      | 10 = SG_C1,SG_C2                |

| PortSw4   | Free assignment ports to pins 37,38      | 11 = SG_D1,SG_D2                |

| CompCon   | Comparator control bits                  |                                 |

| CompConOn | Selects 'switched Comparator'            | 1 = on                          |

| CompSleep | Sets external comparator to sleep mode   | 1 = on                          |

| SignTG1,  | Sign of correction for span compensation |                                 |

| SignTG2   | resistors                                |                                 |

| Reg 9   |                                                           |                                                                                                                                         |

|---------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| AvRate2 | Averaging rate for the 2nd bridge in doublebridge mode    | O = off, 2nd bridge uses AvRate                                                                                                         |

| Cmeas2  | Switch for capacity measurement with external multiplexer | O = off 1 = on without compensation 2 = on with compensation, analog Mux with enable 3 = on with compensation, 2 single analog switches |

| Reg 10                  |                                                        |                                              |

|-------------------------|--------------------------------------------------------|----------------------------------------------|

| LoadStart               | Start measurement through load pin (not the port pins) | 1 = on (recommended)                         |

| LoadStartDel            | Sets delay with LoadStart                              | O = about 25 ns typ.<br>1 = about 140ns Typ. |

| ModRSpan                | Software adaptation of the bridges Span resistor Rspan | 1 = on, recommended for bridges with Rspan   |

| ModSpanByT              | Replace Rspan with temperature measurement value       | 1 = on                                       |

| SignMult2,<br>SignMult1 | Signs for the multiplication factors                   | O = positive<br>1 = negative                 |

| Reg 11 |                                           |                                     |

|--------|-------------------------------------------|-------------------------------------|

| Mult2  | Multiplication factor, fixed-point number | Mult1 = Register3/2 <sup>16</sup> = |

|        | with 8 integer and 16 fractional digits   | 0 255.9999                          |

| _       |                                                     |                                  |  |  |

|---------|-----------------------------------------------------|----------------------------------|--|--|

| Reg 12  |                                                     |                                  |  |  |

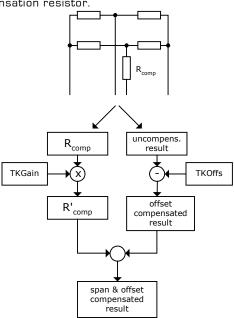

| TkOffs1 | Offset factor for 1st fullbridge in ppm             | 16 Bit integer, 8 Bit fractional |  |  |

|         |                                                     |                                  |  |  |

| Reg 13  |                                                     |                                  |  |  |

| TkOffs2 | Offset factor for 2 <sup>nd</sup> fullbridge in ppm | 16 Bit integer, 8 Bit fractional |  |  |

|         |                                                     |                                  |  |  |

| Reg 14  |                                                     |                                  |  |  |

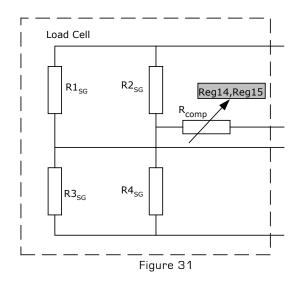

| TkGain1 | Multiplication factor Rspan 1st fullbridge          | 8 Bit integer, 16 Bit fractional |  |  |

|         |                                                     |                                  |  |  |

| Reg 15  |                                                     |                                  |  |  |

| TkGain2 | Multiplication factor Rspan 2nd fullbridge          | 8 Bit integer, 16 Bit fractional |  |  |

#### 2.8.2 Read Registers / Ouput Data Formats

Table 10: Read Registers

|     | To. Troud Trogramme |      |            |                                                                       |            |           |             |             |          |            |          |

|-----|---------------------|------|------------|-----------------------------------------------------------------------|------------|-----------|-------------|-------------|----------|------------|----------|

| ADR | Symbol              | Bits | Descripti  | Description                                                           |            |           |             |             |          |            |          |

| 0   | HB1                 | 24   | Result ha  | lfbridge 1,                                                           | fixed-po   | int no. w | ith 16 inte | ger digits, | 8 fracti | onal digit | s        |

| 1   | HB2                 | 24   | Result ha  | lfbridge 2,                                                           | fixed-po   | int no. w | ith 16 inte | ger digits, | 8 fracti | onal digit | s        |

| 2   | STAT/               | 24   | Bit 23     | Bit 22                                                                | Bit 21     | Bit 20    | Bit 19      | Bit 18      | Bit 17   | Bit 16     | Bit 150  |

|     | TMP                 |      | Double     | TMP                                                                   | Error      | Error     | Error       | Timeout     | Timeo    | Timeo      | Tempera- |

|     |                     |      | Bridge     |                                                                       | PLL1       | PLL2      | DSP         | TMP         | ut       | ut         | ture     |

|     |                     |      |            |                                                                       |            |           |             |             | HB2      | HB1        | result   |

| 3   | REG O               | 24   | Content of | Content of write register 0, to be used for testing the communication |            |           |             |             |          |            |          |

| 4   | TDC1                | 24   | TDC resu   | TDC result                                                            |            |           |             |             |          |            |          |

| 5   | TDC2                | 24   | TDC CAL    | TDC CAL value in measuring range 2                                    |            |           |             |             |          |            |          |

| 6   | RD1                 | 24   | Rdson co   | Rdson configuration value to be written into register 4               |            |           |             |             |          |            |          |

| 7   | RD2                 | 24   | Rdson co   | nfiguratior                                                           | n value to | be writ   | ten into re | gister 5    |          |            |          |

#### Result registers HB1 and HB2

The contents of registers HB1 and HB2 depend on the operating mode:

#### a. Without Doublebridge

Table 11:

| <br>IDIC II. |       |       |             |             |

|--------------|-------|-------|-------------|-------------|

| Bridge[1:0]  | SumFB | SubFB | Content HB1 | Content HB2 |

| 0 or 3       | 0     | 0     | HB1         | HB2         |

| 1            | 0     | 0     | HB1         |             |

| 2            | 0     | 0     |             | HB2         |

| 0 or 3       | 1     | 0     |             | HB1 + HB2   |

| 0 or 3       | 0     | 1     |             | HB2 - HB1   |

### **b. With Doublebridge** Table 12:

| able 12.    |       |       |        |                |                    |  |  |

|-------------|-------|-------|--------|----------------|--------------------|--|--|

| Bridge[1:0] | SumFB | SubFB | DBStat | Content<br>HB1 | Content 2          |  |  |

| 0 or 3      | 0     | 0     | 0      | HB1 of FB1     | HB2 of FB1         |  |  |

| 1           | 0     | 0     | X      | HB1 of FB1     | HB2 of FB1         |  |  |

| 2           | 0     | 0     | X      | HB1 of FB2     | HB2 of FB2         |  |  |

| 0 or 3      | 1     | 0     | 0      |                | (HB1 + HB2) of FB1 |  |  |

| 0 or 3      | 0     | 1     | 0      |                | (HB2 - HB1) of FB1 |  |  |

| 0 or 3      | 0     | 0     | 1      |                | HB2 of FB2         |  |  |

| 0 or 3      | 1     | 0     | 1      |                | (HB1 + HB2) of FB2 |  |  |

| 0 or 3      | 0     | 1     | 1      |                | (HB2 - HB1) of FB2 |  |  |

The data have the format of a fixed-point number with 16 integer and 8 fractional digits:

Table 13: Data format

| 23 8           | 7 0              | A.D.                                                                  |

|----------------|------------------|-----------------------------------------------------------------------|

| Н              | B1 etc.          | HB1 = Mult $\times \frac{\Delta R}{R} \times 10^6$ = Re gister1 ÷ 256 |

| 16 Bit integer | 8 Bit fractional | IX.                                                                   |

#### Content Register STAT (Status register):

**DBStat** Shows in Double-bridge mode the no. of the bridge actually measured

TMP Temperature value is valid

HB2 Value of 2nd halfbridge is valid

HB1 Value of first halfbridge is valid

Error DSP TDC and DSP collided during RAM access. Increase MFake or use Single conversion

TimoHB1 There was a time-out during the last measurement of halfbridge 1

TimoHB2 There was a time-out during the last measurement of halfbridge 2

TimoTMP There was a time-out during the last measurement of temperature

#### Register Reg 0

This register is the mirror image of write register O. It can be used for testing the communication by the SPI interface.

#### Register TDC1

This register represent the result of the time measurement and therefore of the discharge time.

#### Measurement range 2:

The time interval is given in multiples of the reference clock.

Table 14: Data format

|                                 | 23 0 | τ = TDC1 x Tref x 2^ClkHSDiv           |

|---------------------------------|------|----------------------------------------|

|                                 | TDC1 | = register4/65536 x Tref x 2^ClkHSDiv  |

| 8 Bit integer 16 Bit fractional |      | - register4/ 00000 x frei x 2 cikhodiv |

The TDC1 value is given as fixed-point number with 8 integer and 16 fractional digits, therefore the 24 Bit integer register content must be divided by  $2^{16}$ .

#### Measurement range 1:

The time interval is given in multiples of the TDC resolution (LSB).

Table 15: Data format

| 23 0 | τ ≈ TDC1 * 30 ps (Normal resolution)          |  |

|------|-----------------------------------------------|--|

| TDC1 | $\tau \approx TDC1 * 15 ps (High resolution)$ |  |

The resolution of the TDC depends on temperature and supply voltage. The values given are only typical ones at 5 V and  $25^{\circ}$ C Tamb.

#### Register TDC2

In measurement range 2 this register gives the period of the calibration clock in 8-fold multiples of the resolution. As the period is known, e.g. 250 ns with a 4 MHz clock, the resolution of the internal TDC can be calculated:

#### 2.9 Recommended Modifications to the Default Values

$$resolution = \frac{T_{ref} * 2^{ClkHSDiv}}{TDC2 * 8}$$

Table 16: Data format

| 23 0 | τ ≈ TDC2 * 8 * 30 ps (Normal resolution)          |

|------|---------------------------------------------------|

| TDC2 | $\tau \approx TDC2 * 8 * 15 ps (High resolution)$ |

#### Register RD1 and RD2

These registers can be used to optimize the settling behavior of the Rdson compensation. It is possible to read these data after a measurement and to write them back into registers RD1 and RD2 with the next configuration of the  $PS\emptyset 21$ .

#### 2.9 Recommended Modifications to the Default Values

It is possible to have good measuring results already with the default settings. We recommend the following modifications to the default settings to get the best possible measurement quality.

| Register Name | Bits              | Default | Recommended value            |

|---------------|-------------------|---------|------------------------------|

| PSØ21_Adjust1 | Reg10, Bits 16-21 | 'dec17  | 'dec17; 'dec29; 'dec45 * * * |

| Cal_Adjust    | Reg10, Bits 8-14  | 'decO   | 'dec63                       |

- \*\*\* 'dec 17 (default) is generally recommended and shows good results in all operating modes. In the two following exceptional cases modifications might improve the results:

- a. At high AVRate (>20) 'dec45 might give better results. At AVRAten < 20 'dec45 should not be used.

- b. At high AVRate (>20) and low Vcc-Core (<2.5V) it is better to use 'dec29 instead of 'dec45.

3.1 Measuring Task

#### 3. General Introduction

#### 3.1 Measuring Task

Metal strain gauges (SG) change their value with mechanical deformation, especially a variation in length. The strain  $\epsilon$  designates the relative variation in length of the strain gauge:

Strain(

$$\varepsilon$$

) =  $\frac{\Delta L}{L}$  [1].

Common strain gauges have a maximum strain of typical

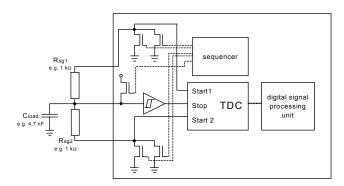

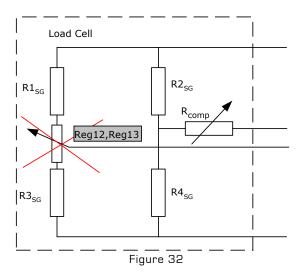

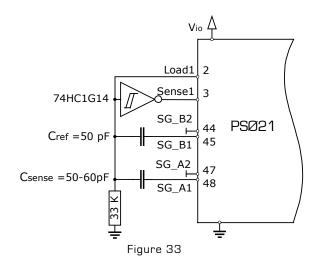

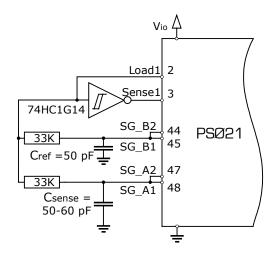

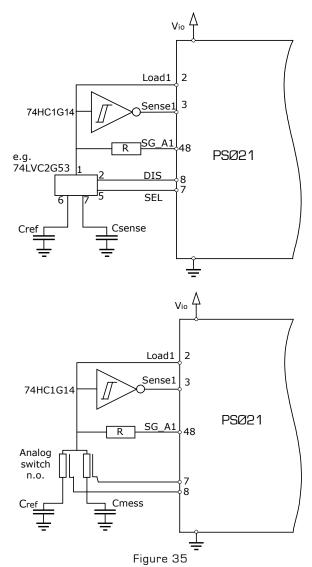

$$\varepsilon_{\text{max}} = 1000 \,\mu \, [1000 \,x \, 10^{-6} \, \text{or} \, 0.1 \,\%].$$