# 82C54

# CMOS Programmable Interval Timer

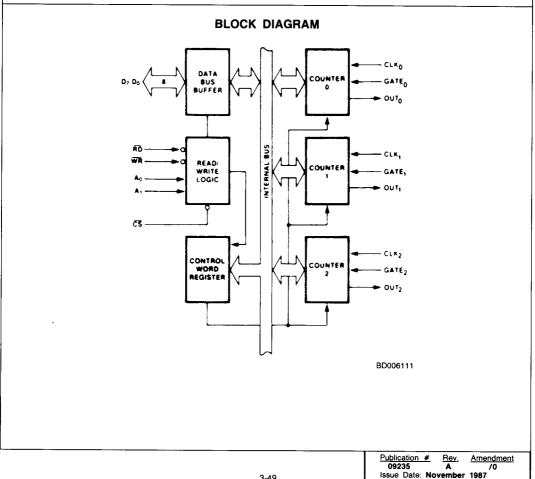

The AMD 82C54 is a high-performance, CMOS version of the industry-standard 8254 counter/timer which is designed to solve the timing-control problems common in microcomputer system design. It provides three independent 16-bit Counters—each capable of handling clock inputs up to 12.5 MHz. All modes are software-programmable. The 82C54 is pin-compatible with the NMOS 8254 and is a superset of the 8253.

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## FOR REFERENCE ONLY

# <u>82C54</u>

CMOS Programmable Interval Timer

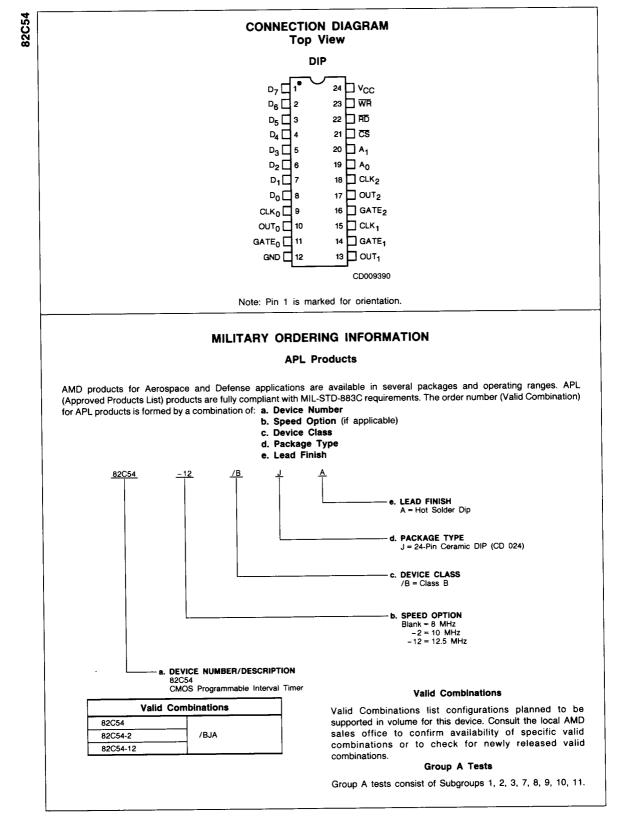

### MILITARY INFORMATION

### DISTINCTIVE CHARACTERISTICS

- · Compatible with all Intel and most other microprocessors

- High-speed, zero-wait-state operation with 10-MHz 8086/88 and 80186/188

- Three independent 16-bit counters

- Handles inputs from DC to 8 MHz .

- 10 MHz for 82C54-2

- 12.5 MHz for 82C54-12

- Low-power CMOS

- I<sub>CC</sub> = 50 μA military standby current I<sub>CC</sub>

- Completely TTL compatible

- Six programmable counter modes

- Binary or BCD counting

- Status read-back command

- Available in 24-pin DIP

### **GENERAL DESCRIPTION**

The AMD 82C54 is a high-performance, CMOS version of the industry-standard 8254 counter/timer which is designed to solve the timing-control problems common in microcomputer system design. It provides three independent 16-bit Counters - each capable of handling clock inputs up to 12.5 MHz. All modes are software-programmable. The 82C54 is pin-compatible with the NMOS 8254 and is a superset of the 8253.

Six programmable-timer modes allow the 82C54 to be used as an event counter, elapsed time indicator, programmable one-shot, and in many other applications as well,

The 82C54 is fabricated with AMD's CMOS technology providing low-power consumption with performance equal to or greater than the equivalent NMOS product. The 82C54 is available in 24-pin DIP package.

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature | 65  | to | + 150°C |

|---------------------|-----|----|---------|

| Voltage on Any Pin  |     |    |         |

| with Respect to GND | 0.5 | to | +7.0 V  |

| Power Dissipation   |     |    | 1 W     |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Military | (M) | Devices |  |

|----------|-----|---------|--|

| -        |     |         |  |

Temperature (T<sub>C</sub>).....-55 to +125°C Supply Voltage (V<sub>CC</sub>) ......5 V ±10%

Operating ranges define those limits between which the functionality of the device is guaranteed.

| DC CHARACTERISTICS ove  | operating rai | ange (for APL | Products, | Group A, | Subgroups | 1, 2, 3 a | are tested |

|-------------------------|---------------|---------------|-----------|----------|-----------|-----------|------------|

| unless otherwise noted) |               |               |           |          | •         |           |            |

| Parameter<br>Symbol                         | Parameter<br>Description                 | Test Condition                                                                | Min.     | Max.            | Uni                    |       |     |

|---------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------|----------|-----------------|------------------------|-------|-----|

| VIL                                         | Input LOW Voltage                        |                                                                               | -0.5*    | 0.8             | V                      |       |     |

| VIH                                         | Input HIGH Voltage                       |                                                                               | 2        | 2.2             | V <sub>CC</sub> +0.5 V | • v   |     |

| VOL                                         | Output LOW Voltage                       | $I_{OL} = 2.0 \text{ mA}$                                                     |          | 1               | .45                    | v     |     |

| VOH                                         | Output HIGH Voltage                      | $I_{OH} = -400 \ \mu A$                                                       | 6-2      | 2.4             |                        | v     |     |

| ηL                                          | Input Load Current                       | VIN = VCC to 0 V                                                              |          |                 | ± 10                   | μA    |     |

| IOFL                                        | Output Float Leakage<br>Current          | V <sub>OUT</sub> = V <sub>CC</sub> to 0 V                                     |          |                 | ± 10                   | μA    |     |

| ICC Operating Power-Sup<br>Current (Note 1) |                                          |                                                                               | 8 MHz    |                 | 20                     |       |     |

|                                             |                                          | CLK Freq                                                                      | 10 MHz   |                 | 20                     | -  m/ |     |

|                                             |                                          |                                                                               | 12.5 MHz |                 | 20                     | 1     |     |

| ICCSB                                       | Standby Power-Supply<br>Current (Note 2) | CLK 7905 DC,<br>CS = RodH,<br>VL Inpos/Data Bus HIGH,<br>All Dutputs Floating |          |                 | ±50                    | μА    |     |

|                                             | <b>NCE</b> (T <sub>C</sub> = 25°C, Voc   | GND = 0 V)                                                                    |          | - <u>+</u>      |                        |       |     |

| Symbol                                      | Description                              | Test Conditions                                                               | s        | Min.            | Max.                   | Units |     |

| C <sub>IN †</sub>                           | Input Capacitance                        | fc = 1 MHZ<br>Unmeasured pins<br>returned to GND                              |          |                 | 10*                    | pF    |     |

| CI/0 †                                      | I/O Capacitance                          |                                                                               |          |                 | 20*                    | pF    |     |

| COUT †                                      | Output Capacitance                       |                                                                               |          | returned to GND |                        |       | 20* |

\* Guaranteed by design; not tested.

See Section 6 of the MOS Microprocessors and Peripherals Data Book (Order #09067A) for Thermal Characteristics Information.

† Not included in Group A tests.

Notes: 1. ICC is measured in a dynamic condition with no output loads applied and inputs at rail levels.

2. Standby ICC is measured in a static condition (CLK = DC) with no output loads applied, and CS and all inputs/ databus at the V<sub>CC</sub> rail level.

3-51

SWITCHING CHARACTERISTICS over operating range (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted) (Note 1).

| Parameter  |                  | 8 MHz                               |      | 10 MHz |      | 12.5 MHz |      |      |      |

|------------|------------------|-------------------------------------|------|--------|------|----------|------|------|------|

| No. Symbol |                  | Parameter Description               | Min. | Max.   | Min. | Max.     | Min. | Max. | Unit |

| READ C     | YCLE             |                                     |      |        |      |          |      | •    | ·    |

| 1          | t <sub>AR</sub>  | Address Stable Before RD            | 45   |        | 30   |          | 25   |      | ns   |

| 2          | tSR              | CS Stable Before RD ↓               | 0    |        | 0    |          | 0    |      | ns   |

| 3          | t <sub>RA</sub>  | Address Hold Time After RD 1        | 0    |        | 0    |          | 0    |      | ns   |

| 4          | t <sub>RR</sub>  | RD Pulse Width                      | 150  |        | 95   |          | 90   |      | ns   |

| 5          | t <sub>RD</sub>  | Data Delay from RD ↓                |      | 120    |      | 85       |      | 80   | ns   |

| 6          | tAD              | Data Delay from Address             |      | 220    |      | 185      |      | 150  | ns   |

| 7          | t <sub>DF</sub>  | RD to Data Floating                 | 5    | 90     | 5    | 65       | 5    | 55   | ns   |

| 8          | t <sub>RV</sub>  | Command Recovery Time               | 200  |        | 165  |          | 135  |      | ns   |

| WRITE (    | CYCLE            |                                     | -    |        |      |          |      |      |      |

| 9          | t <sub>AW</sub>  | Address Stable Before WR            | 0    |        |      |          | 0    |      | ns   |

| 10         | tsw              | CS Stable Before WR ↓               | 0    |        |      |          | 0    |      | ns   |

| 11         | twa              | Address Hold Time After WR          | 0    | X      | 0    |          | 0    |      | ns   |

| 12         | tww              | WR Pulse Width                      |      |        | 95   |          | 80   |      | ns   |

| 13         | tDW              | Data Setup Time Before WR 1         |      |        | 95   |          | 80   |      | ns   |

| 14         | t <sub>WD</sub>  | Data Hold Time After WR             | 0    |        | 0    |          | 0    |      | ns   |

| 15         | t <sub>RV</sub>  | Command Recovery Time               | 200  |        | 165  |          | 135  |      | ns   |

| CLOCK      | AND GATE CY      | 'CLE                                |      | •      |      |          |      |      |      |

| 16         | <sup>t</sup> CLK | Clock Period                        | 125  | DC     | 100  | DC       | 80   | DC   | ns   |

| 17         | t <sub>PWH</sub> | HIGH Pulse Width (Nine 3)           | 60   |        | 30   |          | 30   |      | ns   |

| 18         | tPWL             | LOW Pulse Width Note 3)             | 60   |        | 50   |          | 40   |      | ns   |

| 19         | t <sub>R</sub>   | Clock Rise The Note 4)              |      | 25     |      | 25       |      | 25   | ns   |

| 20         | tF               | Clock call the (Note 4)             |      | 25     |      | 25       |      | 25   | ns   |

| 21         | tGW              | Gate Watch HIGH                     | 50   |        | 50   |          | 40   |      | ns   |

| 22         | t <sub>GL</sub>  | Gate Width LOW                      | 50   |        | 50   | · ··     | 40   |      | ns   |

| 23         | t <sub>GS</sub>  | Gate Setup Time to CLK 1            | 50   |        | 40   |          | 30   |      | ns   |

| 24         | t <sub>GH</sub>  | Gate Hold Time After CLK 1 (Note 2) | 50   |        | 50   |          | 40   |      | ns   |

| 25         | tOD              | Output Delay from CLK ↓             |      | 150    |      | 100      |      | 80   | ns   |

| 26         | todg             | Output Delay from Gate              |      | 120    |      | 100      |      | 80   | ns   |

| 27         | twc              | CLK Delay for Loading               | 0    | 55     | 0    | 55       | 0    | 45   | ns   |

| 28         | twg              | Gate Delay for Sampling             | - 5  | 50     | - 5  | 40       | -5   | 35   | ns   |

| 29         | two              | Out Delay from Mode Write           |      | 260    |      | 240      |      | 200  | ns   |

| 30         | tCL              | CLK Set Up for Count Latch          | - 4  | 45     | - 4  | 40       | -4   | 35   | ns   |

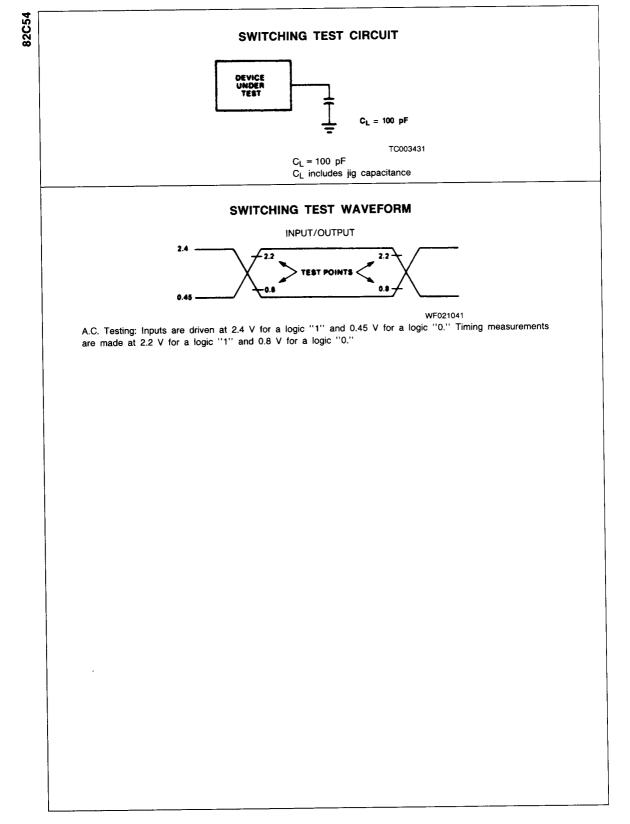

Notes: 1. Timings measured at V<sub>OH</sub> = 2.2 V, V<sub>OL</sub> = 0.8 V. C<sub>L</sub> = 100 pF  $\pm 20$  pF.

In Modes 1 and 5, triggers are sampled on each rising clock edge. A second trigger within 120 ns (70 ns for the 82C54-2) of the rising clock edge may not be detected.

3. LOW-going glitches that violate tPWH, tPWL may cause errors requiring Counter re-programming.

4. Clock rise and fall times are tested at 5 ns, guaranteed by Teradyne J941 test equipment.