Advance Information

MCF5485EC/D Rev. 1.2, 3/2004

MCF548x Integrated Microprocessor Hardware Specifications

The MCF548x is a highly-integrated implementation of the ColdFire<sup>®</sup> family of reduced instruction set computing (RISC) microprocessors. This document describes pertinent electrical and physical characteristics of the MCF548x family: the MCF5480, MCF5481, MCF5482, MCF5483, MCF5484, and MCF5485.

This document contains the following topics:

| Topic                                                | Page |

|------------------------------------------------------|------|

| Section 1.1, "MCF548x Family Overview"               | 1    |

| Section 1.2, "MCF548x Block Diagram"                 | 3    |

| Section 1.3, "MCF548x Family Products"               | 4    |

| Section 1.4, "MCF548x Family Features"               | 5    |

| Section 1.5, "Signal Description"                    | 14   |

| Section 1.6, "Chip Configuration"                    | 43   |

| Section 1.7, "Design Recommendations"                | 45   |

| Section 1.8, "MCF5485/5484 Pinout"                   | 54   |

| Section 1.9, "MCF5483/5482 Pinout"                   | 58   |

| Section 1.10, "MCF5481/5480 Pinout"                  | 62   |

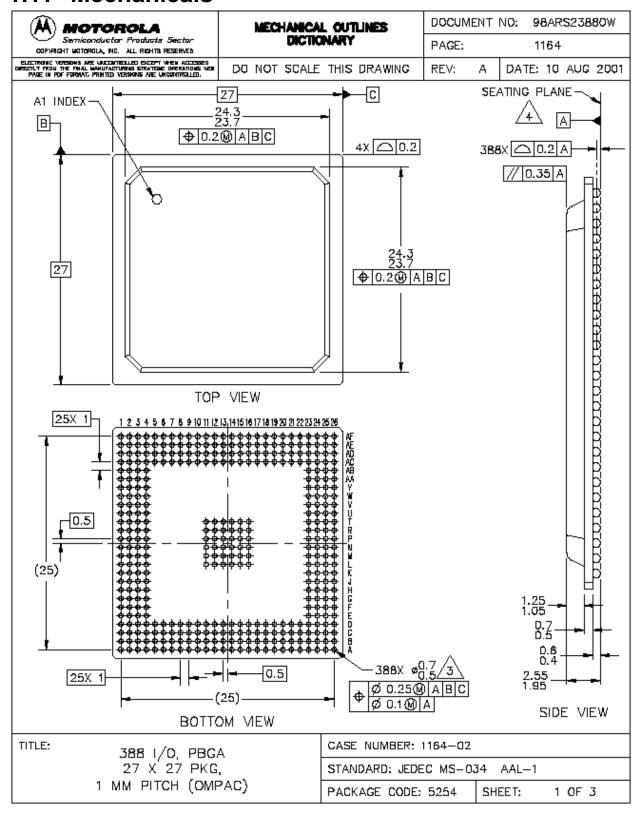

| Section 1.11, "Mechanicals"                          | 67   |

| Section 1.12, "Ordering Information"                 | 68   |

| Section 1.13, "Device/Family Documentation List"     | 68   |

| Section 1.14, "Document Revision History"            | 68   |

| Appendix A, "Preliminary Electrical Characteristics" | 69   |

To locate any published errata or updates for this document, refer to the web site at http://motorola.com/semiconductors.

# 1.1 MCF548x Family Overview

The MCF548x family is based on the ColdFire V4e core, a complex which comprises the ColdFire V4 central processor unit (CPU), an enhanced multiply-accumulate unit (EMAC), a memory management unit (MMU), a double-precision floating point unit (FPU) conforming to standard IEEE-754, and controllers for caches and local data memories. The MCF548x family is capable of performing at an operating frequency of up to 200 MHz or 308 MIPS (Dhrystone 2.1).

#### MCF548x Family Overview

To maximize throughput, the MCF548x family incorporates three independent external bus interfaces:

- 1. The general-purpose local bus (FlexBus) is used for system boot memories and simple peripherals and has up to six chip selects.

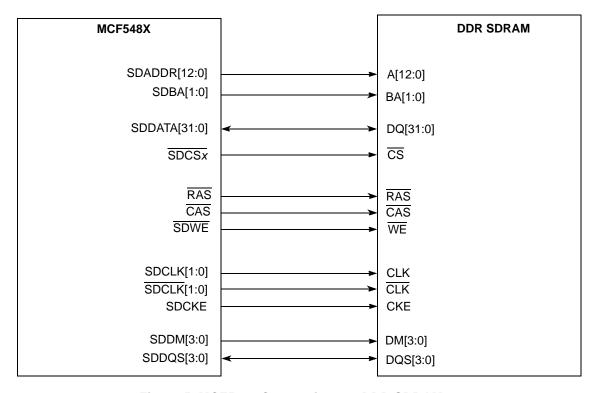

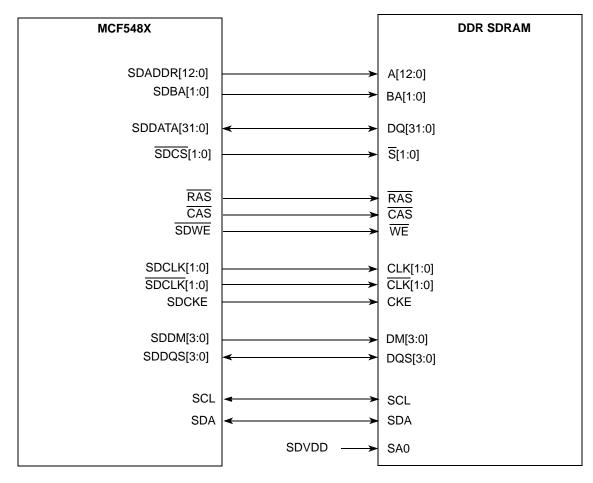

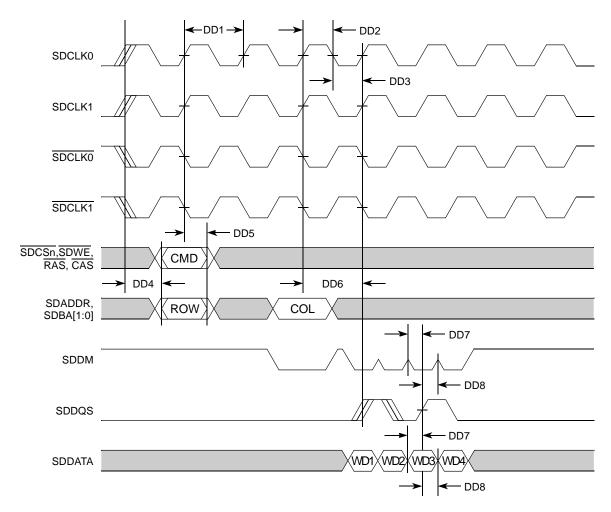

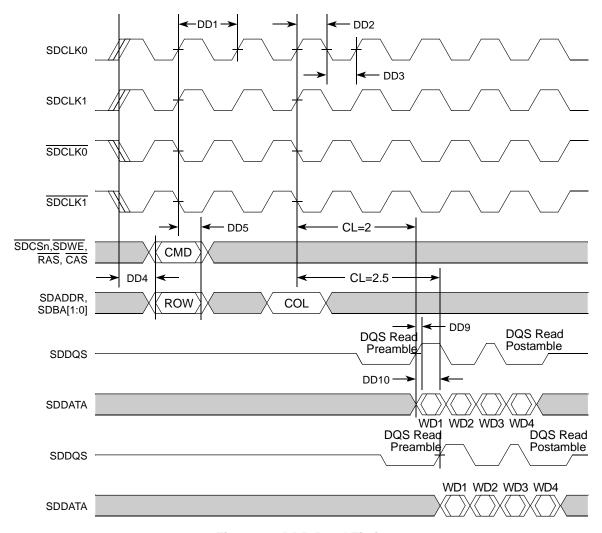

- 2. Program code and data can be stored in SDRAM connected to a dedicated 32-bit double data rate (DDR) bus that can run at up to one half of the CPU core frequency. The glueless DDR SDRAM controller handles all address multiplexing, input and output strobe timing, and memory bus clock generation.

- 3. A 32-bit PCI bus compliant with the version 2.2 specification and running at a typical frequency of 33 MHz or 66 MHz supports peripherals that require high bandwidth, the ability to arbitrate for bus mastership, and access to internal MCF548x memory resources.

The MCF548x family provides substantial communications functionality by integrating the following connectivity peripherals:

- Up to two 10/100 Mbps fast Ethernet controllers (FECs)

- An optional USB 2.0 device (slave) module with seven endpoints and an integrated transceiver

- Up to four UART/USART/IRDA/modem programmable serial controllers (PSCs)

- A DMA serial peripheral interface (DSPI)

- An inter-integrated circuit ( $I^2C^{TM}$ ) bus controller

- Two controller area network 2.0B (FlexCAN) interfaces with 16 message buffers each

Additionally, the MCF548x provides hardware support for a range of Internet security standards with an optional bus-mastering cryptography accelerator. This module incorporates units to speed DES/3DES and AES block ciphers, the RC4 stream cipher, bulk data hashing (MD5/SHA-1/SHA-256/HMAC), and random number generation. Hardware acceleration of these functions is critical to avoiding the throughput bottlenecks associated with software-only implementations of SSH, SSL/TLS, IPsec, SRTP, WEP, and other security standards. The incorporation of cryptography acceleration makes the MCF548x family a compelling solution for a wide range of office automation, industrial control, and SOHO networking devices that must have the ability to securely transmit critical equipment control information across typically insecure Ethernet data networks.

Additional features of MCF548x products include a watchdog timer, two 32-bit slice timers for RTOS scheduling and alarm functionality, up to four 32-bit general-purpose timers with capture, compare, and pulse width modulation capability, a multisource vectored interrupt controller, a phase-locked loop (PLL) to generate the system clock, 32 Kbytes of SRAM for high-speed local data storage, and multiple general-purpose I/O ports. To manage current consumption, MCF548x products provide chip-wide internal clock gating control on a per module basis under software control.

With on-chip support for multiple common communications interfaces, MCF548x products require only the addition of memories and certain physical layer transceivers to be cost-effective system solutions for many applications, such as industrial routers, high-end POS terminals, building automation systems, and process control equipment.

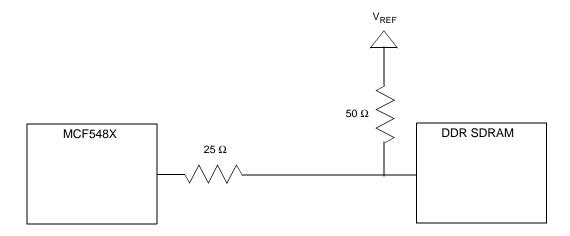

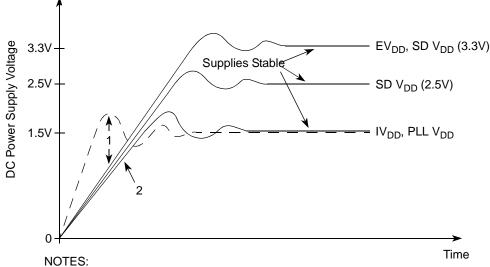

MCF548x products require four supply voltages: 1.5V for the high-performance, low power, internal core logic, 2.5V for the DDR SDRAM bus interface, 1.25V for the DDR SDRAM V<sub>REF</sub>, and 3.3V for all other I/O functionality, including the PCI and FlexBus interfaces.

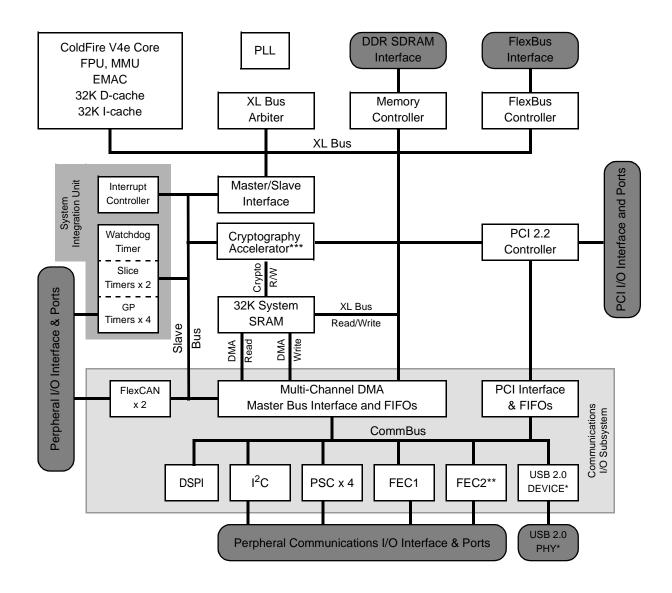

# 1.2 MCF548x Block Diagram

Figure 1 shows a top-level block diagram of the MCF548x products.

<sup>\*</sup>Available in MCF5485, MCF5484, MCF5483, and MCF5482 devices. \*\*Available in MCF5485, MCF5484, MCF5481, and MCF5480 devices.

<sup>\*\*\*</sup>Available in MCF5485, MCF5483, and MCF5481 devices.

Figure 1. MCF548x Block Diagram

# 1.3 MCF548xFamily Products

Table 1 summarizes the products available within the MCF548x product family. All products are available in pin-compatible, 388 pin PBGA packaging allowing for ease of mirgration between products within the family. A printed circuit board designed using the MCF5485/4 footprint is compatible with any of the MCF548x family devices.

Table 1. MCF548x Family Products

| Product | Performance         | Features                                                                                                                                                | Temperature Range |

|---------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| MCF5485 | 308 MIPS<br>200 MHz | Two 10/100 Ethernet Controllers Two CAN Controllers USB 2.0 Device with Integrated PHY v2.2 PCI Controller DDR Memory Controller Encryption Accelerator | -40 to 85 ° C     |

| MCF5484 | 308 MIPS<br>200 MHz | Two 10/100 Ethernet Controllers Two CAN Controllers USB 2.0 Device with Integrated PHY v2.2 PCI Controller DDR Memory Controller                        | -40 to 85 ° C     |

| MCF5483 | 255 MIPS<br>166 MHz | One 10/100 Ethernet Controller Two CAN Controllers USB 2.0 Device with Integrated PHY v2.2 PCI Controller DDR Memory Controller Encryption Accelerator  | -40 to 85 ° C     |

| MCF5482 | 255 MIPS<br>166 MHz | One 10/100 Ethernet Controller Two CAN Controllers USB 2.0 Device with Integrated PHY v2.2 PCI Controller DDR Memory Controller                         | -40 to 85 ° C     |

| MCF5481 | 255 MIPS<br>166 MHz | Two 10/100 Ethernet Controllers Two CAN Controllers v2.2 PCI Controller DDR Memory Controller Encryption Accelerator                                    | -40 to 85 ° C     |

| MCF5480 | 255 MIPS<br>166 MHz | Two 10/100 Ethernet Controllers Two CAN Controllers v2.2 PCI Controller DDR Memory Controller                                                           | -40 to 85 ° C     |

# 1.4 MCF548x Family Features

- ColdFire V4e core

- Limited superscalar V4 ColdFire processor core

- Up to 200 MHz peak internal core frequency (308 Dhrystone 2.1 MIPS)

- Harvard architecture

- 32-Kbyte instruction cache

- 32-Kbyte data cache

- Memory management unit (MMU)

- Separate, 32-entry, fully-associative instruction and data translation lookahead buffers

- Floating point unit (FPU)

- Double-precision support that conforms to IEEE-754 standard

- Eight floating point registers

- Internal master bus (XLB) arbiter

- High performance split address and data transactions

- Support for various parking modes

- 32-bit double data rate (DDR) synchronous DRAM (SDRAM) controller

- 66–133 MHz operation

- Supports both DDR and SDR DRAM

- Built-in initialization and refresh

- Up to four chip selects enabling up to 1 GB of external memory

- Version 2.2 peripheral component interconnect (PCI) bus

- 32-bit target and initiator operation

- Support for up to five external PCI masters

- 33–66 MHz operation with PCI bus to XLB divider ratios of 1:1, 1:2, and 1:4

- Flexible multifunction external bus (FlexBus)

- Supports operation with the following:

- Non-multiplexed 32-bit address and 32-bit data (32-bit address muxed over PCI bus–PCI not usable)

- Multiplexed 32-bit address and 32-bit data (PCI usable)

- Multiplexed 32-bit address and 16-bit data

- Multiplexed 32-bit address and 8-bit data

- Provides a glueless interface to boot Flash/ROM, SRAM, and peripheral devices

- Up to six chip selects

- 33–66 MHz operation

- Communications I/O subsystem

- Intelligent 16-channel DMA controller

- Dedicated DMA channels for receive and transmit on all subsystem peripheral interfaces

#### MCF548x Family Features

- Up to two 10/100 Mbps fast Ethernet controllers (FECs), each with separate 2-Kbyte receive and transmit FIFOs

- Universal serial bus (USB) version 2.0 device controller

- Support for one control and six programmable endpoints interrupt, bulk, or isochronous

- 4 Kbytes of shared endpoint FIFO RAM and 1 Kbyte of endpoint descriptor RAM

- Integrated physical layer interface

- Up to four programmable serial controllers (PSCs) each with separate 512-byte receive and transmit FIFOs for UART, USART, modem, codec, and IrDA 1.1 interfaces

- I<sup>2</sup>C peripheral interface

- Two FlexCAN controller area network 2.0B controllers each with 16 message buffers

- DMA serial peripheral interface (DSPI)

- Optional security encryption controller (SEC) module

- Execution units for the following:

- DES/3DES block cipher

- AES block cipher

- RC4 stream cipher

- MD5/SHA-1/SHA-256/HMAC hashing

- Random number generator compliant with FIPS 140-1 standards for randomness and non-determinism

- Dual-channel architecture permits single-pass encryption and authentication

- 32-Kbyte system SRAM

- Arbitration mechanism shares bandwidth between internal bus masters (CPU, cryptography accelerator, PCI, and DMA)

- System integration unit (SIU)

- Interrupt controller

- Watchdog timer

- Two 32-bit slice timers for periodic alarm and interrupt generation

- Up to four 32-bit general-purpose timers with capture, compare, and PWM capability

- General-purpose I/O ports multiplexed with peripheral pins

- Debug and test features

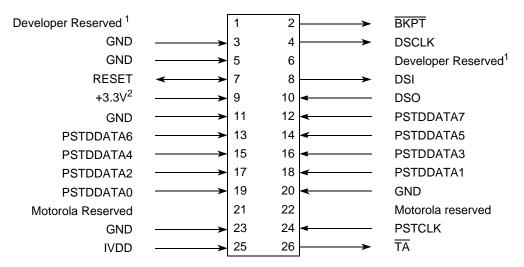

- Core debug support via ColdFire background debug mode (BDM) port

- Chip debug support via JTAG/ IEEE 1149.1 test access port

- PLL and clock generator

- 30–66.67 MHz input frequency range

- Operating Voltages

- 1.5V internal logic

- -2.5V DDR SDRAM bus I/O (1.25V  $V_{REE}$ )

- 3.3V PCI, FlexBus, and all other I/O

- Estimated power consumption

- <1.5W

#### 1.4.1 ColdFire V4e Core Overview

The ColdFire V4e core is a variable-length RISC, clock-multiplied core that includes a Harvard memory architecture, branch cache acceleration logic, and limited superscalar dual-instruction issue capabilities. The limited superscalar design approaches dual-issue performance with the cost of a scalar execution pipeline.

The ColdFire V4e processor core is comprised of two separate pipelines that are decoupled by an instruction buffer. The four-stage instruction fetch pipeline (IFP) prefetches the instruction stream, examines it to predict changes of flow, partially decodes instructions, and packages fetched data into instructions for the operand execution pipeline (OEP). The IFP can prefetch instructions before the OEP needs them, minimizing the wait for instructions. The instruction buffer is a 10 instruction, first-in-first-out (FIFO) buffer that decouples the IFP and OEP by holding prefetched instructions awaiting execution in the OEP. The OEP includes five pipeline stages: the first stage decodes instructions and selects operands (DS), and the second stage generates operand addresses (OAG). The third and fourth stages fetch operands (OC1 and OC2), and the fifth stage executes instructions (EX).

The ColdFire V4e processor contains a double-precision floating point unit (FPU). The FPU conforms to the American National Standards Institute (ANSI)/Institute of Electrical and Electronics Engineers (IEEE) *Standard for Binary Floating-Point Arithmetic* (ANSI/IEEE Standard 754). The FPU operates on 64-bit, double-precision floating point data and supports single-precision and signed integer input operands. The FPU programming model is like that in the MC68060 microprocessor. The FPU is intended to accelerate the performance of certain classes of embedded applications, especially those requiring high-speed floating point arithmetic computations.

The ColdFire V4e processor also incorporates the ColdFire memory management unit (MMU), which provides virtual-to-physical address translation and memory access control. The MMU consists of memory-mapped control, status, and fault registers that provide access to translation lookaside buffers (TLBs). Software can control address translation and access attributes of a virtual address by configuring MMU control registers and loading TLBs. With software support, the MMU provides demand-paged, virtual addressing.

The ColdFire V4e core implements the ColdFire instruction set architecture revision B with support for floating Point instructions. Additionally, the ColdFire V4e core includes the enhanced multiply-accumulate unit (EMAC) for improved signal processing capabilities. The EMAC implements a 4-stage execution pipeline, optimized for 32 x 32 bit operations, with support for four 48-bit accumulators. Supported operands include 16- and 32-bit signed and unsigned integers as well as signed fractional operands and a complete set of instructions to process these data types. The EMAC provides superb support for execution of DSP operations within the context of a single processor at a minimal hardware cost.

### 1.4.2 Debug Module (BDM)

The ColdFire processor core debug interface is provided to support system debugging in conjunction with low-cost debug and emulator development tools. Through a standard debug interface, users can access real-time trace and debug information. This allows the processor and system to be debugged at full speed without the need for costly in-circuit emulators.

The MCF548x debug module provides support in three different areas:

• Real-time trace support: The ability to determine the dynamic execution path through an application is fundamental for debugging. The ColdFire solution implements an 8-bit parallel output bus that reports processor execution status and data to an external BDM emulator system.

#### MCF548x Family Features

- Background debug mode (BDM): Provides low-level debugging in the ColdFire processor complex. In BDM, the processor complex is halted and a variety of commands can be sent to the processor to access memory and registers. The external BDM emulator uses a three-pin, serial, full-duplex channel.

- Real-time debug support: BDM requires the processor to be halted, which many real-time

embedded applications cannot permit. Debug interrupts let real-time systems execute a unique

service routine that can quickly save key register and variable contents and return the system to

normal operation without halting. External development systems can access saved data because

the hardware supports concurrent operation of the processor and BDM-initiated commands. In

addition, the option is provided to allow interrupts to occur.

#### 1.4.3 JTAG

The MCF548x family supports circuit board test strategies based on the Test Technology Committee of IEEE and the Joint Test Action Group (JTAG). The test logic includes a test access port (TAP) consisting of a 16-state controller, an instruction register, and three test registers (a 1-bit bypass register, a 256-bit boundary-scan register, and a 32-bit ID register). The boundary scan register links the device's pins into one shift register. Test logic, implemented using static logic design, is independent of the device system logic. The MCF548x implementation can do the following:

- Perform boundary scan operations to test circuit board electrical continuity

- Sample MCF548x system pins during operation and transparently shift out the result in the boundary scan register

- Bypass the MCF548x for a given circuit board test by effectively reducing the boundary-scan register to a single bit

- Disable the output drive to pins during circuit-board testing

- Drive output pins to stable levels

## 1.4.4 On-Chip Memories

#### 1.4.4.1 Caches

There are two independent caches associated with the ColdFire V4e core complex: a 32-Kbyte instruction cache and a 32-Kbyte data cache. Caches improve system performance by providing single-cycle access to the instruction and data pipelines. This decouples processor performance from system memory performance, increasing bus availability for on-chip DMA or external devices.

# 1.4.4.2 System SRAM

The SRAM module provides a general-purpose 32-Kbyte memory block that the ColdFire core can access in a single cycle. The location of the memory block can be set to any 32-Kbyte address boundary within the 4-Gbyte address space. The memory is ideal for storing critical code or data structures, for use as the system stack, or for storing FEC data buffers. Because the SRAM module is physically connected to the processor's high-speed local bus, it can quickly service core-initiated accesses or memory-referencing commands from the debug module.

The SRAM module is also accessible by multiple non-core bus masters, such as the DMA controller, the encryption accelerator, and the PCI Controller.

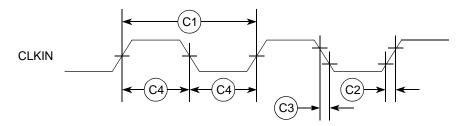

## 1.4.5 PLL and Chip Clocking Options

MCF548x products contain an on-chip PLL capable of accepting input frequencies from 30–66.66 MHz. Table 2 contains the frequencies of the system buses for the members of the MCF548x family under various core/SDRAM/PCI/Flexbus clocking options.

**Table 2. MCF548x Family Clocking Options**

| Core<br>(MHz) | Internal XLB and SDRAM Bus Frequency (MHz) | CLKIN—PCI and FlexBus<br>Frequency<br>(MHz) | Clock Ratio |

|---------------|--------------------------------------------|---------------------------------------------|-------------|

| 120.0–200     | 60.0–100                                   | 30.0–50.0                                   | 1:2         |

## 1.4.6 Communications I/O Subsystem

#### 1.4.6.1 DMA Controller

The communications subsystem contains an intelligent DMA unit that provides front line interrupt control and data movement interface via a separate peripheral bus to the on-chip peripheral functions, leaving the processor core free to handle higher level activities. This concurrent operation enables a significant boost in overall system performance.

The communications subsystem can support up to 16 simultaneously enabled DMA tasks, with support for up to 2 external DMA requests. It uses internal buffers to prefetch reads and post writes such that bursting is used whenever possible. This optimizes both internal and external bus activity. The following communications and computer control peripheral functions are integrated and controlled by the communications subsystem:

- Up to two 10/100 Mbps fast Ethernet controllers (FECs)

- Optional universal serial bus (USB) version 2.0 device controller

- Up to four programmable serial controllers (PSCs)

- I<sup>2</sup>C peripheral interface

- DMA serial peripheral interface (DSPI)

- Two FlexCAN controller area network 2.0B controllers

### 1.4.6.2 10/100 Fast Ethernet Controller (FEC)

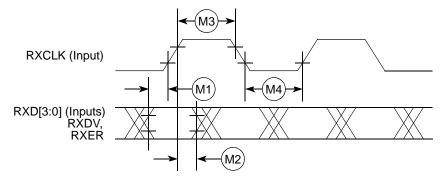

The FEC supports the following standard MAC/PHY interfaces: 10/100 Mbps IEEE 802.3 MII, and 10Mbps 7-wire interface. The controller is full duplex, supports a programmable maximum frame length and retransmission from the transmit FIFO following a collision.

Support for different Ethernet physical interfaces:

- 100 Mbps IEEE 802.3 MII

- 10 Mbps IEEE 802.3 MII

- 10 Mbps 7-wire interface

- IEEE 802.3 full-duplex flow control.

- Support for full-duplex operation (200 Mbps throughput) with a minimum system clock frequency of 50 MHz.

#### MCF548x Family Features

- Support for half duplex operation (100 Mbps throughput) with a minimum system clock frequency of 25 MHz.

- Retransmit from transmit FIFO following collision.

- Internal loopback for diagnostic purposes.

#### 1.4.6.3 USB 2.0 Device (Universal Serial Bus)

The USB module implementation on the MCF548x product family provides all the logic necessary to process the USB protocol as defined by version 2.0 specification for peripheral devices.

- High-speed operation up to 480 Mbps, full-speed operation at 12 Mbps, and low-speed operation at 1.5 Mbps

- Physical interface on chip

- Bulk, interrupt, and isochronous transport modes.

- Six programmable in/out endpoints and one control endpoint

- 4 Kbytes of shared endpoint FIFO RAM and 1 Kbyte of endpoint descriptor RAM

#### 1.4.6.4 Programmable Serial Controllers (PSCs)

The MCF548x product family supports four PSCs that can be independently configured to operate in the following modes:

- Universal asynchronous receiver transmitter (UART) mode

- 5,6,7,8 bits of data plus parity

- Odd, even, none, or force parity

- Stop bit width programmable in 1/16 bit increments

- Parity, framing, and overrun error detection

- Automatic PSCCTS and PSCRTS modem control signals

- IrDA 1.0 SIR mode (SIR)

- Baud rate range of 2400–115200 bps

- Selectable pulse width: either 3/16 of the bit duration or 1.6 μs

- IrDA 1.1 MIR mode (MIR)

- Baud rate of 0.576 or 1.152 Mbps

- IrDA 1.1 FIR mode (FIR)

- Baud rate of 4.0 Mbps

- 8-bit soft modem mode (modem8)

- 16-bit soft modem mode (modem16)

- AC97 soft modem mode (AC97)

Each PSC supports synchronous (USART) and asynchronous (UART) protocols. The PSCs can be used to interface to external full-function modems or external codecs for soft modem support, as well as IrDA 1.1 or 1.0 interfaces. Both 8- and 16-bit data widths are supported. PSCs can be configured to support 1200 baud plain old telephone system (POTS) modem, V.34 or V.90 protocols. The standard UART interface supports connection to an external terminal/computer for debug support.

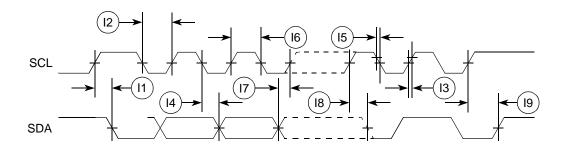

# 1.4.6.5 I<sup>2</sup>C (Inter-Integrated Circuit)

The MCF548x product family provides an I<sup>2</sup>C two-wire, bidirectional serial bus for on-board communication.

- Multimaster operation with arbitration and collision detection

- Calling address recognition and interrupt generation

- Automatic switching from master to slave on arbitration loss

- Software-selectable acknowledge bit

- Start and stop signal generation and detection

- Bus busy status detection

#### 1.4.6.6 DMA Serial Peripheral Interface (DSPI)

The DSPI block operates as a basic SPI block with FIFOs providing support for external queue operation. Data to be transmitted and data received reside in separate FIFOs. The FIFOs can be popped and pushed by host software or by the system DMA controller. The DSPI supports these SPI features:

- Full-duplex, three-wire synchronous transfers

- Master and slave mode—two peripheral chip selects in master mode

- DMA support

### 1.4.6.7 Controller Area Network (CAN)

The FlexCAN modules are communication controllers implementing the CAN protocol. The CAN protocol can be used as an industrial control serial data bus, meeting the specific requirements of real-time processing and reliable operation in a harsh EMI environment, while maintaining cost-effectiveness. Each of the two CAN controllers on the MCF548x family products contains sixteen message buffers. The CAN controllers can be configured to either function as an interface with two separate CAN networks, or as a single 32 message buffer CAN network.

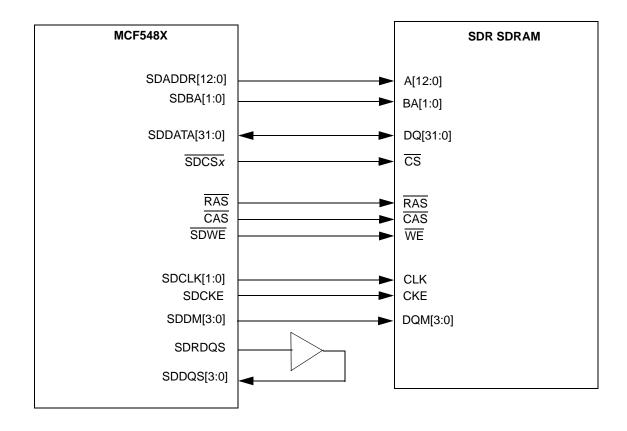

## 1.4.7 DDR SDRAM Memory Controller

The DDR SDRAM memory controller is a glueless interface to DDR memories. The module uses a 32 bit memory port and can address a maximum of 1 Gbyte of data with sixteen 64M x 8 (512-Mbit) devices, 4 per chip select. The controller supplies two clock lines and respective inverted clock lines to help minimize system complexity when using DDR. The module supports either DDR or SDR but not both. This is due to voltage differences between the memory technologies. The supported memory clock rate is up to 133 MHz. At this memory clock rate, DDR memory can receive data at an effective rate of up to 266 MHz.

- Support for up to 13 lines of row address, 11 lines of column address, 2 lines of bank address, and up to 4 chip selects

- Memory bus width fixed at 32 bits

- Four chip selects support up to 1 GByte of SDRAM memory

- Support for page mode to maximize the data rate. Page mode remembers active pages for all four chip selects

- Support for sleep mode and self refresh

#### MCF548x Family Features

• Cache line reads that can use critical word first. These reads can start in the center of a burst and will wrap to the beginning. This allows the processor quicker access to a needed instruction.

All on-chip bus masters have access to DRAM. This includes PCI, the ColdFire V4e core, the cryptography accelerator, and the DMA controller.

## 1.4.8 Peripheral Component Interconnect (PCI)

The PCI controller is a PCI V2.2-compliant bus controller and arbiter. The PCI bus is capable of 66-MHz operation with a 32-bit address/data bus and support for five external masters.

The PCI module includes an inbound FIFO to increase performance when using an external bus master. The bus can address all 4 Gbytes of PCI-addressable space.

The PCI bus is also multiplexed with the flexible local bus (FlexBus) address lines. If 32-bit non-muxed local address and data is required it can be obtained at the expense of utilizing the PCI bus.

When implemented, the PCI controller acts as the central resource, bus arbiter, and configuring master on the PCI bus.

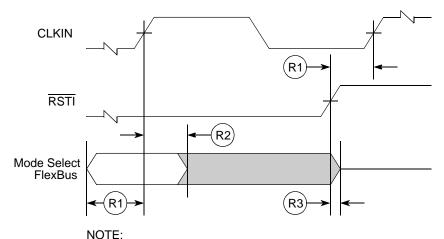

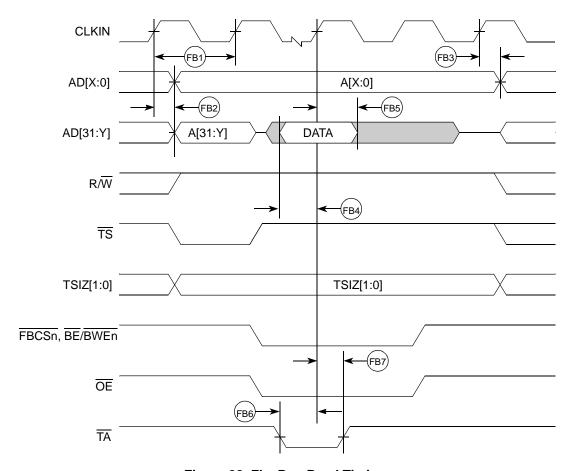

# 1.4.9 Flexible Local Bus (FlexBus)

The FlexBus module is intended to provide the user with basic functionality required to interface to peripheral devices. The FlexBus interface is a multiplexed or non-multiplexed bus, with an operating frequency from 33–66 MHz. The Flexbus is targeted to support external Flash memories, boot ROMs, gate-array logic, or other simple target interfaces. Up to six chip selects are supported by the FlexBus.

Possible combinations of address and data bits are:

- Non-multiplexed 32-bit address and 32-bit data (32-bit address muxed over PCI bus–PCI not usable)

- Multiplexed 32-bit address and 32-bit data (PCI usable)

- Multiplexed 32-bit address and 16-bit data

- Multiplexed 32-bit address and 8-bit data

The non-multiplexed 32-bit address and 32-bit data mode is determined at chip reset. For all other modes, the full 32-bit address is driven during the address phase. The number of bytes used for data are determined on a chip select by chip select basis.

## 1.4.10 Security Encryption Controller (SEC)

As consumers and businesses continue to embrace the Internet, the need for secure point-to-point communications across what is an entirely insecure network has been met by the development of a range of standard protocols. Computer cryptography fundamentally involves calculations with very large numbers. Personal computers have sufficient processing power to implement these algorithms entirely in software. When placed upon the embedded devices typically used for routing and remote access functions, this same computational burden can potentially decrease the throughput of a 100 Mbps Ethernet interface down to 10 Mbps.

Hardware acceleration of common cryptography algorithms is the solution to the computational bandwidth requirements of Internet security standards. Discrete solutions currently address this problem, but the next

logical step is to integrate a cryptography accelerator on an embedded processor, such as the MCF548x family.

Motorola has developed the SEC on the MCF548x family for this purpose. This block accelerates the core cryptography algorithms that underlie standard Internet security protocols like SSL/TLS, IPSec, IKE, and WTLS/WAP.

- The SEC includes execution units for the following:

- DES/3DES block cipher

- AES block cipher

- RC4 stream cipher

- MD5/SHA-1/SHA-256/HMAC hashing

- Random number generator compliant with FIPS 140-1 standards for randomness and non-determinism

- Dual-channel architecture permits single-pass encryption and authentication

# 1.4.11 System Integration Unit (SIU)

#### 1.4.11.1 Timers

The MCF548x family integrates several timer functions required by most embedded systems. Two internal 32-bit slice timers are provided to create short cycle periodic interrupts, typically utilized for RTOS scheduling and alarm functionality. A watchdog timer is included which will reset the processor if not regularly serviced, catching software hang-ups. Four 32-bit general purpose timers are included, which are capable of input capture, output compare, and PWM functionality.

### 1.4.11.2 Interrupt Controller

The interrupt controller on the MCF548x family can support up to 63 interrupt sources. The interrupt controller is organized as seven levels with nine interrupt sources per level. Each interrupt source has a unique interrupt vector, and 56 of the 63 sources of a given controller provide a programmable level [1-7] and priority within the level.

- Support for up to 63 interrupt sources organized as follows:

- 56 fully-programmable interrupt sources

- 7 fixed-level interrupt sources

- Seven external interrupt signals

- Unique vector number for each interrupt source

- Ability to mask any individual interrupt source or all interrupt sources (global mask-all)

- Support for hardware and software interrupt acknowledge (IACK) cycles

- Combinatorial path to provide wake-up from low power modes

### 1.4.11.3 General Purpose I/O

All peripheral I/O pins on the MCF548x family are muxed with GPIO, adding flexibility and usability to all signals on the chip.

# 1.5 Signal Description

Table 3 lists the signals for the MCF548x in functional group order.

#### NOTE

In this table and throughout this document, a single signal within a group is designated without square brackets (for example, AD24), while designations for multiple signals within a group use bracketed numbers separated by a colon (for example, AD[31:0]).

Table 3. MCF548x Signal Description

| PBGA Pin                                     |                   | Pin Fund   | ctions     |          | - Description                | I/O   | Drive | Reset |

|----------------------------------------------|-------------------|------------|------------|----------|------------------------------|-------|-------|-------|

| PBGA FIII                                    | Primary           | GPIO       | Secondary  | Tertiary | Description                  | 1/0   | Dilve | State |

|                                              |                   |            | FlexBus    | 3        |                              |       | •     |       |

| AE2, AF3, AF1,<br>AE3, AE4, AD5,<br>AF2, AD4 | AD[31:24]         | _          | _          | _        | Multiplexed address/data bus | I/O   | 16    | Hi-Z  |

| AD3, AC3, AD2,<br>AC2, AA4, AE1,<br>AC1, AD1 | AD[23:16]         | _          | _          | _        | Multiplexed address/data bus | I/O   | 16    | Hi-Z  |

| AB2, AA3, W4,<br>AB1, AA2, AA1,<br>Y1, Y2    | AD[15:8]          | _          | _          | _        | Multiplexed address/data bus | I/O   | 16    | Hi-Z  |

| W3, W1, W2, V3,<br>V1, V2, T4, U3            | AD[7:0]           | _          | _          | _        | Multiplexed address/data bus | I/O   | 16    | Hi-Z  |

| R1, T2, T3, T1, U2                           | FBCS[5:1]         | PFBCS[5:1] | _          | _        | Chip selects 5–1             | O:I/O | 24    | High  |

| U1                                           | FBCS0             | _          | _          | _        | Chip select 0                | 0     | 24    | High  |

| AD6                                          | TS                | PFBCTL0    | TBST       | _        | Transfer start               | O:I/O | 16    | High  |

| AE5                                          | R/W               | PFBCTL2    | TBST       | _        | Read/write                   | 0     | 16    | Hi-Z  |

| AF4,                                         | BE/BWE3           | PFBCTL7    | TSIZ1      | _        | Byte enables                 | O:I/O | 16    | High  |

| AF5                                          | BE/BWE2           | PFBCTL6    | TSIZ0      | _        | Byte enables                 | O:I/O | 16    | High  |

| AC4                                          | BE/BWE1           | PFBCTL5    | FBADDR1    | _        | Byte enables                 | O:I/O | 16    | High  |

| AE7                                          | BE/BWE0           | PFBCTL4    | FBADDR0    | _        | Byte enables                 | O:I/O | 16    | High  |

| AE6                                          | ŌĒ                | PFBCTL3    | _          | _        | Output enable                | I/O   | 16    | High  |

| AF6                                          | TA                | PFBCTL1    | _          | _        | Transfer<br>acknowledge      | I:I/O | 16    | _     |

|                                              |                   |            | SDRAM Cont | roller   |                              | -     |       |       |

| C10, B9, A8, D5,<br>A6, C8, B7, A5           | SDDATA[31:2<br>4] | _          | _          | _        | SDRAM data bus               | I/O   | 24    | Hi-Z  |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices.

<sup>&</sup>lt;sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| PBGA Pin                                                              |                   | Pin Fund | ctions         |          | - Description               | I/O | Drive | Reset |

|-----------------------------------------------------------------------|-------------------|----------|----------------|----------|-----------------------------|-----|-------|-------|

| FBGAFIII                                                              | Primary           | GPIO     | Secondary      | Tertiary | Description                 | 1/0 | Dilve | State |

| A4, C7, B6, B4,<br>C5, B3, C4, D4                                     | SDDATA[23:1<br>6] | _        | _              | _        | SDRAM data bus              | I/O | 24    | Hi-Z  |

| E2, D1, G4, E1,<br>K4, F1, G2, H3                                     | SDDATA[15:8       | _        | _              | _        | SDRAM data bus              | I/O | 24    | Hi-Z  |

| N4, G1, H2, J3, J1,<br>M4, K3, K2                                     | SDDATA[7:0]       | _        | _              | _        | SDRAM data bus              | I/O | 24    | Hi-Z  |

| A13, A12, D10,<br>B12, C12, A11,<br>D8, B11, C11,<br>A10, D7, B10, A9 | SDADDR[12:<br>0]  | _        | _              | _        | SDRAM address<br>bus        | 0   | 24    | Low   |

| M2, M3                                                                | SDBA[1:0]         | _        | _              | _        | SDRAM bank<br>addresses     | 0   | 24    | Low   |

| E3                                                                    | RAS               | _        | _              | _        | SDRAM row address strobe    | 0   | 24    | High  |

| C2                                                                    | CAS               | _        | _              | _        | SDRAM column address strobe | 0   | 24    | High  |

| R2, P2, P1, N3                                                        | SDCS[3:0]         | _        | _              | _        | SDRAM chip selects          | 0   | 24    | High  |

| B8, A3, G3, J2                                                        | SDDM[3:0]         | _        | _              | _        | SDRAM write data byte mask  | 0   | 24    | High  |

| A7, B5, F2, H1                                                        | SDDQS[3:0]        | _        | _              | _        | SDRAM data strobe           | I/O | 24    | High  |

| L1, N1                                                                | SDCLK[1:0]        | _        | _              | _        | SDRAM clock                 | 0   | 24    | Low   |

| M1, N2                                                                | SDCLK[1:0]        | _        | _              | _        | Inverted SDRAM clock        | 0   | 24    | Low   |

| K1                                                                    | SDWE              | _        | _              | _        | SDRAM write enable          | 0   | 24    | Low   |

| E4                                                                    | SDCKE             | _        | _              | _        | SDRAM clock<br>enable       | 0   | 24    | Low   |

| L2                                                                    | SDRDQS            | _        | _              | _        | SDR SDRAM data strobe       | 0   | 24    | Low   |

| D2                                                                    | VREF              | _        | _              | _        | SDRAM reference voltage     | I   | -     | _     |

|                                                                       | <u> </u>          |          | PCI Contro     | ller     | <u>'</u>                    |     |       |       |

| V25, V26, U25,<br>U26, T24, T25,<br>T26, R24                          | PCIAD[31:24]      | _        | FBADDR[31: 24] | _        | PCI address/data<br>bus     | I/O | 16    | Hi-Z  |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices. <sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| PBGA Pin                                     |              | Pin Fund    | ctions              |          | - Description                    | I/O   | Drive | Reset |

|----------------------------------------------|--------------|-------------|---------------------|----------|----------------------------------|-------|-------|-------|

| PBGA PIII                                    | Primary      | GPIO        | Secondary           | Tertiary | - Description                    | 1/0   | Drive | State |

| R25, R26, P26,<br>P24, P23, P25,<br>N25, N23 | PCIAD[23:16] | _           | FBADDR[23:<br>16]   | _        | PCI address/data<br>bus          | I/O   | 16    | Hi-Z  |

| N26, N24, M26,<br>M25, L26, L25,<br>K26, K25 | PCIAD[15:8]  | _           | FBADDR[15:<br>8]    | _        | PCI address/data<br>bus          | I/O   | 16    | Hi-Z  |

| J26, K24, J25,<br>H26, J24, G26,<br>H25, K23 | PCIAD[7:0]   | _           | FBADDR[7:0] — PCI a |          | PCI address/data<br>bus          | I/O   | 16    | Hi-Z  |

| F26, G25, E26,<br>G24                        | PCICXBE[3:0  | _           | _                   | _        | PCI command/byte enables         | I/O   | 16    | Hi-Z  |

| J23                                          | PCIDEVSEL    | _           | _                   | _        | PCI device select                | I/O   | 16    | Hi-Z  |

| F25                                          | PCIFRM       | _           | _                   | _        | PCI frame                        | I/O   | 16    | Hi-Z  |

| C23                                          | PCIIDSEL     | _           | _                   | _        | PCI initialization device select | I     | _     | _     |

| D24                                          | PCIIRDY      | _           | _                   | _        | PCI initiator ready              | I/O   | 16    | Hi-Z  |

| F23                                          | PCIPAR       | _           | _                   | _        | PCI parity                       | I/O   | 16    | Hi-Z  |

| D26                                          | PCIPERR      | _           | _                   | _        | PCI parity error                 | I/O   | 16    | Hi-Z  |

| G23                                          | PCIRESET     | 1           | _                   | _        | PCI reset                        | 0     | 16    | Low   |

| F24                                          | PCISERR      |             | _                   | _        | PCI system error                 | I/O   | 16    | Hi-Z  |

| E25                                          | PCISTOP      |             | _                   | _        | PCI stop                         | I/O   | 16    | Hi-Z  |

| C26                                          | PCITRDY      | _           | _                   | _        | PCI target ready                 | I/O   | 16    | Hi-Z  |

| W24                                          | PCIBG4       | PPCIBG4     | TBST                | _        | PCI external grant 4             | 0     | 16    | GPI   |

| Y26, W25, V24,<br>W26                        | PCIBG[3:0]   | PPCIBG[3:0] | TOUT[3:0]           | _        | PCI external grant<br>3–0        | I/O   | 16    | GPI   |

| D21                                          | PCIBR4       | PPCIBR4     | ĪRQ4                | _        | PCI external request 4           | I:I/O | 8     | GPI   |

| B24, A25, B23,<br>A24                        | PCIBR[3:0]   | PPCIBR[3:0] | TIN[3:0]            | _        | PCI external request 3           | I:I/O | 8     | GPI   |

|                                              |              | E           | xternal Interru     | pts Port |                                  |       |       |       |

| D14                                          | ĪRQ7         | PIRQ7       | _                   | _        | External interrupt request 7     | I     | _     | _     |

| B14, A14                                     | ĪRQ[6:5]     | PIRQ[6:5]   | CANRX1              | _        | External interrupt request 6—5   | I     | _     | _     |

|                                              |              |             | Ethernet MA         | VC 0     |                                  |       |       | •     |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices.

<sup>&</sup>lt;sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| DDCA Bin          |            | Pin Func    | tions       |          | Description                          | I/O   | Drive | Reset |

|-------------------|------------|-------------|-------------|----------|--------------------------------------|-------|-------|-------|

| PBGA Pin          | Primary    | GPIO        | Secondary   | Tertiary | Description                          | 1/0   | Drive | State |

| AF10              | E0MDIO     | PFECI2C3    | _           | _        | Management<br>channel<br>serial data | I/O   | 8     | GPI   |

| AD11              | E0MDC      | PFECI2C2    | _           | _        | Management channel clock             | O:I/O | 8     | GPI   |

| AF9               | E0TXCLK    | PFEC0H7     | _           | _        | MAC transmit clock                   | I:I/O | 8     | GPI   |

| AE10              | E0TXEN     | PFEC0H6     | _           | _        | MAC transmit enable                  | O:I/O | 8     | GPI   |

| AD9               | E0TXD0     | PFEC0H5     | _           | _        | MAC transmit data                    | O:I/O | 8     | GPI   |

| AC9               | E0COL      | PFEC0H4     | _           | _        | MAC collision                        | I:I/O | 8     | GPI   |

| AD14              | E0RXCLK    | PFEC0H3     | _           | _        | MAC receive clock                    | I:I/O | 8     | GPI   |

| AE14              | E0RXDV     | PFEC0H2     | _           | _        | MAC receive enable                   | I:I/O | 8     | GPI   |

| AD13              | E0RXD0     | PFEC0H1     | _           | _        | MAC receive data                     | I:I/O | 8     | GPI   |

| AE19              | E0CRS      | PFEC0H0     | _           | _        | MAC carrier sense                    | I:I/O | 8     | GPI   |

| AD8, AC6, AF7     | E0TXD[3:1] | PFEC0L[7:5] | _           | _        | MAC transmit data                    | O:I/O | 8     | GPI   |

| AE9               | E0TXER     | PFEC0L4     | _           | _        | MAC transmit error                   | O:I/O | 8     | GPI   |

| AF11, AF12, AF13  | E0RXD[3:1] | PFEC0L[3:1] | _           | _        | MAC receive data                     | I:I/O | 8     | GPI   |

| AC14              | E0RXER     | PFEC0L0     | _           | _        | MAC receive error                    | I:I/O | 8     | GPI   |

|                   |            |             | Ethernet MA | AC 1     |                                      |       |       |       |

| AD25 <sup>1</sup> | E1MDIO     | _           | SDA         | CANRX0   | Management channel serial data       | I/O   | 8     | _     |

| AD24 <sup>1</sup> | E1MDC      | _           | SCL         | CANTX0   | Management channel clock             | O:I/O | 8     | _     |

| AE13 <sup>1</sup> | E1TXCLK    | PFEC1H7     | _           | _        | MAC Transmit clock                   | I:I/O | 8     | GPI   |

| AD25 <sup>1</sup> | E1TXEN     | PFEC1H6     | _           | _        | MAC Transmit enable                  | O:I/O | 8     | GPI   |

| AE12 <sup>1</sup> | E1TXD0     | PFEC1H5     | _           | _        | MAC Transmit data                    | O:I/O | 8     | GPI   |

| AF8 <sup>1</sup>  | E1COL      | PFEC1H4     | _           | _        | MAC Collision                        | I:I/O | 8     | GPI   |

| B22 <sup>1</sup>  | E1RXCLK    | PFEC1H3     | _           | _        | MAC Receive clock                    | I:I/O | 8     | GPI   |

| B25 <sup>1</sup>  | E1RXDV     | PFEC1H2     | _           | _        | MAC Receive enable                   | I:I/O | 8     | GPI   |

| AF24 <sup>1</sup> | E1RXD0     | PFEC1H1     | _           | _        | MAC Receive data                     | I:I/O | 8     | GPI   |

| AC5 <sup>1</sup>  | E1CRS      | PFEC1H0     | _           | _        | MAC Carrier sense                    | I:I/O | 8     | GPI   |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices. <sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| PBGA Pin                                                    |                  | Pin Fund                           | tions            |               | Description                   | I/O   | Drive | Reset |

|-------------------------------------------------------------|------------------|------------------------------------|------------------|---------------|-------------------------------|-------|-------|-------|

| FBGATIII                                                    | Primary          | GPIO                               | Secondary        | Tertiary      | Description                   | 1/0   | Dilve | State |

| AC8 <sup>1</sup> , AC11 <sup>1</sup> ,<br>AE11 <sup>1</sup> | E1TXD[3:1]       | PFEC1L[7:5]                        | _                | _             | MAC Transmit data             | O:I/O | 8     | GPI   |

| AE24 <sup>1</sup>                                           | E1TXER           | PFEC1L4                            | _                | _             | MAC Transmit error            | O:I/O | 8     | GPI   |

| D25 <sup>1</sup> , B26 <sup>1</sup> , A26 <sup>1</sup>      | E1RXD[3:1]       | PFEC1L[3:1]                        | _                | _             | MAC Receive data              | I:I/O | 8     | GPI   |

| AE8 <sup>1</sup>                                            | E1RXER           | RXER PFEC1L0 — — MAC Receive error |                  | I:I/O         | 8                             | GPI   |       |       |

|                                                             |                  |                                    | USB              |               |                               |       |       |       |

| AF16 <sup>2</sup>                                           | USBD+            | _                                  | _                | _             | USB differential data         | I/O   | 24    | _     |

| AF17 <sup>2</sup>                                           | USBD-            | _                                  | _                | _             | USB differential data         | I/O   | 24    | _     |

| AC17 <sup>2</sup>                                           | USBVBUS          | _                                  | _                | _             | USB Vbus monitor input        | I     | _     | _     |

| AC15 <sup>2</sup>                                           | NC               | _                                  | _                | _             | No Connect                    | ļ     | _     | _     |

| AF18 <sup>2</sup>                                           | USBRBIAS         | _                                  | _                | _             | USB bias resistor             | I     | _     | _     |

| AF15 <sup>2</sup>                                           | USBCLKIN         | _                                  | _                | _             | USB crystal input             | I     | _     | _     |

| AF14 <sup>2</sup>                                           | USBCLKOUT        | _                                  | _                | _             | USB crystal output            | 0     | 24    | _     |

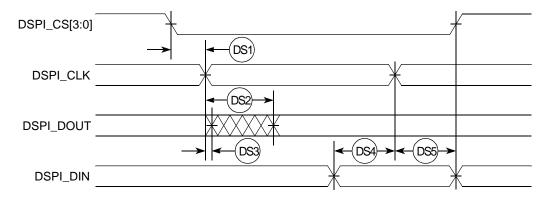

|                                                             |                  |                                    | DSPI             |               |                               |       |       |       |

| Y24                                                         | DSPISOUT         | PDSPI0                             | PSC3TXD          | _             | QSPI data out                 | O:I/O | 24    | GPI   |

| AC24                                                        | DSPISIN          | PDSPI1                             | PSC3RXD          | _             | QSPI data in                  | I:I/O | 24    | GPI   |

| AD22                                                        | DSPISCK          | PDSPI2                             | PSC3CTS          | PSC3BCL<br>K  | QSPI clock                    | I/O   | 24    | GPI   |

| W23                                                         | DSPICS5/PC<br>SS | PDSPI6                             | _                | _             | QSPI chip select              | O:I/O | 24    | GPI   |

| V23                                                         | DSPICS3          | PDSPI5                             | TOUT3            | CANTX1        | QSPI chip select              | O:I/O | 24    | GPI   |

| AA26                                                        | DSPICS2          | PDSPI4                             | TOUT2            | CANTX1        | QSPI chip select              | O:I/O | 24    | GPI   |

| Y25                                                         | DSPICS0/SS       | PDSPI3                             | PSC3RTS          | PSC3FSY<br>NC | QSPI chip select              | O:I/O | 24    | GPI   |

|                                                             |                  |                                    | I <sup>2</sup> C |               | ,                             |       |       |       |

| C24                                                         | SDA              | PFECI2C1                           | _                | _             | I <sup>2</sup> C Serial data  | I/O   | 8     | GPI   |

| C25                                                         | SCL              | PFECI2C0                           | _                | _             | I <sup>2</sup> C Serial clock | I/O   | 8     | GPI   |

|                                                             |                  |                                    | PSCs             | •             | , ,                           |       |       |       |

| AA25                                                        | PSC0TXD          | PPSCL0                             | _                | _             | PSC0 transmit data            | O:I/O | 8     | GPI   |

| AC21                                                        | PSC0RXD          | PPSCL1                             | _                | _             | PSC0 receive data             | I:I/O | 8     | GPI   |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices.

<sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| PBGA Pin   |           | Pin Fund  | ctions     |          | Description          | I/O   | Drive | Reset |

|------------|-----------|-----------|------------|----------|----------------------|-------|-------|-------|

| PBGAPIN    | Primary   | GPIO      | Secondary  | Tertiary | Description          | 1/0   | Drive | State |

| AE23       | PSC0CTS   | PPSCL2    | PSC0BCLK   |          | PSC0 clear to send   | I:I/O | 8     | GPI   |

| AB26       | PSC0RTS   | PPSCL3    | PSC0FSYNC  | _        | PSC0 request to send | I/O   | 8     | GPI   |

| AB25       | PSC1TXD   | PPSCL4    | _          | _        | PSC1 transmit data   | O:I/O | 8     | GPI   |

| AE22       | PSC1RXD   | PPSCL5    | P          |          | PSC1 receive data    | I:I/O | 8     | GPI   |

| AF25       | PSC1CTS   | PPSCL6    | PSC1BCLK   | _        | PSC1 clear to send   | I:I/O | 8     | GPI   |

| Y23        | PSC1RTS   | PPSCL7    | PSC1FSYNC  |          | PSC1 request to send | I/O   | 8     | GPI   |

| AC26       | PSC2TXD   | PPSCH0    | _          | _        | PSC2 transmit data   | O:I/O | 8     | GPI   |

| AD21       | PSC2RXD   | PPSCH1    | _          | _        | PSC2 receive data    | I:I/O | 8     | GPI   |

| AC19       | PSC2CTS   | PPSCH2    | PSC2BCLK   | CANRX0   | PSC2 clear to send   | I:I/O | 8     | GPI   |

| AD26       | PSC2RTS   | PPSCH3    | PSC2FSYNC  | CANTX0   | PSC2 request to send | I/O   | 8     | GPI   |

| AE26       | PSC3TXD   | PPSCH4    | _          | _        | PSC3 transmit data   | O:I/O | 8     | GPI   |

| AE21       | PSC3RXD   | PPSCH5    | _          | _        | PSC3 receive data    | I:I/O | 8     | GPI   |

| AF23       | PSC3CTS   | PPSCH6    | PSC3BCLK   | _        | PSC3 clear to send   | I:I/O | 8     | GPI   |

| AB23       | PSC3RTS   | PPSCH7    | PSC3FSYNC  | _        | PSC3 request to send | I/O   | 8     | GPI   |

|            |           |           | DMA Contro | oller    |                      |       |       |       |

| AF19       | DREQ1     | PDMA1     | TIN1       | ĪRQ1     | DMA request          | I:I/O | 8     | GPI   |

| AF20       | DREQ0     | PDMA0     | TIN0       | _        | DMA request          | I:I/O | 8     | GPI   |

| AC25, AB24 | DACK[1:0] | PDMA[3:2] | TOUT[1:0]  | _        | DMA acknowledge      | O:I/O | 8     | GPI   |

|            |           |           | Timer Mod  | ule      |                      |       |       |       |

| AD19       | TIN3      | PTIM7     | ĪRQ3       | CANRX1   | Timer input          | I:I/O | 8     | GPI   |

| AD23       | TOUT3     | PTIM6     | CANTX1     | _        | Timer output         | O:I/O | 8     | GPI   |

| AF21       | TIN2      | PTIM5     | ĪRQ2       | CANRX1   | Timer input          | I:I/O | 8     | GPI   |

| AC22       | TOUT2     | PTIM4     | CANTX1     | _        | Timer output         | O:I/O | 8     | GPI   |

| AE20       | TIN1      | _         | _          | _        | Timer input          | I:I/O | 8     | GPI   |

| AC23       | TOUT1     | _         | _          | _        | Timer output         | O:I/O | 8     | GPI   |

| AF22       | TIN0      | _         | _          | _        | Timer input          | I:I/O | 8     | GPI   |

| AF26       | TOUT0     | _         | _          | _        | Timer output         | O:I/O | 8     | GPI   |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices.

<sup>&</sup>lt;sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| PBGA Pin                                                                                                         |                   | Pin Fund | tions          |                             | - Description                    | I/O | Drive | Reset |

|------------------------------------------------------------------------------------------------------------------|-------------------|----------|----------------|-----------------------------|----------------------------------|-----|-------|-------|

| PBGA FIII                                                                                                        | Primary           | GPIO     | Secondary      | Tertiary                    | Description                      | 1/0 | Dilve | State |

|                                                                                                                  |                   | Debug    | and JTAG Tes   | t Port Cont                 | rol                              |     | 1     |       |

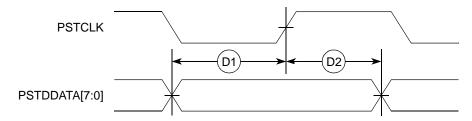

| D20                                                                                                              | PSTCLK            | _        | _              | _                           | Processor clock output           | 0   | 8     | High  |

| A23, B21, D18,<br>C20, A22, B20,<br>A21, B19                                                                     | PSTDDATA[7<br>:0] | _        | _              | Processor status debug data |                                  | 0   | 8     | High  |

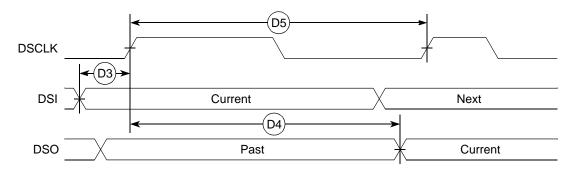

| C15                                                                                                              | DSCLK             | _        | TRST           | _                           | Debug clock / TAP reset          | I   | _     |       |

| B15                                                                                                              | BKPT              | _        | TMS            | _                           | Breakpoint/TAP test mode select  | I   | _     | _     |

| A15                                                                                                              | DSI               | _        | TDI            | _                           | Debug data in / TAP<br>data in   | I   | _     | _     |

| D17                                                                                                              | DSO               | _        | TDO            | _                           | Debug data out /<br>TAP data out | 0   | 8     | High  |

| A16                                                                                                              | TCK               | _        | _              | _                           | TAP clock                        | I   | _     | _     |

|                                                                                                                  |                   | 7        | est, Reset, an | d Clock                     |                                  |     |       |       |

| B17, C14, A18,<br>B16                                                                                            | MTMOD[3:0]        | _        | _              | _                           | Test mode pins                   | I   | _     | _     |

| B13                                                                                                              | RSTI              | _        | _              | _                           | Reset input                      | I   | _     | _     |

| A20                                                                                                              | RSTO              | _        | _              | _                           | Reset output                     | I/O | 8     | Low   |

| A17                                                                                                              | CLKIN             | _        | _              | _                           | Clock input                      | I   | _     | _     |

| D15                                                                                                              | NC                | _        | _              | _                           | No Connect                       | I   | _     | _     |

|                                                                                                                  |                   |          | Power Supp     | olies                       |                                  |     |       |       |

| C16, C22, E24,<br>H24K M24, R3,<br>U24, Y3, AA24,<br>AB3, AC13, AC16,<br>AD7, AD10, AD16,<br>AD18, AD15,<br>AE18 | EVDD              | _        | _              | _                           | Positive I/O supply              | I   | _     | _     |

| C18, D11, D12,<br>D19, D22, H4,<br>H23, L23, P4,<br>R23, V4, AA23,<br>AC12, AC20                                 | IVDD              | _        | _              | _                           | Positive core supply             | I   | _     | _     |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices.

<sup>&</sup>lt;sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 3. MCF548x Signal Description (continued)

| PBGA Pin                                                                                                                                                                                                                                                                                                                                   |                 | Pin Fund | ctions    |          | Description                  | I/O | Drive | Reset |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----------|----------|------------------------------|-----|-------|-------|

| PBGA PIII                                                                                                                                                                                                                                                                                                                                  | Primary         | GPIO     | Secondary | Tertiary | - Description                | 1/0 | Drive | State |

| A2, B2, C3, C17, C19, C21, D6, D9, D13, D23, E23, F4, J4, L4, L11, L12, L13, L14, L15, L16, L24, M11, M12, M13, M14, M15, M16, M23, N11, N12, N13, N14, N15, N16, P11, P12, P13, P14, P15, P16, R4, R11, R12, R13, R14, R15, R16, T11, T12, T13, T14, T15, T16, T23, U4, U23, Y4, AB4, AC7, AC10, AC18, AD12, AE15, AD17, AD20, AE16, AE17 |                 | _        |           |          | Ground                       |     |       |       |

| A1, B1, C1, C6,<br>C9, C13, D3, F3,<br>L3, P3                                                                                                                                                                                                                                                                                              | SDVDD           | _        | _         | _        | Positive SDRAM supply        |     |       |       |

| A19                                                                                                                                                                                                                                                                                                                                        | PLLVDD          | _        | _         | _        | Positive PLL analog supply   |     |       |       |

| B18                                                                                                                                                                                                                                                                                                                                        | PLLVSS          | _        | _         | _        | PLL ground                   |     |       |       |

| AC13 <sup>3</sup>                                                                                                                                                                                                                                                                                                                          | USB_OSCVD<br>D  | _        | _         | _        | USB oscillator supply        |     |       |       |

| AC16 <sup>3</sup>                                                                                                                                                                                                                                                                                                                          | USB_PHYVD<br>D  | _        | _         | _        | USB PHY supply               |     |       |       |

| AD14 <sup>3</sup>                                                                                                                                                                                                                                                                                                                          | USB_OSCAV<br>DD | -        | _         | _        | USB oscillator analog supply |     |       |       |

| AD15 <sup>3</sup>                                                                                                                                                                                                                                                                                                                          | USB_PLLVD<br>D  | _        | _         | _        | USB PLL supply               |     |       |       |

| AE17 <sup>3</sup>                                                                                                                                                                                                                                                                                                                          | USBVDD          | _        | _         | _        | USB supply                   |     |       |       |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices. <sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

#### **Signal Description**

Table 4 lists the MCF548x signals in pin number order for the 388 PBGA package.

Table 4. MCF5485/MCF5484 Signal Description by Pin Number

| DDOA Di-         |           | Pin Fu  | nctions   |          | BBGA Bir |         | Pin F  | unctions  |          |

|------------------|-----------|---------|-----------|----------|----------|---------|--------|-----------|----------|

| PBGA Pin         | Primary   | GPIO    | Secondary | Tertiary | PBGA Pin | Primary | GPIO   | Secondary | Tertiary |

| A1               | SDVDD     | _       | _         | _        | P1       | SDCS1   | _      | _         | _        |

| A2               | VSS       | _       | _         | _        | P2       | SDCS2   | _      | _         | _        |

| A3               | SDDM2     | _       | _         | _        | P3       | EVDD    | _      | _         | _        |

| A4               | SDDATA23  | _       | _         | _        | P4       | IVDD    | _      | _         | _        |

| A5               | SDDATA24  | _       | _         | _        | P11      | VSS     | _      | _         | _        |

| A6               | SDDATA27  | _       | _         | _        | P12      | VSS     | _      | _         | _        |

| A7               | SDDQS3    | _       | _         | _        | P13      | VSS     | _      | _         | _        |

| A8               | SDDATA29  | _       | _         | _        | P14      | VSS     | _      | _         | _        |

| A9               | SDADDR0   | _       | _         | _        | P15      | VSS     | _      | _         | _        |

| A10              | SDADDR3   | _       | _         | _        | P16      | VSS     | _      | _         | _        |

| A11              | SDADDR7   | _       | _         | _        | P23      | PCIAD19 | _      | FBADDR19  | _        |

| A12              | SDADDR11  | _       | _         | _        | P24      | PCIAD20 | _      | FBADDR20  | _        |

| A13              | SDADDR12  | _       | _         | _        | P25      | PCIAD18 | _      | FBADDR18  | _        |

| A14              | ĪRQ5      | PIRQ5   | CANRX1    | _        | P26      | PCIAD21 | _      | FBADDR21  | _        |

| A15              | DSI       | _       | TDI       | _        | R1       | FBCS5   | PFBCS5 | _         | _        |

| A16              | TCK       | _       | _         | _        | R2       | SDCS3   | _      | _         | _        |

| A17              | CLKIN     | _       | _         | _        | R3       | EVDD    | _      | _         | _        |

| A18              | MTMOD1    | _       | _         | _        | R4       | VSS     | _      | _         | _        |

| A19              | PLLVDD    | _       | _         | _        | R11      | VSS     | _      | _         | _        |

| A20              | RSTO      | _       | _         | _        | R12      | VSS     | _      | _         | _        |

| A21              | PSTDDATA1 | _       | _         | _        | R13      | VSS     | _      | _         | _        |

| A22              | PSTDDATA3 | _       | _         | _        | R14      | VSS     | _      | _         | _        |

| A23              | PSTDDATA7 | _       | _         | _        | R15      | VSS     | _      | _         | _        |

| A24              | PCIBR0    | PPCIBR0 | TIN0      | _        | R16      | VSS     | _      | _         | _        |

| A25              | PCIBR2    | PPCIBR2 | TIN2      | _        | R23      | IVDD    | _      | _         | _        |

| A26 <sup>1</sup> | E1RXD1    | PFEC1L5 | _         | _        | R24      | PCIAD24 | _      | FBADDR24  | _        |

| B1               | SDVDD     | _       | _         | _        | R25      | PCIAD23 | _      | FBADDR23  | _        |

| B2               | VSS       | _       | _         | _        | R26      | PCIAD22 | _      | FBADDR22  | _        |

| B3               | SDDATA18  | _       | _         | _        | T1       | FBCS2   | PFBCS2 | _         | _        |

<sup>&</sup>lt;sup>1</sup>This pin is a "no connect" on the MCF5483 and MCF5482 devices.

<sup>&</sup>lt;sup>2</sup>This pin is a "no connect" on the MCF5481 and MCF5480 devices.

<sup>&</sup>lt;sup>3</sup>TBD if the USB power pins are connected when the USB is disabled or not used.

Table 4. MCF5485/MCF5484 Signal Description by Pin Number (continued)

| DDOA Dir         |           | Pin Functions |           |          |            | Pin Functions |         |           |          |

|------------------|-----------|---------------|-----------|----------|------------|---------------|---------|-----------|----------|

| PBGA Pin         | Primary   | GPIO          | Secondary | Tertiary | - PBGA Pin | Primary       | GPIO    | Secondary | Tertiary |

| B4               | SDDATA20  |               | _         | _        | T2         | FBCS4         | PFBCS4  | _         | _        |

| B5               | SDDQS2    | _             | _         | _        | Т3         | FBCS3         | PFBCS3  |           | _        |

| B6               | SDDATA21  | _             | _         | _        | T4         | AD1           | _       | _         | _        |

| B7               | SDDATA25  | _             | _         | _        | T11        | VSS           | _       | _         | _        |

| B8               | SDDM3     | _             | _         | _        | T12        | VSS           | _       | _         | _        |

| B9               | SDDATA30  | _             | _         | _        | T13        | VSS           | _       | _         | _        |

| B10              | SDADDR1   | _             | _         | _        | T14        | VSS           | _       | _         | _        |

| B11              | SDADDR5   | _             | _         | _        | T15        | VSS           | _       | _         | _        |

| B12              | SDADDR9   | _             | _         | _        | T16        | VSS           | _       | _         | _        |

| B13              | RSTI      | _             | _         | _        | T23        | VSS           | _       | _         | _        |

| B14              | ĪRQ6      | PIRQ6         | CANRX1    | _        | T24        | PCIAD27       | _       | FBADDR27  | _        |

| B15              | BKPT      | _             | TMS       | _        | T25        | PCIAD26       | _       | FBADDR26  | _        |

| B16              | MTMOD0    | _             | _         | _        | T26        | PCIAD25       | _       | FBADDR25  | _        |

| B17              | MTMOD3    | _             | _         | _        | U1         | FBCS0         | _       | _         | _        |

| B18              | PLLVSS    | _             | _         | _        | U2         | FBCS1         | PFBCS1  | _         | _        |

| B19              | PSTDDATA0 | _             | _         | _        | U3         | AD0           | _       | _         | _        |

| B20              | PSTDDATA2 | _             | _         | _        | U4         | VSS           | _       | _         | _        |

| B21              | PSTDDATA6 | _             | _         | _        | U23        | VSS           | _       | _         | _        |

| B22 <sup>1</sup> | E1RXCLK   | PFEC1H3       | _         | _        | U24        | EVDD          | _       | _         | _        |

| B23              | PCIBR1    | PPCIBR1       | TIN1      | _        | U25        | PCIAD29       | _       | FBADDR29  | _        |

| B24              | PCIBR3    | PPCIBR3       | TIN3      | _        | U26        | PCIAD28       | _       | FBADDR28  | _        |

| B25 <sup>1</sup> | E1RXDV    | PFEC1H2       | _         | _        | V1         | AD3           | _       | _         | _        |

| B26 <sup>1</sup> | E1RXD2    | PFEC1L2       | _         | _        | V2         | AD2           | _       | _         | _        |

| C1               | SDVDD     | _             | _         | _        | V3         | AD4           | _       | _         | _        |

| C2               | CAS       | _             | _         | _        | V4         | EVDD          | _       | _         | _        |

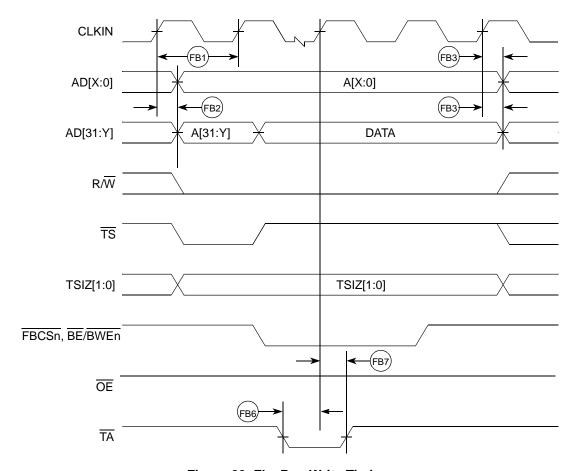

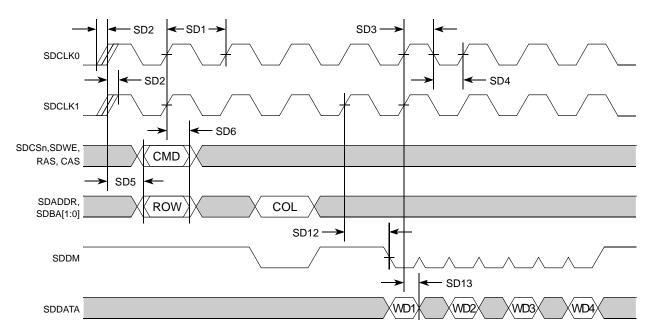

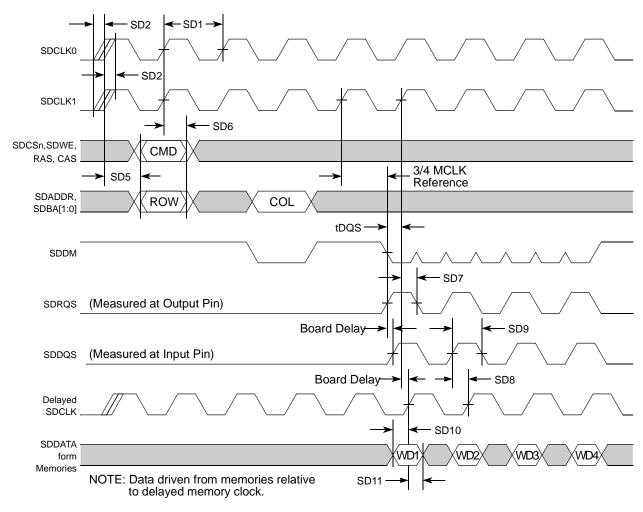

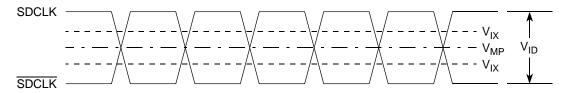

| C3               | VSS       | _             | _         | _        | V23        | DSPICS3       | PDSPI5  | TOUT3     | CANTX1   |