### **General Description**

The MAX3812 is a multirate SMPTE cable driver designed to operate at data rates up to 1.485Gbps, driving one or two 75 $\Omega$  coaxial cables. Two selectable slew rates are provided for compliance to SMPTE 292M, SMPTE 344M, and SMPTE 259M. The MAX3812 is pin compatible with the Gennum GS1528.

The MAX3812 inputs are internally biased and compatible with differential swings of CML, LVPECL, and LVDS. Output voltage swing is adjustable with a single external resistor.

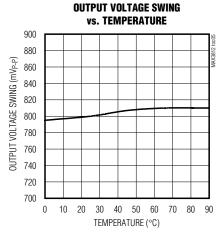

The MAX3812 operates over a 0°C to +85°C temperature range. It typically consumes 106mW with a +3.3V power supply and is available in an 8-pin SO package.

### **Applications**

SMPTE 292M, SMPTE 344M, SMPTE 259M, and DVB-ASI Coaxial Cable Serial Digital Interfaces Professional Digital Video Switchers and Routers Professional Digital Video Cameras and Recording Devices

## **Ordering Information**

| PART        | TEMP RANGE   | PIN-PACKAGE |

|-------------|--------------|-------------|

| MAX3812USA  | 0°C to +85°C | 8 SO        |

| MAX3812USA+ | 0°C to +85°C | 8 SO        |

<sup>+</sup>Denotes lead-free package. Contact factory for availability.

#### **Features**

- ♦ SMPTE 292M, SMPTE 344M, SMPTE 259M, and **DVB-ASI Compliant**

- **♦ 106mW Power Consumption Using a +3.3V Power** Supply

- ♦ Smooth Rise/Fall Transitions for Low EMI

- Selectable Slew Rate for HD and SD Rates

- ♦ Pin Compatible with Gennum GS1528

- **♦ Dual Coaxial Cable Driving Outputs**

- ◆ Adjustable Output Voltage Swing

- ♦ Input Compatibility with Differential Swings of CML, LVPECL, and LVDS

- ♦ 0°C to +85°C Operating Temperature Range

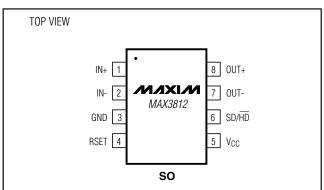

### **Pin Configuration**

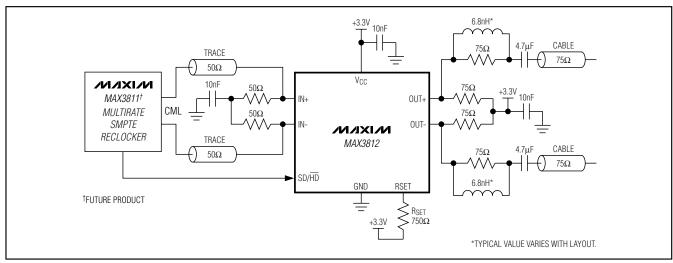

## Typical Application Circuit

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (VCC)              | 0.5V to +4.0V                    | Continuous Power Dissipation (T <sub>A</sub> = +85°C) |                 |

|-----------------------------------|----------------------------------|-------------------------------------------------------|-----------------|

| Voltage at IN+, IN-, RSET, SD/HD, |                                  | 8-Pin SO (derate 5.9mW/°C above +85°C)                | 384mW           |

| OUT+, OUT(                        | 0.5V to (V <sub>CC</sub> + 0.5V) | Storage Temperature Range                             | -55°C to +150°C |

|                                   |                                  | Lead Temperature (soldering, 10s)                     | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(VCC = +3.0V to +3.6V, T<sub>A</sub> = 0°C to +85°C. Typical values are at V<sub>CC</sub> = +3.3V, T<sub>A</sub>= +25°C, unless otherwise noted.)

| PARAMETER                  | SYMBOL           | CONDITIONS                                  | MIN                              | TYP           | MAX                                          | UNITS |

|----------------------------|------------------|---------------------------------------------|----------------------------------|---------------|----------------------------------------------|-------|

| Supply Current             | Icc              | $R_{SET} = 750\Omega$                       |                                  | 32            | 45                                           | mA    |

| Power Consumption          |                  | $R_{SET} = 750\Omega$                       |                                  | 106           |                                              | mW    |

| Output Common-Mode Voltage | V <sub>СМО</sub> | Figure 1, AC-coupled output                 |                                  | Vcc -<br>Vout |                                              | >     |

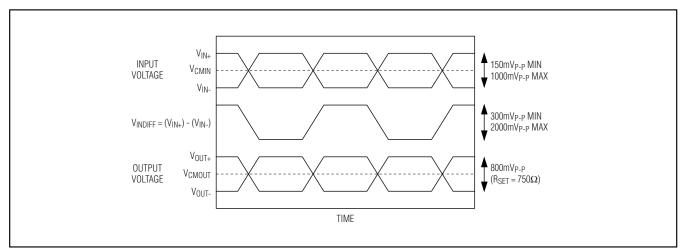

| Input Common-Mode Voltage  | VCMIN            | Figure 1                                    | 1.6 +<br>V <sub>INDIFF</sub> / 4 |               | V <sub>CC</sub> -<br>V <sub>INDIFF</sub> / 4 | V     |

| SD/HD Input-High Voltage   | VIH              |                                             | 2.0                              |               |                                              | V     |

| SD/HD Input-Low Voltage    | VIL              |                                             |                                  |               | 0.8                                          | V     |

| SD/HD Input-High Current   | lін              | 2.0V ≤ V <sub>SD/HD</sub> ≤ V <sub>CC</sub> | -110                             | -40           | •                                            | μΑ    |

| SD/HD Input-Low Current    | I <sub>IL</sub>  | 0V ≤ V <sub>SD/HD</sub> ≤ 0.8V              | -150                             | -90           |                                              | μΑ    |

#### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3V, T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                           | SYMBOL                          | CONDITIONS                                      | MIN | TYP  | MAX  | UNITS             |  |

|-------------------------------------|---------------------------------|-------------------------------------------------|-----|------|------|-------------------|--|

| Serial Input Data Rate              |                                 |                                                 | 19  |      | 1485 | Mb/s              |  |

| Supply-Noise Tolerance              |                                 | 60Hz ≤ f <sub>NOISE</sub> ≤ 27MHz               |     | 100  |      | \/                |  |

|                                     |                                 | 27MHz < f <sub>NOISE</sub> ≤ 1.5GHz             |     | 40   |      | mV <sub>P-P</sub> |  |

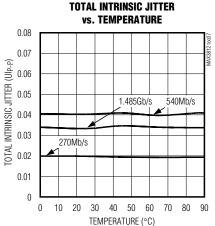

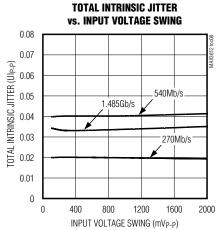

| Total Intrinsic Jitter (Notes 1, 2) | TJ                              | 1.485Gb/                                        |     | 0.03 | 0.05 | - Ulp-p           |  |

|                                     |                                 | 540Mb/s                                         |     | 0.04 | 0.07 |                   |  |

|                                     |                                 | 19Mb/s, 143Mb/s, 177Mb/s, 270Mb/s, 360Mb/s      |     | 0.02 | 0.05 |                   |  |

| Output Rise/Fall Time               | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%, SD/HD = low                         |     | 145  | 220  | ps                |  |

|                                     |                                 | 20% to 80%, SD/HD = high                        | 450 | 675  | 750  |                   |  |

| Mismatch in Rise/Fall Time          |                                 | (Notes 1, 3)                                    |     | 5    | 30   | ps                |  |

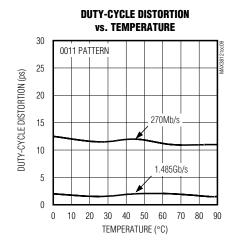

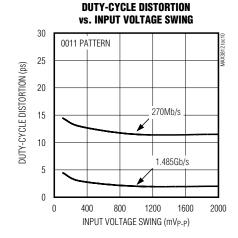

| Duty-Cycle Distortion               |                                 | (Notes 1, 3)                                    |     | 2    |      | ps                |  |

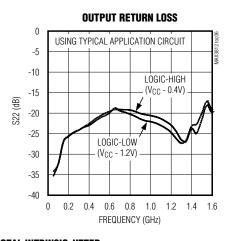

| Output Return Loss                  |                                 | 5MHz to 1.485GHz (Note 4)                       |     | 19   |      | dB                |  |

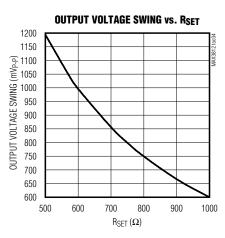

| Output Voltage Swing                |                                 | Single-ended, $R_{SET} = 750\Omega$ , Figure 1  | 750 | 800  | 850  |                   |  |

|                                     | Vout                            | Single-ended, $R_{SET} = 570\Omega$ , Figure 1  |     | 1050 |      | mV <sub>P-P</sub> |  |

|                                     |                                 | Single-ended, $R_{SET} = 1000\Omega$ , Figure 1 |     | 600  |      |                   |  |

| Input Voltage Swing                 | VINDIFF                         | Differential, Figure 1                          | 300 |      | 2000 | mV <sub>P-P</sub> |  |

| Input Rise/Fall Time                |                                 | 20% to 80% (Note 5)                             |     |      | 230  | ps                |  |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3 \text{V}, T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

- Note 1: Guaranteed by design and characterization.

- Note 2: Total intrinsic jitter is defined as the summation of deterministic jitter (DJ) and random jitter (RJ) using the formula: TJ(UIP-P) = DJ(UIP-P) + 14.1 x RJ(UIRMS)

- Note 3: Measured at 1.485Gb/s using a 0011 pattern.

- **Note 4:** See the Output Return Loss graph in the *Typical Operating Characteristics*.

- Note 5: Input signals must reach the full amplitude levels within the unit interval.

Figure 1. Definition of Input and Output Voltage

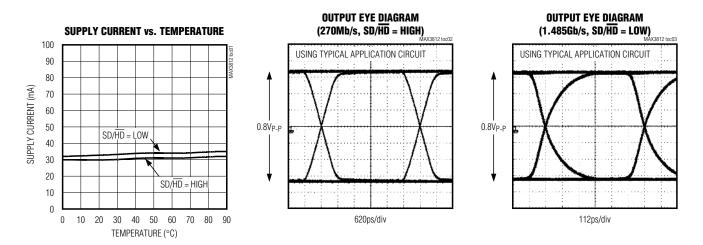

## Typical Operating Characteristics

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, R_{SET} = 750\Omega, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, R_{SET} = 750\Omega, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                 |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN+   | Positive Data Input                                                                                                                      |

| 2   | IN-   | Negative Data Input                                                                                                                      |

| 3   | GND   | Supply Ground                                                                                                                            |

| 4   | RSET  | Output-Voltage-Swing Control. Connect a resistor between RSET and V <sub>CC</sub> to set the output voltage swing.                       |

| 5   | Vcc   | +3.3V Supply Voltage                                                                                                                     |

| 6   | SD/HD | Output Slew-Rate Control, LVTTL. Set HIGH for SMPTE 259M/344M rise/fall specifications. Set LOW for SMPTE 292M rise/fall specifications. |

| 7   | OUT-  | Negative Data Output                                                                                                                     |

| 8   | OUT+  | Positive Data Output                                                                                                                     |

### Detailed Description

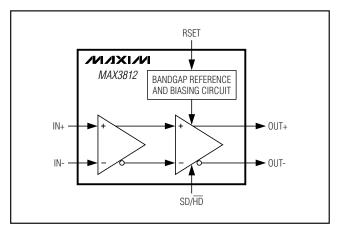

The MAX3812 is a multirate SMPTE cable driver designed to drive  $75\Omega$  coaxial cable for serial digital interfaces. The driver consists of a differential input buffer, slew-rate selection switch, output-voltage-swing control, and a differential output buffer (Figure 2).

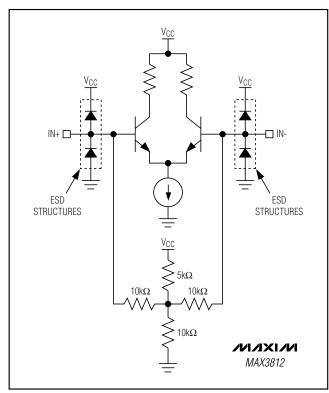

### **Differential Data Inputs**

The MAX3812 data inputs (IN+, IN-) are high impedance and should be terminated as shown in the *Typical Application Circuit*. When properly terminated, the inputs are compatible with differential swings of CML, LVPECL, and LVDS. For more information about logic interfacing, refer to Maxim application note *HFAN-01.0: Introduction to LVDS, PECL, and CML*.

Figure 2. Functional Diagram

While DC-coupled, the MAX3812 operates properly as long as the specified common-mode voltage and differential voltage swings are met. Because of the on-chip biasing network (Figure 3), the inputs self-bias to the proper operating point to accommodate AC-coupling. If the inputs are AC-coupled, a minimum capacitor value of 4.7µF should be used to accommodate SMPTE pathological test signals.

Figure 3. Differential Input Circuit

Figure 4. Slew-Rate Selection Switch

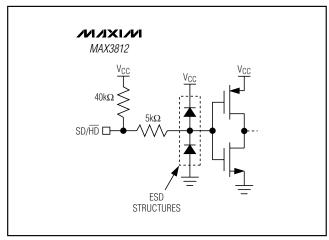

#### **Slew-Rate Selection Switch**

The MAX3812 output has a selectable slew-rate in order to achieve compliance to SMPTE 259M/344M and SMPTE 292M. Output slew rate is selected with the SD/HD input (Figure 4). The SD/HD pin must be set high for SMPTE 259M/344M standards and low for SMPTE 292M standards.

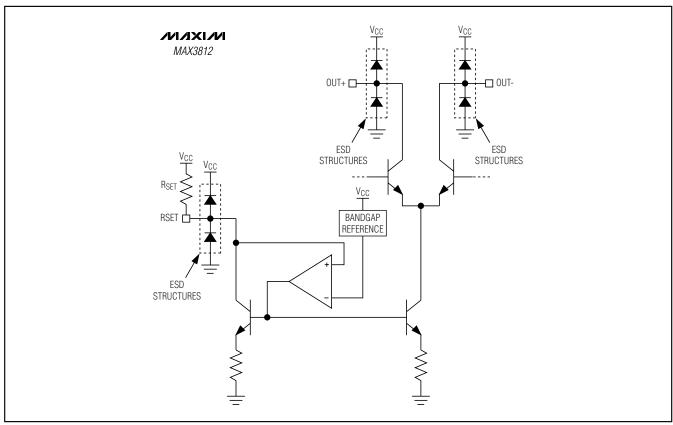

### **Differential Data Outputs**

The MAX3812 differential data outputs are current-mode logic, CML (Figure 5). Each side of the differential output will drive 800mVp-p into a doubly terminated  $75\Omega$  transmission line (RSET =  $750\Omega$ ).

The cable driver output must have a source impedance of  $75\Omega$  and a return loss of at least 15dB between 5MHz and 1.485GHz to comply with the SMPTE 259M, SMPTE 344M, and SMPTE 292M standards. In order to meet the return loss specification, the output network shown in the *Typical Application Circuit* is recommended.

The value of the output inductor is typically 6.8nH, but the value will vary depending on PC board layout. If the outputs are AC-coupled, a minimum capacitor value of 4.7µF should be used to accommodate SMPTE pathological test signals.

When measuring output return loss, it is necessary to take the measurement for both a logic-high and logic-low state. This is due to the output capacitance being slightly dependent on the logic state. See the Output Return Loss graph in the *Typical Operating Characterisitics*.

#### **Output Voltage Swing Control**

The external R<sub>SET</sub> resistor connected between V<sub>CC</sub> and the RSET pin controls the output voltage swing (Figure 5). Typically the output voltage swing is set to 800mVp-p using a value of  $750\Omega$ . For output voltage swings other than 800mVp-p, see the graph Output Voltage Swing vs. R<sub>SET</sub> given in the *Typical Operating Characteristics*. Using R<sub>SET</sub> values below  $500\Omega$  is not recommended.

The RSET resistor should be placed as close as possible to the RSET pin and the capacitance at this node should be minimized.

## Applications Information

### **Layout Considerations**

Use controlled-impedance transmission lines to interface with the MAX3812 high-speed inputs and outputs. Power-supply decoupling capacitors should be placed as close as possible to the VCC connections. To support a 75 $\Omega$  transmission-line environment at the outputs, it is necessary to minimize the parasitic capacitance by removing the PC board ground plane from under the output pins and output components. Transmission line stubs associated with BNC connectors should be minimized. Edge-mount BNC connectors are recommended.

Figure 5. Differential Output and Biasing Circuit

## **Chip Information**

TRANSISTOR COUNT: 926 PROCESS: SiGe Bipolar

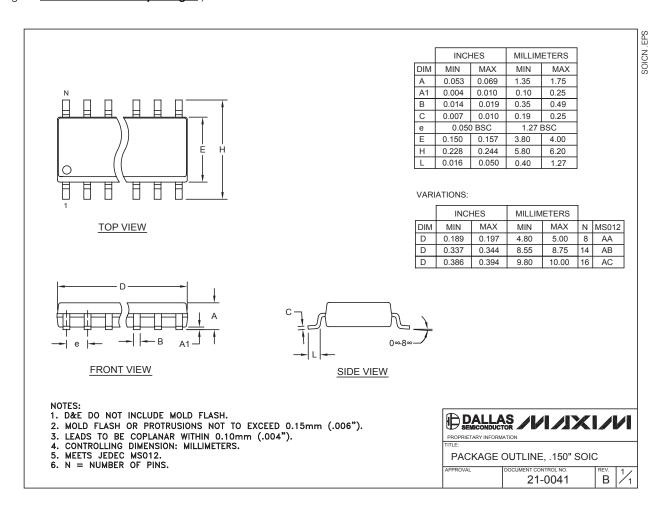

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.