**Preferred Device**

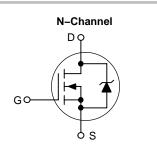

# Power MOSFET 6 Amps, 200 Volts N-Channel DPAK

This advanced Power MOSFET is designed to withstand high energy in the avalanche and commutation modes. The new energy efficient design also offers a drain-to-source diode with a fast recovery time. Designed for low voltage, high speed switching applications in power supplies, converters and PWM motor controls, these devices are particularly well suited for bridge circuits where diode speed and commutating safe operating areas are critical and offer additional safety margin against unexpected voltage transients.

### Features

- Avalanche Energy Specified

- Source-to-Drain Diode Recovery Time Comparable to a Discrete Fast Recovery Diode

- Diode is Characterized for Use in Bridge Circuits

- I<sub>DSS</sub> and V<sub>DS(on)</sub> Specified at Elevated Temperature

- Pb–Free Package is Available\*

### **MAXIMUM RATINGS** ( $T_C = 25^{\circ}C$ unless otherwise noted)

| <b>MAXIMUM IXATINGS</b> ( $T_C = 25$ C unless otherwise hoted)                                                                                                                                                                                    |                                                       |                     |            |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|------------|--|--|

| Rating                                                                                                                                                                                                                                            | Symbol                                                | Value               | Unit       |  |  |

| Drain-to-Source Voltage                                                                                                                                                                                                                           | V <sub>DSS</sub>                                      | 200                 | Vdc        |  |  |

| Drain-to-Gate Voltage ( $R_{GS}$ = 1.0 M $\Omega$ )                                                                                                                                                                                               | V <sub>DGR</sub>                                      | 200                 | Vdc        |  |  |

| Gate–to–Source Voltage<br>– Continuous<br>– Non–repetitive (t <sub>p</sub> ≤ 10 ms)                                                                                                                                                               | V <sub>GS</sub><br>V <sub>GSM</sub>                   | ± 20<br>± 40        | Vdc<br>Vpk |  |  |

| Drain Current<br>– Continuous<br>– Continuous @ 100°C<br>– Single Pulse (t <sub>p</sub> ≤ 10 μs)                                                                                                                                                  | I <sub>D</sub><br>ID<br>I <sub>DM</sub>               | 6.0<br>3.8<br>18    | Adc<br>Apk |  |  |

| Total Power Dissipation<br>Derate above 25°C<br>Total Power Dissipation @ T <sub>A</sub> = 25°C (Note 2)                                                                                                                                          | P <sub>D</sub>                                        | 50<br>0.4<br>1.75   | W/∘C<br>W  |  |  |

| Operating and Storage Temperature Range                                                                                                                                                                                                           | T <sub>J</sub> , T <sub>stg</sub>                     | -55 to<br>150       | °C         |  |  |

| $            Single Pulse Drain-to-Source Avalanche \\             Energy - Starting T_J = 25^\circ C \\              (V_{DD} = 80 \ Vdc, \ V_{GS} = 10 \ Vdc, \\             I_L = 6.0 \ Apk, \ L = 3.0 \ mH, \ R_G = 25 \ \Omega )            $ | E <sub>AS</sub>                                       | 54                  | mJ         |  |  |

| Thermal Resistance – Junction-to-Case<br>– Junction-to-Ambient (Note 1)<br>– Junction-to-Ambient (Note 2)                                                                                                                                         | $f{R}_{	heta JC} \ f{R}_{	heta JA} \ f{R}_{	heta JA}$ | 2.50<br>100<br>71.4 | °C/W       |  |  |

| Maximum Temperature for Soldering<br>Purposes, 1/8" from case for 10 secs                                                                                                                                                                         | TL                                                    | 260                 | °C         |  |  |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1. When surface mounted to an FR4 board using the minimum recommended pad size.

2. When surface mounted to an FR4 board using the 0.5 sq. in. drain pad size.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **ON Semiconductor®**

http://onsemi.com

# 6 AMPERES, 200 VOLTS R<sub>DS(on)</sub> = 460 mΩ

= Pb-Free Package

# ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

**Preferred** devices are recommended choices for future use and best overall value.

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $25^{\circ}$ C unless otherwise noted)

| Characteristic                                                                                                                                                                 |                                                                                        | Symbol               | Min      | Тур         | Max        | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------|----------|-------------|------------|--------------|

| OFF CHARACTERISTICS                                                                                                                                                            |                                                                                        |                      |          |             |            |              |

| Drain–Source Breakdown Voltage<br>( $V_{GS} = 0 \text{ Vdc}, I_D = 0.25 \mu \text{Adc}$ )<br>Temperature Coefficient (Positive)                                                |                                                                                        | V <sub>(BR)DSS</sub> | 200<br>_ | 689         |            | Vdc<br>mV/°C |

| Zero Gate Voltage Drain Current<br>( $V_{DS} = 200 \text{ Vdc}, V_{GS} = 0 \text{ Vdc}$ )<br>( $V_{DS} = 200 \text{ Vdc}, V_{GS} = 0 \text{ Vdc}, T_J = 125^{\circ}\text{C}$ ) |                                                                                        | I <sub>DSS</sub>     |          | -           | 10<br>100  | μAdc         |

| Gate-Body Leakage Current (V <sub>GS</sub> =                                                                                                                                   | ±20 Vdc, V <sub>DS</sub> = 0)                                                          | I <sub>GSS</sub>     | -        | -           | 100        | nAdc         |

| ON CHARACTERISTICS (Note 3)                                                                                                                                                    |                                                                                        |                      |          |             |            |              |

| Gate Threshold Voltage<br>$(V_{DS} = V_{GS}, I_D = 250 \ \mu Adc)$<br>Temperature Coefficient (Negative)                                                                       |                                                                                        | V <sub>GS(th)</sub>  | 2.0      | 3.0<br>7.1  | 4.0<br>_   | Vdc<br>mV/°C |

| Static Drain-Source On-Resistance                                                                                                                                              | $(V_{GS} = 10 \text{ Vdc}, I_D = 3.0 \text{ Adc})$                                     | R <sub>DS(on)</sub>  | -        | 0.46        | 0.700      | Ohm          |

| Drain–Source On–Voltage ( $V_{GS}$ = 10 Vdc)<br>( $I_D$ = 6.0 Adc)<br>( $I_D$ = 3.0 Adc, $T_J$ = 125°C)                                                                        |                                                                                        | V <sub>DS(on)</sub>  |          | 2.9<br>_    | 5.0<br>4.4 | Vdc          |

| Forward Transconductance (V <sub>DS</sub> =                                                                                                                                    | 9fs                                                                                    | 1.5                  | _        | -           | mhos       |              |

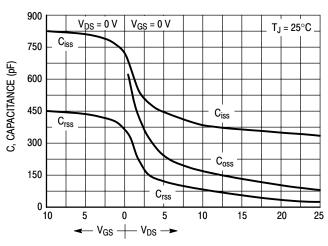

| DYNAMIC CHARACTERISTICS                                                                                                                                                        |                                                                                        |                      |          |             |            |              |

| Input Capacitance                                                                                                                                                              |                                                                                        | C <sub>iss</sub>     | -        | 342         | 480        | pF           |

| Output Capacitance                                                                                                                                                             | $(V_{DS} = 25 \text{ Vdc}, V_{GS} = 0 \text{ Vdc}, f = 1.0 \text{ MHz})$               | C <sub>oss</sub>     | _        | 92          | 130        |              |

| Reverse Transfer Capacitance                                                                                                                                                   | r = 1.0 m 2,                                                                           | C <sub>rss</sub>     | -        | 27          | 55         |              |

| SWITCHING CHARACTERISTICS (I                                                                                                                                                   | Note 4)                                                                                | •                    |          |             |            |              |

| Turn-On Delay Time                                                                                                                                                             |                                                                                        | t <sub>d(on)</sub>   | -        | 8.8         | 17.6       | ns           |

| Rise Time                                                                                                                                                                      | $(V_{DD} = 100 \text{ Vdc}, I_D = 6.0 \text{ Adc}, V_{GS} = 10 \text{ Vdc},$           | t <sub>r</sub>       | -        | 29          | 58         |              |

| Turn-Off Delay Time                                                                                                                                                            | $R_{\rm G} = 9.1 \ \Omega$                                                             | t <sub>d(off)</sub>  | -        | 22          | 44         |              |

| Fall Time                                                                                                                                                                      |                                                                                        | t <sub>f</sub>       | -        | 20          | 40.8       |              |

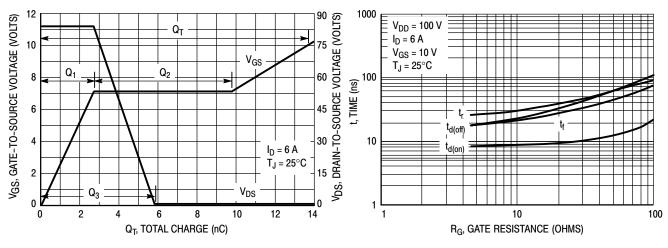

| Gate Charge                                                                                                                                                                    | $(V_{DS} = 160 \text{ Vdc}, I_{D} = 6.0 \text{ Adc}, V_{GS} = 10 \text{ Vdc})$         | QT                   | _        | 13.7        | 21         | nC           |

| (See Figure 8)                                                                                                                                                                 |                                                                                        | Q <sub>1</sub>       | _        | 2.7         | _          | -            |

|                                                                                                                                                                                |                                                                                        | Q <sub>2</sub>       | -        | 7.1         | -          |              |

|                                                                                                                                                                                |                                                                                        | Q <sub>3</sub>       | -        | 5.9         | -          |              |

| SOURCE-DRAIN DIODE CHARACT                                                                                                                                                     | ERISTICS                                                                               |                      |          |             |            |              |

| Forward On–Voltage (Note 3)                                                                                                                                                    |                                                                                        | V <sub>SD</sub>      |          | 0.99<br>0.9 | 1.2        | Vdc          |

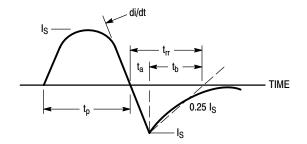

| Reverse Recovery Time                                                                                                                                                          |                                                                                        | t <sub>rr</sub>      | -        | 138         | -          | ns           |

| (See Figure 14)                                                                                                                                                                | (I <sub>S</sub> = 6.0 Adc, V <sub>GS</sub> = 0 Vdc,<br>dI <sub>S</sub> /dt = 100 A/μs) | ta                   | -        | 93          | -          | -            |

|                                                                                                                                                                                |                                                                                        | t <sub>b</sub>       | -        | 45          | -          |              |

| Reverse Recovery Stored Charge                                                                                                                                                 |                                                                                        | Q <sub>RR</sub>      | _        | 0.74        | -          | μC           |

| INTERNAL PACKAGE INDUCTANC                                                                                                                                                     | E                                                                                      |                      |          |             |            |              |

| Internal Drain Inductance<br>(Measured from the drain lead 0.25" from package to center of die)                                                                                |                                                                                        | L <sub>D</sub>       | -        | 4.5         | -          | nH           |

| Internal Source Inductance<br>(Measured from the source lead 0                                                                                                                 | .25" from package to source bond pad)                                                  | L <sub>S</sub>       | -        | 7.5         | -          | nH           |

Pulse Test: Pulse Width ≤ 300 μs, Duty Cycle ≤ 2%.

Switching characteristics are independent of operating junction temperature.

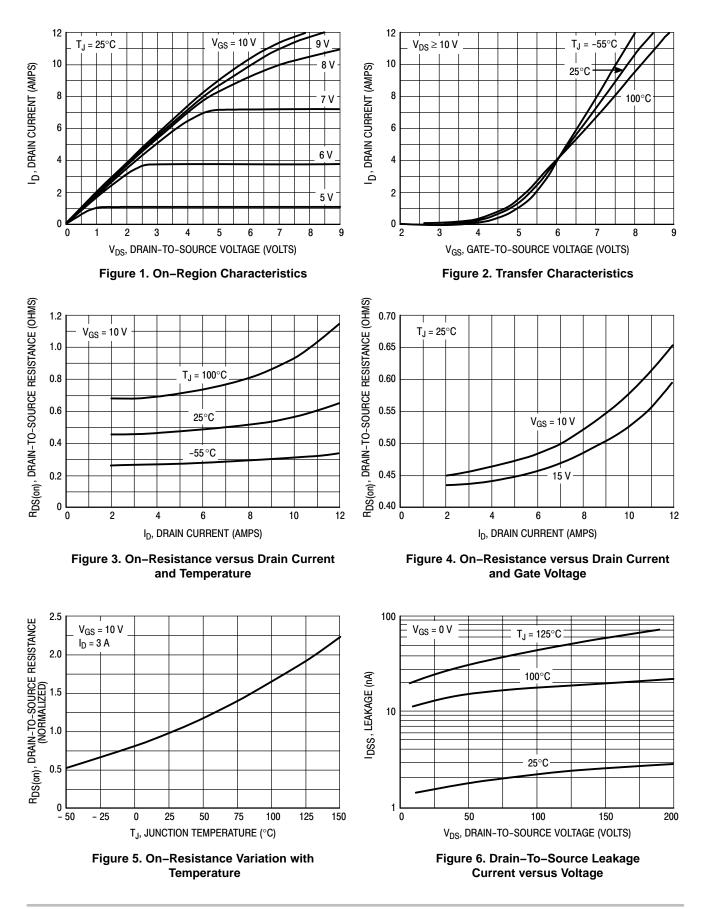

# **TYPICAL ELECTRICAL CHARACTERISTICS**

### POWER MOSFET SWITCHING

Switching behavior is most easily modeled and predicted by recognizing that the power MOSFET is charge controlled. The lengths of various switching intervals ( $\Delta t$ ) are determined by how fast the FET input capacitance can be charged by current from the generator.

The published capacitance data is difficult to use for calculating rise and fall because drain–gate capacitance varies greatly with applied voltage. Accordingly, gate charge data is used. In most cases, a satisfactory estimate of average input current ( $I_{G(AV)}$ ) can be made from a rudimentary analysis of the drive circuit so that

$t = Q/I_{G(AV)}$

During the rise and fall time interval when switching a resistive load,  $V_{GS}$  remains virtually constant at a level known as the plateau voltage,  $V_{SGP}$ . Therefore, rise and fall times may be approximated by the following:

$t_r = Q_2 \ x \ R_G / (V_{GG} - V_{GSP})$

$t_f = Q_2 \ x \ R_G / V_{GSP}$

where

$V_{GG}$  = the gate drive voltage, which varies from zero to  $V_{GG}$

$R_G$  = the gate drive resistance

and  $Q_2$  and  $V_{GSP}$  are read from the gate charge curve.

During the turn–on and turn–off delay times, gate current is not constant. The simplest calculation uses appropriate values from the capacitance curves in a standard equation for voltage change in an RC network. The equations are:

$$\begin{split} t_{d(on)} &= R_G \; C_{iss} \; In \; [V_{GG}/(V_{GG} - V_{GSP})] \\ t_{d(off)} &= R_G \; C_{iss} \; In \; (V_{GG}/V_{GSP}) \end{split}$$

The capacitance ( $C_{iss}$ ) is read from the capacitance curve at a voltage corresponding to the off–state condition when calculating  $t_{d(on)}$  and is read at a voltage corresponding to the on–state when calculating  $t_{d(off)}$ .

At high switching speeds, parasitic circuit elements complicate the analysis. The inductance of the MOSFET source lead, inside the package and in the circuit wiring which is common to both the drain and gate current paths, produces a voltage at the source which reduces the gate drive current. The voltage is determined by Ldi/dt, but since di/dt is a function of drain current, the mathematical solution is complex. The MOSFET output capacitance also complicates the mathematics. And finally, MOSFETs have finite internal gate resistance which effectively adds to the resistance of the driving source, but the internal resistance is difficult to measure and, consequently, is not specified.

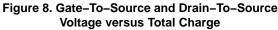

The resistive switching time variation versus gate resistance (Figure 9) shows how typical switching performance is affected by the parasitic circuit elements. If the parasitics were not present, the slope of the curves would maintain a value of unity regardless of the switching speed. The circuit used to obtain the data is constructed to minimize common inductance in the drain and gate circuit loops and is believed readily achievable with board mounted components. Most power electronic loads are inductive; the data in the figure is taken with a resistive load, which approximates an optimally snubbed inductive load. Power MOSFETs may be safely operated into an inductive load; however, snubbing reduces switching losses.

GATE-TO-SOURCE OR DRAIN-TO-SOURCE VOLTAGE (VOLTS)

Figure 7. Capacitance Variation

Figure 9. Resistive Switching Time Variation versus Gate Resistance

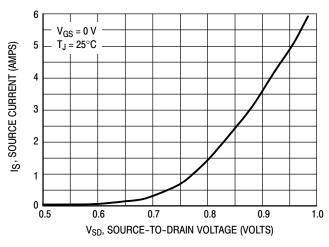

Figure 10. Diode Forward Voltage versus Current

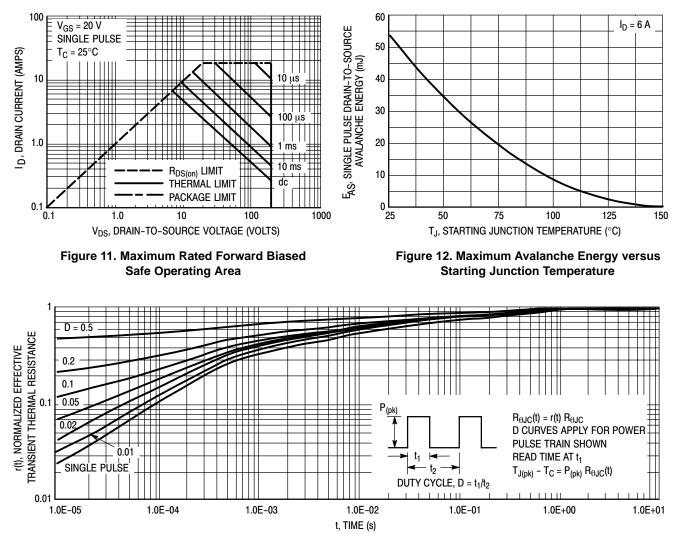

#### SAFE OPERATING AREA

The Forward Biased Safe Operating Area curves define the maximum simultaneous drain–to–source voltage and drain current that a transistor can handle safely when it is forward biased. Curves are based upon maximum peak junction temperature and a case temperature ( $T_C$ ) of 25°C. Peak repetitive pulsed power limits are determined by using the thermal response data in conjunction with the procedures discussed in AN569, "Transient Thermal Resistance–General Data and Its Use."

Switching between the off-state and the on-state may traverse any load line provided neither rated peak current ( $I_{DM}$ ) nor rated voltage ( $V_{DSS}$ ) is exceeded and the transition time ( $t_r, t_f$ ) do not exceed 10 µs. In addition the total power averaged over a complete switching cycle must not exceed ( $T_{J(MAX)} - T_C$ )/( $R_{\theta JC}$ ).

A Power MOSFET designated E–FET can be safely used in switching circuits with unclamped inductive loads. For reliable operation, the stored energy from circuit inductance dissipated in the transistor while in avalanche must be less than the rated limit and adjusted for operating conditions differing from those specified. Although industry practice is to rate in terms of energy, avalanche energy capability is not a constant. The energy rating decreases non–linearly with an increase of peak current in avalanche and peak junction temperature.

Although many E–FETs can withstand the stress of drain–to–source avalanche at currents up to rated pulsed current ( $I_{DM}$ ), the energy rating is specified at rated continuous current ( $I_D$ ), in accordance with industry custom. The energy rating must be derated for temperature as shown in the accompanying graph (Figure 12). Maximum energy at currents below rated continuous  $I_D$  can safely be assumed to equal the values indicated.

## SAFE OPERATING AREA

Figure 13. Thermal Response

Figure 14. Diode Reverse Recovery Waveform

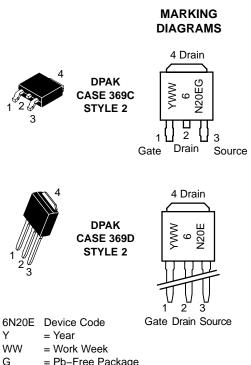

### ORDERING INFORMATION

| Device      | Package               | Shipping <sup>†</sup> |

|-------------|-----------------------|-----------------------|

| MTD6N20E    | DPAK                  | 75 Units / Rail       |

| MTD6N20E1   | DPAK<br>Straight Lead | 75 Units / Rail       |

| MTD6N20ET4  | DPAK                  | 2500 Tape & Reel      |

| MTD6N20ET4G | DPAK<br>(Pb–Free)     | 2500 Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

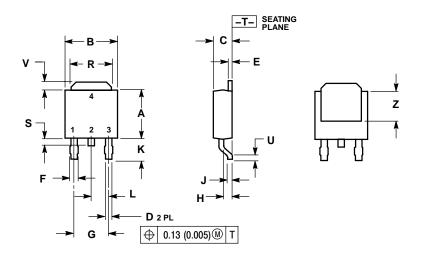

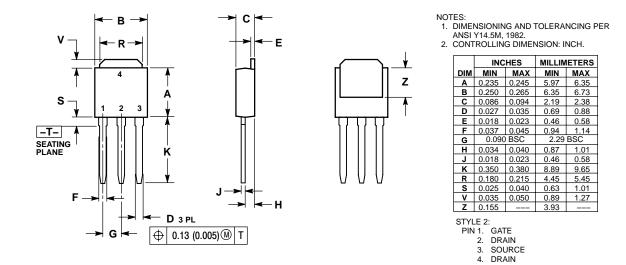

# PACKAGE DIMENSIONS

DPAK CASE 369C-01 ISSUE O

|     | INCHES    |       | MILLIMETER |      |

|-----|-----------|-------|------------|------|

| DIM | MIN       | MAX   | MIN MAX    |      |

| Α   | 0.235     | 0.245 | 5.97       | 6.22 |

| В   | 0.250     | 0.265 | 6.35       | 6.73 |

| С   | 0.086     | 0.094 | 2.19       | 2.38 |

| D   | 0.027     | 0.035 | 0.69       | 0.88 |

| Е   | 0.018     | 0.023 | 0.46       | 0.58 |

| F   | 0.037     | 0.045 | 0.94       | 1.14 |

| G   | 0.180 BSC |       | 4.58 BSC   |      |

| Н   | 0.034     | 0.040 | 0.87       | 1.01 |

| J   | 0.018     | 0.023 | 0.46       | 0.58 |

| Κ   | 0.102     | 0.114 | 2.60       | 2.89 |

| L   | 0.090 BSC |       | 2.29 BSC   |      |

| R   | 0.180     | 0.215 | 4.57       | 5.45 |

| S   | 0.025     | 0.040 | 0.63       | 1.01 |

| U   | 0.020     |       | 0.51       |      |

| ۷   | 0.035     | 0.050 | 0.89       | 1.27 |

| Z   | 0.155     |       | 3.93       |      |

STYLE 2: PIN 1. GATE 2. DRAIN 3. SOURCE 4. DRAIN

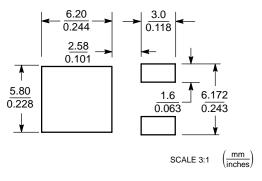

### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### PACKAGE DIMENSIONS

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product customer application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use persons, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.