# Surge Protected IO-Link Transceiver with DC-DC

MAX22514

## **Product Highlights**

- High Configurability and Integration

- IO-Link Device and Master Applications

- COM1, COM2, and COM3 Data Rates

- Integrated High-Efficiency 200mA DC-DC Buck Regulator

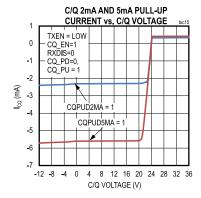

- 200µA/2mA/5mA Current Sinks/Sources

- · C/Q Receiver is Configurable for 5V TTL

- · Highly Configurable Driver Overload Handling

- · Four Selectable Driver Slew Rates

- · SPI Configuration and Monitoring

- Integrated Temperature Sensor

- Configurable C/Q Driver: PNP, NPN, and PP Modes

- Integrated Protection Enables Robust Systems

- Integrated ±1kV/500Ω Surge Protection

- Spread Spectrum DC-DC

- · Reverse Polarity Protection

- · Glitch Filter for Improved Burst Resilience

- Hot-Plug Protection

- Optimized for Small Sensor Designs

- · Accurate Oscillator for IO-Link Communication

- 2.4 $\Omega$  (typ) Driver On-Resistance for Low Power Dissipation

- · 1.2MHz DC-DC Switching Rate

- · Integrated 3.3V and 5V Linear Regulators

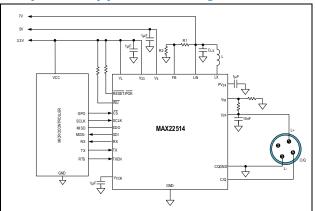

- Available in Tiny WLP (2.5mm x 2.6mm) and TQFN (4mm x 5mm) Packages

## **Key Applications**

- IO-Link and Industrial Sensor and Actuator Devices

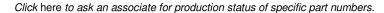

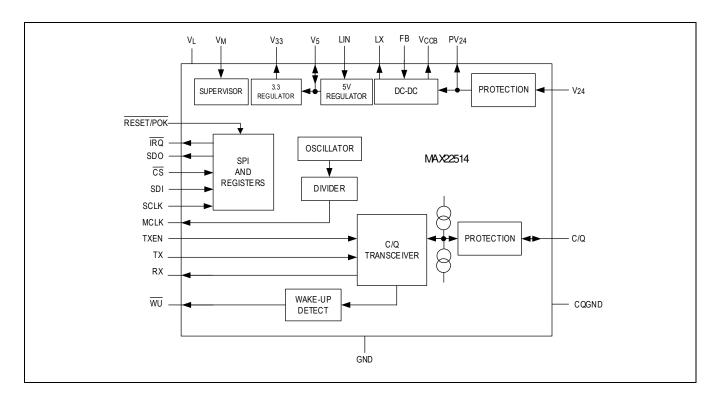

- The MAX22514 features a SPI interface for configuration and diagnostics. A high level of integration (including two linear regulators, a DC-DC buck regulator, and integrated surge protection, combined with low power dissipation and small packages) optimizes the MAX22514 for use in many different industrial and IO-Link small sensor applications.

IO-Link Master Transceivers The MAX22514 is capable of being used in both IO-Link devices and IO-Link master applications. A SPI interface is used for extended configurability and diagnostics, and the transceiver is capable of operating at the COM1, COM2, and COM3 IO-Link data rates. The MAX22514 can be configured to

enable the required 5mA pull-down/pull-up current

on the C/Q line and generate a wake-up pulse.

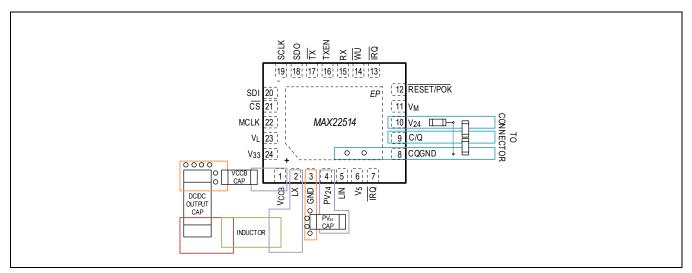

## **Simplified Application Diagram**

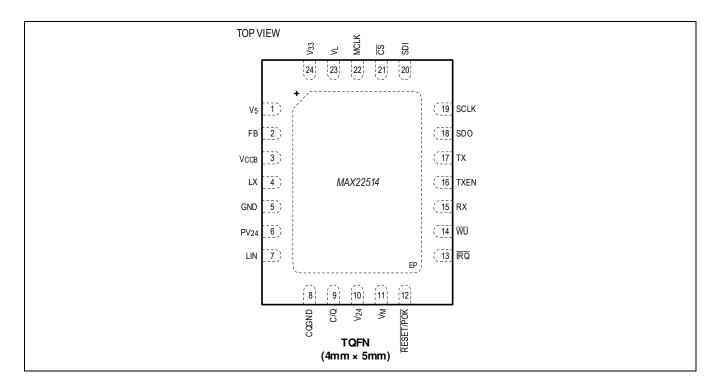

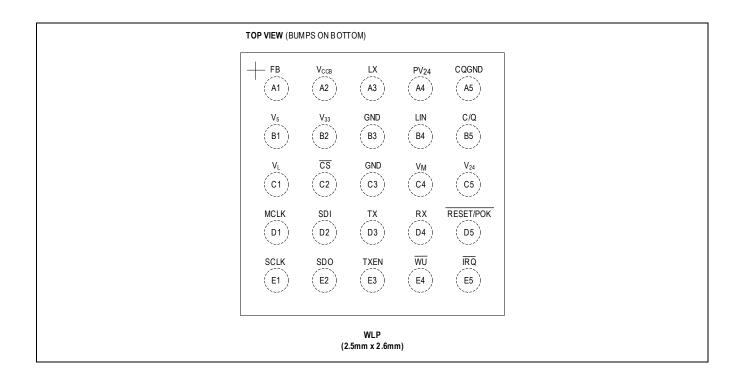

## **Pin Configuration**

See more Who should use this part.

Ordering Information appears at end of data sheet.

## **Absolute Maximum Ratings**

| All voltages referenced to GND, unless otherwise noted.                                | SDO, RX, MCLK0.3V to ( $V_L + 0.3V$ )                                            |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| V <sub>24</sub> (Continuous)36V to +36V                                                | IRQ, WU0.3V to +6V                                                               |

| V <sub>24</sub> (Peak, 100µs)52V to +65V                                               | CQGND0.3V to +0.3V                                                               |

| PV <sub>24</sub> (Continuous)0.3V to +36V                                              | Continuous Current into V24, LX, GND, or CQGND±1A                                |

| $PV_{24}$ (Peak, 100µs) MAX(-0.3V, $V_{24}$ - 52V) to MIN(+52V, $V_{24}$               | Continuous Current into PV <sub>24</sub> ±200mA                                  |

| + 52V)                                                                                 | Peak Current into PV <sub>24</sub> (100µs)±1A                                    |

| LX0.3V to (PV <sub>24</sub> + 0.3V)                                                    | Continuous Current into C/Q±500mA                                                |

| LIN (Continuous) MAX(-0.3V, V <sub>5</sub> - 0.3V) to +36V                             | Continuous Current into Any Other Pin±50mA                                       |

| LIN (Peak, 100µs)MAX(-0.3V, V <sub>5</sub> - 0.3V) to +52V                             | Continuous Power Dissipation                                                     |

| C/Q (Continuous) MAX(-36V, $V_{24}$ - 36V) to MIN(+36V, $V_{24}$ + 36V)                | 24-pin TQFN ( $T_A = +70^{\circ}$ C, derates at 28.6mW/°C above $+70^{\circ}$ C) |

| C/Q (Peak, 100µs) MAX(-52V, V <sub>24</sub> - 60V) to MIN(+52V, V <sub>24</sub> + 60V) | 25-bump WLP (T <sub>A</sub> = +70°C, derates at 22.74mW/°C above +70°C)          |

| V <sub>M</sub> , FB, V <sub>CCB</sub> , RESET/POK0.3V to +6V                           | Operating Temperature Range40°C to +125°C                                        |

| V <sub>5</sub> , V <sub>L</sub> 0.3V to +6V                                            | Maximum Junction Temperature+150°C                                               |

| $V_{33}$ 0.3V to $(V_5+ 0.3V)$                                                         | Storage Temperature Range40°C to +150°C                                          |

| LOGIC INPUTS CS, SCLK, SDI, TX, TXEN0.3V to $(V_L + 0.3V)$                             | Soldering Temperature (Reflow) (TQFN only, soldering, 10 seconds)+300°C          |

| LOGIC OUTPUTS                                                                          | Bump Reflow Temperature+260°C                                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

| T2445+2C                              |  |  |  |  |  |

|---------------------------------------|--|--|--|--|--|

| <u>21-0201</u>                        |  |  |  |  |  |

| <u>90-0083</u>                        |  |  |  |  |  |

|                                       |  |  |  |  |  |

| 35°C/W                                |  |  |  |  |  |

| 1.8°C/W                               |  |  |  |  |  |

|                                       |  |  |  |  |  |

| W252V2+1                              |  |  |  |  |  |

| <u>21-100546</u>                      |  |  |  |  |  |

| Refer to App Note 1891                |  |  |  |  |  |

| Thermal Resistance, Four Layer Board: |  |  |  |  |  |

| 43.98°C/W                             |  |  |  |  |  |

| N/A                                   |  |  |  |  |  |

|                                       |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{CQGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ Typical\ values\ are\ at\ V_{24}=24V,\ V_5=5V,\ V_L=3.3V\ and\ T_A=+25^{\circ}C,\ unless\ otherwise\ noted\ (Note\ 1))$

| $V_{24} = 24V, V_5 = 5V, V_L = 3$ <b>PARAMETER</b>              | SYMBOL                                                                  |                                                                                                                                       | ITIONS                                                       | MIN                                    | TYP  | MAX   | UNITS |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------|------|-------|-------|--|

| DC CHARACTERISTIC                                               | CS                                                                      |                                                                                                                                       | ,                                                            |                                        |      |       |       |  |

| POWER SUPPLY                                                    |                                                                         |                                                                                                                                       |                                                              |                                        |      |       |       |  |

| V <sub>24</sub> Supply Voltage                                  | $V_{24}$                                                                |                                                                                                                                       |                                                              | 8                                      |      | 36    | V     |  |

| V <sub>24</sub> Undervoltage                                    | M                                                                       | V <sub>24</sub> rising                                                                                                                |                                                              | 7                                      | 7.5  | 8     |       |  |

| Lockout Threshold                                               | $V_{24UVLO}$                                                            | V <sub>24</sub> falling                                                                                                               |                                                              | 6.3                                    | 7    | 7.6   | V     |  |

| V <sub>24</sub> Undervoltage<br>Lockout Threshold<br>Hysteresis | V <sub>24</sub> uvlo_hyst                                               |                                                                                                                                       |                                                              |                                        | 500  |       | mV    |  |

|                                                                 |                                                                         | No load on C/Q,<br>V₅ powered                                                                                                         | C/Q disabled, V <sub>33</sub> enabled                        |                                        | 0.04 | 0.075 |       |  |

| V <sub>24</sub> Supply Current                                  | l <sub>24</sub>                                                         | externally, DC-<br>DC disabled,<br>MCLK disabled                                                                                      | C/Q in push-pull,<br>and is high or<br>low                   |                                        | 0.32 | 0.45  | mA    |  |

|                                                                 |                                                                         |                                                                                                                                       | V₅ powered<br>externally, DC-<br>DC enabled,<br>MCLK enabled | C/Q in push-pull<br>and is high or low |      | 1.95  |       |  |

| V₅ Supply Voltage                                               | <b>V</b> <sub>5</sub>                                                   | V₅ supplied extern                                                                                                                    | ally                                                         | 4.5                                    |      | 5.5   | V     |  |

| V₅ Undervoltage                                                 | V <sub>5UVLO</sub>                                                      | V₅ rising                                                                                                                             |                                                              | 3.98                                   |      | 4.26  | V     |  |

| Lockout Threshold                                               | V 5UVLO                                                                 | V₅ falling                                                                                                                            |                                                              | 3.92                                   |      | 4.19  | V     |  |

|                                                                 |                                                                         | V <sub>5</sub> powered<br>externally, DC-<br>DC disabled,<br>MCLK disabled,<br>V <sub>33</sub> enabled, no<br>load on V <sub>33</sub> | C/Q disabled                                                 |                                        | 0.85 | 1.1   |       |  |

| V₅ Supply Current                                               | externally DC-DC of MCLK div V33 enabload on V5 power disabled, 29.48MH | V <sub>5</sub> powered<br>externally,<br>DC-DC disabled,<br>MCLK disabled,<br>V <sub>33</sub> enabled, no<br>load on V <sub>33</sub>  | C/Q in push-pull<br>mode, no load<br>on C/Q                  |                                        | 1.13 | 1.5   | mA    |  |

|                                                                 |                                                                         | V₅ powered extern<br>disabled, MCLK e<br>29.48MHz, C/Q in<br>high or low                                                              | nabled and set to                                            |                                        | 3.0  |       |       |  |

| V <sub>L</sub> Logic Level Supply<br>Voltage                    | VL                                                                      |                                                                                                                                       |                                                              | 2.5                                    |      | 5.5   | V     |  |

| V <sub>L</sub> Undervoltage<br>Threshold                        | $V_{\text{LUVLO}}$                                                      |                                                                                                                                       |                                                              | 0.45                                   |      | 1.35  | V     |  |

| V <sub>L</sub> Logic Level Supply<br>Current                    | lι                                                                      |                                                                                                                                       | GND or V <sub>L</sub> , no load<br>its, MCLK disabled        |                                        | 3    | 10    | μА    |  |

$(V_{24} = 8V \text{ to } 36V, V_5 = 4.5V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{CQGND} = V_{GND} = 0V$ , All logic inputs at  $V_L$  or GND, Typical values are at  $V_{24} = 24V, V_5 = 5V, V_L = 3.3V$  and  $V_L = 2.5V$ , unless otherwise noted (Note 1))

| PARAMETER                                    | SYMBOL                  | CONDITIONS                                                                                                                         | MIN   | TYP   | MAX   | UNITS               |

|----------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------------|

| DC-DC SWITCHING R                            | EGULATOR                |                                                                                                                                    | 1     |       |       | 1                   |

| Input Voltage Range                          | V <sub>24_DC</sub>      | V <sub>24</sub> is the input to the DC-DC                                                                                          | 8     |       | 36    | V                   |

| DC-DC Turn-on<br>Delay                       | tdc_on                  | Delay from V <sub>24</sub> crossing V <sub>24UVLO</sub><br>threshold until the DC-DC regulator<br>finishes soft-start. RESET rises |       | 10.2  |       | ms                  |

| Switching Frequency                          | f <sub>DC_H</sub>       | BUCKSS = 0                                                                                                                         | 1.198 | 1.229 | 1.260 | MHz                 |

| Switching Frequency                          | f <sub>DC_HSPRD</sub>   | BUCKSS = 1                                                                                                                         |       | 1.229 |       | IVIII               |

| Spread Spectrum                              | ∆f <sub>DC_SPRD</sub>   | FREQ = high, BUCKSS = 1                                                                                                            |       | ±10   |       | %                   |

| Feedback (FB)<br>Regulation Voltage          | V <sub>DC_FB</sub>      |                                                                                                                                    |       | 0.9   |       | V                   |

| Output Voltage<br>Accuracy                   | ACCDCFB                 |                                                                                                                                    | -1.5  | 0     | +1.5  | %                   |

| Feedback (FB) OK<br>Threshold                | V <sub>DC_FBOK</sub>    | Voltage rising                                                                                                                     | 92    | 95    | 98    | %V <sub>DC_FB</sub> |

| Feedback (FB) Low<br>Threshold               | V <sub>DC_FBTHLOW</sub> |                                                                                                                                    | 61    | 65    | 70    | %V <sub>DC_FB</sub> |

| LX On-Resistance<br>(High Side)              | R <sub>DC_HS</sub>      | From PV <sub>24</sub> to LX, LX is sinking current (Note 2)                                                                        |       | 2.2   | 3.9   | Ω                   |

| LX On-Resistance<br>(Low Side)               | R <sub>DC_LS</sub>      | From LX to GND (Note 2)                                                                                                            |       | 1.3   | 2.8   | Ω                   |

| Active Diode On-<br>Resistance               | R <sub>DC_ACT</sub>     | DC current (Note 2)                                                                                                                |       | 3     | 5.5   | Ω                   |

| Maximum Peak<br>Current into Active<br>Diode | I <sub>DC_ACTMAX</sub>  |                                                                                                                                    | 300   |       |       | mA                  |

| Maximum LX Current<br>Ripple                 | ΔI <sub>DC_LX</sub>     |                                                                                                                                    |       | 100   |       | %                   |

| High-Side Peak<br>Current Limit              | I <sub>DC_HSLIM</sub>   |                                                                                                                                    | +350  | +400  | +440  | mA                  |

| Low-Side Current<br>Limit                    | IDC_LSMAX               |                                                                                                                                    | -240  | -200  | -150  | mA                  |

| DC-DC Autoretry<br>Period                    | T <sub>DCRETRY</sub>    |                                                                                                                                    |       | 30.6  |       | ms                  |

| External Capacitance on PV <sub>24</sub>     | C <sub>DC_PV24</sub>    |                                                                                                                                    | 1     |       |       | μF                  |

| LX leakage                                   | I <sub>LX_LKG</sub>     | 0V < V <sub>LX</sub> < 36V                                                                                                         | -1    |       | +1    | μA                  |

| FB Input Bias                                | I <sub>FB_LKG</sub>     | 0≤ V <sub>FB</sub> ≤ 1V, T <sub>A</sub> = 25°C                                                                                     | -100  |       | +100  | nA                  |

| LX Minimum On-Time                           | t <sub>LX_MINON</sub>   | (Note 2)                                                                                                                           |       | 64    | 92    | ns                  |

| LX Minimum Off-Time                          | t <sub>LX_MINOFF</sub>  | (Note 2)                                                                                                                           |       | 32    | 60    | ns                  |

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{CQGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ Typical\ values\ are\ at\ V_{24}=24V,\ V_5=5V,\ V_L=3.3V\ and\ T_A=+25^\circ C,\ unless\ otherwise\ noted\ (Note\ 1))$

| PARAMETER                             | SYMBOL                  | CON                                                                                                | IDITIONS                                                 | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|------|------|-------|

| V <sub>CCB</sub> Output Voltage       | V <sub>CCB</sub>        | $8V \le V_{PV24} \le 36V$<br>$0mA \le I_{LOAD} \le 15$                                             |                                                          | 4.75 | 5    | 5.25 | V     |

| V <sub>CCB</sub> Current Limit        | I <sub>CCB_MAX</sub>    | V <sub>PV24</sub> = 8V                                                                             |                                                          | 30   | 55   | 90   | mA    |

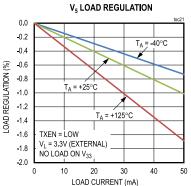

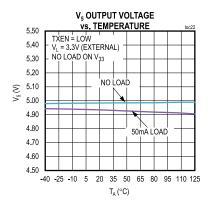

| 5V LINEAR REGULAT                     | OR (V <sub>5</sub> )    |                                                                                                    |                                                          |      |      |      |       |

| LIN Input Supply<br>Voltage           | $V_{LIN}$               |                                                                                                    |                                                          | 6    |      | 36   | V     |

| V <sub>5</sub> Output Voltage         | V <sub>5</sub>          | $6V \le V_{LIN} \le 36V$ ,                                                                         | no load on V <sub>5</sub>                                | 4.75 | 5    | 5.25 | V     |

| V₅ Load Regulation                    | $\Delta V5_{LDR}$       | V <sub>LIN</sub> = 24V, 1mA                                                                        | < I <sub>LOAD</sub> < 50mA                               |      | 0.85 | 2.4  | %     |

| V₅ Line Regulation                    | $\Delta V5_{LNR}$       | $6V \le V_{LIN} \le 36V$ ,                                                                         | I <sub>LOAD</sub> = 1mA                                  |      | 0.02 | 0.2  | mV/V  |

| V₅ Load Capacitance                   | C <sub>V5</sub>         | External capacit                                                                                   | ance on V₅                                               | 1    |      |      | μF    |

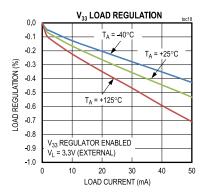

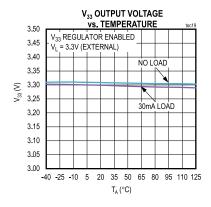

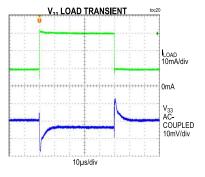

| 3.3V LINEAR REGULA                    | ATOR (V <sub>33</sub> ) |                                                                                                    |                                                          |      |      |      |       |

| V <sub>33</sub> Output Voltage        | V <sub>33</sub>         | No load                                                                                            |                                                          | 3.1  | 3.3  | 3.5  | V     |

| V <sub>33</sub> Load Regulation       | $\Delta V_{33\_LR}$     | 1mA < ILOAD < 5                                                                                    | 0mA                                                      | 0    | 0.18 | 1.2  | %     |

| V <sub>33</sub> Load Capacitance      | Cv33                    | External capaci                                                                                    | tance on V <sub>33</sub>                                 | 1    |      |      | μF    |

| C/Q DRIVER                            |                         | 1                                                                                                  |                                                          |      |      |      | 1     |

| C/Q Driver High-Side<br>On-Resistance | Rсаон                   | (Note 2)                                                                                           | High-side<br>enabled, CL[1:0]<br>= 11,<br>ILOAD = +150mA |      | 2.4  | 4.4  | Ω     |

| C/Q Driver Low-Side<br>On-Resistance  | Rcaol                   | (Note 2)                                                                                           | Low-side<br>enabled, CL[1:0]<br>= 11,<br>ILOAD = -150mA  |      | 2.0  | 4.0  | Ω     |

|                                       |                         |                                                                                                    | CL[1:0] = 00                                             | 50   | 57   | 65   |       |

|                                       |                         | .,                                                                                                 | CL[1:0] = 01                                             | 100  | 114  | 130  |       |

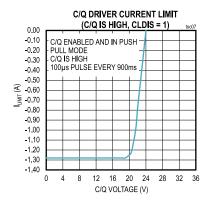

| C/Q Driver Current<br>Limit           | Icacl                   | $V_{DROP} = 3V$ (Note 3)                                                                           | CL[1:0] = 10                                             | 200  | 230  | 260  | mA    |

|                                       |                         | (Note 3)                                                                                           | CL[1:0] = 11                                             | 250  | 290  | 325  | -     |

|                                       |                         |                                                                                                    | WUGEN = 1                                                | 500  |      |      |       |

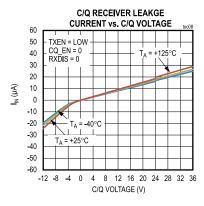

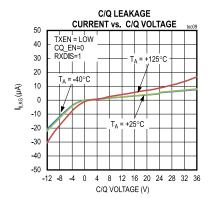

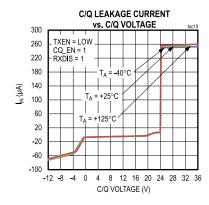

| C/Q Output Reverse<br>Current         | IREV_CQ                 | CQ_EN = 1, CQ<br>0, CQ_PU = 0,<br>V <sub>C/Q</sub> = (V <sub>24</sub> + 5V)                        | $PP = 1, CQ_PD =$ or $(V_{GND} - 5V)$                    | -90  |      | +375 | μΑ    |

| C/Q Leakage Current                   | ILEAK_CQ                | CQ_EN = 0, CQ_PD = 0, CQ_PU = 0, RX_DIS = 0, $V_{24} = 24V$ , $(V_{24} - 36V) \le V_{C/Q} \le 36V$ |                                                          | -35  |      | +60  | μА    |

| C/Q CURRENT SINKS                     | AND SOURC               | ES                                                                                                 |                                                          |      | _    |      |       |

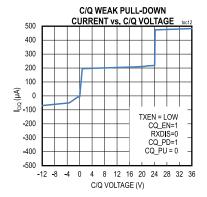

| C/Q Weak Pull-Down<br>Current         | ICQPD                   | V <sub>C/Q</sub> > 5V,<br>CQ_EN = 0, RX                                                            | (_DIS = 1, CQ_PD                                         | -240 | -200 | -160 | μΑ    |

$(V_{24} = 8V \text{ to } 36V, V_5 = 4.5V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{CQGND} = V_{GND} = 0V, \text{ All logic inputs at } V_L \text{ or GND, Typical values are at } V_{24} = 24V, V_5 = 5V, V_L = 3.3V \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted (Note 1))}$

| PARAMETER                              | SYMBOL                  | COND                                              | ITIONS                                                                                                      | MIN                      | TYP | MAX  | UNITS            |

|----------------------------------------|-------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|------------------|

|                                        |                         | = 1, CQ_PU = 0,<br>CQPUD5MA = 0                   | CQPUD2MA = 0,                                                                                               |                          |     |      |                  |

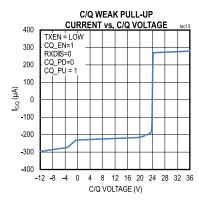

| C/Q Weak Pull-Up<br>Current            | Ісари                   |                                                   | CQ_EN = 0, RX_DIS = 1, CQ_PD = 0, CQ_PU = 1, CQPUD2MA = 0,                                                  |                          |     | +240 | μА               |

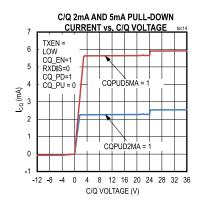

| C/Q 2mA Pull-Down<br>Current           | Icapd2                  |                                                   | CQ_EN = 0, RX_DIS = 1, CQ_PD<br>= 1, CQ_PU = 0, CQPUD2MA = 1,                                               |                          |     | -2.0 | mA               |

| C/Q 2mA Pull-Up<br>Current             | Ісари2                  |                                                   | V <sub>C/Q</sub> = (V <sub>24</sub> - 5V),<br>CQ_EN = 0, RX_DIS = 1, CQ_PD<br>= 0, CQ_PU = 1, CQPUD2MA = 1, |                          |     | +2.6 | mA               |

| C/Q 5mA Pull-Down<br>Current           | Icapd5                  |                                                   | V <sub>C/Q</sub> > 5V,<br>CQ_EN = 0, RX_DIS = 1, CQ_PD<br>= 1, CQ_PU = 0, CQPUD2MA = 0,                     |                          |     | -5.0 | mA               |

| C/Q 5mA Pull-Up<br>Current             | Ісари5                  |                                                   | V <sub>C/Q</sub> = (V <sub>24</sub> - 5V),<br>CQ_EN = 0, RX_DIS = 1, CQ_PD<br>= 0, CQ_PU = 1, CQPUD2MA = 0, |                          |     | +6.5 | mA               |

| C/Q RECEIVER                           |                         | •                                                 |                                                                                                             |                          |     |      |                  |

| C/Q Input Voltage<br>Range             | Vcqin                   | For valid RX logic                                |                                                                                                             | V <sub>24</sub> -<br>36V |     | 36   | V                |

| C/Q Input Threshold                    | .,                      | TXEN = low                                        | V <sub>24</sub> ≥ 18V                                                                                       | 11                       |     | 12.5 | V                |

| High                                   | V <sub>СQТН</sub>       | and/or CQ_EN = 0, RXDIS = 0                       | V <sub>24</sub> < 18V                                                                                       | 54.4                     |     | 78.8 | %V <sub>24</sub> |

| C/Q Input Threshold                    | \/                      | TXEN = low                                        | V <sub>24</sub> ≥ 18V                                                                                       | 9                        |     | 10.5 | V                |

| Low                                    | V <sub>CQTL</sub>       | and/or CQ_EN = 0, RXDIS = 0                       | V <sub>24</sub> < 18V                                                                                       | 45                       |     | 66.9 | %V <sub>24</sub> |

| 0/01                                   | .,                      | TXEN = low                                        | V <sub>24</sub> ≥ 18V                                                                                       |                          | 2   |      | V                |

| C/Q Input Hysteresis                   | Vcqhys                  | and/or CQ_EN = 0, RXDIS = 0                       | V <sub>24</sub> < 18V                                                                                       |                          | 11  |      | %V <sub>24</sub> |

|                                        |                         | TXEN = low                                        | Rising                                                                                                      | 2.1                      |     | 3.45 |                  |

| C/Q Input Threshold<br>High (TTL Mode) | Vcqthttl                | and/or CQ_EN = 0, RXDIS = 0, RXTTL = 1            | Falling                                                                                                     | 1.1                      |     | 1.85 | V                |

| C/Q Input Hysteresis<br>(TTL Mode)     | VcQHYSTTL               |                                                   | TXEN = low and/or CQ_EN = 0,<br>RXDIS = 0, RXTTL = 1                                                        |                          | 1.3 |      | V                |

| C/Q Input<br>Capacitance               | C <sub>IN_CQ</sub>      | Driver disabled, CQ_PD = 0, CQ_PU = 0, f = 100kHz |                                                                                                             |                          | 35  |      | pF               |

| VOLTAGE MONITOR                        | INPUT (V <sub>M</sub> ) |                                                   |                                                                                                             |                          |     |      |                  |

| V <sub>M</sub> Voltage Range           | V <sub>M</sub>          |                                                   |                                                                                                             | 0                        |     | 5.5  | V                |

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{CQGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ Typical\ values\ are\ at\ V_{24}=24V,\ V_5=5V,\ V_L=3.3V\ and\ T_A=+25^\circ C,\ unless\ otherwise\ noted\ (Note\ 1))$

| PARAMETER                                       | SYMBOL                | CONDITIONS                                                                    | MIN                  | TYP   | MAX          | UNITS    |

|-------------------------------------------------|-----------------------|-------------------------------------------------------------------------------|----------------------|-------|--------------|----------|

| V <sub>M</sub> Threshold Voltage                | <b>V</b> тн м         | Rising                                                                        | 0.873                | 0.9   | 0.927        | ٧        |

| VM Threshold Voltage                            | <b>V</b> TH_M         | Falling                                                                       | 0.832                | 0.858 | 0.883        | V        |

| V <sub>M</sub> Input Current                    | I <sub>M</sub>        |                                                                               | -1                   |       | +1           | μA       |

| RESET AND POWER-                                | OK (RESET/PO          | K)                                                                            |                      |       |              |          |

| RESET/POK Input<br>Voltage Low                  | V <sub>RSTIL</sub>    |                                                                               | 0.4                  |       |              | V        |

| RESET/POK Input<br>Voltage High                 | V <sub>RSTIH</sub>    |                                                                               |                      |       | 1.3          | ٧        |

| RESET/POK Output<br>Voltage Low                 | $V_{POKLOW}$          | $I_{LOAD} = -5mA$                                                             |                      |       | 0.4          | <b>V</b> |

| RESET/POK High<br>Impedance Leakage<br>Current  | Irst_od               | RESET/POK not asserted                                                        | -1                   |       | +1           | μΑ       |

| LOGIC INPUTS (CS, S                             | CLK, SDI, SDC         | D, TX, TXEN)                                                                  |                      |       |              |          |

| Logic Input Voltage<br>Low Threshold            | $V_{IL}$              |                                                                               |                      |       | 0.31 x<br>V∟ | V        |

| Logic Input Voltage<br>High Threshold           | V <sub>IH</sub>       |                                                                               | 0.68 x<br>V∟         |       |              | ٧        |

| Logic Input Leakage<br>Current                  | ILEAK                 | Logic input = GND or V <sub>L</sub>                                           | -1                   |       | +1           | μA       |

| LOGIC OUTPUTS (WU                               | , IRQ, <b>SDO, R</b>  | K, MCLK)                                                                      |                      |       |              |          |

| Logic Output Voltage<br>Low                     | VoL                   | IRQ, WU, SDO, RX, MCLK,<br>I <sub>LOAD</sub> = -5mA                           |                      |       | 0.4          | ٧        |

| Logic Output Voltage<br>High                    | V <sub>OH</sub>       | SDO, RX, MCLK,<br>I <sub>LOAD</sub> = +5mA                                    | V <sub>L</sub> - 0.4 |       |              | <b>V</b> |

| Open-Drain High<br>Impedance Leakage<br>Current | I <sub>LK_OD</sub>    | IRQ and WU, not asserted                                                      | -1                   |       | +1           | μΑ       |

| SDO Leakage<br>Current                          | I <sub>LK_SDO</sub>   | CS = high                                                                     | -1                   |       | +1           | μΑ       |

| RX Leakage Current                              | I <sub>LK_RX</sub>    | $RX = GND \text{ or } V_L$                                                    | -1                   |       | +1           | μΑ       |

| THERMAL CHARACT                                 | ERISTICS              |                                                                               |                      |       |              |          |

| C/Q Driver Shutdown<br>Temperature              | T <sub>SHUT_DRV</sub> | Driver temperature rising, C/Q driver fault bit is set and driver is disabled |                      | +160  |              | °C       |

| C/Q Driver Shutdown<br>Hysteresis               | Тѕнит_рнуѕ            | Driver temperature falling, driver is automatically reenabled,  TSHOFFEN = 0  |                      | 15    |              | °C       |

| IC Thermal Warning<br>Threshold                 | $T_{WRN}$             | Die temperature rising, THERMW and THERMWINT bits are set                     |                      | +150  |              | °C       |

| IC Thermal Warning<br>Threshold Hysteresis      | T <sub>WRN_HYS</sub>  | Die temperature falling, THERMW bit is cleared                                |                      | 20    |              | °C       |

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{CQGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ Typical\ values\ are\ at\ V_{24}=24V,\ V_5=5V,\ V_L=3.3V\ and\ T_A=+25^\circ C,\ unless\ otherwise\ noted\ (Note\ 1))$

| PARAMETER                                          | SYMBOL                  |                                              | ITIONS                | MIN  | TYP  | MAX   | UNITS     |

|----------------------------------------------------|-------------------------|----------------------------------------------|-----------------------|------|------|-------|-----------|

| IC Thermal Shutdown<br>Threshold                   | T <sub>SHUT_IC</sub>    | Die temperature ris                          | sing, THSHUTD bit     |      | +170 |       | °C        |

| IC Thermal Shutdown<br>Hysteresis                  | T <sub>SHUT_ICHYS</sub> | Die temperature fa<br>bit is cleared         | lling, THSHUTD        |      | 20   |       | °C        |

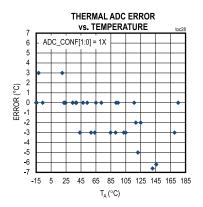

| INTERNAL THERMAL                                   | SENSOR                  | •                                            |                       |      |      |       |           |

| Programmable<br>Thermal Warning<br>Threshold Range | Twrn_rng                | Typical range                                |                       | -15  |      | +174  | °C        |

| Programmable Thermal Warning Threshold Step        | T <sub>WRN_LSB</sub>    | 1 LSB                                        |                       |      | 3    |       | °C        |

| Thermal ADC<br>Resolution                          | T <sub>WRN_RES</sub>    |                                              |                       |      | 6    |       | bit       |

|                                                    | ΔT <sub>PREC_25C</sub>  | T <sub>J</sub> = 27°C (Note 2)               |                       | -8   | 0    | +8    |           |

| Thermal ADC Accuracy                               | ΔT <sub>PREC_85C</sub>  | T <sub>J</sub> = 84°C                        |                       |      | 2    |       | °C        |

| ,                                                  | ΔT <sub>PREC_124C</sub> | $T_J = 126^{\circ}C$ (Note 2                 | 2)                    | -7   | 3    | +12   |           |

| Thermal ADC<br>Conversion Time                     | tadc_conv               |                                              |                       |      | 450  |       | μs        |

| AC ELECTRICAL CHA                                  | RACTERISTIC             | CS                                           |                       |      |      |       |           |

| C/Q DRIVER                                         |                         |                                              |                       |      |      |       |           |

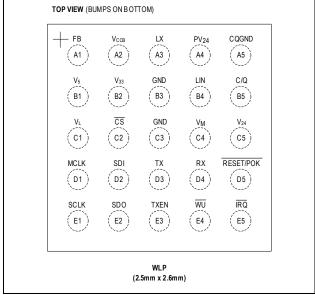

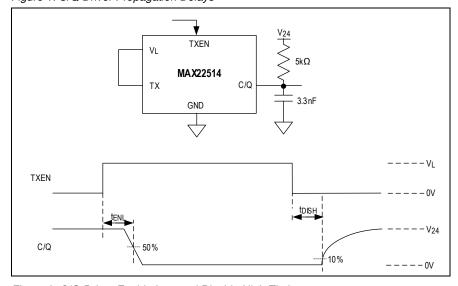

| Driver Low-to-High                                 | tpdlh_pp                | CQLOSLEW[1:0]<br>= 00, <i>Figure 1</i>       | Push-pull or PNP mode |      | 0.6  | 0.8   | lle.      |

| Propagation Delay                                  | tpdlh_oc                | CQLOSLEW[1:0]<br>= 00, <i>Figure 1</i>       | NPN mode              |      | 1.8  |       | μs        |

| Driver High-to-Low                                 | tpdhl_pp                | CQLOSLEW[1:0]<br>= 00, <u>Figure 1</u>       | Push-pull or NPN mode |      | 0.7  | 0.9   | lie.      |

| Propagation Delay                                  | t <sub>PDHL_OC</sub>    | CQLOSLEW[1:0]<br>= 00, <i>Figure 1</i>       | PNP mode              |      | 2    |       | μs        |

| Driver Skew                                        | t <sub>SKEW</sub>       | t <sub>PDLH</sub> - t <sub>PDHL</sub>  , CQL | OSLEW[1:0] = 00       | -0.2 |      | +0.2  | μs        |

|                                                    |                         |                                              | CQLOSLEW[1:0]<br>= 00 | 0.2  | 0.37 | 0.565 |           |

| Driver Bigo Time                                   | 4                       | Push-pull or PNP mode,                       | CQLOSLEW[1:0]<br>= 01 | 0.4  | 0.67 | 1.035 |           |

| Driver Rise Time                                   | trise                   | $V_{24}(max) = 30V,$ <u>Figure 1</u>         | CQLOSLEW[1:0]<br>= 10 | 0.8  | 1.56 | 2.55  | - μs<br>- |

|                                                    |                         |                                              | CQLOSLEW[1:0]<br>= 11 | 2.4  | 6.0  | 11.2  |           |

| Driver Fell Time                                   | <b>t</b> _              | Push-pull or NPN mode,                       | CQLOSLEW[1:0]<br>= 00 | 0.2  | 0.38 | 0.565 |           |

| Driver Fall Time                                   | t <sub>FALL</sub>       | $V_{24}(max) = 30V,$ <u>Figure 1</u>         | CQLOSLEW[1:0]<br>= 01 | 0.45 | 0.76 | 1.08  | μs        |

$(V_{24} = 8V \text{ to } 36V, V_5 = 4.5V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{CQGND} = V_{GND} = 0V$ , All logic inputs at  $V_L$  or GND, Typical values are at  $V_{24} = 24V, V_5 = 5V, V_L = 3.3V$  and  $V_L = 2.5V$ , unless otherwise noted (Note 1))

| PARAMETER                               | SYMBOL                 | CONI                                    | DITIONS                 | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------|------------------------|-----------------------------------------|-------------------------|-------|-------|-------|-------|

|                                         |                        |                                         | CQLOSLEW[1:0]<br>= 10   | 1.2   | 1.87  | 2.7   |       |

|                                         |                        |                                         | CQLOSLEW[1:0]<br>= 11   | 5     | 9     | 14    |       |

| C/Q Driver Enable<br>Time High          | tenh                   | Push-pull or PNP                        | mode, Figure 2          |       | 0.59  | 0.935 | μs    |

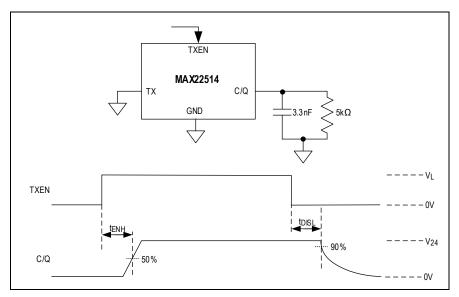

| C/Q Driver Enable<br>Time Low           | tenL                   | Push-pull or NPN                        | N mode, <u>Figure 3</u> |       | 0.45  | 0.7   | μs    |

| C/Q Driver Disable<br>Time High         | tыsн                   | Push-pull or PNF<br>(Note 2)            | P mode, Figure 2        |       | 1.6   | 2.2   | μs    |

| C/Q Driver Disable<br>Time Low          | t <sub>DISL</sub>      | Push-pull or NPN<br>(Note 2)            | N mode, <i>Figure 3</i> |       | 1.3   | 2.4   | μs    |

| C/Q RECEIVER                            |                        |                                         |                         |       |       |       |       |

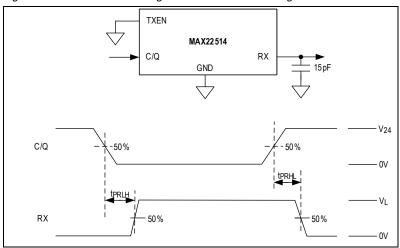

| C/Q Receiver Low-to-                    |                        |                                         | RXFILTER = 1            | 0.825 | 1.22  | 1.6   |       |

| High Propagation<br>Delay               | tprlh_cq               | Figure 4                                | RXFILTER = 0            | 0.24  | 0.28  | 0.43  | μs    |

| C/Q Receiver High-                      |                        | Figure 4                                | RXFILTER = 1            | 0.75  | 1.11  | 1.5   | μs    |

| to-Low Propagation<br>Delay             | tprhl_cq               | <u>Figure 4</u>                         | RXFILTER = 0            | 0.15  | 0.25  | 0.305 |       |

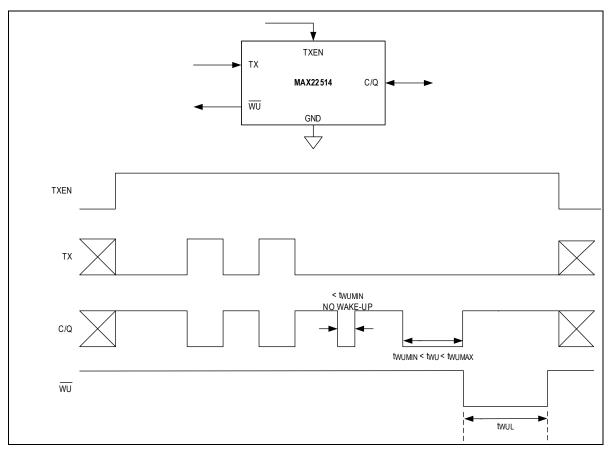

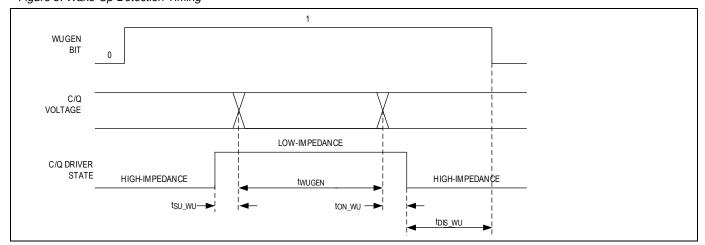

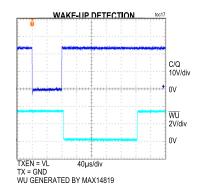

| WAKE-UP DETECTION                       | N ( <i>Figure 5</i> )  |                                         |                         |       |       |       |       |

| Wake-Up Input<br>Minimum Pulse Width    | twumin                 |                                         |                         | 62.2  | 64    | 65.8  | μs    |

| Wake-Up Input<br>Maximum Pulse<br>Width | twuмах                 |                                         |                         | 106   | 109   | 112   | μs    |

| WU Output Low Time                      | twuL                   | Valid wake-up co                        | ndition on C/Q          | 150   | 200   | 250   | μs    |

| WAKE-UP GENERATI                        | ON ( <u>Figure 6</u> ) |                                         |                         |       |       |       |       |

| Setup Time before<br>Wake-Up            | tsu_su                 |                                         |                         |       | 80    |       | μs    |

| Wake-up Pulse<br>Duration               | twugen                 | Wake-up pulse had polarity of the exist |                         | 77.8  | 80    | 82.2  | μs    |

| On-Time after Wake-<br>Up               | t <sub>ON_WU</sub>     | C/Q driver enable polarity after two    | d with original         |       | 2     |       | μs    |

| High Impedance<br>Time after Wake-Up    | tois_wu                | C/Q driver is high ton_wu               | impedance after         |       | 418   |       | μs    |

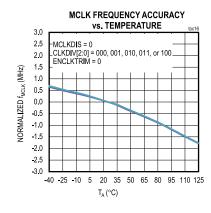

| MCLK CLOCK                              |                        |                                         |                         |       |       |       |       |

|                                         |                        | CLKDIV[2:0] = 0                         | 00                      | 3.594 | 3.686 | 3.779 |       |

|                                         |                        | CLKDIV[2:0] = 001                       |                         | 7.189 | 7.373 | 7.557 |       |

| MCLK Frequency                          | $f_{MCLK}$             | CLKDIV[2:0] = 01                        | 0                       | 14.38 | 14.74 | 15.11 | MHz   |

|                                         |                        | CLKDIV[2:0] = 01                        | 1                       | 28.75 | 29.49 | 30.23 |       |

|                                         |                        | CLKDIV[2:0] = 10                        | 0                       | 1.797 | 1.843 | 1.889 |       |

$(V_{24}=8V\ to\ 36V,\ V_5=4.5V\ to\ 5.5V,\ V_L=2.5V\ to\ 5.5V,\ V_{CQGND}=V_{GND}=0V,\ All\ logic\ inputs\ at\ V_L\ or\ GND,\ Typical\ values\ are\ at\ V_{24}=24V,\ V_5=5V,\ V_L=3.3V\ and\ T_A=+25^{\circ}C,\ unless\ otherwise\ noted\ (Note\ 1))$

| PARAMETER                                        | SYMBOL                  | CONDITIONS                      | MIN | TYP  | MAX | UNITS |

|--------------------------------------------------|-------------------------|---------------------------------|-----|------|-----|-------|

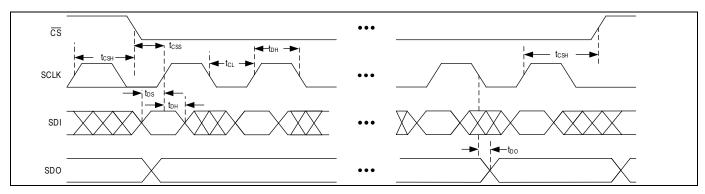

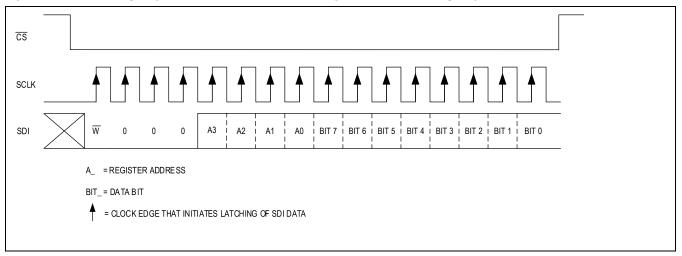

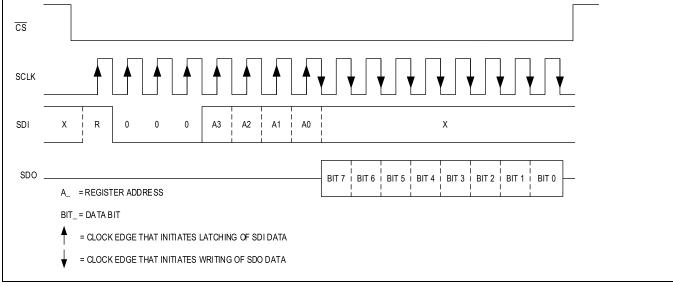

| SPI TIMING (CS, SCLK                             | (, SDI, SDO) ( <u>/</u> | igure 7)                        |     |      |     |       |

| Maximum SCLK<br>Frequency                        | fspi_max                |                                 |     |      | 12  | MHz   |

| SCLK Clock Period                                | t <sub>CH+CL</sub>      |                                 | 35  |      |     | ns    |

| SCLK Pulse Width<br>High                         | tсн                     |                                 | 5   |      |     | ns    |

| SCLK Pulse Width<br>Low                          | tcL                     |                                 | 30  |      |     | ns    |

| CS Fall to SCLK Rise Time                        | tcss                    |                                 | 7   |      |     | ns    |

| SCLK Rise to <sub>CS</sub> Rise<br>Hold Time     | tсsн                    |                                 | 0   |      |     | ns    |

| SDI Hold Time                                    | tон                     |                                 | 3   |      |     | ns    |

| SDI Setup Time                                   | t <sub>DS</sub>         |                                 | 3   |      |     | ns    |

| SDO Output Data<br>Propagation Delay             | t <sub>DO</sub>         |                                 |     |      | 23  | ns    |

| SDO Rise and Fall<br>Times                       | tғт                     |                                 |     | 0.7  |     | ns    |

| Minimum <sup>CS</sup> Pulse                      | tcsw                    |                                 |     | 15   |     | ns    |

| EMC TOLERANCE                                    |                         |                                 | •   |      |     | •     |

| ESD Protection<br>(V <sub>24</sub> , C/Q Pins)   |                         | IEC 61000-4-2 Contact Discharge |     | ±2.5 |     | kV    |

| ESD Protection<br>(All Other Pins)               |                         | Human Body Model                |     | ±1.5 |     | kV    |

| Surge Protection<br>(V <sub>24</sub> , C/Q Pins) | $V_{SRG}$               | 500Ω 8/20μs surge to ground     |     | ±1.2 |     | kV    |

- Note 1: All devices are 100% production tested at  $T_A = 25$ °C. Limits over the operating temperature range are guaranteed by design.

- Note 2: Not production tested. Guaranteed by design.

- Note 3:  $V_{DROP}$  is measured as the voltage from the driver output to GND ( $V_{DRIVER}$   $V_{GND}$ ) when measuring the low-side driver current limit and as ( $V_{24}$   $V_{DRIVER}$ ) when measuring the high-side current limit.

## **Timing Diagrams**

Figure 1. C/Q Driver Propagation Delays

Figure 2. C/Q Driver Enable Low and Disable High Timing

Figure 3. C/Q Driver Enable High and Disable Low Timing

Figure 4. C/Q Receiver Timing

Figure 5. Wake-Up Detection Timing

Figure 6. Wake-Up Generation

Figure 7. SPI Timing Diagram

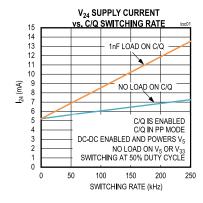

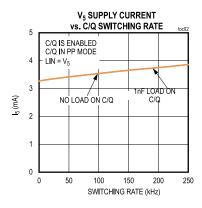

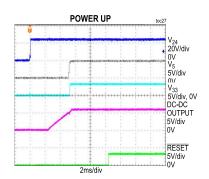

## **Typical Operating Characteristics**

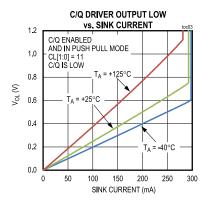

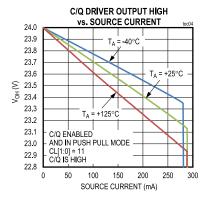

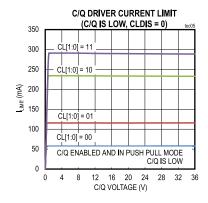

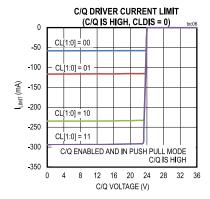

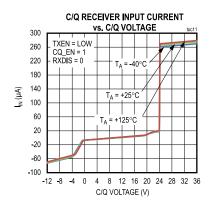

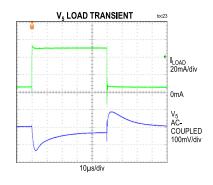

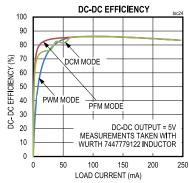

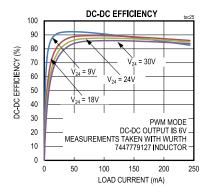

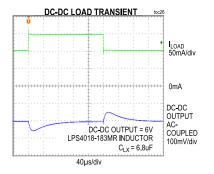

$V_{24}$  = 24V, DC-DC regulator is enabled and connected to LIN,  $V_L$  =  $V_{33}$ ,  $T_A$  = +25°C, unless otherwise noted.

V<sub>24</sub> = 24V, DC-DC regulator is enabled and connected to LIN, V<sub>L</sub> = V<sub>33</sub>, T<sub>A</sub> = +25°C, unless otherwise noted.

V<sub>24</sub> = 24V, DC-DC regulator is enabled and connected to LIN, V<sub>L</sub> = V<sub>33</sub>, T<sub>A</sub> = +25°C, unless otherwise noted.

## **Pin Configurations**

## **Pin Descriptions**

| PIN      |           |                  |                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN     | WLP       | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                               |

| SUPPLY   | •         |                  |                                                                                                                                                                                                                                                                                                                                                                        |

| 3        | A2        | V <sub>CCB</sub> | Internal 5V Supply Regulator Output. Bypass V <sub>CCB</sub> to GND with a 1µF capacitor as close to the device as possible. V <sub>CCB</sub> can supply an external load up to 5mA.                                                                                                                                                                                   |

| 6        | A4        | PV <sub>24</sub> | Active Diode Output and DC-DC Input. Bypass PV <sub>24</sub> with an external 1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                        |

| 7        | B4        | LIN              | 5V Linear Regulator Input. Connect LIN to the output of the DC-DC circuit, the PV $_{24}$ supply, or an external supply between 6V and 36V. Bypass LIN to GND with a 1 $\mu$ F capacitor. Connect LIN to V $_{5}$ to disable the 5V linear regulator.                                                                                                                  |

| 1        | B1        | V <sub>5</sub>   | 5V Linear Regulator Output/ Supply Input. $V_5$ is the output of the internal 5V linear regulator. Bypass $V_5$ to GND with a 1µF capacitor as close to the device as possible. To disable the 5V linear regulator, connect LIN to $V_5$ . 5V is required on $V_5$ for normal operation. If the 5V regulator is disabled, apply an external 5V power supply to $V_5$ . |

| 10       | C5        | V <sub>24</sub>  | Supply Voltage Input. Connect $V_{24}$ to the L+ terminal of the IO-Link connector, or to an external supply. Bypass $V_{24}$ to GND with a 10nF capacitor as close to the device as possible.                                                                                                                                                                         |

| 8        | A5        | CQGND            | C/Q Driver IO-Link Ground. Connect CQGND to the L- terminal of the IO-Link connector and to GND. See the <i>Layout and Grounding</i> section for more information.                                                                                                                                                                                                     |

| 23       | C1        | VL               | Logic Supply Input. Bypass $V_L$ to GND with a $1\mu F$ capacitor as close to the device as possible. $V_L$ sets the logic levels for all logic signals. Connect $V_L$ to $V_{33}$ , $V_5$ , or to an external voltage between 2.5V and 5.5V.                                                                                                                          |

| 5        | B3, C3    | GND              | Ground. Connect GND to CQGND. See the <u>Layout and Grounding</u> section for more information.                                                                                                                                                                                                                                                                        |

| 24       | B2        | V <sub>33</sub>  | $3.3V$ Linear Regulator Output. Bypass $V_{33}$ to GND with a $1\mu F$ capacitor as close to the device as possible.                                                                                                                                                                                                                                                   |

| EP       | -         | EP               | Exposed Pad. Connect EP to GND. See the <u>Layout and Grounding</u> section for more information.                                                                                                                                                                                                                                                                      |

| DC-DC RE | GULATOR   | •                |                                                                                                                                                                                                                                                                                                                                                                        |

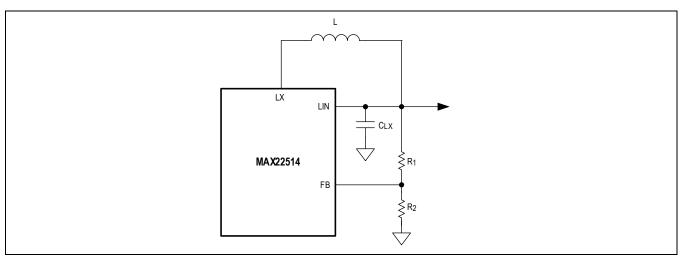

| 4        | A3        | LX               | Switching Output of the Integrated DC-DC Converter. Connect an inductor between LX and the output capacitor to generate a voltage with the DC-DC circuit. See the <u>DC-DC Component Selection</u> section for more information.                                                                                                                                       |

| 2        | A1        | FB               | DC-DC Buck Regulator Feedback Input. Connect FB to the tap of a resistor divider between the output of the DC-DC and GND. See $\underline{\textit{Table 4}}$ for recommended component values to set the DC-DC output between 2.5V and 12V. Connect FB to $V_{\text{CCB}}$ if the DC-DC is not used.                                                                   |

| 24V LINE | INTERFACE |                  |                                                                                                                                                                                                                                                                                                                                                                        |

| 9        | B5        | C/Q              | IO-Link Transceiver Input/ Output. The C/Q driver is disabled at startup. Set CQ_EN = 1 and TXEN = high to enable the C/Q driver.                                                                                                                                                                                                                                      |

| CONTROL  | INTERFAC  | E                |                                                                                                                                                                                                                                                                                                                                                                        |

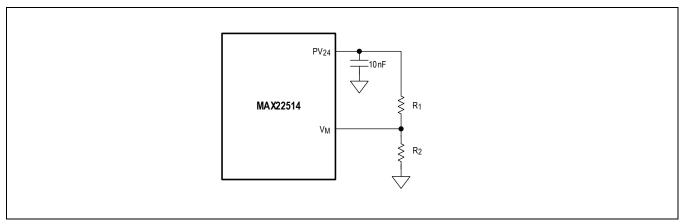

| 11       | C4        | V <sub>M</sub>   | Voltage Monitor Input. Connect a resistor divider between the monitored supply voltage (e.g. V <sub>24</sub> or PV <sub>24</sub> ) and GND to define the power-OK threshold voltage for the monitored supply voltage. See the <u>Voltage Monitor Input (VM)</u> section for more information.                                                                          |

|          | 1      | <b>,</b>      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12       | D5     | RESET/P<br>OK | Dual Function Active-Low Reset Input and Open-Drain Power-OK (POK) Output. Drive RESET/POK low to set the MAX22514 in reset mode. The C/Q output is disabled and all registers are reset to default values when RESET/POK is driven low. The MAX22514 asserts RESET/POK low when any of the V <sub>24</sub> , V <sub>5</sub> , or DC-DC output voltages are below their respective undervoltage lockout (UVLO) thresholds. Only V <sub>5</sub> is monitored when the DC-DC regulator is disabled. The MAX22514 deasserts RESET/POK 4ms (typ) after the power supplies rise above their UVLO thresholds. Connect RESET/POK to V <sub>CCB</sub> or V <sub>L</sub> with a 10k $\Omega$ (typ) resistor for normal operation. |

| 14       | E4     | WU            | Open-Drain IO-Link Wake-Up Request Output. WU asserts low for 200µs (typ) when a valid IO-Link wake-up pulse is detected on the C/Q line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13       | E5     | IRQ           | Active-Low Open-Drain Interrupt Request Output. IRQ asserts low when a bit is set in the INTERRUPT register. See the Register Details section for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18       | E2     | SDO           | Serial Data Output. Connect SDO on the MAX22514 to the MISO input on the SPI master. SDO is high impedance when CS is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19       | E1     | SCLK          | Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 20       | D2     | SDI           | Serial Data Input. Connect SDI on the MAX22514 to the MOSI output on the SPI master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21       | C2     | CS            | SPI Chip-Select Input. Drive CS low to start a read/write cycle. The cycle ends when CS is driven high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UART INT | ERFACE | •             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15       | D4     | RX            | C/Q Receiver Logic Output. RX is inverted, relative to the logic state of C/Q, by default. Set the INVCQ bit in the CQCONFIG register to set RX to the same logic state as C/Q. Connect RX to the RX input of the UART for IO-Link communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16       | E3     | TXEN          | C/Q Driver Enable Logic Input. Drive TXEN high and set the CQ_EN bit in the CQCONFIG register to enable the C/Q driver. Drive TXEN low to disable the C/Q driver. Connect TXEN to the RTS output of a microcontroller for IO-Link communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17       | D3     | TX            | C/Q Driver Logic Input. TX is inverted, relative to the logic state of C/Q, by default. Set the INVCQ bit in the CQCONFIG register to set TX to the same logic state as C/Q. Connect TX to the TX output of the UART for IO-Link communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLOCK O  | UTPUT  |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22       | D1     | MCLK          | Microcontroller Clock Output. Set the MCLK frequency by setting the CLKDIV bits in the CLKCONFIG register. Connect MCLK to an external microcontroller for comparison and trimming. The MCLK frequency is 3.686MHz (typ) by default, but can be disabled or programmed to 3.686MHz, 7.373MHz, 14.74MHz, 29.49MHz, or 1.843MHz.                                                                                                                                                                                                                                                                                                                                                                                           |

## **Functional Diagrams**

## **Detailed Description**

The MAX22514 IO-Link transceiver integrates high voltage functionality, including one 24V line driver, an integrated DC-DC buck regulator, and 5V and 3.3V linear regulators. The MAX22514 is targeted for IO-Link devices, masters, and industrial switching sensor applications, and can be configured and monitored using a standard SPI interface.

#### 24V Interface I/O (C/Q)

The MAX22514 features an IO-Link transceiver interface capable of operating with voltages up to 36V. This is the industrial standard 24V interface and includes the C/Q input/output, the V24 supply, and ground. The C/Q switching driver is programmable for PNP, NPN, or push-pull mode, features a programmable current limit, slew rate, and pull-up/pull-down currents, and operates over all of the COM1, COM2, and COM3 IO-Link data rates.

The C/Q driver is enabled when TXEN is high and the CQ\_EN = 1 in the CQCONFIG register. Toggle the TX input to switch the C/Q output. Alternatively, set the CQ\_Q bit in the CONTROL register to set C/Q high or low. See <u>Table 1</u> and <u>Table 2</u>. C/Q is the logic inverse of the TX input, by default. Set the INVCQ = 1 in the CQCONFIG register to align the TX, C/Q, and RX logic states.

Table 1. C/Q Driver Control (CQINV = 0)

| INPUTS |      |    |      |                | C/Q OUTPUT                |        |  |  |

|--------|------|----|------|----------------|---------------------------|--------|--|--|

| CQ_EN  | TXEN | TX | CQ_Q | NPN MODE       | NPN MODE PNP MODE PP MODE |        |  |  |

| 0      | X    | X  | X    | C/Q Driver Dis | C/Q Driver Disabled       |        |  |  |

|        | L    | X  | X    | HIGH Z         | HIGH Z                    | HIGH Z |  |  |

|        |      |    | 0    | HIGH Z         | HIGH                      | HIGH   |  |  |

| 1      | 1    | L  | 1    | HIGH Z         | HIGH                      | HIGH   |  |  |

|        | H    | 11 | 0    | LOW            | LOW HIGH Z                |        |  |  |

|        |      | Н  | 1    | HIGH Z         | HIGH                      | HIGH   |  |  |

X = Don't care

Table 2. C/Q Receiver Logic

|       | INPU  | ОИТРИТ |     |        |

|-------|-------|--------|-----|--------|

| RXDIS | CQ_EN | CQINV  | C/Q | RX     |

|       |       |        | L   | Н      |

|       | V     | 0      | Н   | L      |

| U     | X     | 1      | L   | L      |

|       |       |        | Н   | Н      |

| 1     | Х     | Х      | Х   | HIGH Z |

X = Don't care

#### **Overcurrent Limiting**

The C/Q driver features a programmable current limit. Select the current limit by setting the CL[1:0] bits in the CURRLIM register. Current limit thresholds can be set to 50mA (min), 100mA (min), 200mA (min), and 250mA (min). When the load attempts to draw more current than the current limit threshold setting, the C/Q driver actively limits the load current so a higher load current does not flow.

Setting CLDIS = 1 disables active current limiting, resulting in higher load currents. Setting CLDIS = 1 should only be done in PNP mode. Setting CLDIS = 1 in NPN or push-pull modes can damage the device.

#### Autoretry

The MAX22514 features an autoretry function to mange and limit heating and power dissipation during driver overload conditions.