Document Number: MC33883

Rev 10.0, 10/2012

# H-Bridge Gate Driver IC

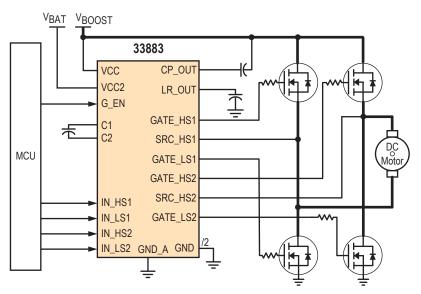

The 33883 is an H-bridge gate driver (also known as a full-bridge pre-driver) IC with integrated charge pump and independent high and low side gate driver channels. The gate driver channels are independently controlled by four separate input pins, thus allowing the device to be optionally configured as two independent high side gate drivers and two independent low side gate drivers. The low side channels are referenced to ground. The high side channels are floating.

The gate driver outputs can source and sink up to 1.0 A peak current pulses, permitting large gate-charge MOSFETs to be driven and/or high pulse- width modulation (PWM) frequencies to be utilized. A linear regulator is incorporated, providing a 15 V typical gate supply to the low side gate drivers.

This device powered by SMARTMOS technology.

#### **Features**

- V<sub>CC</sub> operating voltage range from 5.5 V up to 55 V

- V<sub>CC2</sub> operating voltage range from 5.5 V up to 28 V

- CMOS/LSTTL compatible I/O

- · 1.0 A peak gate driver current

- · Built-in high side charge pump

- Under-voltage lockout (UVLO)

- Over-voltage lockout (OVLO)

- Global enable with <10 μA Sleep mode</li>

- · Supports PWM up to 100 kHz

# 33883

#### H-BRIDGE GATE DRIVER IC

| ORDERING INFORMATION                           |                                        |          |  |  |  |  |

|------------------------------------------------|----------------------------------------|----------|--|--|--|--|

| Device<br>(Add R2 Suffix for<br>Tape and Reel) | Temperature<br>Range (T <sub>A</sub> ) | Package  |  |  |  |  |

| MC33883HEG                                     | -40 °C to 125 °C                       | 20 SOICW |  |  |  |  |

Figure 1. 33883 Simplified Application Diagram

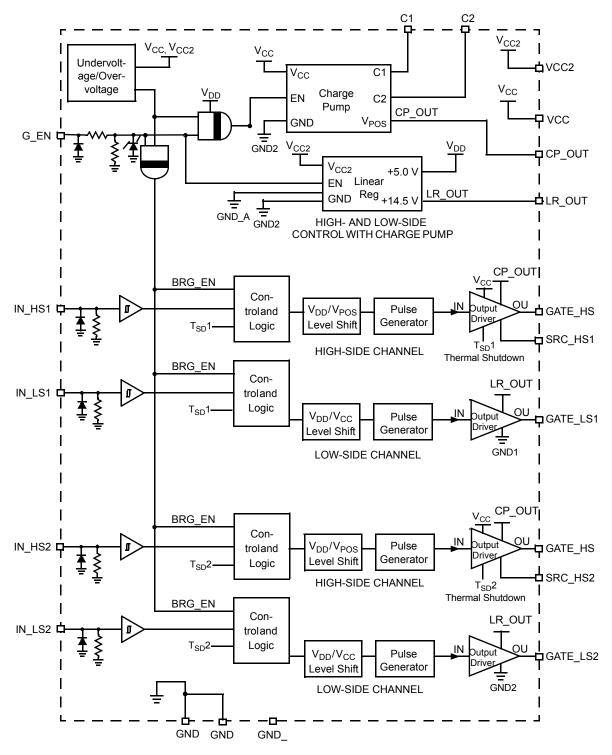

## INTERNAL BLOCK DIAGRAM

Figure 2. 33883 Simplified Internal Block Diagram

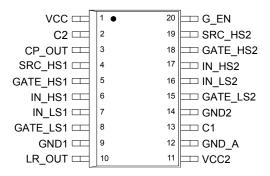

# **PIN CONNECTIONS**

Figure 3. 33883 20-SOICW Pin Connections

A functional description of each pin can be found in the Functional Pin Description section beginning on page 10.

Table 1. 20-SOICW Pin Definitions

| Pin | Pin Name     | Formal Name               | Definition                                                                                                  |

|-----|--------------|---------------------------|-------------------------------------------------------------------------------------------------------------|

| 1   | VCC          | Supply Voltage 1          | Device power supply 1.                                                                                      |

| 2   | C2           | Charge Pump Capacitor     | External capacitor for internal charge pump.                                                                |

| 3   | CP_OUT       | Charge Pump Out           | External reservoir capacitor for internal charge pump.                                                      |

| 4   | SRC_HS1      | Source 1 Output High Side | Source of high-side 1 MOSFET                                                                                |

| 5   | GATE_HS<br>1 | Gate 1 Output High Side   | Gate of high-side 1 MOSFET.                                                                                 |

| 6   | IN_HS1       | Input High Side 1         | Logic input control of high-side 1 gate (i.e., IN_HS1 logic HIGH = GATE_HS1 HIGH).                          |

| 7   | IN_LS1       | Input Low Side 1          | Logic input control of low-side 1 gate (i.e., IN_LS1 logic HIGH = GATE_LS1 HIGH).                           |

| 8   | GATE_LS1     | Gate 1 Output Low Side    | Gate of low-side 1 MOSFET.                                                                                  |

| 9   | GND1         | Ground 1                  | Device ground 1.                                                                                            |

| 10  | LR_OUT       | Linear Regulator Output   | Output of internal linear regulator.                                                                        |

| 11  | VCC2         | Supply Voltage 2          | Device power supply 2.                                                                                      |

| 12  | GND_A        | Analog Ground             | Device analog ground.                                                                                       |

| 13  | C1           | Charge Pump Capacitor     | External capacitor for internal charge pump.                                                                |

| 14  | GND2         | Ground 2                  | Device ground 2.                                                                                            |

| 15  | GATE_LS2     | Gate 2 Output Low Side    | Gate of low-side 2 MOSFET.                                                                                  |

| 16  | IN_LS2       | Input Low Side 2          | Logic input control of low-side 2 gate (i.e., IN_LS2 logic HIGH = GATE_LS2 HIGH).                           |

| 17  | IN_HS2       | Input High Side 2         | Logic input control of high-side 2 gate (i.e., IN_HS2 logic HIGH = GATE_HS2 HIGH).                          |

| 18  | GATE_HS<br>2 | Gate 2 Output High Side   | Gate of high-side 2 MOSFET.                                                                                 |

| 19  | SRC_HS2      | Source 2 Output High Side | Source of high-side 2 MOSFET.                                                                               |

| 20  | G_EN         | Global Enable             | Logic input Enable control of device (i.e., G_EN logic HIGH = Full Operation, G_EN logic LOW = Sleep Mode). |

# **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### **Table 2. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                                                               | Symbol                                        | Value                       | Unit |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|------|

| ELECTRICAL RATINGS                                                                                                   |                                               |                             |      |

| Supply Voltage 1                                                                                                     | V <sub>CC</sub>                               | -0.3 to 65                  | V    |

| Supply Voltage 2 <sup>(1)</sup>                                                                                      | V <sub>CC2</sub>                              | -0.3 to 35                  | V    |

| Linear Regulator Output Voltage                                                                                      | V <sub>LR_OUT</sub>                           | -0.3 to 18                  | V    |

| High-Side Floating Supply Absolute Voltage                                                                           | V <sub>CP_OUT</sub>                           | -0.3 to 65                  | V    |

| High-Side Floating Source Voltage                                                                                    | V <sub>SRC_HS</sub>                           | -2.0 to 65                  | V    |

| High-Side Source Current from CP_OUT in Switch ON State                                                              | Is                                            | 250                         | mA   |

| High-Side Gate Voltage                                                                                               | V <sub>GATE_HS</sub>                          | -0.3 to 65                  | V    |

| High-Side Gate Source Voltage (2)                                                                                    | V <sub>GATE_HS</sub> -<br>V <sub>SRC_HS</sub> | -0.3 to 20                  | V    |

| High-Side Floating Supply Gate Voltage                                                                               | V <sub>CP_OUT</sub> -<br>V <sub>GATE_HS</sub> | -0.3 to 65                  | V    |

| Low-Side Gate Voltage                                                                                                | V <sub>GATE_LS</sub>                          | -0.3 to 17                  | V    |

| Wake-Up Voltage                                                                                                      | V <sub>G_EN</sub>                             | -0.3 to 35                  | V    |

| Logic Input Voltage                                                                                                  | V <sub>IN</sub>                               | -0.3 to 10                  | V    |

| Charge Pump Capacitor Voltage                                                                                        | V <sub>C1</sub>                               | -0.3 to V <sub>LR_OUT</sub> | V    |

| Charge Pump Capacitor Voltage                                                                                        | V <sub>C2</sub>                               | -0.3 to 65                  | V    |

| ESD Voltage <sup>(3)</sup> Human Body Model on All Pins (V <sub>CC</sub> and V <sub>CC2</sub> as Two Power Supplies) | V <sub>ESD1</sub>                             | ±1500                       | V    |

| Machine Model                                                                                                        | V <sub>ESD2</sub>                             | ±130                        |      |

#### Notes

- 1.  $V_{CC2}$  can sustain load dump pulse of 40 V, 400 ms, 2.0  $\Omega$ .

- In case of high current (SRC\_HS>100 mA) and high voltage (>20 V) between GATE\_HSX and SRC\_HS an external zener of 18 V is needed as shown in <u>Figure 14</u>.

- 3. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$ =100 pF,  $R_{ZAP}$ =1500  $\Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ ).

#### Table 2. Maximum Ratings

MC33xxxD enter 33xxx), and review parametrics.

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                    | Symbol                             | Value                | Unit     |

|---------------------------------------------------------------------------|------------------------------------|----------------------|----------|

| Power Dissipation and Thermal Characteristics                             | _                                  |                      |          |

| Maximum Power Dissipation @ 25°C Thermal Resistance (Junction to Ambient) | P <sub>D</sub><br>R <sub>θJA</sub> | 1.25<br>100          | °C/W     |

| Operating Junction Temperature Storage Temperature                        | TJ                                 | -40 to 150           | °C<br>°C |

| Peak Package Reflow Temperature During Reflow (4), (5)                    | T <sub>STG</sub>                   | -65 to 150<br>Note 5 | °C       |

| T can't achage reliew temperature burning reliew ,                        | PPRI                               | Note 5               |          |

#### Notes

- 4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e.

#### STATIC ELECTRICAL CHARACTERISTICS

# **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions  $V_{CC}$  = 12 V,  $V_{CC2}$  = 12 V,  $C_{CP}$  = 33 nF,  $G_{EN}$  = 4.5 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Symbol              | Min                                    | Тур              | Max                             | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------|------------------|---------------------------------|------|

| OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     | 1                                      |                  | 1                               |      |

| Supply Voltage 1 for Output High-Side Driver and Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>CC</sub>     | 5.5                                    | -                | 55                              | V    |

| Supply Voltage 2 for Linear Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>CC2</sub>    | 5.5                                    | -                | 28                              | V    |

| High-Side Floating Supply Absolute Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>CP_OUT</sub> | V <sub>CC</sub> +4                     | -                | V <sub>CC</sub> +11<br>but < 65 | V    |

| LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |                                        |                  | •                               | ,    |

| Logic 1 Input Voltage (IN_LS and IN_HS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>IH</sub>     | 2.0                                    | _                | 10                              | V    |

| Logic 0 Input Voltage (IN_LS and IN_HS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>IL</sub>     | _                                      | _                | 0.8                             | V    |

| Logic 1 Input Current V <sub>IN</sub> = 5.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>IN+</sub>    | 200                                    | _                | 1000                            | μА   |

| Wake-Up Input Voltage (G_EN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>G_EN</sub>   | 4.5                                    | 5.0              | V <sub>CC2</sub>                | V    |

| Wake-Up Input Current (G_EN) $V_{G\_EN} = 14 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sub>G_EN</sub>   | _                                      | 200              | 500                             | μА   |

| Wake-Up Input Current (G_EN) $V_{G\_EN} = 28 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sub>G_EN2</sub>  | _                                      | _                | 1.5                             | mA   |

| LINEAR REGULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     | I I                                    |                  | ı                               |      |

| Linear Regulator $V_{LR\_OUT} @ V_{CC2} \text{ from 15 V to 28 V, I}_{LOAD} \text{ from 0 mA to 20 mA} \\ V_{LR\_OUT} @ I_{LOAD} = 20 \text{ mA} \\ V_{LR\_OUT} @ I_{LOAD} = 20 \text{ mA, V}_{CC2} = 5.5 \text{ V, V}_{CC} = 5.5 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>LR_OUT</sub> | 12.5<br>V <sub>CC2</sub> -1.5<br>4.0   | -<br>-<br>-      | 16.5<br>-<br>-                  | V    |

| CHARGE PUMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | <u> </u>                               |                  |                                 | 1    |

| Charge Pump Output Voltage, Reference to VCC $V_{CC} = 12 \text{ V, I}_{LOAD} = 0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ $V_{CC} = 12 \text{ V, I}_{LOAD} = 7.0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ $V_{CC2} = V_{CC} = 5.5 \text{ V, I}_{LOAD} = 0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ $V_{CC2} = V_{CC} = 5.5 \text{ V, I}_{LOAD} = 7.0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ $V_{CC} = 55 \text{ V, I}_{LOAD} = 0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ $V_{CC} = 55 \text{ V, I}_{LOAD} = 7.0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ $V_{CC} = 55 \text{ V, I}_{LOAD} = 7.0 \text{ mA, C}_{CP\_OUT} = 1.0 \mu\text{F}$ | V <sub>CP</sub> OUT | 7.5<br>7.0<br>2.3<br>1.8<br>7.5<br>7.0 | -<br>-<br>-<br>- | -<br>-<br>-<br>-                | V    |

| Peak Current Through Pin C1 Under Rapidly Changing VCC Voltages (see Figure 13, page 17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>C1</sub>     | -2.0                                   | _                | 2.0                             | А    |

| Minimum Peak Voltage at Pin C1 Under Rapidly Changing VCC Voltages (see Figure 13, page 17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>C1</sub> MIN | -1.5                                   | _                | -                               | V    |

# Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $V_{CC}$  = 12 V,  $V_{CC2}$  = 12 V,  $C_{CP}$  = 33 nF,  $G_{EN}$  = 4.5 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                      | Symbol                 | Min  | Тур | Max | Unit |

|-------------------------------------------------------------------------------------|------------------------|------|-----|-----|------|

| SUPPLY VOLTAGE                                                                      |                        |      |     |     | 1    |

| Quiescent VCC Supply Current                                                        | IV <sub>CCSLEEP</sub>  |      |     |     | μА   |

| $V_{G\_EN} = 0 V$ and $V_{CC} = 55 V$                                               |                        | -    | _   | 10  |      |

| $V_{G\_EN}$ = 0 V and $V_{CC}$ = 12 V                                               |                        | _    | _   | 10  |      |

| Operating VCC Supply Current <sup>(6)</sup>                                         | IV <sub>CCOP</sub>     |      |     |     | mA   |

| $V_{CC}$ = 55 V and $V_{CC2}$ = 28 V                                                |                        | _    | 2.2 | _   |      |

| $V_{CC}$ = 12 V and $V_{CC2}$ = 12 V                                                |                        | _    | 0.7 | -   |      |

| Additional Operating V <sub>CC</sub> Supply Current for Each Logic Input Pin Active | IV <sub>CCLOG</sub>    |      |     |     | mA   |

| $V_{CC}$ = 55 V and $V_{CC2}$ = 28 V $^{(7)}$                                       |                        | -    | _   | 5.0 |      |

| Quiescent VCC2 Supply Current                                                       | IV <sub>CC2SLEEP</sub> |      |     |     | μА   |

| $V_{G\_EN} = 0 V$ and $V_{CC} = 12 V$                                               |                        | _    | _   | 5.0 |      |

| $V_{G\_EN}$ = 0 V and $V_{CC}$ = 28 V                                               |                        | -    | _   | 5.0 |      |

| Operating VCC2 Supply Current <sup>(6)</sup>                                        | IV <sub>CC2OP</sub>    |      |     |     | mA   |

| $V_{CC}$ = 55 V and $V_{CC2}$ = 28 V                                                |                        | -    | _   | 12  |      |

| $V_{CC}$ = 12 V and $V_{CC2}$ = 12 V                                                |                        | _    | _   | 9.0 |      |

| Additional Operating VCC2 Supply Current for Each Logic Input Pin Active            | IV <sub>CC2LOG</sub>   |      |     |     | mA   |

| $V_{CC}$ = 55 V and $V_{CC2}$ = 28 V $^{(7)}$                                       |                        |      |     |     |      |

|                                                                                     |                        | -    | _   | 5.0 |      |

| Undervoltage Shutdown VCC                                                           | UV                     | 4.0  | 5.0 | 5.5 | V    |

| Undervoltage Shutdown VCC2 (8)                                                      | UV2                    | 4.0  | 5.0 | 5.5 | V    |

| Overvoltage Shutdown VCC                                                            | OV                     | 57   | 61  | 65  | V    |

| Overvoltage Shutdown VCC2                                                           | OV2                    | 29.5 | 31  | 35  | V    |

| ОИТРИТ                                                                              |                        |      | •   |     | 1.   |

| Output Sink Resistance (Turned Off)                                                 | R <sub>DS</sub>        |      |     |     | Ω    |

| $I_{discharge LSS} = 50 \text{ mA}$ , $V_{SRC\_HS} = 0 \text{ V}^{(8)}$             |                        | _    | -   | 22  |      |

| Output Source Resistance (Turned On)                                                | R <sub>DS</sub>        |      |     |     | Ω    |

| Icharge HSS = 50 mA, $^{V}CP_{OUT}$ = 20 $^{V}$ (8)                                 |                        | -    | _   | 22  |      |

| Charge Current of the External High-Side MOSFET Through GATE_HSn Pin $^{(9)}$       | ICHARGE HSS            | _    | 100 | 200 | mA   |

| Maximum Voltage (V <sub>GATE_HS</sub> - V <sub>SRC_HS</sub> )                       | VMAX                   |      |     |     | V    |

| INH = Logic 1, I <sub>S</sub> max = 5.0 mA                                          |                        | -    | _   | 18  |      |

# Notes

- 6. Logic input pin inactive (high impedance).

- 7. High-frequency PWM-ing (» 20 kHz) of the logic inputs will result in greater power dissipation within the device. Care must be taken to remain within the package power handling rating.

- 8. The device may exhibit predictable behavior between 4.0 V and 5.5 V.

- 9. See Figure 5, page 12, for a description of charge current.

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                             | Symbol          | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| TIMING CHARACTERISTICS                                                                     |                 |     |     |     | •    |

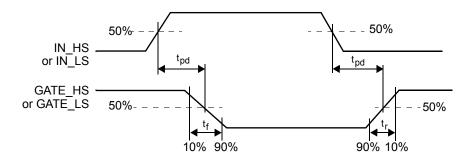

| Propagation Delay High Side and Low Side                                                   | t <sub>PD</sub> |     |     |     | ns   |

| C <sub>LOAD</sub> = 5.0 nF, Between 50% Input to 50% Output <sup>(10)</sup> (see Figure 4) |                 | -   | 200 | 300 |      |

| Turn-On Rise Time                                                                          | t <sub>R</sub>  |     |     |     | ns   |

| $C_{LOAD}$ = 5.0 nF, 10% to 90% <sup>(10)</sup> , <sup>(11)</sup> (see <u>Figure 4</u> )   |                 | -   | 80  | 180 |      |

| Turn-Off Fall Time                                                                         | t <sub>F</sub>  |     |     |     | ns   |

| $C_{LOAD}$ = 5.0 nF, 10% to 90% <sup>(10)</sup> , <sup>(11)</sup> (see <u>Figure 4</u> )   |                 | -   | 80  | 180 |      |

<sup>10.</sup> C<sub>LOAD</sub> corresponds to a capacitor between GATE\_HS and SRC\_HS for the high side and between GATE\_LS and ground for low side.

<sup>11.</sup> Rise time is given by time needed to change the gate from 1.0 V to 10 V (vice versa for fall time).

# **TIMING DIAGRAMS**

Figure 4. Timing Characteristics

#### **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

The 33883 is an H-bridge gate driver (or full-bridge predriver) with integrated charge pump and independent highand low-side driver channels. It has the capability to drive large gate-charge MOSFETs and supports high PWM frequency. In sleep mode its supply current is very low.

#### **FUNCTIONAL PIN DESCRIPTION**

#### **SUPPLY VOLTAGE PINS (VCC AND VCC2)**

The VCC and VCC2 pins are the power supply inputs to the device.  $V_{CC}$  is used for the output high-side drivers and the charge pump.  $V_{CC2}$  is used for the linear regulation. They can be connected together or independent with different voltage values. The device can operate with  $V_{CC}$  up to 55 V and  $V_{CC2}$  up to 28 V.

The VCC and VCC2 pins have undervoltage (UV) and overvoltage (OV) shutdown. If one of the supply voltage drops below the undervoltage threshold or rises above the overvoltage threshold, the gate outputs are switched LOW in order to switch off the external MOSFETs. When the supply returns to a level that is above the UV threshold or below the OV threshold, the device resumes normal operation according to the established condition of the input pins.

# INPUT HIGH- AND LOW-SIDE PINS (IN\_HS1, IN\_HS2, AND IN\_LS1, IN\_LS2)

The IN\_HSn and IN\_LSn pins are input control pins used to control the gate outputs. These pins are 5.0 V CMOS-compatible inputs with hysteresis. IN\_HSn and IN\_LSn independently control GATE\_HSn and GATE\_LSn, respectively.

During wake-up, the logic is supplied from the G\_EN pin. There is no internal circuit to prevent the external high-side and low-side MOSFETs from conducting at the same time.

# SOURCE OUTPUT HIGH-SIDE PINS (SRC\_HS1 AND SRC\_HS2)

The SRC\_HSn pins are the sources of the external high-side MOSFETs. The external high-side MOSFETs are controlled using the IN\_HSn inputs.

# GATE HIGH- AND LOW-SIDE PINS (GATE\_HS1, GATE\_HS2, AND GATE\_LS1, GATE\_LS2)

The GATE\_HSn and GATE\_LSn pins are the gates of the external high- and low-side MOSFETs. The external high- and low-side MOSFETs are controlled using the IN\_HSn and IN\_LSn inputs.

### **GLOBAL ENABLE (G\_EN)**

The G\_EN pin is used to place the device in a sleep mode. When the G\_EN pin voltage is a logic LOW state, the device

is in sleep mode. The device is enabled and fully operational when the  $G_EN$  pin voltage is logic HIGH, typically 5.0 V.

### **CHARGE PUMP OUT (CP\_OUT)**

The CP\_OUT pin is used to connect an external reservoir capacitor for the charge pump.

# CHARGE PUMP CAPACITOR PINS (C1 AND C2)

The C1 and C2 pins are used to connect an external capacitor for the charge pump.

# LINEAR REGULATOR OUTPUT (LR\_OUT)

The LR\_OUT pin is the output of the internal regulator. It is used to connect an external capacitor.

# GROUND PINS (GND\_A, GND1 AND GND2)

These pins are the ground pins of the device. They should be connected together with a very low impedance connection.

**Table 5. Functional Truth Table**

| Conditions                               | G_EN | IN_HSn | IN_LSn | Gate_HSn | Gate_LSn | Comments                                                                                                                                  |

|------------------------------------------|------|--------|--------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep                                    | 0    | ×      | Х      | 0        | 0        | Device is in Sleep mode. The gates are at low state.                                                                                      |

| Normal                                   | 1    | 1      | 1      | 1        | 1        | Normal mode. The gates are controlled independently.                                                                                      |

| Normal                                   | 1    | 0      | 0      | 0        | 0        | Normal mode. The gates are controlled independently.                                                                                      |

| Undervoltage                             | 1    | х      | Х      | 0        | 0        | The device is currently in fault mode. The gates are at low state. Once the fault is removed, the 33883 recovers its normal mode.         |

| Overvoltage                              | 1    | x      | х      | 0        | 0        | The device is currently in fault mode. The gates are at low state. Once the fault is removed, the 33883 recovers its normal mode.         |

| Overtemperature on High-Side Gate Driver | 1    | 1      | х      | 0        | Х        | The device is currently in fault mode. The high-side gate is at low state. Once the fault is removed, the 33883 recovers its normal mode. |

| Overtemperature on Low-Side Gate Driver  | 1    | Х      | 1      | х        | 0        | The device is currently in fault mode. The low-side gate is at low state. Once the fault is removed, the 33883 recovers its normal mode.  |

x = Don't care.

#### **FUNCTIONAL DEVICE OPERATION**

#### **DRIVER CHARACTERISTICS**

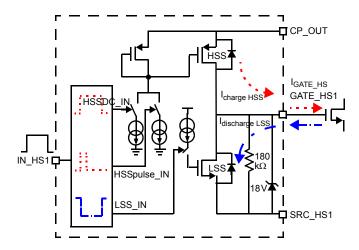

Figure 5 represents the external circuit of the high-side gate driver. In the schematic, HSS represents the switch that is used to charge the external high-side MOSFET through the GATE\_HS pin. LSS represents the switch that is used to discharge the external high-side MOSFET through the GATE\_HS pin. A 180KΩ internal typical passive discharge resistance and a 18 V typical protection zener are in parallel with LSS. The same schematic can be applied to the external low-side MOSFET driver simply by replacing pin CP\_OUT with pin LR\_OUT, pin GATE\_HS with pin GATE\_LS, and pin SRC HS with GND.

Figure 5. High-Side Gate Driver Functional Schematic

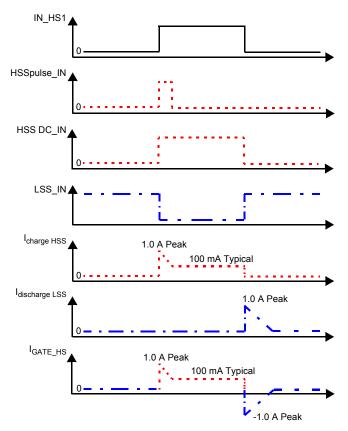

The different voltages and current of the high-side gate driver are illustrated in Figure 6. The output driver sources a peak current of up to 1.0 A for 200 ns to turn on the gate. After 200 ns, 100 mA is continuously provided to maintain the gate charged. The output driver sinks a high current to turn off the gate. This current can be up to 1.0 A peak for a 100 nF load.

**Note** GATE\_HS is loaded with a 100 nF capacitor in the chronograms. A smaller load will give lower peak and DC charge or discharge currents.

Figure 6. High-Side Gate Driver Chronograms

#### **OPERATIONAL MODES**

#### **TURN-ON**

For turn-on, the current required to charge the gate source capacitor  $C_{\rm iss}$  in the specified time can be calculated as follows:

$$I_P = Q_a/t_r = 80 \text{ nC/80 ns} \approx 1.0 \text{ A}$$

Where  $Q_g$  is power MOSFET gate charge and  $t_r$  is peak current for rise time.

#### **TURN-OFF**

The peak current for turn-off can be obtained in the same way as for turn-on, with the exception that peak current for fall time,  $t_{\rm f}$ , is substituted for  $t_{\rm r}$ :

$$I_P = Q_a/t_f = 80 \text{ nC/80 ns} \approx 1.0 \text{ A}$$

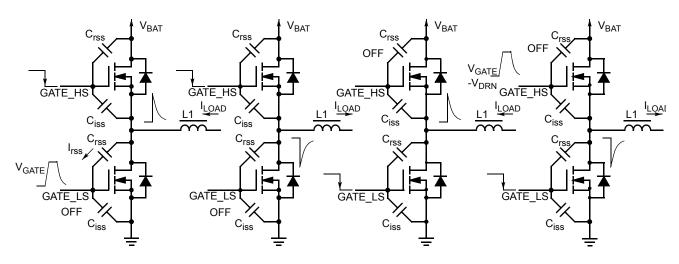

In addition to the dynamic current required to turn off or on the MOSFET, various application-related switching scenarios must be considered. These scenarios are presented in Figure 7. In order to withstand high dV/dt spikes, a low resistive path between gate and source is implemented during the OFF-state.

Flyback spike charges lowside gate via C<sub>rss</sub> charge current I<sub>rss</sub> up to 2.0 A. Causes increased uncontrolled turn-on of low-side MOSFET. Flyback spike pulls down high-side source V<sub>GS</sub>. Delays turn-off of high-side MOSFET.

Flyback spike charges lowside gate via C<sub>rss</sub> charge current I<sub>rss</sub> up to 2.0 A. Delays turn-off of low-side MOSFET. Flyback spike pulls down high-side source V<sub>GS</sub>.

Causes increased uncontrolled turn-on of high-side

Driver Requirement: Low Resistive Gate-Source Path During OFF-State Driver Requirement: Low Resistive Gate-Source Path During OFF-State. High Peak Sink Current Capability Driver Requirement: High Peak Sink Current Capability Driver Requirement: Low Resistive Gate-Source Path During OFF-State

Figure 7. OFF-State Driver Requirement

#### LOW-DROP LINEAR REGULATOR

The low-drop linear regulator is supplied by  $V_{CC2}$ . If  $V_{CC2}$  exceeds 15.0 V, the output is limited to 14.5 V (typical).

The low-drop linear regulator provides the 5.0 V for the logic section of the driver, the  $V_{gs\_ls}$  buffered at LR\_OUT, and the +14.5 V for the charge pump, which generates the CP\_OUT The low-drop linear regulator provides 4.0 mA average current per driver stage.

In case of the full bridge, that means approximately  $16\ \text{mA} - 8.0\ \text{mA}$  for the high side and  $8.0\ \text{mA}$  for the low side.

**Note:** The average current required to switch a gate with a frequency of 100 kHz is:

$$I_{CP} = Q_q * f_{PWM} = 80 \text{ nC} * 100 \text{ kHz} = 8.0 \text{ mA}$$

In a full-bridge application only one high side and one low side switches on or off at the same time.

#### **CHARGE PUMP**

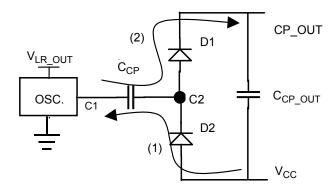

The charge pump generates the high-side driver supply voltage (CP\_OUT), buffered at C<sub>CP\_OUT</sub>. Figure 8 shows the charge pump basic circuit without load.

Figure 8. Charge Pump Basic Circuit

When the oscillator is in low state [(1) in Figure 8],  $C_{CP}$  is charged through D2 until its voltage reaches  $V_{CC}$  -  $V_{D2}$ . When the oscillator is in high state (2),  $C_{CP}$  is discharged though D1 in  $C_{CP\_OUT}$ , and final voltage of the charge pump,  $V_{CP\_OUT}$ , is  $V_{cc}$  +  $V_{LR\_OUT}$  -  $2V_D$ . The frequency of the 33883 oscillator is about 330 kHz.

#### **EXTERNAL CAPACITORS CHOICE**

External capacitors on the charge pump and on the linear regulator are necessary to supply high peak current absorbed during switching.

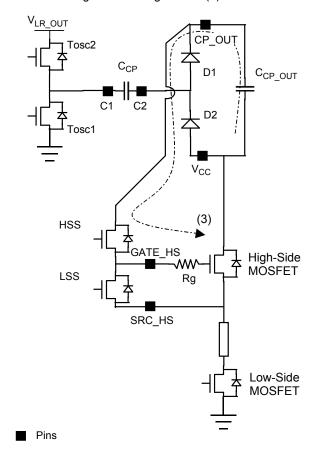

<u>Figure 9</u> represents a simplified circuitry of the high-side gate driver. Transistors Tosc1 and Tosc2 are the oscillator-switching MOSFETs. When Tosc1 is on, the oscillator is at low level. When Tosc2 is on, the oscillator is at high level. The

capacitor C<sub>CP\_OUT</sub> provides peak current to the high-side MOSFET through HSS during turn-on (3).

Figure 9. High-Side Gate Driver

## CCP

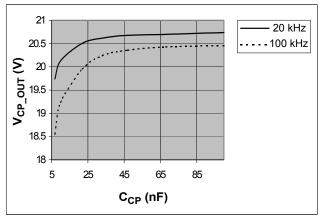

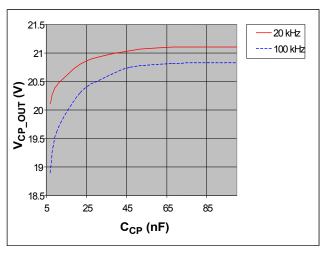

$C_{CP}$  choice depends on power MOSFET characteristics and the working switching frequency. <u>Figure 10</u> contains two diagrams that depict the influence of  $C_{CP}$  value on  $V_{CP\_OUT}$  average voltage level. The diagrams represent two different frequencies for two power MOSFETs, MTP60N06HD and MPT36N06V.

MTP60N06HD ( $Q_g = 50 \text{ nC}$ )

MTP36N06V ( $Q_g = 40 \text{ nC}$ )

Figure 10. V<sub>CP</sub> OUT Versus C<sub>CP</sub>

The smaller the  $C_{CP}$  value is, the smaller the  $V_{CP\_OUT}$  value is. Moreover, for the same  $C_{CP}$  value, when the switching frequency increases, the average  $V_{CP\_OUT}$  level decreases. For most of the applications, a typical value of 33 nF is recommended.

# C<sub>CP</sub> OUT

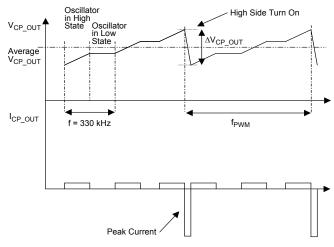

Figure 11 depicts the simplified C<sub>CP\_OUT</sub> current and voltage waveforms. f<sub>PWM</sub> is the working switching frequency.

Figure 11. Simplified C<sub>CP\_OUT</sub> Current and Voltage Waveforms

As shown above, at high-side MOSFET turn-on  $V_{CP\_OUT}$  voltage decreases. This decrease can be calculated according to the  $C_{CP\_OUT}$  value as follows:

$$\Delta V_{CP\_OUT} = \frac{Q_g}{C_{CP\_OUT}}$$

Where Q<sub>q</sub> is power MOSFET gate charge.

#### C<sub>LR</sub> OUT

$C_{LR\_OUT}$  provides peak current needed by the low-side MOSFET turn-on.  $V_{LR\_OUT}$  decrease is as follows:

$$\Delta V_{LR\_OUT} = \frac{Q_g}{C_{LR\_OUT}}$$

## **TYPICAL VALUES OF CAPACITORS**

In most working cases the following typical values are recommended for a well-performing charge pump:

$$C_{CP}$$

= 33 nF,  $C_{CP\ OUT}$  = 470 nF, and  $C_{LR\ OUT}$  = 470 nF

These values give a typical 100 mV voltage ripple on  $V_{CP\_OUT}$  and  $V_{LR\_OUT}$  with  $Q_g$  = 50 nC.

#### PROTECTION AND DIAGNOSTIC FEATURES

#### **GATE PROTECTION**

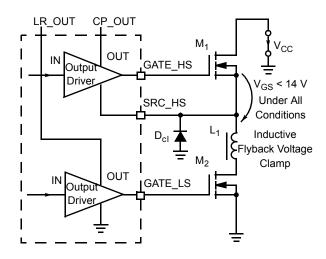

The low-side driver is supplied from the built-in low-drop regulator. The high-side driver is supplied from the internal charge pump buffered at CP OUT.

The low-side gate is protected by the internal linear regulator, which ensures that  $V_{GATE\_LS}$  does not exceed the maximum  $V_{GS}$ . Especially when working with the charge pump, the voltage at CP\_OUT can be up to 65 V. The high-side gate is clamped internally in order to avoid a  $V_{GS}$  exceeding 18 V.

Gate protection does not include a fly-back voltage clamp that protects the driver and the external MOSFET from a fly-back voltage that can occur when driving inductive load. This fly-back voltage can reach high negative voltage values and needs to be clamped externally, as shown in <u>Figure 12</u>.

Figure 12. Gate Protection and Flyback Voltage Clamp

#### LOAD DUMP AND REVERSE BATTERY

$V_{CC}$  and  $V_{CC2}$  can sustain load a dump pulse of 40 V and double battery of 24 V. Protection against reverse polarity is ensured by the external power MOSFET with the free-wheeling diodes forming a conducting pass from ground to  $V_{CC}.$  Additional protection is not provided within the circuit. To protect the circuit an external diode can be put on the battery line. It is not recommended putting the diode on the ground line.

#### **TEMPERATURE PROTECTION**

There is temperature shutdown protection per each half-bridge. Temperature shutdown protects the circuitry against temperature damage by switching off the output drivers. Its typical value is 175°C with an hysteresis of 15°C.

#### DV/DT AT V<sub>CC</sub>

$V_{CC}$  voltage must be higher than (SRC\_HS voltage minus a diode drop voltage) to avoid perturbation of the high-side driver.

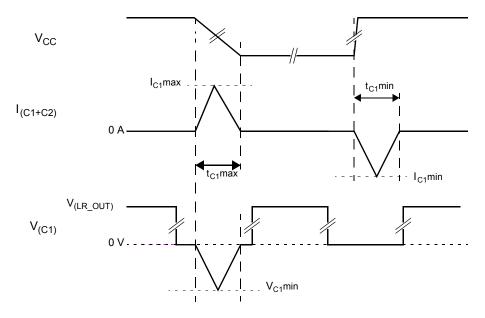

In some applications a large dV/dt at pin C2 owing to sudden changes at  $V_{CC}$  can cause large peak currents flowing through pin C1, as shown in Figure 13.

For positive transitions at pin C2, the absolute value of the minimum peak current,  $I_{C1}$ min, is specified at 2.0 A for a  $t_{C1}$ min duration of 600 ns.

For negative transitions at pin C2, the maximum peak current,  $I_{C1}$ max, is specified at 2.0 A for a  $t_{C1}$ max duration of 600 ns. Current sourced by pin C1 during a large dV/dt will result in a negative voltage at pin C1 (Figure 13). The minimum peak voltage  $V_{C1}$ min is specified at -1.5 V for a duration of  $t_{C1}$ max = 600 ns. A series resistor with the charge pump capacitor (Ccp) capacitor can be added in order to limit the surge current.

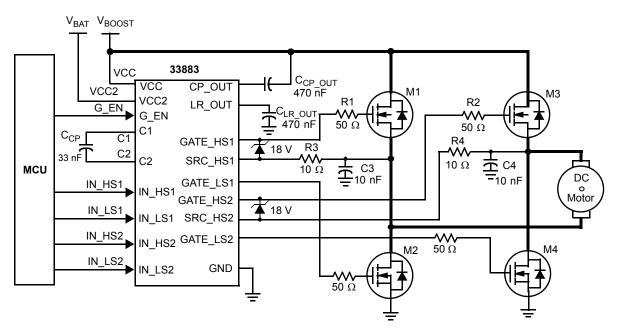

Figure 13. Limits of C1 Current and Voltage with Large Values of dV/dt

In the case of rapidly changing V<sub>CC</sub> voltages, the large dV/dt may result in perturbations of the high-side driver, thereby forcing the driver into an OFF state. The addition of capacitors C3 and C4, as shown in Figure 14, reduces the dV/dt of the source line, consequently reducing driver perturbation. Typical values for R3/R4 and C3/C4 are 10  $\Omega$  and 10 nF, respectively.

# DV/DT AT V<sub>CC2</sub>

When the external high-side MOSFET is on, in case of rapid negative change of  $V_{CC2}$  the voltage ( $V_{GATE\_HS}$ -  $V_{SRC\_HS}$ ) can be higher than the specified 18 V. In this case a resistance in the SRC line is necessary to limit the current to 5.0 mA max. It will protect the internal zener placed between GATE\_HS and SRC pins.

In case of high current (SRC\_HS>100 mA) and high voltage (>20 V) between GATE\_HSX and SRC\_HS an external zener of 18 V is needed as shown in Figure 14.

# **TYPICAL APPLICATIONS**

Figure 14. Application Schematic with External Protection Circuit

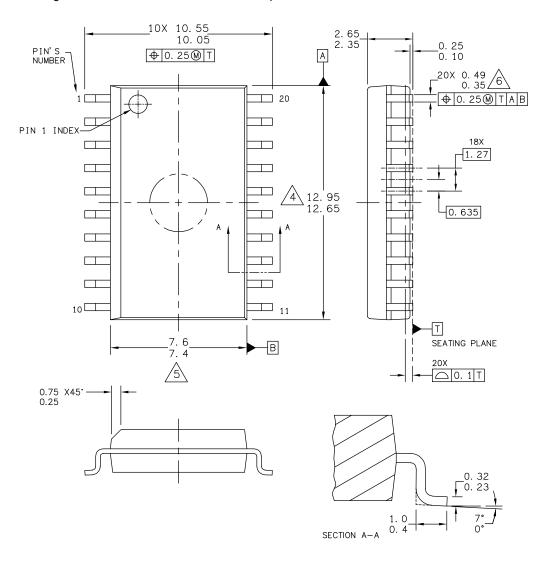

# **PACKAGING**

# **PACKAGING DIMENSIONS**

**Important** For the most current revision of the package, visit <a href="www.freescale.com">www.freescale.com</a> and do a keyword search on the 98ASB42343B drawing number below. Dimensions shown are provided for reference ONLY.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               | 07 017011 | DOCUMENT NO  | ): 98ASB42343B   | REV: J      |

| 20LD SOIC W/B, 1.                                    |           | CASE NUMBER  | 2: 751D-07       | 23 MAR 2005 |

| CNSE OUTET                                           | INL       | STANDARD: JE | IDEC MS-013AC    |             |

DW SUFFIX EG SUFFIX (PB-FREE) 20-PIN SOICW PLASTIC PACKAGE 98ASB42343B ISSUE J

# **REVISION HISTORY**

| REVISION | DATE    | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.0      | 1/2007  | <ul> <li>Implemented Revision History page</li> <li>Updated to the current Freescale format and style</li> <li>Added MCZ33883EG/R2 to the Ordering Information</li> <li>Updated the package drawing to Rev. J</li> <li>Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from MAXIMUM RATINGS on page 4. Added note with instructions from www.freescale.com.</li> </ul> |

| 10.0     | 10/2012 | <ul> <li>Updated orderable part number from MCZ33883EG to MC33883HEG.</li> <li>Updated Freescale form and style</li> <li>Removed MC33883DW from the ordering information</li> <li>Changed from Advance Information to Technical Data</li> </ul>                                                                                                                                                        |

How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off.SMARTMOS is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2013 Freescale Semiconductor, Inc.

Document Number: MC33883

Rev 10.0 10/2012