### **General Description**

The MAX6730-MAX6735 single-/dual-/triple-voltage microprocessor (µP) supervisors feature a watchdog timer and manual reset capability. The MAX6730-MAX6735 offer factory-set reset thresholds for monitoring voltages from +0.9V to +5V and an adjustable reset input for monitoring voltages down to +0.63V. The combination of these features significantly improves system reliability and accuracy when compared to separate ICs or discrete components.

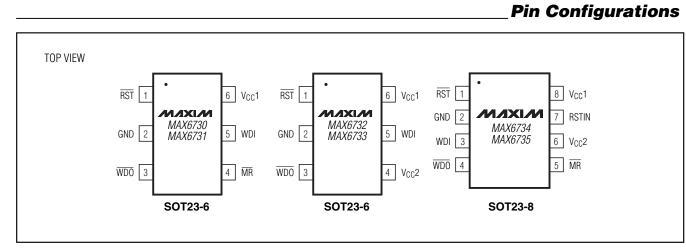

The active-low reset output asserts and remains asserted for the reset timeout period after all the monitored voltages exceed their respective thresholds. Multiple factoryset reset threshold combinations reduce the number of external components required. The MAX6730/MAX6731 monitor a single fixed voltage, the MAX6732/MAX6733 monitor two fixed voltages, and the MAX6734/MAX6735 monitor two fixed voltages and one adjustable voltage. All devices are offered with six minimum reset timeout periods ranging from 1.1ms to 1120ms.

The MAX6730–MAX6735 feature a watchdog timer with an independent watchdog output. The watchdog timer prevents system lockup during code execution errors. A watchdog startup delay of 54s after reset asserts allows system initialization during power-up. The watchdog operates in normal mode with a 1.68s delay after initialization. The MAX6730/MAX6732/MAX6734 provide an active-low, open-drain watchdog output. The MAX6731/MAX6733/MAX6735 provide an active-low, push-pull watchdog output.

Other features include a manual reset input (MAX6730/ MAX6731/MAX6734/MAX6735) and push-pull reset output (MAX6731/MAX6733/MAX6735) or open-drain reset output (MAX6730/MAX6732/MAX6734). The MAX6730-MAX6733 are offered in a tiny SOT23-6 package. The MAX6734/MAX6735 are offered in a space-saving SOT23-8 package. All devices are fully specified over the extended -40°C to +85°C temperature range.

### **Applications**

Multivoltage Systems

Telecom/Networking Equipment

Computers/Servers

Portable/Battery-Operated Equipment

Industrial Equipment

Printer/Fax

Set-Top Boxes

Typical Operating Circuit and Pin Configurations appear at end of data sheet.

### Features

- V<sub>CC</sub>1 (Primary Supply) Reset Threshold Voltages from +1.575V to +4.63V

- VCC2 (Secondary Supply) Reset Threshold Voltages from +0.79V to +3.08V

- Adjustable RSTIN Threshold for Monitoring Voltages Down to +0.63V (MAX6734/MAX6735 Only)

- Six Reset Timeout Options

- Watchdog Timer with Independent Watchdog Output 35s (min) Initial Watchdog Startup Period 1.12s (min) Normal Watchdog Timeout Period

- Manual Reset Input (MAX6730/MAX6731/MAX6734/MAX6735)

- Guaranteed Reset Valid down to  $V_{CC1}$  or  $V_{CC2} = +0.8V$

- ♦ Push-Pull RESET or Open-Drain RESET Output

- Immune to Short Vcc Transients

MAX6734 KA\_\_D\_ -T

- Low Supply Current: 14µA (typ) at +3.6V

- Small 6-Pin and 8-Pin SOT23 Packages

#### PART\* **TEMP RANGE PIN-PACKAGE** MAX6730 UT\_D\_ -T 6 SOT23-6 -40°C to +85°C MAX6731 UT\_D\_ -T -40°C to +85°C 6 SOT23-6 MAX6732 UT\_ \_D\_ -T -40°C to +85°C 6 SOT23-6 MAX6733 UT\_ \_D\_ -T -40°C to +85°C 6 SOT23-6

-40°C to +85°C

-40°C to +85°C

**Ordering Information**

8 SOT23-8

8 SOT23-8

MAX6735 KA\_ \_D\_ -T \*Insert the threshold level suffixes for  $V_{CC}$  and  $V_{CC}$  (Table 1) after "UT" or "KA." For the MAX6730/MAX6731, insert only the V<sub>CC</sub>1 threshold suffix after the "UT." Insert the reset timeout delay (Table 2) after "D" to complete the part number. For example, the MAX6732UTLTD3-T provides a V<sub>CC</sub>1 threshold of +4.625V, a V<sub>CC</sub>2 threshold of +3.075V, and a 210ms reset timeout period. Sample stock is generally held on standard versions only (see the Standard Versions table). Standard versions have an order increment requirement of 2500 pieces. Nonstandard versions have an order increment requirement of 10,000 pieces. Contact factory for availability.

Devices are available in both leaded and lead-free packaging. Specify lead-free by replacing "-T" with "+T" when ordering.

#### Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> 1, V <sub>CC</sub> 2, RSTIN, MR, WDI to GND |              |

|-------------------------------------------------------------|--------------|

| RST, WDO to GND (open drain)                                | -0.3V to +6V |

| RST, WDO to GND (push-pull)0.3V to (V                       | CC1 + 0.3V)  |

| Input Current/Output Current (all pins)                     | 20mA         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )       |              |

| 6-Pin SOT23-6 (derate 8.7mW/°C above +70°C).                | 696mW        |

| 8-Pin SOT23-8 (derate 8.9mW/°C above +70°C).                | 714mW        |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Storage Temperature Range         | 65°C to +150°C |

| Junction Temperature              | +150°C         |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC}1 = V_{CC}2 = +0.8V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                         | SYMBOL                                  | CONDITIONS                                                                 | MIN   | ТҮР   | MAX   | UNITS |  |

|-----------------------------------|-----------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Supply Voltage                    | V <sub>CC</sub> 1,<br>V <sub>CC</sub> 2 |                                                                            | 0.8   |       | 5.5   | V     |  |

|                                   | 11                                      | V <sub>CC</sub> 1 < +5.5V, all I/O connections open, outputs not asserted  |       | 15    | 39    |       |  |

| Questo Questo et                  | ICC1                                    | V <sub>CC</sub> 1 < +3.6V, all I/O connections open, outputs not asserted  |       | 10    | 28    |       |  |

| Supply Current                    |                                         | V <sub>CC</sub> 2 < +3.6V, all I/O connections open, outputs not asserted  |       | 4     | 11    | μA    |  |

|                                   | I <sub>CC</sub> 2                       | V <sub>CC</sub> 2 < +2.75V, all I/O connections open, outputs not asserted |       | 3     | 9     |       |  |

|                                   |                                         | L (falling)                                                                | 4.500 | 4.625 | 4.750 |       |  |

|                                   |                                         | M (falling)                                                                | 4.250 | 4.375 | 4.500 |       |  |

|                                   |                                         | T (falling)                                                                | 3.000 | 3.075 | 3.150 | ]     |  |

|                                   |                                         | S (falling)                                                                | 2.850 | 2.925 | 3.000 |       |  |

| V <sub>CC</sub> 1 Reset Threshold | V <sub>TH</sub> 1                       | R (falling)                                                                | 2.550 | 2.625 | 2.700 | V     |  |

|                                   |                                         | Z (falling)                                                                | 2.250 | 2.313 | 2.375 |       |  |

|                                   |                                         | Y (falling)                                                                | 2.125 | 2.188 | 2.250 |       |  |

|                                   |                                         | W (falling)                                                                | 1.620 | 1.665 | 1.710 | 1     |  |

|                                   |                                         | V (falling)                                                                | 1.530 | 1.575 | 1.620 | Ī     |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}1 = V_{CC}2 = +0.8V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                                                      | MIN   | ТҮР   | MAX                  | UNITS  |

|-------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|-------|-------|----------------------|--------|

|                                     |                   | T (falling)                                                                                                     | 3.000 | 3.075 | 3.150                |        |

|                                     |                   | S (falling)                                                                                                     | 2.850 | 2.925 | 3.000                |        |

|                                     |                   | R (falling)                                                                                                     | 2.550 | 2.625 | 2.700                |        |

|                                     |                   | Z (falling)                                                                                                     | 2.250 | 2.313 | 2.375                |        |

|                                     |                   | Y (falling)                                                                                                     | 2.125 | 2.188 | 2.250                |        |

|                                     |                   | W (falling)                                                                                                     | 1.620 | 1.665 | 1.710                |        |

| V <sub>CC</sub> 2 Reset Threshold   | V <sub>TH</sub> 2 | V (falling)                                                                                                     | 1.530 | 1.575 | 1.620                | V      |

|                                     |                   | I (falling)                                                                                                     | 1.350 | 1.388 | 1.425                |        |

|                                     |                   | H (falling)                                                                                                     | 1.275 | 1.313 | 1.350                |        |

|                                     |                   | G (falling)                                                                                                     | 1.080 | 1.110 | 1.140                |        |

|                                     |                   | F (falling)                                                                                                     | 1.020 | 1.050 | 1.080                |        |

|                                     |                   | E (falling)                                                                                                     | 0.810 | 0.833 | 0.855                |        |

|                                     |                   | D (falling)                                                                                                     | 0.765 | 0.788 | 0.810                |        |

| Reset Threshold Tempco              |                   |                                                                                                                 |       | 20    |                      | ppm/°C |

| Reset Threshold Hysteresis          | V <sub>HYST</sub> | Referenced to V <sub>TH</sub> typical                                                                           |       | 0.5   |                      | %      |

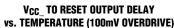

| V <sub>CC</sub> to RST Output Delay | trd               | $V_{CC1} = (V_{TH1} + 100mV)$ to<br>(V_{TH1} - 100mV) or<br>$V_{CC2} = (V_{TH2} + 75mV)$ to<br>(V_{TH2} - 75mV) |       | 45    |                      | μs     |

|                                     |                   | D1                                                                                                              | 1.1   | 1.65  | 2.2                  | ms     |

|                                     |                   | D2                                                                                                              | 8.8   | 13.2  | 17.6                 |        |

| Reset Timeout Period                | top               | D3                                                                                                              | 140   | 210   | 280                  |        |

| neset filleout renou                | t <sub>RP</sub>   | D5                                                                                                              | 280   | 420   | 560                  |        |

|                                     |                   | D6                                                                                                              | 560   | 840   | 1120                 |        |

|                                     |                   | D4                                                                                                              | 1120  | 1680  | 2240                 |        |

| ADJUSTABLE RESET COMPAR             | RATOR INPUT (     | (MAX6734/MAX6735)                                                                                               |       |       |                      |        |

| RSTIN Input Threshold               | VRSTIN            |                                                                                                                 | 611   | 626.5 | 642                  | mV     |

| RSTIN Input Current                 | IRSTIN            |                                                                                                                 | -25   |       | +25                  | nA     |

| RSTIN Hysteresis                    |                   |                                                                                                                 |       | 3     |                      | mV     |

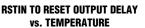

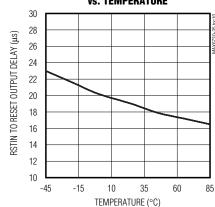

| RSTIN to Reset Output Delay         | <b>t</b> RSTIND   | V <sub>RSTIN</sub> to (V <sub>RSTIN</sub> - 30mV)                                                               |       | 22    |                      | μs     |

| MANUAL RESET INPUT (MAX6            | 730/MAX6731/N     | /AX6734/MAX6735)                                                                                                |       |       |                      |        |

| MR Input Threshold                  | VIL               |                                                                                                                 |       |       | $0.3 \times V_{CC}1$ | V      |

|                                     | VIH               | V <sub>IH</sub> 0.7 × V <sub>CC</sub> 1                                                                         |       |       | v                    |        |

| MR Minimum Pulse Width              |                   |                                                                                                                 | 1     |       |                      | μs     |

| MR Glitch Rejection                 |                   |                                                                                                                 |       | 100   |                      | ns     |

| MR to Reset Output Delay            | t <sub>MR</sub>   |                                                                                                                 |       | 200   |                      | ns     |

| MR Pullup Resistance                |                   |                                                                                                                 | 25    | 50    | 80                   | kΩ     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}1 = V_{CC}2 = +0.8V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                               | SYMBOL          | CONDITIONS                                                                    | MIN                     | ТҮР  | МАХ                   | UNITS |

|---------------------------------------------------------|-----------------|-------------------------------------------------------------------------------|-------------------------|------|-----------------------|-------|

| WATCHDOG INPUT                                          |                 |                                                                               |                         |      | 1                     |       |

| Watchdog Timeout Period                                 | twD-L           | First watchdog period after reset timeout period                              | 35                      | 54   | 72                    | S     |

|                                                         | twd-s           | Normal mode                                                                   | 1.12                    | 1.68 | 2.24                  |       |

| WDI Pulse Width                                         | twdi            | (Note 2)                                                                      | 50                      |      |                       | ns    |

|                                                         | VIL             |                                                                               |                         |      | $0.3 \times V_{CC}$ 1 | V     |

| WDI Input Voltage                                       | VIH             |                                                                               | 0.7 × V <sub>CC</sub> 1 |      |                       | v     |

| WDI Input Current                                       | Iwdi            | $WDI = 0 \text{ or } V_{CC}1$                                                 | -1                      |      | +1                    | μA    |

| RESET/WATCHDOG OUTPUT                                   |                 |                                                                               |                         |      |                       |       |

| RST/WDO Output Low Voltage<br>(Push-Pull or Open Drain) |                 | $V_{CC1}$ or $V_{CC2} \ge +0.8V$ ,<br>$I_{SINK} = 1\mu A$ , output asserted   |                         |      | 0.3                   |       |

|                                                         | Vol             | $V_{CC}1$ or $V_{CC}2 \ge +1.0V$ ,<br>$I_{SINK} = 50\mu A$ , output asserted  |                         |      | 0.3                   |       |

|                                                         |                 | $V_{CC}1$ or $V_{CC}2 \ge +1.2V$ ,<br>$I_{SINK} = 100\mu A$ , output asserted |                         |      | 0.3                   | V     |

|                                                         |                 | $V_{CC}1$ or $V_{CC}2 \ge +2.7V$ ,<br>$I_{SINK} = 1.2mA$ , output asserted    |                         |      | 0.3                   |       |

|                                                         |                 | $V_{CC1}$ or $V_{CC2} \ge +4.5V$ ,<br>$I_{SINK} = 3.2mA$ , output asserted    | 0.4                     |      |                       |       |

|                                                         |                 | $V_{CC1} \ge +1.8V$ , $I_{SOURCE} = 200\mu A$ ,<br>output not asserted        | $0.8 \times V_{CC}$ 1   |      | V                     |       |

| RST/WDO Output High Voltage<br>(Push-Pull Only)         | V <sub>OH</sub> | $V_{CC1} \ge +2.7V$ , $I_{SOURCE} = 500\mu A$ ,<br>output not asserted        | $0.8 \times V_{CC}$ 1   |      |                       |       |

|                                                         |                 | $V_{CC1} \ge +4.5V$ , $I_{SOURCE} = 800\mu A$ ,<br>output not asserted        | 0.8 × V <sub>CC</sub> 1 |      |                       |       |

| RST/WDO Output Open-Drain<br>Leakage Current            |                 | Output not asserted                                                           |                         |      | 0.5                   | μA    |

**Note 1:** Devices tested at  $T_A = +25$ °C. Overtemperature limits are guaranteed by design and not production tested. **Note 2:** Parameter guaranteed by design.

M/IXI/M

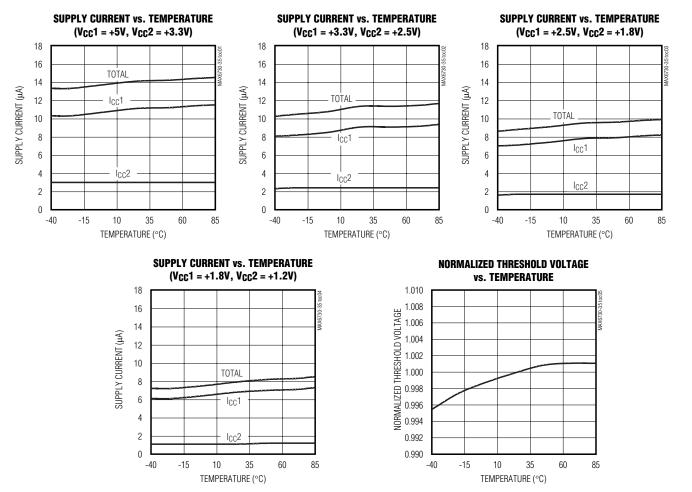

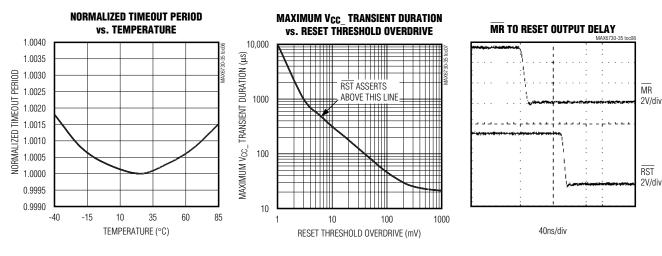

**Typical Operating Characteristics**

$(V_{CC}1 = +5V, V_{CC}2 = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub>1 = +5V, V<sub>CC</sub>2 = +3.3V,  $T_A$  = +25°C, unless otherwise noted.)

80

75

70

65

60

55

50

45

40

-45

-15

10

35

TEMPERATURE (°C)

60

85

$V_{CC_{-}}$  TO RESET OUTPUT DELAY ( $\mu s$ )

-----

6

## \_Pin Description

|                    | PIN                |                    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------------------|--------------------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX6730<br>MAX6731 | MAX6732<br>MAX6733 | MAX6734<br>MAX6735 | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 1                  | 1                  | 1                  | RST               | Active-Low Reset Output. The MAX6730/MAX6732/MAX6734 provide an open-<br>drain output. The MAX6731/MAX6733/MAX6735 provide a push-pull output. RST asserts low when any of the following conditions occur: V <sub>CC</sub> 1 or V <sub>CC</sub> 2 drops below its preset threshold, RSTIN drops below its reset threshold, or MR is driven low. Open-drain versions require an external pullup resistor.                                                                                                                                                                                                                                                           |  |

| 2                  | 2                  | 2                  | GND               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 3                  | 3                  | 4                  | WDO               | Active-Low Watchdog Output. The MAX6730/MAX6732/MAX6734 provide an opendrain $\overline{WDO}$ output. The MAX6731/MAX6733/MAX6735 provide a push-pull $\overline{WDO}$ output. $\overline{WDO}$ asserts low when no low-to-high or high-to-low transition occurs on WDI within the watchdog timeout period (twD) or if an undervoltage lockout condition exists for V <sub>CC1</sub> , V <sub>CC2</sub> , or RSTIN. $\overline{WDO}$ deasserts without a timeout period when V <sub>CC1</sub> , V <sub>CC2</sub> , and RSTIN exceed their reset thresholds, or when the manual reset input is deasserted. Open-drain versions require an external pullup resistor. |  |

| 4                  | _                  | 5                  | MR                | Active-Low Manual Reset Input. Drive $\overline{\text{MR}}$ low to force a reset. $\overline{\text{RST}}$ remains asserted as long as $\overline{\text{MR}}$ is low and for the reset timeout period after $\overline{\text{MR}}$ releases high. $\overline{\text{MR}}$ has a 50k $\Omega$ pullup resistor to V <sub>CC</sub> 1; leave $\overline{\text{MR}}$ open or connect to V <sub>CC</sub> 1 if unused.                                                                                                                                                                                                                                                      |  |

| 5                  | 5                  | 3                  | WDI               | Watchdog Input. If WDI remains high or low for longer than the watchdog timeout period, the internal watchdog timer expires and the watchdog output asserts low. The internal watchdog timer clears whenever $\overline{\text{RST}}$ asserts or a rising or falling edge on WDI is detected. The watchdog has an initial watchdog timeout period (35s mir after each reset event and a short timeout period (1.12s min) after the first valid WDI transition. Floating WDI does not disable the watchdog timer function.                                                                                                                                           |  |

| 6                  | 6                  | 8                  | V <sub>CC</sub> 1 | Primary Supply-Voltage Input. $V_{CC}$ 1 provides power to the device when it is greate than $V_{CC}$ 2. $V_{CC}$ 1 is the input to the primary reset threshold monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                    | 4                  | 6                  | V <sub>CC</sub> 2 | Secondary Supply-Voltage Input. V <sub>CC</sub> 2 provides power to the device when it is greater than V <sub>CC</sub> 1. V <sub>CC</sub> 2 is the input to the secondary reset threshold monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                    | _                  | 7                  | RSTIN             | Undervoltage Reset Comparator Input. RSTIN provides a high-impedance comparator input for the adjustable reset monitor. $\overrightarrow{\text{RST}}$ asserts low if the voltage at RSTIN drops below the 626mV internal reference voltage. Connect a resistive voltage-divider to RSTIN to monitor voltages higher than 626mV. Connect RSTIN to $V_{CC}$ 1 or $V_{CC}$ 2 if unused.                                                                                                                                                                                                                                                                               |  |

| PART NO. SUFFIX | V <sub>CC</sub> 1 NOMINAL<br>VOLTAGE<br>THRESHOLD(V) | V <sub>CC</sub> 2 NOMINAL<br>VOLTAGE<br>THRESHOLD (V) |

|-----------------|------------------------------------------------------|-------------------------------------------------------|

| LT              | 4.625                                                | 3.075                                                 |

| MS              | 4.375                                                | 2.925                                                 |

| MR              | 4.375                                                | 2.625                                                 |

| TZ              | 3.075                                                | 2.313                                                 |

| SY              | 2.925                                                | 2.188                                                 |

| RY              | 2.625                                                | 2.188                                                 |

| TW              | 3.075                                                | 1.665                                                 |

| SV              | 2.925                                                | 1.575                                                 |

| RV              | 2.625                                                | 1.575                                                 |

| TI              | 3.075                                                | 1.388                                                 |

| SH              | 2.925                                                | 1.313                                                 |

| RH              | 2.625                                                | 1.313                                                 |

| TG              | 3.075                                                | 1.110                                                 |

| SF              | 2.925                                                | 1.050                                                 |

| RF              | 2.625                                                | 1.050                                                 |

| TE              | 3.075                                                | 0.833                                                 |

| SD              | 2.925                                                | 0.788                                                 |

| RD              | 2.625                                                | 0.788                                                 |

| ZW              | 2.313                                                | 1.665                                                 |

| YV              | 2.188                                                | 1.575                                                 |

| ZI              | 2.313                                                | 1.388                                                 |

| YH              | 2.188                                                | 1.313                                                 |

| ZG              | 2.313                                                | 1.110                                                 |

| YF              | 2.188                                                | 1.050                                                 |

| ZE              | 2.313                                                | 0.833                                                 |

| YD              | 2.188                                                | 0.788                                                 |

| WI              | 1.665                                                | 1.388                                                 |

| VH              | 1.575                                                | 1.313                                                 |

| WG              | 1.665                                                | 1.110                                                 |

| VF              | 1.575                                                | 1.050                                                 |

| WE              | 1.665                                                | 0.833                                                 |

| VD              | 1.575                                                | 0.788                                                 |

Table 1. Reset Voltage Threshold Suffix Guide\*\*

#### \*\*Standard versions are shown in bold and are available in a D3 timeout option only. Standard versions require 2500-piece order increments and are typically held in sample stock. There is a 10,000-piece order increment on nonstandard versions. Other threshold voltages may be available; contact factory for availability.

#### Table 2. Reset Timeout Period Suffix Guide

| TIMEOUT       | ACTIVE TIMEOUT PERIOD |          |  |

|---------------|-----------------------|----------|--|

| PERIOD SUFFIX | MIN (ms)              | MAX (ms) |  |

| D1            | 1.1                   | 2.2      |  |

| D2            | 8.8                   | 17.6     |  |

| D3            | 140                   | 280      |  |

| D5            | 280                   | 560      |  |

| D6            | 560                   | 1120     |  |

| D4            | 1120                  | 2240     |  |

### **Detailed Description**

#### **Supply Voltages**

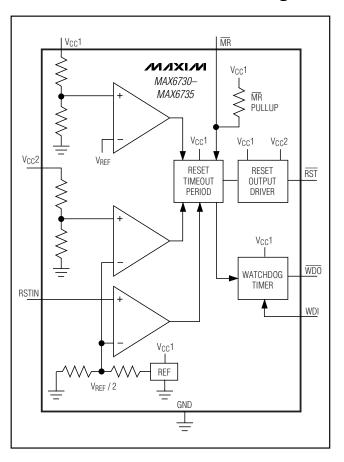

The MAX6730–MAX6735 microprocessor ( $\mu$ P) supervisors maintain system integrity by alerting the  $\mu$ P to fault conditions. The MAX6730–MAX6735 monitor one to three supply voltages in  $\mu$ P-based systems and assert an active-low reset output when any monitored supply voltage drops below its preset threshold. The output state remains valid for V<sub>CC</sub>1 or V<sub>CC</sub>2 greater than +0.8V.

#### **Threshold Levels**

The two-letter code in the Reset Voltage Threshold Suffix Guide (Table 1) indicates the threshold level combinations for V<sub>CC</sub>1 and V<sub>CC</sub>2.

#### **Reset Output**

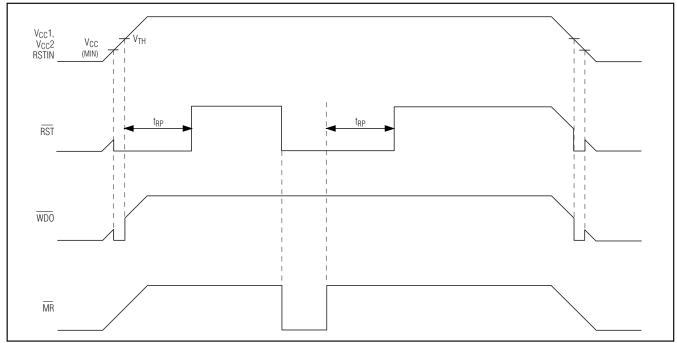

The MAX6730–MAX6735 feature an active-low reset output (RST). RST asserts when the voltage at either V<sub>CC1</sub> or V<sub>CC2</sub> falls below the voltage threshold level, V<sub>RSTIN</sub> drops below its threshold, or MR is driven low (Figure 1). RST remains low for the reset timeout period (Table 2) after V<sub>CC1</sub>, V<sub>CC2</sub>, and RSTIN increase above their respective thresholds and after MR releases high. Whenever V<sub>CC1</sub>, V<sub>CC2</sub>, or RSTIN go below the reset threshold before the end of the reset timeout period, the internal timer restarts. The MAX6730/MAX6732/ MAX6734 provide an open-drain RST output, and the MAX6731/ MAX6733/MAX6735 provide a push-pull RST output.

#### Manual Reset Input

Many µP-based products require manual reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A logic low on MR asserts the reset output, clears the watchdog timer, and deasserts the watchdog output. Reset remains asserted while MR is low and for the reset timeout period (tRP) after MR returns high. An internal 50k $\Omega$  pullup resistor allows MR to be left open if unused. Drive MR with TTL or CMOS-logic levels or with open-drain/collector outputs. Connect a normally open momentary switch from MR to GND to create a manual reset function; external debounce circuitry is not required. Connect a 0.1µF capacitor from MR to GND to provide additional noise immunity when driving MR over long cables or if the device is used in a noisy environment.

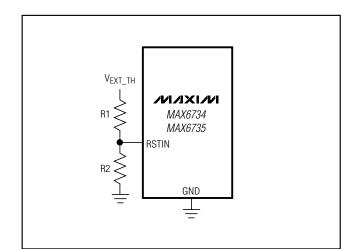

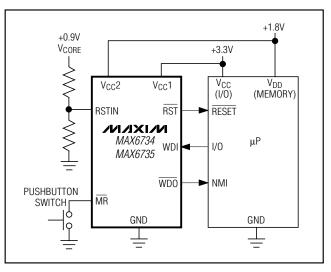

#### Adjustable Input Voltage (RSTIN)

The MAX6734/MAX6735 provide an additional highimpedance comparator input with a 626mV threshold to monitor a third supply voltage. To monitor a voltage higher than 626mV, connect a resistive-divider to the circuit as shown in Figure 2 to establish an externally controlled threshold voltage, V<sub>EXT\_TH</sub>.

$$VEXT_TH = 626mV \times \frac{(R1 + R2)}{R2}$$

Figure 2. Monitoring a Third Voltage

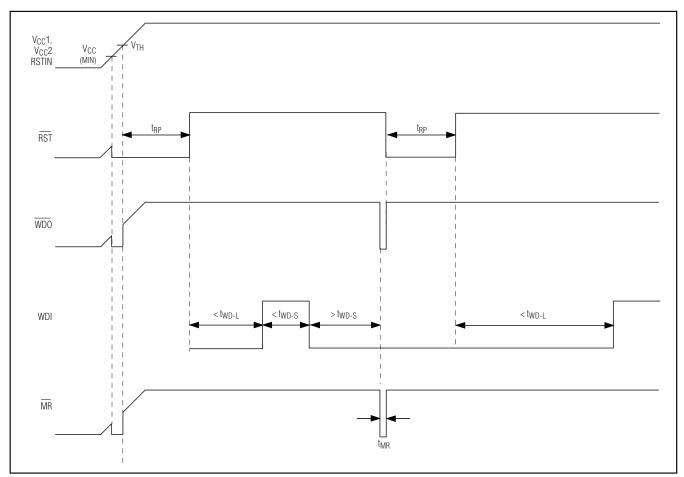

Figure 1. RST, WDO, and MR Timing Diagram

MAX6730-MAX6735

The RSTIN comparator derives power from V<sub>CC</sub>1, and the input voltage must remain less than or equal to V<sub>CC</sub>1. Low leakage current at RSTIN allows the use of large-valued resistors, resulting in reduced power consumption of the system.

#### Watchdog

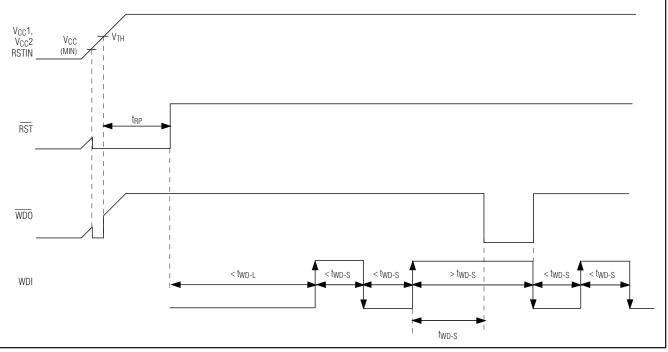

The watchdog feature monitors  $\mu$ P activity through the watchdog input (WDI). A rising or falling edge on WDI within the watchdog timeout period (twp) indicates normal  $\mu$ P operation. WDO asserts low if WDI remains high or low for longer than the watchdog timeout period. Floating WDI does not disable the watchdog timer.

The MAX6730–MAX6735 include a dual-mode watchdog timer to monitor  $\mu$ P activity. The flexible timeout architecture provides a long-period initial watchdog mode, allowing complicated systems to complete lengthy boots, and a short-period normal watchdog mode, allowing the supervisor to provide quick alerts when processor activity fails. After each reset event (V<sub>CC</sub> power-up, brownout, or manual reset), there is a long initial watchdog period of 35s (min). The long watchdog period mode provides an extended time for the system to power up and fully initialize all  $\mu$ P and system components before assuming responsibility for routine watchdog updates. The usual watchdog timeout period (1.12s min) begins after the initial watchdog timeout period ( $t_{WD-L}$ ) expires or after the first transition on WDI (Figure 3). During normal operating mode, the supervisor asserts the WDO output if the  $\mu$ P does not update the WDI with a valid transition (high to low or low to high) within the standard timeout period ( $t_{WD-S}$ ) (1.12s min).

Connect  $\overline{\text{MR}}$  to  $\overline{\text{WDO}}$  to force a system reset in the event that no rising or falling edge is detected at WDI within the watchdog timeout period.  $\overline{\text{WDO}}$  asserts low when no edge is detected by WDI, the  $\overline{\text{RST}}$  output asserts low, the watchdog counter immediately clears, and  $\overline{\text{WDO}}$  returns high. The watchdog counter restarts, using the long watchdog period, when the reset timeout period ends (Figure 4).

### Ensuring a Valid RESET Output Down to V<sub>CC</sub> = 0

The MAX6730–MAX6735 guarantee proper operation down to V<sub>CC</sub> = +0.8V. In applications that require valid reset levels down to V<sub>CC</sub> = 0, use a 100k $\Omega$  pulldown resistor from RST to GND. The resistor value used is not critical, but it must be large enough not to load the reset output when V<sub>CC</sub> is above the reset threshold. For most applications, 100k $\Omega$  is adequate. Note that this configuration does not work for the open-drain outputs of MAX6730/MAX6732/MAX6734.

Figure 3. Watchdog Input/Output Timing Diagram (MR and WDO Not Connected)

Figure 4. Watchdog Input/Output Timing Diagram (MR and WDO Connected)

### **Applications Information**

#### Interfacing to µPs with Bidirectional Reset Pins

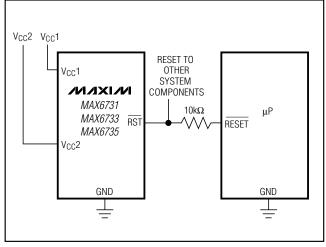

Microprocessors with bidirectional reset pins can interface directly with the open-drain  $\overline{RST}$  output options. However, conditions might occur in which the push-pull output versions experience logic contention with the bidirectional reset pin of the  $\mu P.$  Connect a 10k $\Omega$  resistor between  $\overline{RST}$  and the  $\mu P's$  reset I/O port to prevent logic contention (Figure 5).

#### **Falling Vcc Transients**

The MAX6730–MAX6735  $\mu$ P supervisors are relatively immune to short-duration falling V<sub>CC</sub> transients (glitches). Small glitches on V<sub>CC</sub> are ignored by the MAX6730–MAX6735, preventing undesirable reset pulses to the  $\mu$ P. The *Typical Operating Characteristics* show Maximum Transient Duration vs. Reset Threshold

Figure 5. Interfacing to µPs with Bidirectional Reset I/O

MAX6730-MAX6735

Overdrive, for which reset pulses are not generated. The graph was produced using falling V<sub>CC</sub> pulses, starting above V<sub>TH</sub> and ending below the reset threshold by the magnitude indicated (reset threshold overdrive). The graph shows the maximum pulse width that a falling V<sub>CC</sub> transient typically might have without causing a reset pulse to be issued. As the amplitude of the transient increases (i.e., goes further below the reset threshold), the maximum allowable pulse width decreases. A 0.1µF bypass capacitor mounted close to V<sub>CC</sub> provides additional transient immunity.

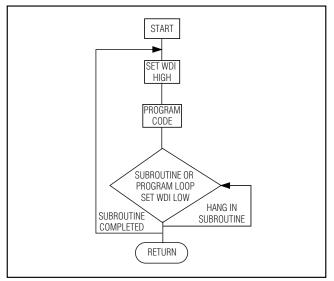

#### Watchdog Software Considerations

Setting and resetting the watchdog input at different points in the program rather than "pulsing" the watchdog input high-low-high or low-high-low helps the watchdog timer closely monitor software execution. This technique avoids a "stuck" loop, in which the watchdog timer continues to be reset within the loop, preventing the watchdog from timing out. Figure 6 shows an example flow diagram in which the I/O driving the watchdog input is set high at the beginning of the program, set low at the beginning of every subroutine or loop, and then set high again when the program returns to the beginning. If the program "hangs" in any subroutine, the I/O continually asserts low (or high), and the watchdog timer expires, issuing a reset or interrupt.

Figure 6. Watchdog Flow Diagram

### **Functional Diagram**

### \_Standard Versions

| PART            | TOP MARK | PART            | TOP MARK |

|-----------------|----------|-----------------|----------|

| MAX6730UTLD3-T  | ABCC     | MAX6733UTZGD3-T | ABQI     |

| MAX6730UTSD3-T  | ABPB     | MAX6733UTYDD3-T | ABQG     |

| MAX6730UTRD3-T  | ABPA     | MAX6733UTVHD3-T | ABQE     |

| MAX6730UTZD3-T  | ABPD     | MAX6733UTWGD3-T | ABQF     |

| MAX6730UTVD3-T  | ABPC     | MAX6733UTVDD3-T | ABQD     |

| MAX6731UTLD3-T  | ABPE     | MAX6734KALTD3-T | AEHN     |

| MAX6731UTTD3-T  | ABCD     | MAX6734KASYD3-T | AEHS     |

| MAX6731UTSD3-T  | ABPG     | MAX6734KASVD3-T | AEHR     |

| MAX6731UTRD3-T  | ABPF     | MAX6734KARVD3-T | AEHO     |

| MAX6731UTZD3-T  | ABPI     | MAX6734KASHD3-T | AEHQ     |

| MAX6731UTVD3-T  | ABPH     | MAX6734KATGD3-T | AEHT     |

| MAX6732UTLTD3-T | ABCE     | MAX6734KASDD3-T | AEHP     |

| MAX6732UTSYD3-T | ABPN     | MAX6734KAZWD3-T | AEIA     |

| MAX6732UTSVD3-T | ABPM     | MAX6734KAYHD3-T | AEHY     |

| MAX6732UTRVD3-T | ABPJ     | MAX6734KAZGD3-T | AEHZ     |

| MAX6732UTSHD3-T | ABPL     | MAX6734KAYDD3-T | AEHX     |

| MAX6732UTTGD3-T | ABPO     | MAX6734KAVHD3-T | AEHV     |

| MAX6732UTSDD3-T | ABPK     | MAX6734KAWGD3-T | AEHW     |

| MAX6732UTZWD3-T | ABPV     | MAX6734KAVDD3-T | AEHU     |

| MAX6732UTYHD3-T | ABPT     | MAX6735KALTD3-T | AEIB     |

| MAX6732UTZGD3-T | ABPU     | MAX6735KASYD3-T | AEIG     |

| MAX6732UTYDD3-T | ABPS     | MAX6735KASVD3-T | AEIF     |

| MAX6732UTVHD3-T | ABPQ     | MAX6735KARVD3-T | AEIC     |

| MAX6732UTWGD3-T | ABPR     | MAX6735KASHD3-T | AEIE     |

| MAX6732UTVDD3-T | ABPP     | MAX6735KATGD3-T | AEIH     |

| MAX6733UTLTD3-T | ABPW     | MAX6735KASDD3-T | AEID     |

| MAX6733UTSYD3-T | ABQB     | MAX6735KAZWD3-T | AEIO     |

| MAX6733UTSVD3-T | ABQA     | MAX6735KAZID3-T | AAJZ     |

| MAX6733UTRVD3-T | ABPX     | MAX6735KAYHD3-T | AEIM     |

| MAX6733UTSHD3-T | ABPZ     | MAX6735KAZGD3-T | AEIN     |

| MAX6733UTTGD3-T | ABQC     | MAX6735KAYDD3-T | AEIL     |

| MAX6733UTSDD3-T | ABPY     | MAX6735KAVHD3-T | AEIJ     |

| MAX6733UTZWD3-T | ABQJ     | MAX6735KAWGD3-T | AEIK     |

| MAX6733UTYHD3-T | ABQH     | MAX6735KAVDD3-T | AEII     |

**Note:** Sample stock is generally held on standard versions only. Standard versions have an order increment requirement of 2500 pieces. Nonstandard versions have an order increment requirement of 10,000 pieces. Contact factory for availability of nonstandard versions.

### \_Typical Operating Circuit

### **Chip Information**

TRANSISTOR COUNT: 1073 PROCESS: BICMOS

### Selector Guide

| PART NUMBER | VOLTAGE<br>MONITORS | RST OUTPUT | MANUAL RESET | WATCHDOG<br>INPUT | WATCHDOG<br>OUTPUT |

|-------------|---------------------|------------|--------------|-------------------|--------------------|

| MAX6730     | 1                   | Open Drain | $\checkmark$ | $\checkmark$      | Open Drain         |

| MAX6731     | 1                   | Push-Pull  | $\checkmark$ | $\checkmark$      | Push-Pull          |

| MAX6732     | 2                   | Open Drain | —            | $\checkmark$      | Open Drain         |

| MAX6733     | 2                   | Push-Pull  | —            | $\checkmark$      | Push-Pull          |

| MAX6734     | 3                   | Open Drain | $\checkmark$ | $\checkmark$      | Open Drain         |

| MAX6735     | 3                   | Push-Pull  | $\checkmark$ |                   | Push-Pull          |

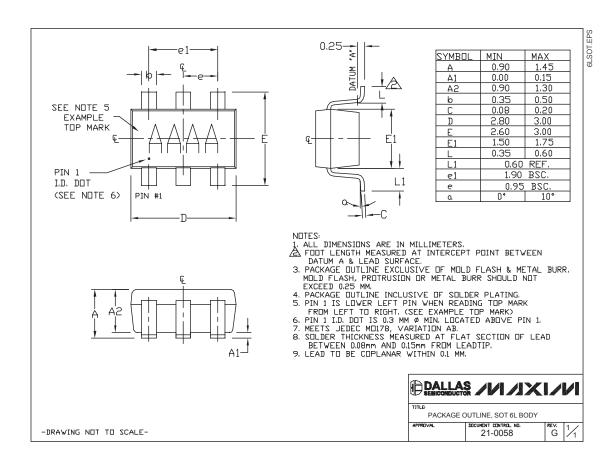

### Package Information

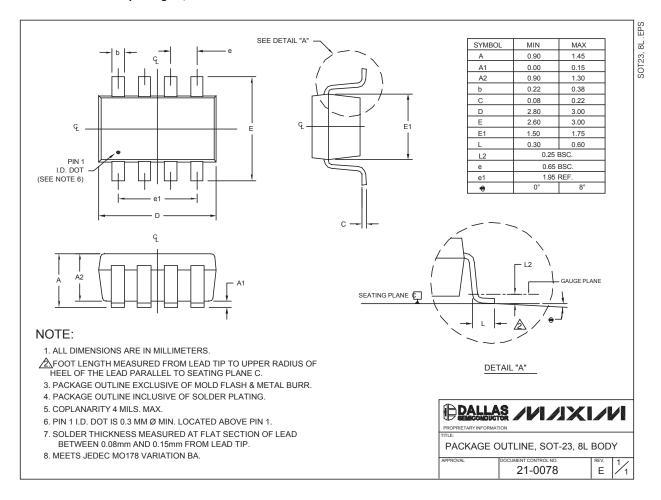

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

### \_Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

© 2005 Maxim Integrated Products Printed USA

16

**MAXIM** is a registered trademark of Maxim Integrated Products, Inc.