# MLX71121 300 to 930MHz FSK/FM/ASK Receiver

#### **Features**

| Dual RF input for antenna space and frequency diversity, LNA cascading or differential feeding |

|------------------------------------------------------------------------------------------------|

| Fully integrated PLL-based synthesizer                                                         |

| 2 <sup>nd</sup> mixer with image rejection                                                     |

| Reception of ASK or FSK modulated signals                                                      |

| Wide operating voltage                                                                         |

| Very low standby current consumption                                                           |

| Low operating current consumption                                                              |

| Internal IF filter                                                                             |

| Internal FSK demodulator                                                                       |

| Average or peak detection data slicer mode                                                     |

| RSSI output with high dynamic range for RF level indication                                    |

| Noise cancellation filter                                                                      |

| MCU clock output                                                                               |

| High over-all frequency accuracy                                                               |

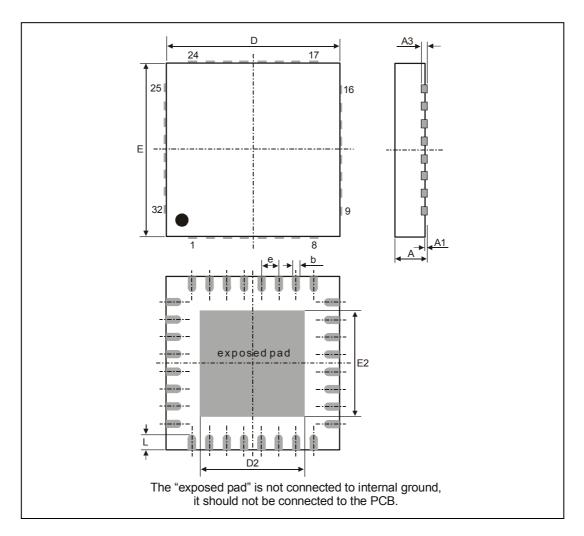

| 32-pin Quad Flat No-Lead Package (QFN)                                                         |

### **Ordering Information**

| Part Number | Temperature Code    | Package Code           | Delivery Form             |

|-------------|---------------------|------------------------|---------------------------|

| MLX71121    | C (-10 °C to 70 °C) | LQ (32 L QFN 5x5 Quad) | 73 pc/tube<br>5000 pc/T&R |

## **Application Examples**

General digital and analog RF receivers at 300 to 930MHz

Automatic meter reading (AMR)

Consumer remote controls

Low power telemetry systems

Alarm and security systems

Garage and gate controls

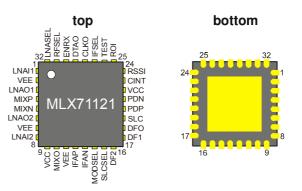

## Pin Description

## **General Description**

☐ Home and building automation

The MLX71121 is a multi-band, single-channel RF receiver based on a double-conversion super-heterodyne architecture. It can receive FSK and ASK modulated signals. The IC is designed for general purpose applications for example in the European bands at 433MHz and 868MHz or for similar applications in North America or Asia, for example at 315MHz or 915MHz.

## 300 to 930MHz FSK/FM/ASK Receiver

## **Document Content**

| 1 | The          | eory of Operation                         | 4        |

|---|--------------|-------------------------------------------|----------|

|   | 1.1          | General                                   | 4        |

|   | 1.2          | Technical Data Overview                   | 4        |

|   | 1.3          | Block Diagram                             | 5        |

|   | 1.4          | Operating Modes                           | 6        |

|   | 1.5          | LNA Selection                             | 6        |

|   | 1.6          | Mixer Section                             | 7        |

|   | 1.7          | IF Filter                                 | 7        |

|   | 1.8          | IF Amplifier                              | 7        |

|   | 1.9          | PLL Synthesizer                           | 7        |

|   | Refere       | ence Oscillator                           | 8        |

|   | 1.10         | Clock Output                              | 8        |

|   | 1.11         | FSK Demodulator                           | 8        |

|   | 1.12         | Baseband Data Path                        | <i>9</i> |

|   | 1.13         | Data Filter                               | 10       |

|   | 1.14<br>1.14 | Data Slicer                               |          |

|   | 1.14         | 4.2 Peak Detection Mode                   | 11       |

|   | 1.15         | Noise Cancellation Filter and Data Output | 12       |

| 2 | Fu           | nctional Description                      | 13       |

|   | 2.1          | Frequency Planning                        | 13       |

|   | 2.2          | Calculation of Frequency Settings         | 14       |

|   | 2.3          | Standard Frequency Plans                  | 15       |

|   | 2.4          | 433/868MHz Frequency Diversity            | 15       |

| 3 | Pir          | Definitions and Descriptions              | 16       |

| 4 |              | chnical Data                              |          |

| • | 4.1          | Absolute Maximum Ratings                  |          |

|   | 4.2          | Normal Operating Conditions               |          |

|   | 4.3          | DC Characteristics                        |          |

|   | 4.4          | AC System Characteristics                 |          |

|   | 4.5          | External Components                       |          |

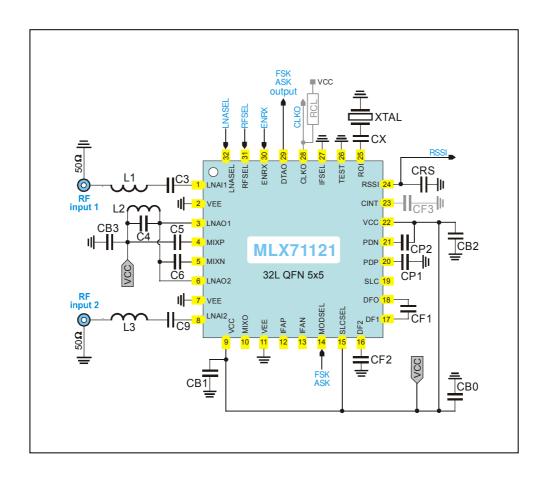

| 5 |              | st Circuit                                |          |

| J |              |                                           |          |

|   | 5.1<br>5.1.  | Antenna Diversity Application Circuit     |          |

|   | 0.7.         |                                           |          |

| 6 | Package Description |                       |    |  |  |

|---|---------------------|-----------------------|----|--|--|

|   | 6.1                 | Soldering Information | 26 |  |  |

| 7 | Re                  | liability Information | 27 |  |  |

| 8 | ES                  | D Precautions         | 27 |  |  |

| 9 | Dis                 | sclaimer              | 28 |  |  |

300 to 930MHz FSK/FM/ASK Receiver

### 1 Theory of Operation

#### 1.1 General

The MLX71121 receiver architecture is based on a double-conversion super-heterodyne approach. The two LO signals are derived from an on-chip integer-N PLL frequency synthesizer. The PLL reference frequency is derived from a crystal (XTAL). As the first intermediate frequency (IF1) is very high, a reasonably high degree of image rejection is provided even without using an RF front-end filter. At applications asking for very high image rejections, cost-efficient RF front-end filtering can be realized by using a SAW filter in front of the LNA. The second mixer MIX2 is an image-reject mixer.

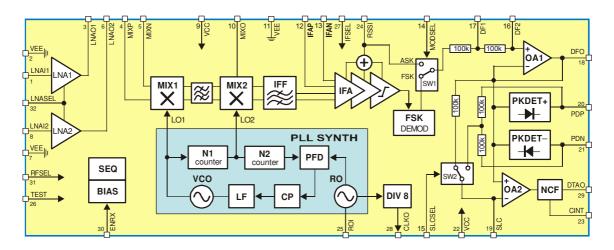

The receiver signal chain can be setup by one or two low noise amplifiers (LNA1, LNA2), two down-conversion mixers (MIX1, MIX2), an on-chip IF filter (IFF) as well as an IF amplifier (IFA). By choosing the required modulation via an FSK/ASK switch (at pin MODSEL), either the on-chip FSK demodulator (FSK DEMOD) or the RSSI-based ASK detector is selected. A second order data filter (OA1) and a data slicer (OA2) follow the demodulator. The data slicer threshold can be generated from the mean-value of the data stream or by means of the positive and negative peak detectors (PKDET+/-). Some post-processing of the data output signal can be performed by means a noise cancellation filter (NCF).

The dual LNA configuration can be used for antenna space diversity or antenna frequency diversity or to setup an LNA cascade (to further improve the input sensitivity). Another option is to set up the two LNAs for feeding the RF signal differentially.

A sequencer circuit (SEQ) controls the timing during start-up. This is to reduce start-up time and to minimize power dissipation.

A clock output, which is a divide-by-8 version of the crystal oscillator signal, can be used to drive a microcontroller. The clock output is an open drain and gets activated only if a loading resistor is connected to positive supply.

#### 1.2 Technical Data Overview

| Input frequency ranges: 300 to 470MHz         | Image rejection:                                            |

|-----------------------------------------------|-------------------------------------------------------------|

| 610 to 930MHz                                 | 65dB 1 <sup>st</sup> IF (with external RF front-end filter) |

| Power supply range: 2.1 to 5.5V               | 25dB 2 <sup>nd</sup> IF (internal image rejection)          |

| Temperature range: -10 to +70°C               | Maximum data rate: 50kps RZ (bi-phase) code                 |

| Shutdown current: 50 nA                       | 100kps NRZ                                                  |

| Operating current: 10.0 to 11.1mA             | Spurious emission: < -54dBm                                 |

| FSK input sensitivity: -107dBm* (433MHz)      | Usable RSSI range: 45 to 55dB                               |

| ASK input sensitivity: -112dBm* (433MHz)      | Crystal frequency: 16 to 27MHz                              |

| Internal IF: 1.8MHz with 300kHz 3dB bandwidth | MCU clock frequency: 2.0 to 3.4MHz                          |

| FSK deviation range: ±10kHz to ±100kHz        |                                                             |

<sup>\*</sup> at 4kbps NRZ, BER =  $3\cdot10^{-3}$ , at LNA input pins

300 to 930MHz FSK/FM/ASK Receiver

#### 1.3 Block Diagram

Fig. 1: MLX71121 block diagram

The MLX71121 receiver IC consists of the following building blocks:

- PLL synthesizer (PLL SYNTH) to generate the first and second local oscillator signals LO1 and LO2. The PLL SYNTH consists of a fully integrated voltage-controlled oscillator (VCO), a distributed feedback divider chain (N1,N2), a phase-frequency detector (PFD) a charge pump (CP), a loop filter (LF) and a crystal-based reference oscillator (RO).

- Two low-noise amplifiers (LNA1, LNA2) for high-sensitivity RF signal reception

- First mixer (MIX1) for down-conversion of the RF signal to the first IF (intermediate frequency)

- Second mixer (MIX2) with image rejection for down-conversion from the first to the second IF

- IF Filter (IFF) with a 1.8MHz center frequency and a 300kHz 3dB bandwidth

- IF amplifier (IFA) to provide a high voltage gain and an RSSI signal output

- FSK demodulator (FSK DEMOD)

- Operational amplifiers OA1 and OA2 for low-pass filtering and data slicing, respectively

- Positive (PKDET+) and negative (PKDET-) peak detectors

- Switches SW1 to select between FSK and ASK as well as SW2 to chose between averaging or peak detection mode.

- Noise cancellation filter (NCF)

- · Sequencer circuit (SEQ) and biasing (BIAS) circuit

- Clock output (DIV8)

# MLX71121 300 to 930MHz

300 to 930MHz FSK/FM/ASK Receiver

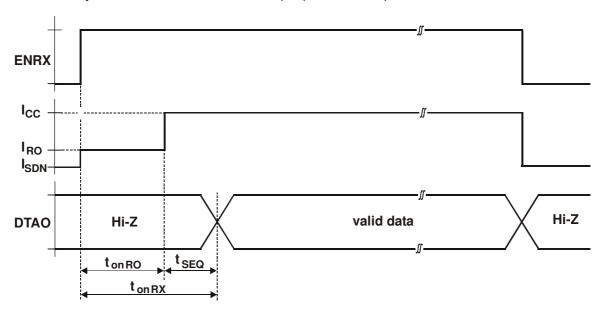

#### 1.4 Operating Modes

The receiver offers two operating modes selectable by setting the corresponding logic level at pin ENRX.

| ENRX | Description   |  |

|------|---------------|--|

| 0    | Shutdown mode |  |

| 1    | Receive mode  |  |

Note: ENRX is pulled down internally.

The receiver's start-up procedure is controlled by a sequencer circuit. It performs the sequential activation of the different building blocks. It also initiates the pre-charging of the data filter and data slicer capacitors in order to reduce the overall start-up time and current consumption during the start-up phase.

At ENRX = 0, the receiver is in shutdown mode and draws only a few nA. The bias system and the reference oscillator are activated after enabling the receiver by a positive edge at pin ENRX. The crystal oscillator (RO) is turned on first. Then the crystal oscillation amplitude builds up from noise. After reaching a certain amplitude level at pin ROI, the whole IC is activated and draws the full receive mode current consumption  $I_{CC}$ . This event is used to start the pre-charging of the external data path capacitors. Pre-charging is finished after 5504 clock cycles. After that time the data output pin DTAO output is activated.

Fig. 2: Timing diagram of start-up and shutdown behavior

#### 1.5 LNA Selection

The receiver features two identical LNAs. Each LNA is a cascode amplifier with a voltage gain of approximately 18dB. The actual gain depends on the antenna matching network at the inputs and the LC tank network between the LNA outputs and mixer input. LNA operation can be controlled by the LNASEL pin.

| LNASEL | Description                |  |

|--------|----------------------------|--|

| 0      | LNA1 active, LNA2 shutdown |  |

| Hi-Z   | LNA1 and LNA2 active       |  |

| 1      | LNA1 shutdown, LNA2 active |  |

Pin LNASEL is internally pulled to VCC/2 during receive mode. Therefore both LNAs are active if LNASEL is left floating (Hi-Z state).

300 to 930MHz FSK/FM/ASK Receiver

#### 1.6 Mixer Section

The mixer section consists of two mixers. Both are double-balanced mixers. The second mixer is built as an image rejection mixer. The first mixer's inputs (MIXP and MIXN) are functionally the same. For single-ended drive, the unused input has to be tied to ground via a capacitor. A soft band-pass filter is placed between the mixers.

| RFSEL | Description                         |

|-------|-------------------------------------|

| 0     | Input frequency range 300 to 470MHz |

| 1     | Input frequency range 610 to 930MHz |

Pin RFSEL is used to select the required RF band. The LO frequencies and the proper sidebands for image suppression will be set accordingly.

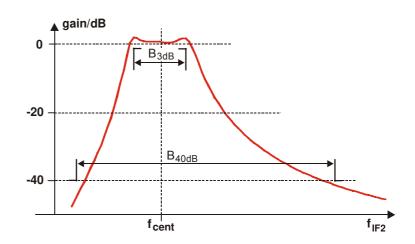

#### 1.7 IF Filter

The MLX71121 comprises an internal IF filter with a -3dB bandwidth (B3dB) of 300kHz and a -40dB attenuation bandwidth (B40dB) of 1.4MHz. This filter contains three capacitively coupled biquad stages that represent resonant tanks at a filter center frequency (f<sub>cent</sub>) of 1.8MHz

Fig. 3: IF filter tolerance scheme

#### 1.8 IF Amplifier

After having passed the IF filter, the signal is amplified by a high-gain limiting amplifier. It consists of several AC-coupled gain stages with a bandwidth of 400kHz to 11MHz. The overall small-signal pass-band gain is about 80dB. A received-signal-strength indicator (RSSI) signal is generated within the IF amplifier and is available at pin RSSI.

#### 1.9 PLL Synthesizer

The PLL synthesizer consists of a fully integrated voltage-controlled oscillator that runs at 400MHz to 640MHz, a distributed feedback divider chain, an edge-triggered phase-frequency detector, a charge pump, a loop filter and a crystal-based reference oscillator. The PLL is used for generating the LO signals. The LO1 is directly taken from the VCO output, and the LO2 is derived from the LO1 signal passing the N1 counter. Another counter N2 follows N1 to provide the comparison frequency to the PFD. The overall feedback divider ratio  $N_{tot}$  is 24. The values of N1 and N2 can be changed via pin RFSEL for selecting the LO1 and LO2 frequencies. The table below shows the range of the LO frequencies.

| RFSEL | f <sub>LO1min</sub><br>[MHz] | f <sub>LO1max</sub><br>[MHz] | f <sub>LO2min</sub><br>[MHz] | f <sub>LO2max</sub><br>[MHz] | N <sub>1</sub> | N <sub>2</sub> | N <sub>tot</sub> |

|-------|------------------------------|------------------------------|------------------------------|------------------------------|----------------|----------------|------------------|

| 0     | 400                          | 640                          | 100                          | 160                          | 4              | 6              | 24               |

| 1     | 400                          | 640                          | 200                          | 320                          | 2              | 12             | 24               |

300 to 930MHz FSK/FM/ASK Receiver

#### Reference Oscillator

A Colpitts crystal oscillator with integrated functional capacitors is used as the reference oscillator (RO) of the PLL synthesizer. The equivalent input capacitance CRO offered to the crystal at pin ROI is about 18pF. The crystal oscillator features an amplitude control loop. This is to assure a very stable frequency over the specified supply voltage and temperature range together with a short start-up time. A buffer amplifier with hysteresis is between RO and PFD. Also a clock divider follows the buffer.

#### 1.10 Clock Output

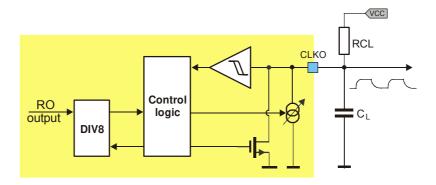

The clock output pin CKOUT is an open-drain output. For power saving reasons, the circuit is only active if an external pull-up resistor RCL is applied to the pin. Furthermore, RCL can be used to adjust the clock waveform. It forms an RC low-pass together with the capacitive load at the pin, the parasitics of the PCB and the input capacitance of the external circuitry (e.g. a microcontroller).

The clock output feature is disabled if pin CKOUT is connected to ground or left open.

Fig. 4: Clock output implementation

#### 1.11 FSK Demodulator

The integrated FSK demodulator is based on a phase-coincidence demodulator principle. An injection-locked oscillator (ILO) is used as a frequency-dependent phase shifter. This topology features a good linearity of the frequency-phase relationship over the entire locking range. The type of demodulator has no built-in constraints regarding the modulation index. It also offers a wide carrier acceptance range.

In addition, the demodulator provides an AFC loop for correcting the remaining free-running frequency error and drift effects, and also to remove possible frequency offsets between transmitter and receiver frequencies. The AFC loop features a dead band which means that the AFC loop is only closed if the demodulator output voltage leaves the linear region of the demodulator. Most of the time, the control loop is open. This leads to several advantages. The AFC loop bandwidth can be high and therefore the reaction time is short. Furthermore the demodulator itself has no low-end cut-off frequency.

The FSK demodulator has a negative control slope, this means the output voltage decreases by increasing the IF2 frequency. This guarantees an overall positive slope because the mixer section converts the receive frequency to IF2 either with high-low or low-high side injection.

The FSK demodulator is turned off during ASK demodulation.

300 to 930MHz FSK/FM/ASK Receiver

#### 1.12 Baseband Data Path

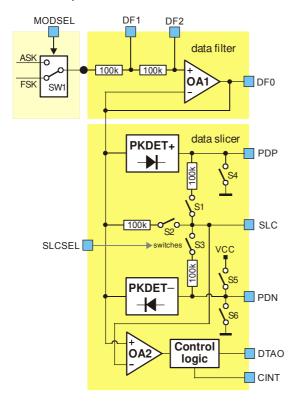

The baseband data path can be divided into a data filter section and a data slicer section.

Fig. 5: Block diagram of the data path

The data filter input is either connected to the ASK or to the FSK demodulation output. Pin MODSEL can be used to set the internal switch SW1 accordingly.

| MODSEL | Description      |

|--------|------------------|

| 0      | ASK demodulation |

| 1      | FSK demodulation |

For ASK demodulation, the RSSI signal of the IFA is used. During FSK demodulation, SW1 is connected to the FSK demodulator output.

The SLCSEL pin is used to control the internal switches depending on operating and slicer mode.

Pins DF1, DF2, DFO, SLC and DTAO are left floating during shutdown mode. So they are in a high-Z state.

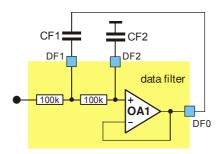

#### 1.13 Data Filter

The data filter is formed by the operational amplifier OA1, two internal  $100k\Omega$  resistors and two external capacitors. It is implemented as a  $2^{nd}$  order Sallen-Key filter. The low pass filter characteristic rejects noise at higher frequencies and therefore leads to an increased sensitivity.

Fig. 6: Data filter

The filter's pole locations can be set by the external capacitors CF1 and CF2. The cut-off frequency  $f_c$  has to be adjusted according to the transmission data rate R. It should be set to approximately 1.5 times the fastest expected data rate. For a Butterworth filter characteristic, the data filter capacitors can be calculated as follows.

$$CF1 = \frac{1}{\sqrt{2} \cdot \pi \cdot 100k \cdot f_{c}}$$

$$CF2 = \frac{CF1}{2}$$

| R <sub>RZ</sub> [kbit/s] | R <sub>NRZ</sub> [kbit/s] | fc [kHz] | CF1 [pF] | CF2 [pF] |

|--------------------------|---------------------------|----------|----------|----------|

| 0.6                      | 1.2                       | 0.9      | 2200     | 1000     |

| 1.2                      | 2.4                       | 1.8      | 1200     | 680      |

| 1.6                      | 3.2                       | 2.4      | 1000     | 470      |

| 2.4                      | 4.8                       | 3.6      | 680      | 330      |

| 3.3                      | 6.6                       | 5        | 470      | 220      |

| 4.8                      | 9.6                       | 7.2      | 330      | 150      |

| 6.0                      | 12                        | 9        | 220      | 100      |

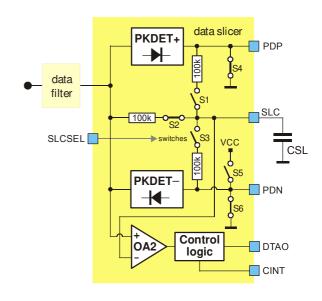

#### 1.14 Data Slicer

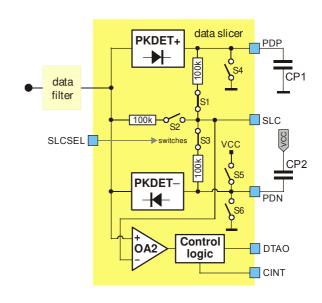

The purpose of the data slicer is to convert the filtered data signal into a digital output. It can therefore be considered as an analog-to-digital converter. This is done by using the operational amplifier OA2 as a comparator that compares the data filter output with a threshold voltage. The threshold voltage can be derived in two different ways from the data signal.

| SLCSEL | Description              |

|--------|--------------------------|

| 0      | Averaging detection mode |

| 1      | Peak detection mode      |

300 to 930MHz FSK/FM/ASK Receiver

#### 1.14.1 Averaging Detection Mode

The simplest configuration is the averaging or RC integration method. Here an on-chip  $100k\Omega$  resistor together with an external slicer capacitor (CSL) are forming an RC low-pass filter. This way the threshold voltage automatically adjusts to the mean or average value of the analog input voltage.

To create a stable threshold voltage, the cut-off frequency of the low pass has to be lower than the lowest signal frequency.

$$CSL \ge \frac{\tau_{AVG}}{100k} \qquad \qquad \tau_{AVG} = \frac{1.5}{R_{RZ}}$$

A long string of zeros or ones, like in NRZ codes, can cause a drift of the threshold. That's why a Manchester or other DC-free coding scheme works best.

The peak detectors are disabled during averaging detection mode, and the output pins PDP and PDN are pulled to ground (S4, S6 are closed).

Fig. 7: Data path in averaging detection mode

#### 1.14.2 Peak Detection Mode

Peak detection mode has a general advantage over averaging detection mode because of the part attack and slow release times. Peak detection should be used for all non DC-free codes like NRZ. In this configuration the threshold is generated by using the positive and negative peak detectors. The slicer comparator threshold is set to the midpoint between the high output and the low output of the data filter by an on-chip resistance divider. Two external capacitors (CP1, CP2) determine the release times for the positive and negative envelope. The two on-chip resistors provide a path for the capacitors to discharge. This allows the peak detectors to dynamically follow peak changes of the data filter output voltage. The attack times are very short due to the high peak detector load currents of about 500uA.

The decay time constant mainly depends on the longest time period without bit polarity change. This corresponds to the maximum number of consecutive bits with the same polarity  $(N_{\text{MAX}})$ .

$$CP1/2 \ge \frac{\tau_{DECAY}}{100k} \qquad \qquad \tau_{DECAY} = \frac{N_{MAX}}{R_{NRZ}}$$

Fig. 8: Data path in peak detection mode

If the receiver is in shutdown mode and peak detection mode is selected then the peak detectors are disabled and the output of the positive peak detector (PDP) is connected to VEE (S4 is closed) and the output of the negative peak detector (PDN) is connected to VCC (S5 is closed). This guarantees the correct biasing of CP1 and CP2 during start-up.

300 to 930MHz FSK/FM/ASK Receiver

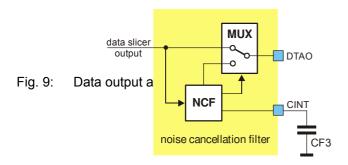

#### 1.15 Noise Cancellation Filter and Data Output

The data output pin DTAO delivers the demodulated data signal which can be further processed by a noise cancellation filter (NCF). **The NCF can be disabled if pin CINT is connected to ground.** In this case the multiplexer (MUX) connects the receiver output DTAO directly to the data slicer output.

The noise cancellation filter can suppress random pulses in the data output which are shorter than  $t_{min}$ .

CF3 =

$$15 \cdot 10^{-6} \cdot t_{\min} = \frac{15 \cdot 10^{-6}}{R_{NRZ}} = \frac{7.5 \cdot 10^{-6}}{R_{RZ}}$$

The NCF can also operate as a muting circuit. So if the RF input signal is below sensitivity level (or if no RF signal is applied) then the data output will go to a constant DC level (either HIGH or LOW). This can be achieved by setting the bandwidth of the preceding data filter (sec 1.13) about 10 times higher than the bandwidth of the NCF.

Having the NCF activated is a good means for reducing the computing power of the microcontroller that follows the receiver IC for further data processing.

In contrast to a conventional muting (or squelch) circuit, this topology does not need the RSSI signal for level indication. The filtering process is done by means of an analogue integrator. The cut-off frequency of the NCF is set by the external capacitor connected to pin CINT. This capacitor  $C_{F3}$  should be set according to the maximum data rate. Below table provides some recommendations..

During receiver start-up a sequencer checks if pin CINT is connected to a capacitor or to ground. The maximum value of  $C_{F3}$  should not exceed 12nF. This defines the lowest data rate that can be processed if the noise cancellation filter is activated.

| R <sub>RZ</sub> [kbit/s] | R <sub>NRZ</sub> [kbit/s] | C <sub>F3</sub> [nF] |

|--------------------------|---------------------------|----------------------|

| 0.6                      | 1.2                       | 12                   |

| 1.2                      | 2.4                       | 6.8                  |

| 1.6                      | 3.2                       | 4.7                  |

| 2.4                      | 4.8                       | 3.3                  |

| 3.3                      | 6.6                       | 2.2                  |

| 4.8                      | 9.6                       | 1.5                  |

| 6.0                      | 12                        | 1.2                  |

In shutdown mode pin DTAO is set to Hi-Z state.

### 2 Functional Description

#### 2.1 Frequency Planning

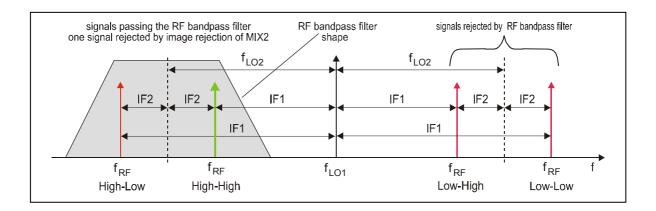

Because of the double conversion architecture that employs two mixers and two IF signals, there are four different combinations for injecting the LO1 and LO2 signals:

LO1 high side and LO2 high side: receiving at f<sub>RF</sub>(high-high)

LO1 high side and LO2 low side: receiving at f<sub>RF</sub>(high-low)

LO1 low side and LO2 high side: receiving at f<sub>RF</sub>(low-high)

LO1 low side and LO2 low side: receiving at f<sub>RF</sub>(low-low)

As a result, four different radio frequencies (RFs) could yield one and the same second IF (IF2). Fig. 10 shows this for the case of receiving at  $f_{RF}$ (high-high). In the example of Fig. 10, the image signals at  $f_{RF}$ (low-high) and  $f_{RF}$ (low-low) are suppressed by the bandpass characteristic provided by the RF front-end. The bandpass shape can be achieved either with a SAW filter (featuring just a couple of MHz bandwidth), or by the tank circuits at the LNA input and output (this typically yields 30 to 60MHz bandwidth). In any case, the high value of the first IF (IF1) helps to suppress the image signals at  $f_{RF}$ (low-high) and  $f_{RF}$ (low-low).

The two remaining signals at IF1 resulting from  $f_{RF}(high-high)$  and  $f_{RF}(high-low)$  are entering the second mixer MIX2. This mixer features image rejection with so-called single-sideband (SSB) selection. This means either the upper or lower sideband of IF1 can be selected. In the example of Fig. 10, LO2 high-side injection has been chosen to select the IF2 signal resulting from  $f_{RF}(high-high)$ .

Fig. 10: The four receiving frequencies in a double conversion superhet receiver

It can be seen from the block diagram of Fig. 1 that there is a fixed relationship between the LO signal frequencies ( $f_{LO1}$ ,  $f_{LO2}$ ) and the reference oscillator frequency  $f_{RO}$ .

$$\mathbf{f}_{\text{LO1}} = \mathbf{N}_1 \cdot \mathbf{f}_{\text{LO2}} \qquad \qquad \mathbf{f}_{\text{LO2}} = \mathbf{N}_2 \cdot \mathbf{f}_{\text{RO}}$$

The operating frequency of the internal IF filter (IFF) and FSK demodulator (FSK DEMOD) are 1.8MHz. Therefore the second IF (IF2) is set to 1.8MHz as well.

300 to 930MHz FSK/FM/ASK Receiver

#### 2.2 Calculation of Frequency Settings

The receiver has two predefined receive frequency plans which can be selected by the RFSEL control pin. Depending on the logic level of RFSEL pin the sideband selection of the second mixer and the counter settings for  $N_1$  and  $N_2$  are changed accordingly.

| RFSEL | Injection | f <sub>RFmin</sub> [MHz] | f <sub>RFmax</sub> [MHz] | N <sub>1</sub> | N <sub>2</sub> |

|-------|-----------|--------------------------|--------------------------|----------------|----------------|

| 0     | high-low  | 300                      | 470                      | 4              | 6              |

| 1     | low-high  | 610                      | 930                      | 2              | 12             |

The following table shows the relationships of several internal receiver frequencies for the two input frequency ranges.

| f <sub>RF</sub> [MHz] | f <sub>IF1</sub>                                                           | f <sub>LO1</sub>                            | f <sub>LO2</sub>                   | f <sub>RO</sub>                         |

|-----------------------|----------------------------------------------------------------------------|---------------------------------------------|------------------------------------|-----------------------------------------|

| 300 to 470            | $\frac{f_{RF} + N_1 f_{IF2}}{N_1 - 1}$                                     | $\frac{N_{1}(f_{RF} + f_{IF2})}{N_{1} - 1}$ | $\frac{f_{RF} + f_{IF2}}{N_1 - 1}$ | $\frac{f_{RF} + f_{IF2}}{N_2(N_1 - 1)}$ |

| 610 to 930            | $\frac{\mathbf{f}_{RF} - \mathbf{N}_1 \mathbf{f}_{IF2}}{\mathbf{N}_1 + 1}$ | $\frac{N_{1}(f_{RF} + f_{IF2})}{N_{1} + 1}$ | $\frac{f_{RF} + f_{IF2}}{N_1 + 1}$ | $\frac{f_{RF} + f_{IF2}}{N_2(N_1 + 1)}$ |

Given IF2 = 1.8MHz and the corresponding  $N_1$ ,  $N_2$  counter settings, above equations can be transferred into the following table.

| f <sub>RF</sub> [MHz] | f <sub>IF1</sub>  | f <sub>LO1</sub>              | f <sub>LO2</sub>  | f <sub>RO</sub>               |

|-----------------------|-------------------|-------------------------------|-------------------|-------------------------------|

| 300 to 470            | $f_{RF} + 7.2MHz$ | $\frac{4(f_{RF} + 1.8MHz)}{}$ |                   | $\underline{f_{RF} + 1.8MHz}$ |

|                       | 3                 | 3                             | $f_{RF} + 1.8MHz$ | 18                            |

| 610 to 930            | $f_{RF} - 3.6MHz$ | $2(f_{RF} + 1.8MHz)$          | 3                 | $\underline{f_{RF}} + 1.8MHz$ |

|                       | 3                 | 3                             |                   | 36                            |

## 300 to 930MHz FSK/FM/ASK Receiver

#### 2.3 Standard Frequency Plans

IF2 = 1.8MHz

| RFSEL | f <sub>RF</sub> [MHz] | f <sub>IF1</sub> [MHz] | f <sub>LO1</sub> [MHz] | f <sub>LO2</sub> [MHz] | f <sub>RO</sub> [MHz] |

|-------|-----------------------|------------------------|------------------------|------------------------|-----------------------|

| 0     | 315                   | 107.40                 | 422.40                 | 105.60                 | 17.600000             |

|       | 433.92                | 147.04                 | 580.96                 | 145.24                 | 24.206667             |

| 1     | 868.3                 | 288.23                 | 580.07                 | 290.03                 | 24.169444             |

| I     | 915                   | 303.80                 | 611.20                 | 305.60                 | 25.466667             |

#### 2.4 433/868MHz Frequency Diversity

The receiver's multi-band functionality can be used to operate at two different frequency bands just by changing the logic level at pin RFSEL and without changing the crystal. This feature is applicable for common use of the 433 and 868MHz bands. Below table shows the corresponding frequency plans.

IF2 = 1.8MHz

| RFSEL | f <sub>RF</sub> [MHz] | f <sub>IF1</sub> [MHz] | f <sub>LO1</sub> [MHz] | f <sub>LO2</sub> [MHz] | f <sub>RO</sub> [MHz] |

|-------|-----------------------|------------------------|------------------------|------------------------|-----------------------|

| 0     | 433.25                | 146.82                 | 580.07                 | 145.02                 | 24.169444             |

| 1     | 868.3                 | 288.23                 | 580.07                 | 290.03                 | 24.109444             |

300 to 930MHz FSK/FM/ASK Receiver

# 3 Pin Definitions and Descriptions

| Pin No. | Name   | I/O Type         | Functional Schematic                                         | Description                 |

|---------|--------|------------------|--------------------------------------------------------------|-----------------------------|

| 3       | LNAO1  | analog<br>output | Vbias LNAO1                                                  | LNA output 1                |

| 1       | LNAI1  | analog<br>input  | LNAI1 VEE                                                    | LNA input 1                 |

| 2       | VEE    | ground           |                                                              | negative supply voltage     |

| 4       | MIXP   | analog<br>input  | VCC Vbias VCC                                                | MIX1 positive input         |

| 5       | MIXN   | analog<br>input  | 4 VEE VEE                                                    | MIX1 negative input         |

| 6       | LNAO2  | analog<br>output | Vbias LNAO2 Vbias Vbias VEE                                  | LNA output 2                |

| 8       | LNAI2  | analog<br>input  | LNAI2 VEE                                                    | LNA input 2                 |

| 7       | VEE    | ground           |                                                              | negative supply voltage     |

| 9       | VCC    | supply           |                                                              | positive supply voltage     |

| 10      | MIXO   | analog<br>output | not used<br>pin left open                                    | mixer 2 output              |

| 11      | VEE    | ground           |                                                              | negative supply voltage     |

| 12      | IFAP   | analog<br>input  | not used                                                     | IF amplifier positive input |

| 13      | IFAN   | analog<br>input  | pins left open                                               | IF amplifier negative input |

| 14      | MODSEL | CMOS<br>input    | MODSEL VCC VCC MODSEL VCC VCC VCC VCC VCC VCC VCC VCC VCC VC | modulation select input     |

| Pin No. | Name   | I/O Type         | Functional Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                   |

|---------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 15      | SLCSEL | CMOS<br>input    | SLCSEL VCC | slicer mode select input      |

| 16      | DF2    | analog<br>I/O    | DF2 400 VCC P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | data filter connection 2      |

| 17      | DF1    | analog<br>I/O    | DF1 VCC WOOD WCC WOOD WCC WOOD WCC WOOD WCC WOOD WCC WCC WCC WCC WCC WCC WCC WCC WCC WC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | data filter connection 1      |

| 18      | DFO    | analog<br>output | DFO 400 VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | data filter output            |

| 19      | SLC    | analog<br>input  | SLC   100k   100k   19   VEE   100k   100k  | slicer reference input        |

| 20      | PDP    | analog<br>output | PDP 400 VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | peak detector positive output |

| 21      | PDN    | analog<br>output | PDN 400 VEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | peak detector negative output |

| Pin No. | Name  | I/O Type         | Functional Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                 |

|---------|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 22      | VCC   | supply           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | positive supply voltage                                                                                                     |

| 23      | CINT  | analog<br>input  | CINT VCC P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | capacitor for noise cancella-<br>tion filter pin must be connected to<br>ground if noise cancellation<br>filter is not used |

| 24      | RSSI  | analog<br>output | RSSI 400 VEE VEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | receive signal strength indication                                                                                          |

| 25      | ROI   | analog<br>input  | VCC III VCC II | reference oscillator input                                                                                                  |

| 26      | TEST  | CMOS input       | not used connect to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | test pin                                                                                                                    |

| 27      | IFSEL | CMOS input       | not used connect pin to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IF select input                                                                                                             |

| 28      | CLKO  | CMOS<br>output   | CLKO CLKO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | clock output<br>connect pull-up resistor<br>to activate clock                                                               |

| 29      | DTAO  | CMOS<br>output   | DTAO VCC VCC VCC VCC VCC VCC VCC VCC VCC VC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | data output                                                                                                                 |

| 30      | ENRX  | CMOS<br>input    | ENRX 400 VCC VCC VCC VCC VCC VCC VCC VCC VCC V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | enable RX mode control                                                                                                      |

| Pin No. | Name   | I/O Type      | Functional Schematic                            | Description                    |

|---------|--------|---------------|-------------------------------------------------|--------------------------------|

| 31      | RFSEL  | CMOS<br>input | RFSEL 400 VCC VCC VCC VCC VCC VCC VCC VCC VCC V | receive frequency select input |

| 32      | LNASEL | CMOS<br>input | LNASEL 400 32 VEE                               | LNA select input               |

300 to 930MHz FSK/FM/ASK Receiver

### 4 Technical Data

### 4.1 Absolute Maximum Ratings

Operation beyond absolute maximum ratings may cause permanent damage of the device.

| Parameter               | Symbol            | Condition                                    | Min  | Max                  | Unit |

|-------------------------|-------------------|----------------------------------------------|------|----------------------|------|

| Supply voltage          | V <sub>CC</sub>   |                                              | 0    | 7                    | V    |

| Input voltage           | V <sub>IN</sub>   |                                              | -0.3 | V <sub>CC</sub> +0.3 | V    |

| Storage temperature     | T <sub>STG</sub>  |                                              | -55  | 150                  | °C   |

| Junction temperature    | T <sub>J</sub>    |                                              |      | 150                  | °C   |

| Thermal Resistance      | R <sub>thJA</sub> |                                              |      | 22                   | K/W  |

| Power dissipation       | P <sub>diss</sub> |                                              |      | 0.12                 | W    |

| Electrostatic discharge | V <sub>ESD</sub>  | HBM according to MIL STD 833D, method 3015.7 | ±1   |                      | kV   |

## 4.2 Normal Operating Conditions

| Parameter                 | Symbol           | Condition                                        | Min                 | Max                 | Unit  |  |

|---------------------------|------------------|--------------------------------------------------|---------------------|---------------------|-------|--|

| Supply voltage            | $V_{CC}$         |                                                  | 2.1                 | 5.5                 | V     |  |

| Operating temperature     | T <sub>A</sub>   |                                                  | -10                 | 70                  | °C    |  |

| Input low voltage (CMOS)  | V <sub>IL</sub>  | ENRX, SEL pins                                   |                     | 0.3*V <sub>CC</sub> | V     |  |

| Input high voltage (CMOS) | V <sub>IH</sub>  | ENRX, SEL pins                                   | 0.7*V <sub>CC</sub> |                     | V     |  |

| Input frequency range     | f                | RFSEL=0                                          | 300                 | 470                 | MHz   |  |

| Input frequency range     | f <sub>RF</sub>  | RFSEL=1                                          | 610                 | 930                 | IVIHZ |  |

| First IF range            | f                | RFSEL=0                                          | 100                 | 170                 | MHz   |  |

|                           | f <sub>IF1</sub> | RFSEL=1                                          | 200                 | 310                 |       |  |

| LO1 range (VCO frequency) | f <sub>LO1</sub> | $f_{LO1} = 24*f_{REF}$                           | 400                 | 640                 | MHz   |  |

| LO2 range                 | f <sub>LO2</sub> | RFSEL=0, f <sub>LO2</sub> = f <sub>LO1</sub> / 4 | 100                 | 160                 | MHz   |  |

| LO2 range                 |                  | RFSEL=1, f <sub>LO2</sub> = f <sub>LO1</sub> / 2 | 200                 | 320                 |       |  |

| XOSC frequency            | f <sub>REF</sub> | set by the crystal                               | 16                  | 27                  | MHz   |  |

| CLKO frequency            | f <sub>CLK</sub> | f <sub>CLK</sub> = f <sub>REF</sub> / 8          | 2.0                 | 3.375               | MHz   |  |

| FSK deviation             | Δf               |                                                  | ±10                 | ±100                | kHz   |  |

| Data rata ACK             | П                | bi-phase code                                    |                     | 50                  | kbps  |  |

| Data rate ASK             | R <sub>ASK</sub> | NRZ                                              |                     | 100                 |       |  |

| Data rata FSV             | В                | bi-phase code                                    |                     | 50                  |       |  |

| Data rate FSK             | R <sub>FSK</sub> | NRZ                                              |                     | 100                 |       |  |

300 to 930MHz FSK/FM/ASK Receiver

#### 4.3 DC Characteristics

all parameters under normal operating conditions, unless otherwise stated; typical values at  $T_A$ = 23 °C and  $V_{CC}$ = 3 V, all parameters based on test circuits as shown Fig. 11

| Parameter                           | Symbol               | Condition                                       | Min                 | Тур  | Max                 | Unit |

|-------------------------------------|----------------------|-------------------------------------------------|---------------------|------|---------------------|------|

| Operating Currents                  |                      |                                                 |                     |      |                     |      |

| Shutdown current                    | I <sub>SDN</sub>     | ENRX=0, T <sub>A</sub> = 70°C                   |                     | 50   | 150                 | nA   |