# TAS5508-5142K7EVM User's Guide

Evaluation Module for the TAS5508B Digital Audio PWM Processor and TAS5142 Digital Amplifier Power Output Stage

User's Guide

2

## **Contents**

| 1   | Overview |                                                        |     |

|-----|----------|--------------------------------------------------------|-----|

|     | 1.1      | TAS5508-5142K7EVM Features                             | . 6 |

|     | 1.2      | PCB Key Map                                            | . 7 |

| 2   | Syst     | em Interfaces                                          | . 9 |

|     | 2.1      | Power Supply (PSU) Interface (J901 and J900)           | . 9 |

|     | 2.2      | PSU Control Interface (J902)                           | 10  |

|     | 2.3      | Loudspeaker Connectors (J101 J107)                     | 10  |

|     | 2.4      | Headphone Connector (J700)                             | 11  |

|     | 2.5      | Control Interface (J40)                                | 11  |

|     | 2.6      | Digital Audio Interface (J60)                          | 13  |

| 3   | Prot     | ection                                                 | 15  |

|     | 3.1      | Short-Circuit Protection and Fault-Reporting Circuitry | 15  |

|     | 3.2      | Fault Reporting                                        |     |

| 4   | Rela     | ted Documentation From Texas Instruments               | 17  |

|     | 4.1      | Trademarks                                             | 17  |

| Imp | ortant   | Notices                                                | 18  |

## List of Figures

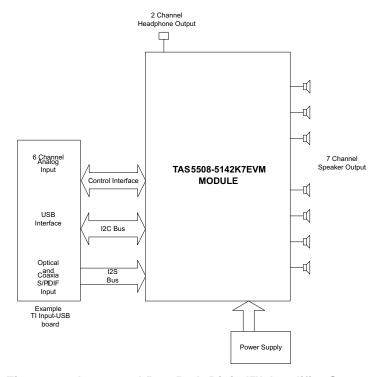

| 1-1 | Integrated PurePath Digital™ Amplifier System            | . 6 |

|-----|----------------------------------------------------------|-----|

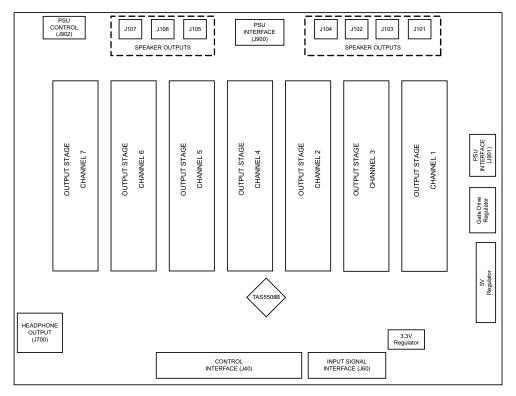

| 1-2 | Physical Structure for TAS5508-5142K7EVM (Rough Outline) | . 7 |

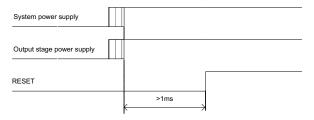

| 2-1 | Recommended Power-Up Sequence                            |     |

| 2-2 | J901 and J900 Pin Numbers                                | . 9 |

| 2-3 | J902 Pin Numbers                                         | 10  |

| 2-4 | J101 J107 Pin Numbers                                    |     |

| 2-5 | J700 Pin Numbers                                         | 11  |

| 2-1 | List of Tables  Recommended Supply Voltages              | 0   |

| 2-1 | J901 Pin Description                                     |     |

| 2-3 | J900 Pin Description                                     | 10  |

| 2-4 | J902 Pin Description                                     |     |

| 2-5 | J101 J107 Pin Description                                | 11  |

| 2-6 | J700 Pin Description                                     | 11  |

| 2-7 | J40 Pin Description                                      | 11  |

| 2-8 | J60 Pin Description                                      | 13  |

| 3_1 | TASS142 Warning/Error Signal Decoding                    | 15  |

### **Overview**

The TAS5508-5142K7EVM PurePath Digital™ customer evaluation amplifier module demonstrates two audio integrated circuits, TAS5508B and TAS5142, from Texas Instruments (TI).

The TAS5508BPAG is a high-performance 32-bit (24-bit input) multichannel PurePath Digital pulse width modulator (PWM) based on Equibit™ technology, with a fully symmetrical AD modulation scheme. It accepts an input sample rate from 32 kHz to 192 kHz. The device also has digital audio processing (DAP) that provides 48-bit signal processing, advanced performance, and a high level of system integration. The device has interfaces for headphone output and power supply volume control (PSVC).

The TAS5142DKD is a compact, high-power, digital amplifier power stage designed to drive a 4- $\Omega$  loudspeaker up to 100 W/10% THD+N. It contains integrated gate drivers, four matched and electrically isolated enhancement-mode N-channel power DMOS transistors, and protection/fault-reporting circuitry.

The DKD package has a PowerPAD™ on the top side for heat transfer through a heatsink. The heatsink in this design is for evaluation purposes only.

This EVM, together with a TI input-USB board, is a complete 7-channel digital audio amplifier system, which includes digital input (S/PDIF), analog inputs, interface to PC, and DAP features, such as digital volume control, input and output mixers, auto mute, equalization, tone controls, loudness, dynamic range compression, and PSVC output. There are configuration options for stereo line level output, stereo headphone output, and power-stage failure protection.

This 6.1 system is designed for home-theater applications, such as A/V receivers, DVD minicomponent systems, home theater in a box (HTIB), DVD receivers, or plasma display panels (PDPs).

### 1.1 TAS5508-5142K7EVM Features

- 7-channel PurePath Digital evaluation module (double-sided plated-through PCB layout)

- Stereo channel line output

- Stereo headphone output

- Self-contained protection system (short circuit and thermal)

- Standard I<sup>2</sup>S and I<sup>2</sup>C/control connector for TI input board

- Double-sided plated-through PCB layout

Figure 1-1. Integrated PurePath Digital™ Amplifier System

### 1.2 PCB Key Map

Physical structure for the TAS5508-5142K7EVM is illustrated in Figure 1-2.

Figure 1-2. Physical Structure for TAS5508-5142K7EVM (Rough Outline)

## System Interfaces

This chapter describes the TAS5508-5142K7EVM board in regards to power supplies and system interfaces.

#### 2.1 Power Supply (PSU) Interface (J901 and J900)

The TAS5508-5142K7EVM module must be powered from external power supplies. High-end audio performance requires a stabilized power supply with low ripple voltage and low output impedance.

Note: The length of power-supply cable must be minimized. Increasing length of PSU cable is equal to increasing the distortion for the amplifier at high output levels and low frequencies.

Maximum output-stage supply voltage depends of the speaker load resistance. Please check the recommended maximum supply voltage in the TAS5142 data sheet.

Table 2-1. Recommended Supply Voltages

| DESCRIPTION               | VOLTAGE<br>LIMITATIONS | CURRENT RECOMMENDATIONS |

|---------------------------|------------------------|-------------------------|

| System power supply       | 15 V to 20 V           | 0.3 A                   |

| Output-stage power supply | 0 V to 32 V            | 6 A <sup>(1)</sup>      |

The rated current correspond to 2-channel full scale (80 W each), which most likely is adequate for a standard 8-channel amplifier design.

The recommended TAS5142 power-up sequence is shown in the figure below. For proper TAS5142 operation, the RESET signal should be kept low during power up. RESET is pulled low during power up for 200 ms by the onboard reset generator (U73).

Figure 2-1. Recommended Power-Up Sequence

Figure 2-2. J901 and J900 Pin Numbers

SLEU071-June 2006 Submit Documentation Feedback

Table 2-2. J901 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION               |

|---------|------------------------|---------------------------|

| 1       | PVDD                   | Output-stage power supply |

| 2       | SYSTEM                 | System power supply       |

| 3       | GND                    | Ground                    |

| 4       | GND                    | Ground                    |

Table 2-3. J900 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION                     |

|---------|------------------------|---------------------------------|

| 1       | PVDD                   | Extra output-stage power supply |

| 2       | PVDD                   | Extra output-stage power supply |

| 3       | GND                    | Extra ground                    |

| 4       | GND                    | Extra ground                    |

### 2.2 PSU Control Interface (J902)

This interface is used for onboard sensing of output supply voltage and for the power supply volume control (PSVC) signal.

Figure 2-3. J902 Pin Numbers

Table 2-4. J902 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION                        |

|---------|------------------------|------------------------------------|

| 1       | _                      | Reserved for future use            |

| 2       | PVDD                   | Sense of output power supply       |

| 3       | GND                    | Ground                             |

| 4       | RESET                  | System reset (bidirectional)       |

| 5       | PSVC                   | Power supply volume control signal |

### 2.3 Loudspeaker Connectors (J101 ... J107)

#### **CAUTION**

Both positive and negative speaker outputs are floating and may not be connected to ground (e.g., through an oscilloscope).

(PCB connector top view)

**Figure 2-4. J101 . . . J107 Pin Numbers**

Table 2-5. J101 . . . J107 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION             |

|---------|------------------------|-------------------------|

| 1       | OUT-1                  | Speaker negative output |

| 2       | OUT-2                  | Speaker positive output |

### 2.4 Headphone Connector (J700)

Figure 2-5. J700 Pin Numbers

Table 2-6. J700 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION            |

|---------|------------------------|------------------------|

| 1       | OUT-R                  | Right headphone output |

| 2       | GND                    | Ground                 |

| 3       | _                      | For future use         |

| 4       | OUT-L                  | Left headphone output  |

### 2.5 Control Interface (J40)

This interface connects the TAS5508-5142K7EVM board to a TI input-USB board.

Table 2-7. J40 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION                                                                                                                      |

|---------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND                    | Ground                                                                                                                           |

| 2       | RESERVED               | _                                                                                                                                |

| 3       | GND                    | Ground                                                                                                                           |

| 4       | RESET                  | System reset (bidirectional). Activate MUTE before RESET for quiet reset.                                                        |

| 5       | BKND-ERR               | Backend error (or soft reset) provides reduced click and pop reset, without resetting I <sup>2</sup> C volume register settings. |

| 6       | MUTE                   | Ramp volume from any setting to noiseless soft mute. Mute can also be activated by I <sup>2</sup> C.                             |

| 7       | PDN                    | Power down. TAS5508B will go to power-down state when activated.                                                                 |

| 8       | RESERVED               | _                                                                                                                                |

| 9       | RESERVED               | _                                                                                                                                |

| 10      | SDA                    | I <sup>2</sup> C data clock                                                                                                      |

Table 2-7. J40 Pin Description (continued)

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION                                                                                                                                               |

|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11      | GND                    | Ground                                                                                                                                                    |

| 12      | SCL                    | I <sup>2</sup> C bit clock                                                                                                                                |

| 13      | RESERVED               | _                                                                                                                                                         |

| 14      | RESERVED               | _                                                                                                                                                         |

| 15      | RESERVED               | _                                                                                                                                                         |

| 16      | RESERVED               | _                                                                                                                                                         |

| 17      | GND                    | Ground                                                                                                                                                    |

| 18      | RESERVED               | _                                                                                                                                                         |

| 19      | RESERVED               | _                                                                                                                                                         |

| 20      | SD                     | Shutdown error reporting for all channels. Activated if TAS5142 has high current or high temperature. See Chapter 3, <i>Protection</i> .                  |

| 21      | SD                     | Shutdown reporting. Activated if one or more TAS5142 has high current or high temperature. Pin 21 connected to Pin 20. See Chapter 3, <i>Protection</i> . |

| 22      | отw                    | Temperature warning. Activated if TAS5142 has reached temperature warning level.                                                                          |

| 23      | ОТW                    | Temperature warning. Activated if one or more TAS5142 has reached temperature warning level. Pin 23 connected to Pin 22.                                  |

| 24      | HP-SEL                 | Headphone select. Headphone active when LOW and inactive when HIGH. To use this pin, <100-Ω resistor must be placed for R50.                              |

| 25      | GND                    | Ground                                                                                                                                                    |

| 26      | GND                    | Ground                                                                                                                                                    |

| 27      | RESERVED               | _                                                                                                                                                         |

| 28      | RESERVED               | _                                                                                                                                                         |

| 29      | RESERVED               | _                                                                                                                                                         |

| 30      | RESERVED               | _                                                                                                                                                         |

| 31      | GND                    | Ground                                                                                                                                                    |

| 32      | GND                    | Ground                                                                                                                                                    |

| 33      | +5V                    | +5Vdc power supply (output)                                                                                                                               |

| 34      | +5V                    | +5Vdc power supply (output)                                                                                                                               |

### 2.6 Digital Audio Interface (J60)

The digital audio interface contains digital audio signal data ( $I^2S$ ), clocks, etc. Please see the *TAS5508B Data Manual* for signal timing and details not explained in this document.

Table 2-8. J60 Pin Description

| PIN NO. | NET-NAME AT SCHEMATICS | DESCRIPTION                                                                                                                                                  |

|---------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND                    | Ground                                                                                                                                                       |

| 2       | MCLK                   | Master clock input. Low jitter system clock for PWM generation and reclocking. Ground connection from source to TAS5508B must be a low impedance connection. |

| 3       | GND                    | Ground                                                                                                                                                       |

| 4       | SDIN1                  | I <sup>2</sup> S data 1, channel 1 and 2                                                                                                                     |

| 5       | SDIN2                  | I <sup>2</sup> S data 2, channel 3 and 4                                                                                                                     |

| 6       | SDIN3                  | I <sup>2</sup> S data 3                                                                                                                                      |

| 7       | SDIN4                  | I <sup>2</sup> S data 4                                                                                                                                      |

| 8       | _                      | Reserved                                                                                                                                                     |

| 9       | _                      | Reserved                                                                                                                                                     |

| 10      | GND                    | Ground                                                                                                                                                       |

| 11      | SCLK                   | I <sup>2</sup> S bit clock                                                                                                                                   |

| 12      | GND                    | Ground                                                                                                                                                       |

| 13      | LRCLK                  | I <sup>2</sup> S left-right clock                                                                                                                            |

| 14      | GND                    | Ground                                                                                                                                                       |

| 15      | _                      | Reserved                                                                                                                                                     |

| 16      | GND                    | Ground                                                                                                                                                       |

### **Protection**

This chapter describes the short-circuit protection and fault-reporting circuitry of the TAS5142 device.

#### 3.1 Short-Circuit Protection and Fault-Reporting Circuitry

The TAS5142 is a self-protecting device that provides fault reporting (including high-temperature protection and short-circuit protection). The TAS5142 is configured in back-end auto-recovery mode and, therefore, resets automatically after all errors (M1, M2, and M3 are set low). This means that the device will restart itself after a error occasion and report through the  $\overline{SD}$  error signal.

### 3.2 Fault Reporting

The  $\overline{\text{OTW}}$  and  $\overline{\text{SD}}$  outputs from the TAS5142 indicate fault conditions. Please refer to the TAS5142 Data Manual for a description of these pins.

| OTW | SD | DEVICE CONDITION                                 |

|-----|----|--------------------------------------------------|

| 0   | 0  | High-temperature error and/or high-current error |

| 0   | 1  | High-temperature warning                         |

| 1   | 0  | Undervoltage lockout or high-current error       |

| 1   | 1  | Normal operation, no errors/warnings             |

Table 3-1. TAS5142 Warning/Error Signal Decoding

The temperature warning signals at the TAS5508-5142K7EVM board are wired-OR to one temperature warning signal ( $\overline{OTW}$  – pin 22 in control interface connector). Shutdown signals are wired-OR into one shutdown signal ( $\overline{SD}$  – pin 20 in control interface connector).

The shutdown signals, together with the temperature warning signal, give chip state information as described in Table 3-1. Device fault-reporting outputs are open-drain outputs.

### Related Documentation From Texas Instruments

The following is a list of documents that have detailed descriptions of the integrated circuits used in the design of the TAS5508-5142K7EVM. This information can be obtained at the URL <a href="http://www.ti.com">http://www.ti.com</a>.

- TAS5508B data sheet (<u>SLES162</u>)

- TAS5142 data sheet (SLES126)

- TPA112 data sheet (<u>SLOS212</u>)

- TPS3801K33 data sheet (SLVS219)

- LM317M data sheet (SLVS297)

- TPS76733 data sheet (SLVS208)

#### Additional documents

- TAS5508-5142K7EVM Application Report (SLEA055)

- PC Configuration Tool for TAS5508B (TAS5508 GUI ver. 4.0 or later)

- General Application Notes

#### 4.1 Trademarks

Equibit, PurePath Digital, and PowerPAD are trademarks of Texas Instruments.

#### **EVALUATION BOARD/KIT IMPORTANT NOTICE**

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. Persons handling the product(s) must have electronics training and observe good engineering practice standards. As such, the goods being provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives or other related directives.

Should this evaluation board/kit not meet the specifications indicated in the User's Guide, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies TI from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the user **is not exclusive.**

The assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read the User's Guide and, specifically, the Warnings and Restrictions notice in the User's Guide prior to handling the product. This notice contains important safety information about temperatures and voltages. For additional information on TI's environmental and/or safety programs, please contact the TI application engineer or visit www.ti.com/esh.

No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine, process, or combination in which such TI products or services might be or are used.

### **FCC Warning**

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **EVM WARNINGS AND RESTRICTIONS**

It is important to operate this EVM within the input voltage range of 0 to 32 V and the output voltage range of 15 V to 20 V.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than 75°C. The EVM is designed to operate properly with certain components above 75°C as long as the input and output ranges are maintained. These components include but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2006, Texas Instruments Incorporated

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products              |                        | Applications       |                           |

|-----------------------|------------------------|--------------------|---------------------------|

| Amplifiers            | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters       | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                   | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface             | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic                 | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt            | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers      | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                  | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| Low Power<br>Wireless | www.ti.com/lpw         | Video & Imaging    | www.ti.com/video          |

|                       |                        | Wireless           | www.ti.com/wireless       |

|                       |                        |                    |                           |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2007, Texas Instruments Incorporated