# Quad 8-Bit Multiplying CMOS D/A Converter with Memory

# DAC8408

#### **FEATURES**

Four DACs in a 28 Pin, 0.6 Inch Wide DIP or 28-Pin JEDEC

Plastic Chip Carrier

±1/4 LSB Endpoint Linearity

Guaranteed Monotonic

DACs Matched to Within 1%

Microprocessor Compatible

Read/Write Capability (with Memory)

TTL/CMOS Compatible

Four-Quadrant Multiplication

Single-Supply Operation (+5 V)

Low Power Consumption

Latch-Up Resistant

Available In Die Form

#### **APPLICATIONS**

Voltage Set Points in Automatic Test Equipment Systems Requiring Data Access for Self-Diagnostics Industrial Automation Multichannel Microprocessor-Controlled Systems Digitally Controlled Op Amp Offset Adjustment Process Control Digital Attenuators

# GENERAL DESCRIPTION

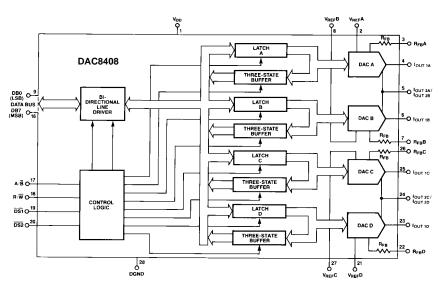

The DAC 8408 is a monolithic quad 8-bit multiplying digital-to-analog CMOS converter. Each DAC has its own reference input, feedback resistor, and onboard data latches that feature read/write capability. The readback function serves as memory for those systems requiring self-diagnostics.

A common 8-bit TTL/CMOS compatible input port is used to load data into any of the four DAC data-latches. Control lines DS1, DS2, and A/B determine which DAC will accept data. Data loading is similar to that of a RAMs write cycle. Data can be read back onto the same data bus with control line R/W. The DAC 8408 is bus compatible with most 8-bit microprocessors, including the 6800, 8080, 8085, and Z80. The DAC 8408 operates on a single +5 volt supply and dissipates less than 20 mW. The DAC 8408 is manufactured using PMI's highly stable, thin-film resistors on an advanced oxide-isolated, silicon-gate, CMOS process. PMI's improved latch-up resistant design eliminates the need for external protective Schottky diodes.

# ORDERING INFORMATION<sup>1</sup>

| Model                   | INL      | DNL      | Temperature<br>Range | Package<br>Description |

|-------------------------|----------|----------|----------------------|------------------------|

| DAC8408GP               | ±1/4 LSB | ±1/2 LSB | 0°C to +70°C         | 28-Pin Plastic DIP     |

| DAC8408ET               | ±1/4 LSB | ±1/2 LSB | -40°C to +85°C       | 28-Pin Cerdip          |

| DAC8408AT <sup>2</sup>  | ±1/4 LSB | ±1/2 LSB | -55°C to +125°C      | 28-Pin Cerdip          |

| DAC8408FT               | ±1/2 LSB | ±1 LSB   | -40°C to +85°C       | 28-Pin Cerdip          |

| DAC8408BT <sup>2</sup>  | ±1/2 LSB | ±1 LSB   | -55°C to +125°C      | 28-Pin Cerdip          |

| DAC8408FPC <sup>3</sup> | ±1/2 LSB | ±1 LSB   | -40°C to +85°C       | 28-Contact PLCC        |

| DAC8408FS               | ±1/2 LSB | ±1 LSB   | -40°C to +85°C       | 28-Pin SOL             |

| DAC8408FP               | ±1/2 LSB | ±1 LSB   | -40°C to +85°C       | 28-Pin Plastic DIP     |

#### NOTES

- <sup>1</sup>Burn-in is available on commercial and industrial temperature range parts in cerdip, plastic DIP, and TO-can packages. For outline information see Package Information section.

- <sup>2</sup>For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- $^3\mbox{For}$  availability and burn-in information on SO and PLCC packages, contact your local sales office.

# FUNCTIONAL BLOCK DIAGRAM

# REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

| <b>T</b>                                   |                     |                                                                    |                                        | DAC8408     |            |           |

|--------------------------------------------|---------------------|--------------------------------------------------------------------|----------------------------------------|-------------|------------|-----------|

| Parameter                                  | Symbol              | Conditions                                                         | Min                                    | Тур         | Max        | Units     |

| STATIC ACCURACY                            |                     |                                                                    |                                        |             |            |           |

| Resolution                                 | N                   |                                                                    | 8                                      |             |            | Bits      |

| Nonlinearity <sup>1, 2</sup>               | INL                 | DAC8408A/E/G                                                       |                                        |             | $\pm 1/4$  | LSB       |

|                                            |                     | DAC8408B/F/H                                                       |                                        |             | $\pm 1/2$  | LSB       |

| Differential                               | DNL                 | DAC 8408 A/E/G                                                     |                                        |             | $\pm 1/2$  | LSB       |

| Nonlinearity                               | DIVE                | DAC8408B/F/H                                                       |                                        |             | ±1/2       | LSB       |

| Gain Error                                 | $G_{FSE}$           | (Using Internal R <sub>FB</sub> )                                  |                                        |             | ±1         | LSB       |

| Gain Tempco <sup>3, 6</sup>                | TC <sub>GFS</sub>   | (Osing Internal K <sub>FB</sub> )                                  |                                        | ±2          | ±40        | ppm/°C    |

| Power Supply Rejection                     | 1 C <sub>GFS</sub>  |                                                                    |                                        | <u> </u>    | ±40        | ppiii/ C  |

| ( $\Delta V_{DD} = \pm 10\%$ )             | PSR                 |                                                                    |                                        |             | 0.001      | %FSR/%    |

| $I_{OUT 1A, B, C, D}$                      | rsk                 |                                                                    |                                        |             | 0.001      | 701°3K/70 |

| Leakage Current <sup>13</sup>              | $I_{LKG}$           | $T_A = +25$ °C                                                     |                                        |             | ±30        | nA        |

| Deakage Carrent                            | 1LKG                | $T_A = Full$ Temperature Range                                     |                                        |             | ±100       | nA        |

| REFERENCE INPUT                            |                     | . 1 5-                                                             | +                                      |             | -          |           |

| Input Voltage Range                        |                     |                                                                    |                                        |             | ±20        | V         |

|                                            |                     | D                                                                  |                                        |             |            |           |

| Input Resistance Match <sup>4</sup>        | D                   | R <sub>A, B, C, D</sub>                                            | _                                      | 10          | ±1         | %<br>IvO  |

| Input Resistance                           | R <sub>IN</sub>     | 1                                                                  | 6                                      | 10          | 14         | kΩ        |

| DIGITAL INPUTS                             |                     |                                                                    |                                        |             | 0.0        | 177       |

| Digital Input Low                          | $V_{IL}$            |                                                                    |                                        |             | 0.8        | V         |

| Digital Input High                         | $V_{IH}$            |                                                                    | 2.4                                    | 10.01       | . 1 0      | V         |

| Input Current <sup>5</sup>                 |                     | $T_A = +25^{\circ}C$                                               |                                        | $\pm 0.01$  | ±1.0       | μΑ        |

|                                            | $I_{IN}$            | $T_A$ = Full Temperature Range                                     |                                        |             | $\pm 10.0$ | μA        |

| Input Capacitance <sup>6</sup>             | $C_{IN}$            |                                                                    |                                        |             | 8          | pF        |

| DATA BUS OUTPUTS                           |                     |                                                                    |                                        |             |            |           |

| Digital Output Low                         | V <sub>OL</sub>     | 16 mA Sink                                                         |                                        |             | 0.4        | V         |

| Digital Output High                        | $V_{OH}$            | 400 μA Source                                                      | 4                                      |             |            | V         |

| Output Leakage Current                     | $I_{LKG}$           | $T_A = +25$ °C                                                     |                                        | $\pm 0.005$ | $\pm 1.0$  | μA        |

|                                            |                     | $T_A$ = Full Temperature Range                                     |                                        | $\pm 0.075$ | $\pm 10.0$ | μA        |

| DAC OUTPUTS <sup>6</sup>                   |                     |                                                                    |                                        |             |            |           |

| Propagation Delay <sup>7</sup>             | $t_{PD}$            |                                                                    |                                        | 150         | 180        | ns        |

| Settling Time <sup>11,12</sup>             | $t_{S}$             |                                                                    |                                        | 190         | 250        | ns        |

| Output Capacitance                         | C <sub>OUT</sub>    | DAC Latches All "0s"                                               |                                        |             | 30         | pF        |

|                                            |                     | DAC Latches All "1s"                                               |                                        |             | 50         | pF        |

| AC Feedthrough                             | FT                  | $(20 \text{ V}_{p-p} @ \text{F} = 100 \text{ kHz})$                | 54                                     |             |            | dB        |

| SWITCHING CHARACTERISTICS <sup>6, 10</sup> |                     |                                                                    | 1                                      |             |            |           |

| Write to Data Strobe Time                  | t <sub>DS1</sub> or | $T_A = +25$ °C                                                     | 90                                     |             |            | ns        |

|                                            | t <sub>DS2</sub>    | $T_A = Full Temperature Range$                                     | 145                                    |             |            | ns        |

| Data Valid to Strobe Set-Up Time           | t <sub>DSU</sub>    | $T_A = +25$ °C                                                     | 150                                    |             |            | ns        |

|                                            | 230                 | $T_A = Full Temperature Range$                                     | 175                                    |             |            | ns        |

| Data Valid to Strobe Hold Time             | $t_{\mathrm{DH}}$   | A                                                                  | 10                                     |             |            | ns        |

| DAC Select to Strobe Set-Up Time           | t <sub>AS</sub>     |                                                                    | 0                                      |             |            | ns        |

| DAC Select to Strobe Hold Time             | t <sub>AH</sub>     |                                                                    | 0                                      |             |            | ns        |

| Write Select to Strobe Set-Up Time         | t <sub>WSU</sub>    |                                                                    | $\begin{vmatrix} 0 \\ 0 \end{vmatrix}$ |             |            | ns        |

| Write Select to Strobe Hold Time           | t <sub>WH</sub>     |                                                                    | $\begin{vmatrix} 0 \\ 0 \end{vmatrix}$ |             |            | ns        |

| Read to Data Strobe Width                  | t <sub>RDS</sub>    | $T_A = +25$ °C                                                     | 220                                    |             |            | ns        |

|                                            | פחא                 | $T_A = 123$ C<br>$T_A = Full Temperature Range$                    | 350                                    |             |            | ns        |

| Data Strobe to Output Valid Time           | t <sub>CO</sub>     | $T_A = 1$ and $T$ emperature Range $T_A = +25$ °C                  | 320                                    |             |            | ns        |

| _ sta street to output raine i inic        | "                   | $T_A = 123$ C<br>$T_A = Full Temperature Range$                    | 430                                    |             |            | ns        |

| Output Data to Deselect Time               | t <sub>OTD</sub>    | $T_A = 1 \text{ diff reimperature Range}$<br>$T_A = +25 \text{°C}$ | 200                                    |             |            | ns        |

| Carpar Data to Describer 1 mile            | 010                 | $T_A = 123$ C<br>$T_A = Full Temperature Range$                    | 270                                    |             |            | ns        |

| Read Select to Strobe Set-Up Time          | t <sub>RSU</sub>    | - A 1 am 1 amperature runge                                        | 0                                      |             |            | ns        |

|                                            | -1000               |                                                                    | 0                                      |             |            | 1         |

Specifications subject to change without notice.

ELECTRICAL CHARACTERISTICS @  $V_{DD}$  = +5 V;  $V_{REF}$  = ±10 V;  $V_{OUT}$ A, B, C, D = 0 V;  $T_A$  = -55°C to +125°C apply for DAC8408AT/BT,  $T_A$  = -40°C to +85°C apply for DAC8408ET/FT/FP/FPC/FS;  $T_A$  = 0°C to +70°C apply for DAC8408GP, unless otherwise noted. Specifications apply for DAC A, B, C, & D. *Continued*

|                             |                   |                                | ]   | DAC840 | 8   |       |

|-----------------------------|-------------------|--------------------------------|-----|--------|-----|-------|

| Parameter                   | Sym bol           | Conditions                     | Min | Typ    | Max | Units |

| POWER SUPPLY                |                   |                                |     |        |     |       |

| Voltage Range               | $V_{\mathrm{DD}}$ |                                | 4.5 |        | 5.5 | V     |

| Supply Current <sup>8</sup> | $I_{DD}$          |                                |     |        | 50  | μΑ    |

| Supply Current <sup>9</sup> | $I_{DD}$          | $T_A = +25^{\circ}C$           |     |        | 1.0 | mA    |

|                             |                   | $T_A$ = Full Temperature Range |     |        | 1.5 | m A   |

#### NOTES

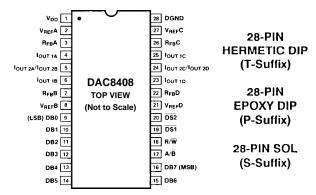

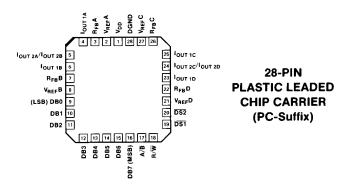

#### PIN CONNECTIONS

# ABSOLUTE MAXIMUM RATINGS

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Industrial Grade (ET, FT, FP, FPC, FS) . -40°C to +85°C

Military Grade (AT, BT) .....55°C to +125°C

Junction Temperature .....+150°C

Storage Temperature .....-65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . +300°C

| Package Type            | $\theta_{JA}*$ | $\theta_{ m JC}$ | Units |

|-------------------------|----------------|------------------|-------|

| 28-Pin Hermetic DIP (T) | 55             | 10               | °C/W  |

| 28-Pin Plastic DIP (P)  | 53             | 27               | °C/W  |

| 28-Pin SOL (S)          | 68             | 23               | °C/W  |

| 28-Contact PLCC (PC)    | 66             | 29               | °C/W  |

<sup>\*</sup> $\theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for cerdip and P-DIP packages;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SOL and PLCC packages.

# **CAUTION**

- 1. Do not apply voltages higher than  $V_{DD}$  +0.3 V or less than -0.3 V potential on any terminal except  $V_{REF}$  and  $R_{FB}$ .

- The digital control inputs are diode-protected; however, permanent damage may occur on unconnected inputs from high energy electrostatic fields. Keep in conductive foam at all times until ready to use.

- 3. Use proper antistatic handling procedures.

- Absolute Maximum Ratings apply to both packaged devices and DICE. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device.

REV. A -3-

<sup>&</sup>lt;sup>1</sup>This is an end-point linearity specification.

<sup>&</sup>lt;sup>2</sup>Guaranteed to be monotonic over the full operating temperature range.

$<sup>^{3}</sup>$ ppm/ $^{\circ}$ C of FSR (FSR = Full Scale Range =  $V_{REF}$ -1 LSB.)

<sup>&</sup>lt;sup>4</sup>Input Resistance Temperature Coefficient = +300ppm/°C.

<sup>&</sup>lt;sup>5</sup>Logic Inputs are MOS gates. Typical input current at +25°C Is less than 10 nA.

<sup>&</sup>lt;sup>6</sup>Guaranteed by design.

<sup>&</sup>lt;sup>7</sup>From Digital Input to 90% of final analog output current.

<sup>&</sup>lt;sup>8</sup>All Digital Inputs "0" or V<sub>DD</sub>.

<sup>&</sup>lt;sup>9</sup>All Digital Inputs V<sub>IH</sub> or V<sub>IL</sub>.

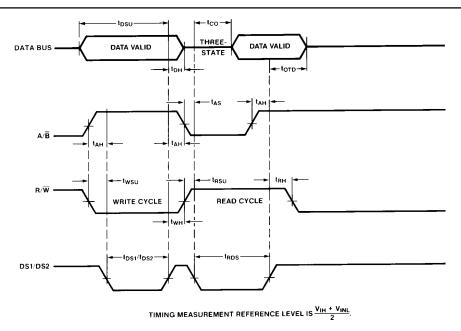

<sup>&</sup>lt;sup>10</sup>See Timing Diagram.

$<sup>^{11}</sup>$ Digital Inputs = 0 V to  $V_{\rm DD}$  or  $V_{\rm DD}$  to 0 V.

$<sup>^{12}</sup>Extrapolated$ :  $t_S$  (1/2 LSB) =  $t_{PD}$  + 6.2 $\tau$  where  $\tau$  = the measured first time constant of the final RC decay.

$<sup>^{13}</sup>$ All Digital Inputs = 0 V;  $V_{REF} = +10 \text{ V}$ .

Specifications subject to change without notice.

Burn-in Circuit

# CAUTION -

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the DAC 8408 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

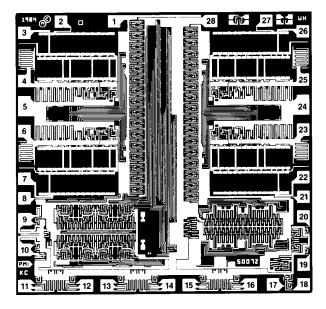

# **DICE CHARACTERISTICS**

DIE SIZE  $0.130 \times 0.124$  inch, 16,120 sq. mils  $(3.30 \times 3.15 \text{ mm}, 10.4 \text{ sq. mm})$

| $1. V_{DD}$                  | 15. DB6                                      |

|------------------------------|----------------------------------------------|

| $V_{REF}A$                   | 16. DB7 (MSB)                                |

| $3. R_{FB}A$                 | 17. A/ $\overline{B}$                        |

| 4. I <sub>OUT 1A</sub>       | 18. R/ <del>W</del>                          |

| 5. $I_{OUT\ 2A}/I_{OUT\ 2B}$ | 19. <del>DS1</del>                           |

| 6. I <sub>OUT 1B</sub>       | $20. \overline{DS2}$                         |

| $7. R_{FB}B$                 | $21. V_{REF}D$                               |

| $8. V_{REF}B$                | 22. $R_{FB}D$                                |

| 9. DB0 (LSB)                 | 23. I <sub>OUT 1D</sub>                      |

| 10. DB1                      | 24. I <sub>OUT 2C</sub> /I <sub>OUT 2D</sub> |

| 11. DB2                      | 25. I <sub>OUT 1C</sub>                      |

| 12. DB3                      | $26. R_{FB}C$                                |

| 13. DB4                      | 27. $V_{REF}C$                               |

| 14. DB5                      | 28. DGND                                     |

|                              |                                              |

WAFER TESTLIMITS at  $V_{DD} = +5$  V;  $V_{REF} = \pm 10$  V;  $V_{CUT}A$ , B, C, D = 0 V;  $T_A = +25$ °C, unless otherwise noted. Specifications apply for DAC A, B, C, & D.

| Parameter                                             | Symbol                                                             | Conditions                     | DAC8408G<br>Limits | Units      |

|-------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|--------------------|------------|

| STATIC ACCURACY                                       |                                                                    |                                |                    |            |

| Resolution                                            | N                                                                  |                                | 8                  | Bits min   |

| Nonlinearity <sup>1</sup>                             | INL                                                                |                                | ±1/2               | LSB max    |

| Differential Nonlinearity                             | DNL                                                                |                                | ±1                 | LSB max    |

| Gain Error                                            | $G_{FSE}$                                                          | Using Internal R <sub>FB</sub> | ±1                 | LSB max    |

| Power Supply Rejection $(\Delta V_{DD} = \pm 10\%)^2$ | PSR                                                                | Using Internal R <sub>FB</sub> | 0.001              | %FSR/% max |

| I <sub>OUT 1A, B, C, D</sub> Leakage Current          | $\begin{vmatrix} I_{LKG} \\ V_{REF} = +10 \text{ V} \end{vmatrix}$ | All Digital Inputs = 0 V       | ±30                | nA max     |

| REFERENCE INPUT                                       |                                                                    |                                |                    |            |

| Reference Input<br>Resistance <sup>3</sup>            | R <sub>IN</sub>                                                    |                                | 6/14               | kΩ min/max |

| Input Resistance Match                                | R <sub>IN</sub>                                                    |                                | ±1                 | % max      |

| DIGITAL INPUTS                                        |                                                                    |                                |                    |            |

| Digital Input Low                                     | $V_{ m IL}$                                                        |                                | 0.8                | V max      |

| Digital Input High                                    | V <sub>IH</sub>                                                    |                                | 2.4                | V min      |

| Input Current <sup>4</sup>                            | I <sub>IN</sub>                                                    |                                | ±1.0               | μA max     |

| DATA BUS OUTPUTS                                      |                                                                    |                                |                    |            |

| Digital Output Low                                    | $V_{OL}$                                                           | 1.6 mA Sink                    | 0.4                | V max      |

| Digital Output High                                   | V <sub>OH</sub>                                                    | 400 μA Source                  | 4                  | V min      |

| Output Leakage Current                                | I <sub>LKG</sub>                                                   | •                              | ±1.0               | μA max     |

| POWER SUPPLY                                          |                                                                    |                                |                    |            |

| Supply Current <sup>5</sup>                           | $I_{DD}$                                                           |                                | 50                 | μA max     |

| Supply Current <sup>6</sup>                           | $I_{DD}$                                                           |                                | 1.0                | mA max     |

# NOTES

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

REV. A -5-

<sup>&</sup>lt;sup>1</sup>This is an endpoint linearity specification.

<sup>&</sup>lt;sup>2</sup>FSR is Full Scale Range = V<sub>REF</sub> -1 LSB.

<sup>3</sup>Input Resistance Temperature Coefficient approximately equals +300 ppm/°C.

<sup>4</sup>Logic inputs are MOS gates. Typical input current at +25 °C is less than 10 nA.

$<sup>^5</sup>$  All Digital Inputs are either "0" or  $V_{\rm DD}.$   $^6$  All Digital Inputs are either  $V_{\rm IH}$  or  $V_{\rm IL}.$

# TYPICAL PERFORMANCE CHARACTERISTICS

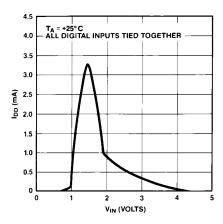

Supply Current vs. Logic Level

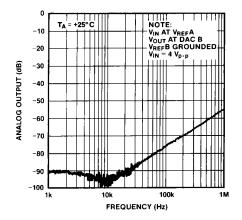

Analog Crosstalk vs. Frequency

-6- REV. A

Timing Diagram

# PARAMETER DEFINITIONS

### RESOLUTION

Resolution is the number of states (2<sup>n</sup>) that the full-scale range (FSR) of a DAC is divided (or resolved) into.

# NONLINEARITY

Nonlinearity (Relative Accuracy) is a measure of the maximum deviation from a straight line passing through the end-points of the DAC transfer function. It is measured after adjusting for ideal zero and full-scale and is expressed in LSB, %, or ppm of full-scale range.

# DIFFERENTIAL NONLINEARITY

Differential Nonlinearity is the worst case deviation of any adjacent analog outputs from the ideal 1 LSB step size. A specified differential nonlinearity of  $\pm 1$  LSB maximum over the operating temperature range ensures monotonicity.

# **GAIN ERROR**

Gain Error (full-scale error) is a measure of the output error between the ideal and actual DAC output. The ideal full-scale output is  $V_{REF}$ -1 LSB.

# **OUTPUT CAPACITANCE**

Output Capacitance is that capacitance between  $I_{OUT\ 1A},\,I_{OUT\ 1B},\,I_{OUT\ 1C},$  or  $I_{OUT\ 1D}$  and AGND.

# AC FEEDTHROUGH ERROR

This is the error caused by capacitance coupling from  $V_{\text{REF}}$  to the DAC output with all switches off.

# SETTLING TIME

Settling Time is the time required for the output function of the DAC to settle to within 1/2 LSB for a given digital input signal.

# PROPAGATION DELAY

This is a measure of the internal delays of the DAC. It is defined as the time from a digital input change to the analog output current reaching 90% of its final value.

# CHANNEL-TO-CHANNEL ISOLATION

This is the portion of input signal that appears at the output of a DAC from another DAC's reference input. It is expressed as a ratio in dB.

# DIGITAL CROSSTALK

Digital Crosstalk is the glitch energy transferred to the output of one DAC due to a change in digital input code from other DACs. It is specified in nVs.

REV. A -7-

# CIRCUIT INFORMATION

The DAC 8408 combines four identical 8-bit CMOS DACs onto a single monolithic chip. Each DAC has its own reference input, feedback resistor, and on-board data latches. It also features a read/write function that serves as an accessible memory location for digital-input data words. The DAC's three-state readback drivers place the data word back onto the data bus.

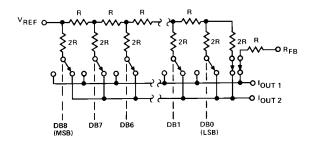

# D/A CONVERTER SECTION

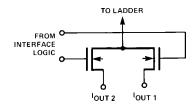

Each DAC contains a highly stable, silicon-chromium, thin-film, R-2R resistor ladder network and eight pairs of current steering switches. These switches are in series with each ladder resistor and are single-pole, double-throw NMOS transistors; the gates of these transistors are controlled by CMOS inverters. Figure 1 shows a simplified circuit of the R-2R resistor ladder section, and Figure 2 shows an approximate equivalent switch circuit. The current through each resistor leg is switched between  $I_{\rm OUT\ 1}$  and  $I_{\rm OUT\ 2}$ . This maintains a constant current in each leg, regardless of the digital input logic states.

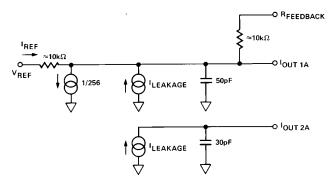

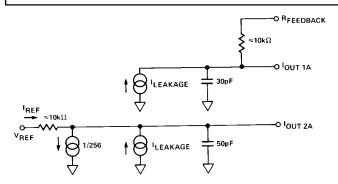

Each transistor switch has a finite "ON" resistance that can introduce errors to the DAC's specified performance. These resistances must be accounted for by making the voltage drop across each transistor equal to each other. This is done by binarily-scaling the transistor's "ON" resistance from the most significant bit (MSB) to the least significant bit (LSB). With 10 volts applied at the reference input, the current through the MSB switch is 0.5 mA, the next bit is 0.25 mA, etc.; this maintains a constant 10 mV drop across each switch and the converter's accuracy is maintained. It also results in a constant resistance appearing at the DAC's reference input terminal; this allows the DAC to be driven by a voltage or current source, ac or dc of positive or negative polarity.

Shown in Figure 3 is an equivalent output circuit for DAC A. The circuit is shown with all digital inputs high. The leakage current source is the combination of surface and junction leakages to the substrate. The 1/256 current source represents the constant 1-bit current drain through the ladder terminating resistor. The situation is reversed with all digital inputs low, as shown in Figure 4. The output capacitance is code dependent, and therefore, is modulated between the low and high values.

Figure 1. Simplified D/A Circuit of DAC8408

Figure 2. N-Channel Current Steering Switch

Figure 3. Equivalent DAC Circuit (All Digital Inputs HIGH)

Figure 4. Equivalent DAC Circuit (All Digital Inputs LOW)

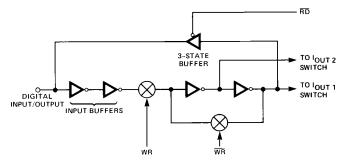

#### DIGITAL SECTION

Figure 5 shows the digital input/output structure for one bit. The digital WR,  $\overline{WR}$ , and  $\overline{RD}$  controls shown in the figure are internally generated from the external A/B, R/W, DS1, and DS2 signals. The combination of these signals decide which DAC is selected. The digital inputs are CMOS inverters, designed such that TTL input levels (2.4 V and 0.8 V) are converted into CMOS logic levels. When the digital input is in the region of 1.2 V to 1.8 V, the input stages operate in their linear region and draw current from the +5 V supply (see Typical Supply Current vs. Logic Level curve on page 6). It is recommended that the digital input voltages be as close to V<sub>DD</sub> and DGND as is practical in order to minimize supply currents. This allows maximum savings in power dissipation inherent with CMOS devices. The three-state readback digital output drivers (in the active mode) provide TTL-compatible digital outputs with a fan-out of one TTL load. The three state digital readback leakage-current is typically 5 nA.

Figure 5. Digital Input/Output Structure

# INTERFACE LOGIC SECTION

#### **DAC Operating Modes**

- All DACs in HOLD MODE.

- DAC A, B, C, or D individually selected (WRITE MODE).

- DAC A, B, C, or D individually selected (READ MODE).

- DACs A and C simultaneously selected (WRITE MODE).

- DACs B and D simultaneously selected (WRITE MODE).

**DAC Selection:** Control inputs,  $\overline{DS1}$ ,  $\overline{DS2}$ , and  $A/\overline{B}$  select which DAC can accept data from the input port (see Mode Selection Table).

**Mode Selection:** Control inputs  $\overline{DS}$  and  $R/\overline{W}$  control the operating mode of the selected DAC.

**Write Mode:** When the control inputs  $\overline{DS}$  and  $R/\overline{W}$  are both low, the selected DAC is in the write mode. The input data latches of the selected DAC are transparent, and its analog output responds to activity on the data inputs DB0–DB7.

**Hold Mode:** The selected DAC latch retains the data that was present on the bus line just prior to  $\overline{DS}$  or  $R/\overline{W}$  going to a high state. All analog outputs remain at the values corresponding to the data in their respective latches.

**Read Mode:** When  $\overline{DS}$  is low and  $R/\overline{W}$  is high, the selected DAC is in the read mode, and the data held in the appropriate latch is put back onto the data bus.

# MODE SELECTION TABLE

| DS1 | Contro<br>DS2 | ol Logi<br>A/B | c<br>R/W | Mode  | DAC     |

|-----|---------------|----------------|----------|-------|---------|

| L   | Н             | Н              | L        | WRITE | A       |

| L   | Н             | L              | L        | WRITE | В       |

| H   | L             | Н              | L        | WRITE | C       |

| Н   | L             | L              | L        | WRITE | D       |

| L   | Н             | Н              | Н        | READ  | A       |

| L   | Н             | L              | Н        | READ  | В       |

| H   | L             | Н              | Н        | READ  | C       |

| Н   | L             | L              | H        | READ  | D       |

| L   | L             | Н              | L        | WRITE | A&C     |

| L   | L             | L              | L        | WRITE | B&D     |

| Н   | Н             | X              | X        | HOLD  | A/B/C/D |

| L   | L             | Н              | H        | HOLD  | A/B/C/D |

| L   | L             | L              | H        | HOLD  | A/B/C/D |

L = Low State, H = High State, X = Irrelevant

REV. A \_9\_

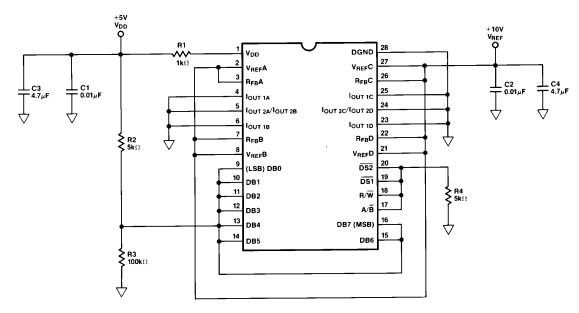

# BASIC APPLICATIONS

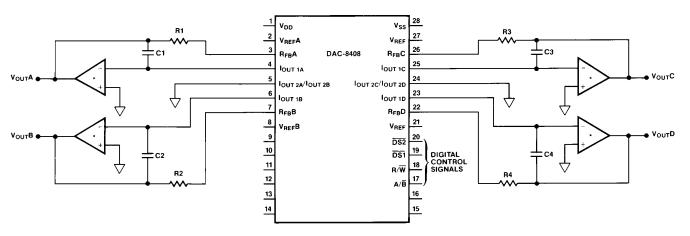

Some basic circuit configurations are shown in Figures 6 and 7. Figure 6 shows the DAC 8408 connected in a unipolar configuration (2-Quadrant Multiplication), and Table I shows the Code Table. Resistors R1, R2, R3, and R4 are used to trim full scale output. Full-scale output voltage =  $V_{REF}$  –1 LSB =  $V_{REF}$  (1–2<sup>-8</sup>) or  $V_{REF}\times(255/256)$  with all digital inputs high. Low temperature coefficient (approximately 50 ppm/°C) resistors or trimmers should be selected if used. Full scale can also be adjusted using  $V_{REF}$  voltage. This will eliminate resistors R1, R2, R3, and R4. In many applications, R1 through R4 are not required, and the maximum gain error will then be that of the DAC.

Each DAC exhibits a variable output resistance that is codedependent. This produces a code-dependent, differential nonlinearity term at the amplifier's output which can have a maximum value of  $0.67 \times$  the amplifier's offset voltage. This differential nonlinearity term adds to the R-2R resistor ladder differential-nonlinearity; the output may no longer be monotonic. To maintain monotonicity and minimize gain and linearity errors, it is recommended that the op amp offset voltage be adjusted to less than 10% of 1 LSB (1 LSB =  $2^{-8} \times V_{REF}$  or  $1/256 \times V_{REF}$ ), or less than 3.9 mV over the operating temperature range. Zeroscale output voltage (with all digital inputs low) may be adjusted using the op amp offset adjustment. Capacitors C1, C2, C3, and C4 provide phase compensation and help prevent overshoot and ringing when using high speed op amps.

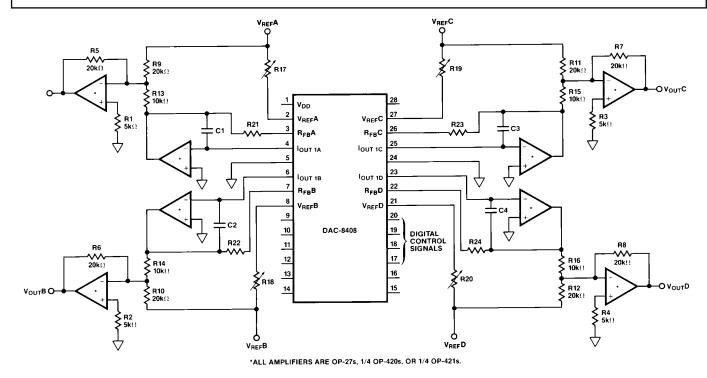

Figure 7 shows the recommended circuit configuration for the bipolar operation (4-quadrant multiplication), and Table II shows the Code Table. Trimmer resistors R17, R18, R19, and R20

are used only if gain error adjustments are required and range between 50  $\Omega$  and 1000  $\Omega$ . Resistors R21, R22, R23, and R24 will range betwen 50  $\Omega$  and 500  $\Omega$ . If these resistors are used, it is essential that resistor pairs R9–R13, R10–R14, R11–R15, R12–R16 are matched both in value and tempco. They should be within 0.01%; wire wound or metal foil types are preferred for best temperature coefficient matching. The circuits of Figure 6 and 7 can either be used as a fixed reference D/A converter, or as an attenuator with an ac input voltage.

Table I. Unipolar Binary Code Table (Refer to Figure 6)

| DAC Data Input<br>MSB LSB | Analog Output                                              |

|---------------------------|------------------------------------------------------------|

| 1 1 1 1 1 1 1             | $-V_{REF}\left(\frac{255}{256}\right)$                     |

| 1 0 0 0 0 0 0 1           | $-V_{REF} \left(\frac{129}{256}\right)$                    |

| 1 0 0 0 0 0 0 0           | $-V_{REF}\left(\frac{128}{256}\right) = \frac{-V_{IN}}{2}$ |

| 0 1 1 1 1 1 1 1           | $-V_{REF}\left(\frac{127}{256}\right)$                     |

| 0 0 0 0 0 0 0 1           | $-V_{REF}\left(\frac{1}{256}\right)$                       |

| 0 0 0 0 0 0 0 0           | $-V_{REF}\left(\frac{0}{256}\right) = 0$                   |

NOTE

1 LSB =

$$(2^{-8})$$

(V<sub>REF</sub>) =  $\frac{1}{256}$  (V<sub>REF</sub>)

\*ALL AMPLIFIERS ARE OP-27s, 1/4 OP-420s, OR 1/4 OP-421s

Figure 6. Quad DAC Unipolar Operation (2-Quadrant Multiplication)

–10– REV. A

Figure 7. Quad DAC Bipolar Operation (4-Quadrant Multiplication)

Table II. Bipolar (Offset Binary) Code Table (Refer to Figure 7)

| DAC Da<br>MSB | nta Input<br>LSB | Analog Output<br>(DAC A OR DAC B)                                           |

|---------------|------------------|-----------------------------------------------------------------------------|

| 1 1 1 1       | 1 1 1 1          | $+V_{REF}\left(\frac{127}{128}\right)$ $+V_{REF}\left(\frac{1}{128}\right)$ |

| 1 0 0 0       | 0 0 0 1          | $+V_{REF}\left(\frac{1}{128}\right)$                                        |

| 1 0 0 0       | 0 0 0 0          | 0                                                                           |

| 0 1 1 1       | 1 1 1 1          | $-V_{REF}\left(\frac{1}{128}\right)$ $-V_{REF}\left(\frac{127}{127}\right)$ |

| 0 0 0 0       | 0 0 0 1          | $-V_{REF} \left(\frac{127}{128}\right)$ (128)                               |

| 0 0 0 0       | 0 0 0 0          | $-V_{REF}\left(\frac{128}{128}\right)$                                      |

NOTE

1 LSB =

$$(2^{-7})$$

$(V_{REF}) = \frac{1}{128} (V_{REF})$

# APPLICATION HINTS

General Ground Management: AC or transient voltages between AGND and DGND can appear as noise at the DAC8408's analog output. Note that in Figures 5 and 6, I<sub>OUT2A</sub>/I<sub>OUT2B</sub> and I<sub>OUT 2C</sub>/I<sub>OUT 2D</sub> are connected to AGND. Therefore, it is recommended that AGND and DGND be tied together at the DAC8408 socket. In systems where AGND and DGND are tied together on the backplane, two diodes (1N914 or equivalent) should be connected in inverse parallel between AGND and DGND.

**Write Enable Timing:** During the period when both  $\overline{DS}$  and  $R/\overline{W}$  are held low, the DAC latches are transparent and the analog output responds directly to the digital data input. To prevent unwanted variations of the analog output, the  $R/\overline{W}$  should not go low until the data bus is fully settled (DATA VALID).

REV. A -11-

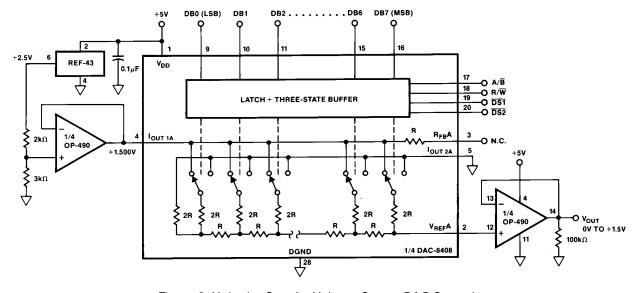

# SINGLE SUPPLY, VOLTAGE OUTPUT OPERATION

The DAC 8408 can be connected with a single +5 V supply to produce DAC output voltages from 0 V to +1.5 V. In Figure 8, the DAC 8408 R-2R ladder is inverted from its normal connection. A +1.500 V reference is connected to the current output pin 4 ( $I_{\rm OUT\ IA}$ ), and the normal  $V_{\rm REF}$  input pin becomes the DAC output. Instead of a normal current output, the R-2R ladder outputs a voltage. The OP-490, consisting of four precision low power op amps that can operate its inputs and outputs to zero volts, buffers the DAC to produce a low impedance output voltage from 0 V to +1.5 V full-scale. Table III shows the code table.

With the supply and reference voltages as shown, better than 1/2 LSB differential and integral nonlinearity can be expected. To maintain this performance level, the +5 V supply must not drop below 4.75 V. Similarly, the reference voltage must be no higher than 1.5 V. This is because the CMOS switches require a minimum level of bias in order to maintain the linearity performance.

Table III. Single Supply Binary Code Table (Refer to Figure 8)

| DAC Data Input<br>MSB LSB | Analog Output                                               |

|---------------------------|-------------------------------------------------------------|

| 1 1 1 1 1 1 1 1           | $V_{REF} \left( \frac{255}{256} \right), +1.4941 \text{ V}$ |

| 1 0 0 0 0 0 0 1           | $V_{REF} \left(\frac{129}{256}\right), +0.7559 \text{ V}$   |

| 1 0 0 0 0 0 0 0           | $V_{REF} \left(\frac{128}{256}\right), +0.7500 \text{ V}$   |

| 0 1 1 1 1 1 1 1           | $V_{REF} \left(\frac{127}{256}\right), +0.7441 \text{ V}$   |

| 0 0 0 0 0 0 0 1           | $V_{REF} \left( \frac{1}{256} \right), +0.0059 \text{ V}$   |

| 0 0 0 0 0 0 0 0           | $V_{REF} \left( \frac{0}{256} \right), 0.0000 \text{ V}$    |

Figure 8. Unipolar Supply, Voltage Output DAC Operation

-12- REV. A

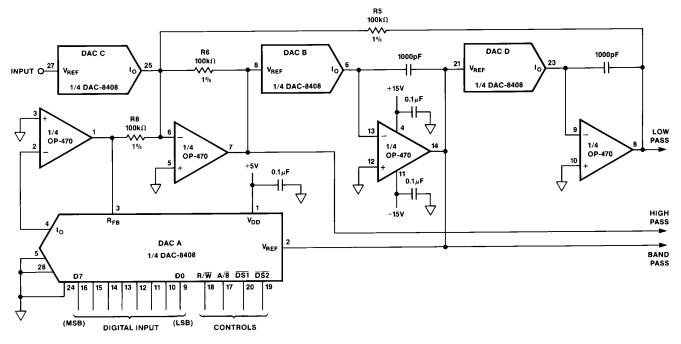

Figure 9. A Digitally Programmable Universal Active Filter

# A DIGITALLY PROGRAMMABLE ACTIVE FILTER

A powerful D/A converter application is a programmable active filter design as shown in Figure 9. The design is based on the state-variable filter topology which offers stable and repeatable filter characteristics. DAC B and DAC D can be programmed in tandem with a single digital byte load which sets the center frequency of the filter. DAC A sets the Q of the filter. DAC C sets the gain of the filter transfer function. The unique feature of this design is that varying the gain of filter does not affect the Q of the filter. Similarly, the reverse is also true. This makes the programmability of the filter extremely reliable and predictable. Note that low-pass, high-pass, and bandpass outputs are available. This sophisticated function is achieved in only two IC packages.

The network analyzer photo shown in Figure 10 superimposes five actual bandpass responses ranging from the lowest frequency of 75 Hz (1 LSB ON) to a full-scale frequency of 19.132 kHz (all bits ON), which is equivalent to a 256 to 1 dynamic range. The frequency is determined by  $f_C=1/2\pi RC$  where R is the ladder resistance  $(R_{\rm IN})$  of the DAC8408, and C is 1000 pF. Note that from device to device, the resistance  $R_{\rm IN}$  varies. Thus some tuning may be necessary.

Figure 10. Programmable Active Filter Band-Pass Frequency Response

All components used are available off-the-shelf. Using low drift thin-film resistors, the DAC 8408 exhibits very stable performance over temperature. The wide bandwidth of the OP-470 produces excellent high frequency and high Q response. In addition, the OP470's low input offset voltage assures an unusually low dc offset at the filter output.

REV. A -13-

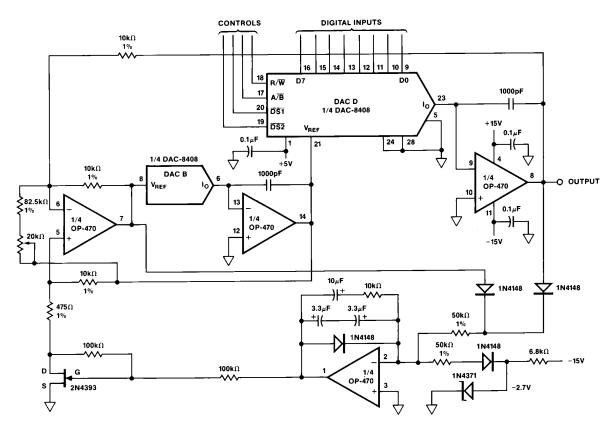

Figure 11. A Digitally Programmable, Low-Distortion Sinewave Oscillator

# A LOW-DISTORTION, PROGRAMMABLE SINEWAVE OSCILLATOR

By varying the previous state-variable filter topology slightly, one can obtain a very low distortion sinewave oscillator with programmable frequency feature as shown in Figure 11. Again, DAC B and DAC D in tandem control the oscillating frequency based on the relationship  $f_C=1/2\pi RC$ . Positive feedback is accomplished via the 82.5 k $\Omega$  and the 20 k $\Omega$  potentiometer. The Q of the oscillator is determined by the ratio of 10 k $\Omega$  and

$475\Omega$  in series with the FET transistor, which acts as an automatic gain control variable resistor. The AGC action maintains a very stable sinewave amplitude at any frequency. Again, only two ICs accomplish a very useful function.

At the highest frequency setting, the harmonic distortion level measures 0.016%. As the frequencies drop, distortion also drops to a low of 0.006%. At the lowest frequency setting, distortion came back up to a worst case of 0.035%.

-14- REV. A