## **SMBus Dual/Quad Current Monitor**

#### **General Description**

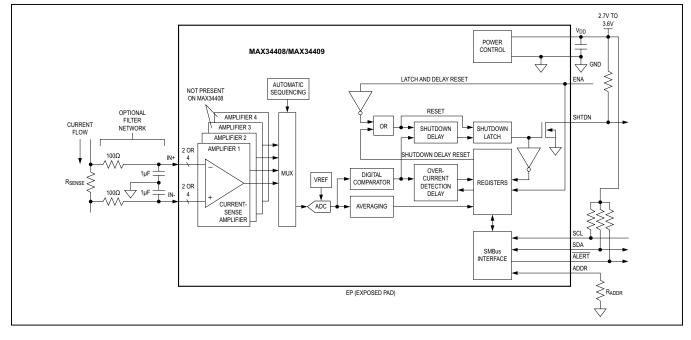

The MAX34408/MAX34409 are two- and four-channel current monitors that are configured and monitored with a standard I<sup>2</sup>C/SMBus serial interface. Each unidirectional current sensor offers precision high-side operation with a low full-scale sense voltage. The devices automatically sequence through two or four channels and collect the current-sense samples and average them to reduce the effect of impulse noise. The raw ADC samples are compared to user-programmable digital thresholds to indicate overcurrent conditions. Overcurrent conditions trigger a hardware output to provide an immediate indication to shut down any necessary external circuitry.

#### **Applications**

- Network Switches and Routers

- Base Stations

- Servers

- Smart Grid Network Systems

- Industrial Controls

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Enables Accurate Current Consumption Measurement on Up to Four Rails with Digital Serial Readout

- Low 12.25mV Full-Scale Current-Sense Voltage

- Automatic Round Robin Sequencing to Sample Each Current-Sense Input

- Selectable Averaging to Improve Current-Sense Accuracy

- Programmable Digital Overcurrent Thresholds with Delay Function

- I<sup>2</sup>C/SMBus Interface with Bus Timeout

- Register Access to Real-Time Current Measurements

- Compatible on a Wide Range of Voltage Rails

Wide 2.5V to 13.2V Common-Mode Range

- Automatic System Shutdown on Overcurrent Condition

Shutdown Output Provides Immediate Hardware Indication of Overcurrent

For related parts and recommended products to use with this part, refer to <u>www.maximintegrated.com/MAX34408.related</u>.

## **Typical Application Circuit and Block Diagram**

## SMBus Dual/Quad Current Monitor

## **Absolute Maximum Ratings**

| Voltage Range on V <sub>DD</sub> Relative to GND     | 0.3V to +4V    |

|------------------------------------------------------|----------------|

| Voltage Range on IN+, IN- Relative to GND            | 0.3V to +16V   |

| Voltage Range on All Other Pins                      |                |

| Relative to GND0.3V to (V <sub>DD</sub> + 0.3V) (not | to exceed +4V) |

| Differential Input Voltage, IN+ to IN                | ±16V           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Thermal Characteristics(Note 1)

#### TQFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......40°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).....6°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="http://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Recommended DC Operating Conditions**

| PARAMETER                               | SYMBOL           | CONDITIONS | MIN                      | TYP MAX                  | UNITS |

|-----------------------------------------|------------------|------------|--------------------------|--------------------------|-------|

| V <sub>DD</sub> Operating Voltage Range | V <sub>DD</sub>  |            | 2.7                      | 3.6                      | V     |

| Input Logic 1: ENA Pin                  | V <sub>IH1</sub> |            | V <sub>DD</sub> x<br>0.7 | V <sub>DD</sub> +<br>0.3 | V     |

| Input Logic 0: ENA Pin                  | V <sub>IL1</sub> |            | -0.3                     | +0.3 x V <sub>DD</sub>   | V     |

| Input Logic 1: SCL/SDA Pins             | V <sub>IH2</sub> |            | 2.1                      | V <sub>DD</sub> + 0.3    | V     |

| Input Logic 0: SCL/SDA Pins             | V <sub>IL2</sub> |            | -0.3                     | +0.8                     | V     |

## **Electrical Characteristics**

$(V_{IN+} = V_{IN-} = 12V, V_{SENSE} = 0V, V_{DD} = 2.7V$  to 3.6V,  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $V_{DD} = 3.3V$  and  $T_A = +25^{\circ}C$ .) (Notes 2, 3)

| PARAMETER                                | SYMBOL          | CONDITIONS                                                   | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------|-----------------|--------------------------------------------------------------|-------|-------|-------|-------|

| Supply Current                           | I <sub>DD</sub> | SMBus idle                                                   |       | 830   |       | μA    |

| Current-Sense Common-Mode<br>Input Range |                 |                                                              | 2.5   |       | 13.2  | V     |

| Input Bias Current (IN+/IN-)             |                 | Common-mode voltage = 13.2V, IN input differential = 12.25mV |       | 2     |       | μA    |

| ADC Resolution                           |                 |                                                              | 8     |       |       | Bits  |

| Per-Channel Current<br>Sample Rate       |                 |                                                              |       | 1     |       | ksps  |

| IN Input Full Scale                      |                 |                                                              | 12.00 | 12.25 | 12.50 | mV    |

| ADC INL                                  |                 |                                                              |       | ±0.5  | ±2    | LSB   |

| ADC DNL                                  |                 |                                                              |       | ±0.5  | ±2    | LSB   |

| IN Input Offset                          |                 |                                                              |       | ±0.5  | ±4    | LSB   |

# SMBus Dual/Quad Current Monitor

## **Electrical Characteristics (continued)**

$(V_{IN+} = V_{IN-} = 12V, V_{SENSE} = 0V, V_{DD} = 2.7V$  to 3.6V,  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $V_{DD} = 3.3V$  and  $T_A = +25^{\circ}C$ .) (Notes 2, 3)

| PARAMETER                                                                                    | SYMBOL            | CONDITIONS                    | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------------------------------------|-------------------|-------------------------------|-----|-----|-----|-------|

| Output Logic Low<br>(SHTDN, ALERT)                                                           | V <sub>OL</sub>   | I <sub>OL</sub> = 4mA         |     |     | 0.4 | V     |

| Output Leakage<br>(SHTDN, ALERT)                                                             |                   |                               |     |     | ±1  | μA    |

| SCL, SDA Leakage                                                                             |                   | V <sub>DD</sub> = 0V or float |     |     | ±5  | μA    |

| ENA Leakage                                                                                  |                   |                               |     |     | ±1  | μA    |

| Digital Comparator Resolution                                                                |                   |                               | 8   |     |     | Bits  |

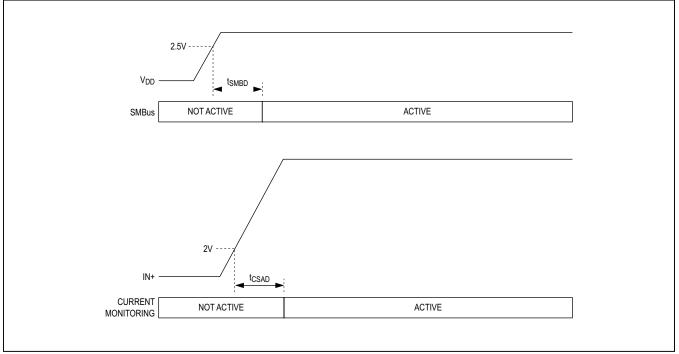

| Delay Time from V <sub>DD</sub> Applied<br>Until SMBus Active (Figure 1)                     | <sup>t</sup> SMBD |                               |     | 500 |     | μs    |

| Delay Time from Common-Mode<br>Voltage Applied Until Current<br>Monitoring Active (Figure 1) | <sup>t</sup> CSAD |                               |     | 10  |     | ms    |

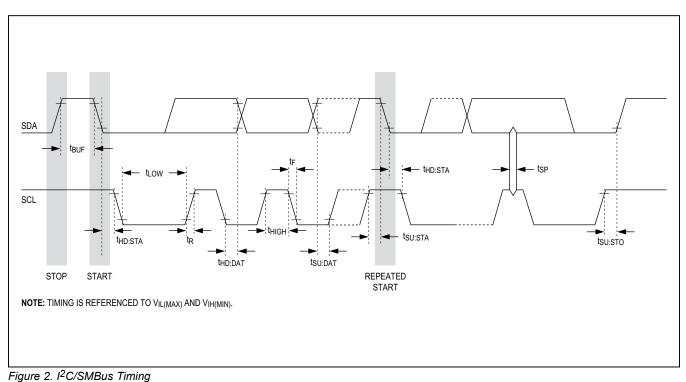

## AC Electrical Characteristics: I<sup>2</sup>C/SMBus Interface

$(V_{DD} = 2.7V \text{ to } 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{DD} = 3.3V, T_A = +25^{\circ}C.)$  (Notes 3, 4) (Figure 2)

| PARAMETER                                          | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|---------------------|------------|-----|-----|-----|-------|

| SCL Clock Frequency                                | f <sub>SCL</sub>    |            | 10  |     | 400 | kHz   |

| Bus Free Time Between<br>STOP and START Conditions | t <sub>BUF</sub>    |            | 1.3 |     |     | μs    |

| Hold Time (Repeated)<br>START Condition            | thd:sta             |            | 0.6 |     |     | μs    |

| Low Period of SCL                                  | tLOW                |            | 1.3 |     |     | μs    |

| High Period of SCL                                 | thigh               |            | 0.6 |     |     | μs    |

| Data Hold Time                                     | 4                   | Receive    | 0   |     |     | 20    |

|                                                    | <sup>t</sup> HD:DAT | Transmit   | 300 |     |     | ns    |

| Data Setup Time                                    | t <sub>SU:DAT</sub> |            | 100 |     |     | ns    |

| Start Setup Time                                   | t <sub>SU:STA</sub> |            | 0.6 |     |     | μs    |

| SDA and SCL Rise Time                              | t <sub>R</sub>      |            |     |     | 300 | ns    |

| SDA and SCL Fall Time                              | t <sub>F</sub>      |            |     |     | 300 | ns    |

| Stop Setup Time                                    | t <sub>SU:STO</sub> |            | 0.6 |     |     | μs    |

| Clock Low Timeout                                  | t <sub>TO</sub>     |            | 25  |     | 35  | ms    |

Note 2: All voltages are referenced to ground. Current entering the device are specified as positive and currents exiting the device are negative.

**Note 3:** Limits are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 4: All timing specifications are guaranteed by design.

# SMBus Dual/Quad Current Monitor

# **Timing Diagrams**

Figure 1. Delay Timing

rigure 2. r C/Sivibus rinning

# SMBus Dual/Quad Current Monitor

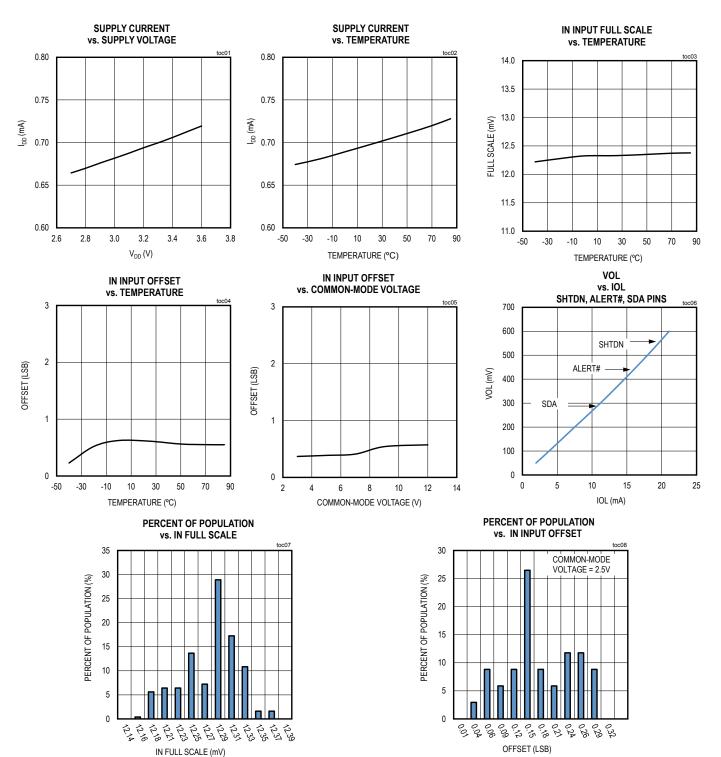

## **Typical Operating Characteristics**

(VDD = 3.3V and TA = +25°C, common-mode voltage = 12.0V, unless otherwise noted.)

# SMBus Dual/Quad Current Monitor

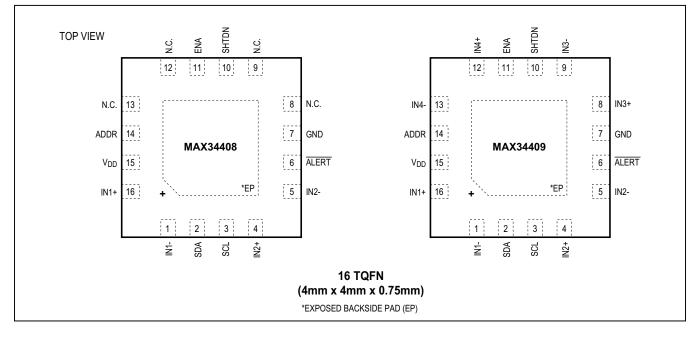

# **Pin Configurations**

## **Pin Description**

| PIN           MAX34408         MAX34409 |    | NAME  | EUNCTION                                                                                                                                                                                                                                         |  |

|-----------------------------------------|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                         |    |       | FUNCTION                                                                                                                                                                                                                                         |  |

| 1                                       | 1  | IN1-  | External Sense Resistor Load-Side Connection for Amplifier 1. This pin should be left open circuit if not needed.                                                                                                                                |  |

| 2                                       | 2  | SDA   | I <sup>2</sup> C/SMBus-Compatible Data Input/Output. Output is open drain.                                                                                                                                                                       |  |

| 3                                       | 3  | SCL   | I <sup>2</sup> C/SMBus-Compatible Clock Input                                                                                                                                                                                                    |  |

| 4                                       | 4  | IN2+  | External Sense Resistor Power-Side Connection for Amplifier 2. This pin should be left open circuit if not needed.                                                                                                                               |  |

| 5                                       | 5  | IN2-  | External Sense Resistor Load-Side Connection for Amplifier 2. This pin should be left open circuit if not needed.                                                                                                                                |  |

| 6                                       | 6  | ALERT | I <sup>2</sup> C/SMBus Interrupt. Open-drain output.                                                                                                                                                                                             |  |

| 7                                       | 7  | GND   | Ground Connection                                                                                                                                                                                                                                |  |

| 8, 9, 12, 13                            | —  | N.C.  | No Connection. Do not connect any signal to this pin.                                                                                                                                                                                            |  |

| 10                                      | 10 | SHTDN | Shutdown Output. Open-drain output. This output transitions to high impedance when any of the digital comparator thresholds are exceeded as long as the ENA pin is high.                                                                         |  |

| 11                                      | 11 | ENA   | SHTDN Enable Input. CMOS digital input. Connect to GND to clear the latch and unconditionally deassert (force low) the SHTDN output and reset the shutdown delay. Connect to $V_{DD}$ to enable normal latch operation of the SHTDN output.      |  |

| 14                                      | 14 | ADDR  | I <sup>2</sup> C/SMBus Address Select. On device power-up, the device samples a resistor to ground to determine the 7-bit serial bus address. See the <i>Addressing</i> section for details on which resistor values select which SMBus address. |  |

## SMBus Dual/Quad Current Monitor

| PIN      |                                                          | NAME            | FUNCTION                                                                                                                               |  |  |  |

|----------|----------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX34408 | MAX34409                                                 | NAME            | FUNCTION                                                                                                                               |  |  |  |

| 15       | 15                                                       | V <sub>DD</sub> | Supply Voltage for Comparators and Logic. A +2.7V to +3.6V supply. This pin should be decoupled to GND with a 100nF ceramic capacitor. |  |  |  |

| 16       | 16 16 IN1+                                               |                 | External Sense Resistor Power-Side Connection for Amplifier 1. This pin should be left open circuit if not needed.                     |  |  |  |

| _        | 8                                                        | IN3+            | External Sense Resistor Power-Side Connection for Amplifier 3. This pin should be left open circuit if not needed.                     |  |  |  |

| _        | 9                                                        | IN3-            | External Sense Resistor Load-Side Connection for Amplifier 3. This pin should be left open circuit if not needed.                      |  |  |  |

| _        | 12   IN4+                                                |                 | External Sense Resistor Power-Side Connection for Amplifier 4. This pin should be left open circuit if not needed.                     |  |  |  |

| _        | 1.3 IN4-                                                 |                 | External Sense Resistor Load-Side Connection for Amplifier 4. This pin should be left open circuit if not needed.                      |  |  |  |

|          | — EP Exposed Pad. No internal electrical connection. Can |                 | Exposed Pad. No internal electrical connection. Can be left open circuit.                                                              |  |  |  |

#### **Pin Description (continued)**

#### **Detailed Description**

The MAX34408 and MAX34409 are two- and four-channel current monitors that are configured and monitored with a standard I<sup>2</sup>C/SMBus serial interface. Each unidirectional current sensor offers precision high-side operation with a low full-scale sense voltage. The devices automatically sequence through two or four channels and collect the current-sense samples and average them to reduce the effect of impulse noise. The raw ADC samples are compared to user-programmable digital thresholds to indicate overcurrent conditions. Overcurrent conditions trigger a hardware output to provide an immediate indication to shut down any necessary external circuitry.

The devices provide an ALERT output signal. Host communications are conducted through a SMBus-compatible communications port.

#### **SMBus Operation**

The devices use the SMBus command/response format as described in the System Management Bus Specification Version 2.0. The structure of the data flow between the host and the slave is shown for several different types of transactions. Data is sent MSB first. The fixed slave address of the MAX34408 or MAX34409 is determined on device power-up by sampling the resistor connected to the ADDR pin. See the <u>Addressing</u> section for details. On device power-up, the device defaults to the STATUS command code (00h). If the host sends an invalid command code, the device NACKs (not acknowledge) the command code. If the host attempts to read the device with an invalid command code, all ones (FFh) are returned in the data byte.

# SMBus Dual/Quad Current Monitor

#### **Table 1. Read Byte Format**

| 1 | 7                | 1 | 1 | 8               | 1 | 1  | 7                | 1 | 1 | 8         | 1  | 1 |

|---|------------------|---|---|-----------------|---|----|------------------|---|---|-----------|----|---|

| S | Slave<br>Address | W | A | Command<br>Code | A | SR | Slave<br>Address | R | A | Data Byte | NA | Р |

#### **Table 2. Write Byte Format**

| 1 | 7                | 1 | 1 | 8               | 1 | 8            | 1 | 1 |

|---|------------------|---|---|-----------------|---|--------------|---|---|

| s | Slave<br>Address | W | A | Command<br>Code | А | Data<br>Byte | А | Р |

#### Key:

S = Start

SR = Repeated Start

P = Stop

W = Write Bit (0)

R = Read Bit (1)

A = Acknowledge (ACK) (0)

NA = Not Acknowledge (NACK) (1)

Shaded Block = Slave Transaction

#### Addressing

The devices respond to receiving the fixed slave address by asserting an ACK on the bus. The fixed slave address of the MAX34408 or MAX34409 is determined on device power-up by sampling the resistor connected to the ADDR pin. See <u>Table 4</u> for more details. The devices do not respond to a General Call address, only when it receives its fixed slave address or the Alert Response Address (ARA). See the ALERT description for more details.

#### ALERT and Alert Response Address (ARA)

If the  $\overline{\text{ALERT}}$  output is enabled (ALERT bit = 1 in CONTROL), when an overcurrent condition is detected, the devices assert the  $\overline{\text{ALERT}}$  signal and then wait for the host to send the Alert Response Address (ARA) as shown in Table 5.

When the ARA is received and the devices are asserting  $\overline{\text{ALERT}}$ , the devices attempt to place the fixed slave

# Table 3. Receive Byte Format (reads data from the last transacted command code)

| 1 | 7                | 1 | 1 | 8         | 1  | 1 |

|---|------------------|---|---|-----------|----|---|

| S | Slave<br>Address | R | А | Data Byte | NA | Ρ |

#### **Table 4. SMBus Slave Address Select**

| R <sub>ADDR</sub><br>(±1%) | SLAVE<br>ADDRESS  | R <sub>ADDR</sub><br>(±1%) | SLAVE<br>ADDRESS  |

|----------------------------|-------------------|----------------------------|-------------------|

| Open                       | 0011 110<br>(3Ch) | 3.01kΩ                     | 0010 110<br>(2Ch) |

| 9.31kΩ                     | 0011 100<br>(38h) | 1.69kΩ                     | 0010 100<br>(28h) |

| 6.81kΩ                     | 0011 010<br>(34h) | 750Ω                       | 0010 010<br>(24h) |

| 4.75kΩ                     | 0011 000<br>(30h) | 0 (connect to<br>GND)      | 0010 000<br>(20h) |

# Table 5. Alert Response Address (ARA)Byte Format

| 1 | 7              | 1 | 1 | 8                                    | 1  | 1 |

|---|----------------|---|---|--------------------------------------|----|---|

| S | ARA<br>0001100 | R | А | Device Slave Address<br>with LSB = 1 | NA | Ρ |

address on the bus by arbitrating the bus since another device may also try to respond to the ARA. The rules of arbitration state that the lowest address device wins. If the devices win the arbitration, they deassert ALERT. If the devices lose arbitration, they keep ALERT asserted and wait for the host to once again send the ARA.

# SMBus Dual/Quad Current Monitor

#### **SMBus Commands**

A summary of the SMBus commands supported by the devices are described in the following sections, see Table 6.

| COMMAND<br>CODE | NAME    | DETAILED DESCRIPTION                                | ТҮРЕ      | POR<br>(Note 1) |

|-----------------|---------|-----------------------------------------------------|-----------|-----------------|

| 00h             | STATUS  | Overcurrent Alarm                                   | R/W Byte  | 00h             |

| 01h             | CONTROL | Device Configuration                                | R/W Byte  | 0Ch             |

| 02h             | OCDELAY | Overcurrent Detection Delay Configuration           | R/W Byte  | 04h             |

| 03h             | SDDELAY | SHTDN Pin Delay Configuration                       | R/W Byte  | 14h             |

| 04h             | ADC1    | Averaged ADC Reading from Current Sensor 1          | Read Byte | _               |

| 05h             | ADC2    | Averaged ADC Reading from Current Sensor 2          | Read Byte |                 |

| 06h             | ADC3    | Averaged ADC Reading from Current Sensor 3 (Note 2) | Read Byte |                 |

| 07h             | ADC4    | Averaged ADC Reading from Current Sensor 4 (Note 2) | Read Byte | _               |

| 08h             | OCT1    | Overcurrent Threshold for Current Sensor 1          | R/W Byte  | D1h             |

| 09h             | OCT2    | Overcurrent Threshold for Current Sensor 2          | R/W Byte  | D1h             |

| 0Ah             | OCT3    | Overcurrent Threshold for Current Sensor 3 (Note 3) | R/W Byte  | D1h             |

| 0Bh             | OCT4    | Overcurrent Threshold for Current Sensor 4 (Note 3) | R/W Byte  | D1h             |

| 0Ch             | DID     | Device ID & Revision                                | Read Byte | Factory Set     |

| 0Dh             | DCYY    | Date Code Year                                      | Read Byte | Factory Set     |

| 0Eh             | DCWW    | Date Code Work Week                                 | Read Byte | Factory Set     |

#### Table 6. Command Codes

Note 1: POR = Power-on reset, and this is the default value when power is applied to the device.

Note 2: In the MAX34408, ADC3 and ADC4 always report 00h when read.

Note 3: In the MAX34408, OCT3 and OCT4 can be written to and read from, but they have no affect on the device.

#### STATUS (00h)

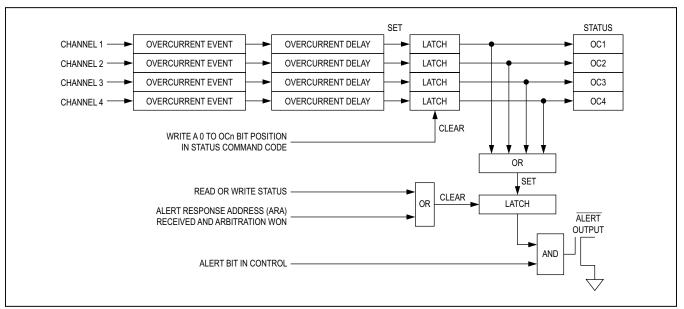

The STATUS command returns 1 byte of information with a summary of the fault conditions along with the real-time status of the ENA and SHTDN pins. The STATUS byte message content is described in <u>Table 7</u>. See <u>Figure 3</u> for STATUS bits 3:0 organization.

## Table 7. STATUS (00h)—R/W Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | NA    | NA    | ENA   | SHTDN | OC4   | OC3   | OC2   | OC1   |

| POR  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Note: Bit positions marked as NA are Not Assigned and have no meaning. These bits can be either 0 or 1 when read.

| BIT | NAME                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | ENA                               | This bit reports the real-time status of the ENA input pin. The ENA pin is sampled when SMBus communication is initiated. This bit has no affect on the ALERT output. Writing a 0 or 1 to this bit position has no affect on the device.                                                                                                                                                       |

| 4   | SHTDN                             | This bit reports the real-time status of the SHTDN output pin. The shutdown latch is sampled when SMBus communication is initiated. This bit has no affect on the ALERT output. Writing a 0 or 1 to this bit position has no affect on the device.                                                                                                                                             |

| 3:0 | OC4/OC3/<br>OC2/OC1<br>(MAX34409) | These bits reflect the latched status of the overcurrent thresholds for each current sensor. The OCD0 to OCD3 bits configured with the OCDELAY command determine the number of consecutive overcurrent threshold excursion samples that are required to set these bits. Once set, these bits remain set until written with a 0. Once they are cleared, they are not set again until the sensed |

| 1:0 | OC2/OC1<br>(MAX34408)             | current has exceeded the threshold for the programmed delay time. The setting of any of these bits asserts the ALERT pin if the ALERT bit in the CONTROL command is set to a one. Reading or writing the STATUS command deasserts the ALERT pin if it is asserted. In the MAX34408, bit positions OC3 and OC4 are inactive.                                                                    |

Figure 3. OCn Status Bits Set/Clear Functionality and ALERT Assertion

# SMBus Dual/Quad Current Monitor

#### CONTROL (01h)

The CONTROL command configures the digital current-sensing averaging function. The CONTROL command also defines if the devices respond to the Alert Response Address. The CONTROL byte command is described in Table 8.

#### Table 8. CONTROL (01h)—R/W Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | NA    | NA    | NA    | NA    | ALERT | AVG2  | AVG1  | AVG0  |

| POR  | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 0     |

Note: Bit positions marked as NA are Not Assigned and have no meaning. These bits can be either 0 or 1 when read.

| BIT | NAME      |                |                                                                                                                                                                                                                                  |                | DESCRIPTION                             |  |  |  |  |

|-----|-----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------|--|--|--|--|

| 3   | ALERT     |                | f this bit is cleared, the ALERT output is disabled and the devices do not respond to the Alert Response<br>Address. If this bit is set, the ALERT function is enabled and the devices respond to the Alert Response<br>Address. |                |                                         |  |  |  |  |

|     |           | These bits cor | nfigure the digit                                                                                                                                                                                                                | al current-sen | sing averaging function as shown below. |  |  |  |  |

|     |           | AVG2           | AVG1                                                                                                                                                                                                                             | AVG0           | SELECTED AVERAGING                      |  |  |  |  |

|     |           | 0              | 0                                                                                                                                                                                                                                | 0              | 1 Sample (no averaging)                 |  |  |  |  |

|     |           | 0              | 0                                                                                                                                                                                                                                | 1              | 2 Samples                               |  |  |  |  |

| 2:0 | AVG2/     | 0              | 1                                                                                                                                                                                                                                | 0              | 4 Samples                               |  |  |  |  |

| 2.0 | AVG1/AVG0 | 0              | 1                                                                                                                                                                                                                                | 1              | 8 Samples                               |  |  |  |  |

|     |           | 1              | 0                                                                                                                                                                                                                                | 0              | 16 Samples (default)                    |  |  |  |  |

|     |           | 1              | 0                                                                                                                                                                                                                                | 1              | 32 Samples                              |  |  |  |  |

|     |           | 1              | 1                                                                                                                                                                                                                                | 0              | 64 Samples                              |  |  |  |  |

|     |           | 1              | 1                                                                                                                                                                                                                                | 1              | 128 Samples                             |  |  |  |  |

## OVER\_CURRENT\_DELAY (02h)

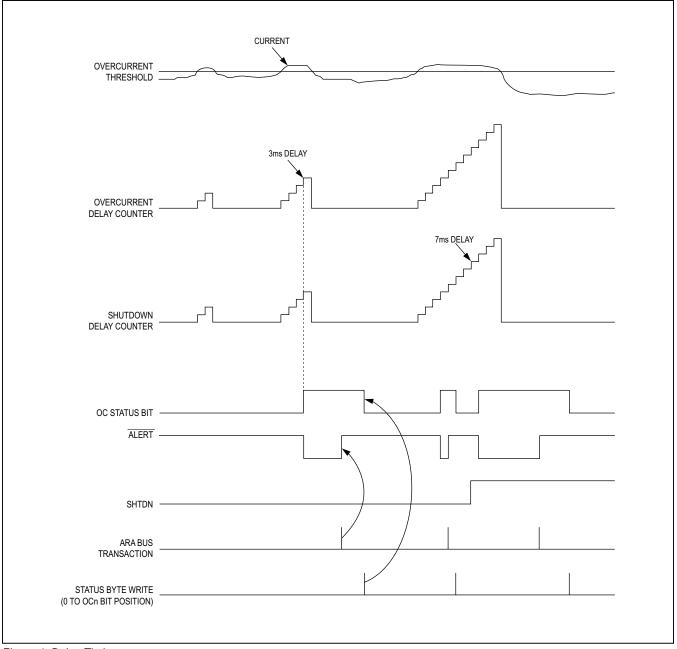

The OVER\_CURRENT\_DELAY command configures and resets the overcurrent delay counters. The OVER\_CURRENT\_DELAY byte command is described in Table 9. See Figure 4 for delay counter timing.

## Table 9. OVER\_CURRENT\_DELAY (02h)—R/W Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | RESET | OCD6  | OCD5  | OCD4  | OCD3  | OCD2  | OCD1  | OCD0  |

| POR  | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| BIT | NAME            |                                                                                                                                      | DESCRIPTION                                                                                                                                                                                                                                                           |                                                                                                                                              |  |  |  |  |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | RESET           | If this is set, all of the overcurre                                                                                                 | If this bit is cleared, the OCD0 to OCD6 bits are used to set the overcurrent delay for all channels.<br>If this is set, all of the overcurrent delay counters are reset and the devices do not trigger any<br>overcurrent events and the OC status bits are cleared. |                                                                                                                                              |  |  |  |  |

|     |                 | threshold must be continuously<br>the respective OC bit in the ST<br>with the ALERT bit in the CON<br>bit and the ALERT output are a | urrent delay as shown below. For ea<br>y breached in consecutive samples f<br>ATUS register is set and the ALERT<br>IROL command). For example, if the<br>asserted on the first sample that breact<br>I the ALERT output are not asserted<br>amples.                  | or the delay listed below before<br>output is asserted (if enabled<br>e delay is set to 0ms, then the OC<br>aches the threshold. If delay is |  |  |  |  |

|     |                 | OCD[6:0]                                                                                                                             | OCD[6:0] OVERCURRENT DELAY                                                                                                                                                                                                                                            |                                                                                                                                              |  |  |  |  |

|     |                 | 00h                                                                                                                                  | Oms                                                                                                                                                                                                                                                                   | 1 Event                                                                                                                                      |  |  |  |  |

| 6:0 | OCD6 to<br>OCD0 | 01h                                                                                                                                  | 1ms                                                                                                                                                                                                                                                                   | 2 Consecutive Events                                                                                                                         |  |  |  |  |

|     | UCDU            | 02h                                                                                                                                  | 2ms                                                                                                                                                                                                                                                                   | 3 Consecutive Events                                                                                                                         |  |  |  |  |

|     |                 | 03h                                                                                                                                  | 3ms                                                                                                                                                                                                                                                                   | 4 Consecutive Events                                                                                                                         |  |  |  |  |

|     |                 | 04h                                                                                                                                  | 4ms (default)                                                                                                                                                                                                                                                         | 5 Consecutive Events                                                                                                                         |  |  |  |  |

|     |                 | 14h                                                                                                                                  | 20ms                                                                                                                                                                                                                                                                  | 21 Consecutive Events                                                                                                                        |  |  |  |  |

|     |                 | 15h                                                                                                                                  | 21ms                                                                                                                                                                                                                                                                  | 22 Consecutive Events                                                                                                                        |  |  |  |  |

|     |                 | 7Eh                                                                                                                                  | 126ms                                                                                                                                                                                                                                                                 | 127 Consecutive Events                                                                                                                       |  |  |  |  |

|     |                 | 7Fh                                                                                                                                  | 127ms                                                                                                                                                                                                                                                                 | 128 Consecutive Events                                                                                                                       |  |  |  |  |

# SMBus Dual/Quad Current Monitor

Figure 4. Delay Timing

# SMBus Dual/Quad Current Monitor

#### SHUTDOWN\_DELAY (03h)

The SHUTDOWN\_DELAY command configures and resets the shutdown delay counters. The SHUTDOWN\_DELAY byte command is described in Table 10.

#### Table 10. SHUTDOWN\_DELAY (03h)—R/W Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | RESET | SHD6  | SHD5  | SHD4  | SHD3  | SHD2  | SHD1  | SHD0  |

| POR  | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 0     |

| BIT | NAME            |                                                                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                                             |                                                                                                       |  |  |  |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | RESET           | If this bit is cleared, the SHD0 to SHD6 bits are used to set the shutdown delay that is used to control the SHTDN pin. If this is set, the shutdown delay counter is reset and the SHTDN pin is forced inactive (low). |                                                                                                                                                                                                         |                                                                                                       |  |  |  |

|     |                 | overcurrent threshold must be of<br>below before the shutdown latc<br>is set to 0ms, then the SHTDN                                                                                                                     | wh latch delay as shown below. For<br>continuously breached in consecutiv<br>h (and hence the SHTDN pin) is as<br>output is asserted on the first sampl<br>SHTDN output is not asserted until<br>mples. | e samples for the delay listed<br>serted. For example, if the delay<br>e that breaches the threshold. |  |  |  |

|     |                 | SHD[6:0]                                                                                                                                                                                                                | SHD[6:0] SHUTDOWN DELAY                                                                                                                                                                                 |                                                                                                       |  |  |  |

|     |                 | 00h                                                                                                                                                                                                                     | 0ms                                                                                                                                                                                                     | 1 Event                                                                                               |  |  |  |

| 6:0 | SHD6 to<br>SHD0 | 01h                                                                                                                                                                                                                     | 1ms                                                                                                                                                                                                     | 2 Consecutive Events                                                                                  |  |  |  |

|     | GIIDO           | 02h                                                                                                                                                                                                                     | 2ms                                                                                                                                                                                                     | 3 Consecutive Events                                                                                  |  |  |  |

|     |                 | 03h                                                                                                                                                                                                                     | 3ms                                                                                                                                                                                                     | 4 Consecutive Events                                                                                  |  |  |  |

|     |                 | 13h                                                                                                                                                                                                                     | 19ms                                                                                                                                                                                                    | 20 Consecutive Events                                                                                 |  |  |  |

|     |                 | 14h                                                                                                                                                                                                                     | 20ms (default)                                                                                                                                                                                          | 21 Consecutive Events                                                                                 |  |  |  |

|     |                 | 15h                                                                                                                                                                                                                     | 21ms                                                                                                                                                                                                    | 22 Consecutive Events                                                                                 |  |  |  |

|     |                 | 7Eh                                                                                                                                                                                                                     | 126ms                                                                                                                                                                                                   | 127 Consecutive Events                                                                                |  |  |  |

|     |                 | 7Fh                                                                                                                                                                                                                     | 127ms                                                                                                                                                                                                   | 128 Consecutive Events                                                                                |  |  |  |

#### ADC1/2/3/4 (04h/05h/06h/07h)

The ADC1/2/3/4 command returns the associated latest measured current reading. The ADC1/2/3/4 byte command is described in Table 11.

#### Table 11. ADC1/2/3/4 (04h/05h/06h/07h)—Read Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | C7    | C6    | C5    | C4    | C3    | C2    | C1    | C0    |

| POR  | Х     | Х     | Х     | Х     | Х     | Х     | Х     | х     |

| BIT | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | C7 to C0 | These bits report the latest current reading from the ADC. The reported results are averaged according to the averaging function as configured with the AVG0 to AVG2 bits in the CONTROL command. Reading the ADC results faster than they are sampled and averaged results in the previous values being reported. In the MAX34408, ADC3 and ADC4 always report 00h when read. |

# SMBus Dual/Quad Current Monitor

#### OVER\_CURRENT\_THRESHOLD\_1/2/3/4 (08h/09h/0Ah/0Bh)

The OVER\_CURRENT\_THRESHOLD\_1/2/3/4 command sets the overcurrent threshold for each channel. The OVER\_CURRENT\_THRESHOLD\_1/2/3/4 byte command is described in <u>Table 12</u>. See <u>Table 13</u> for the configuration formula and Table 14 for an example.

#### Table 12. OVER\_CURRENT\_THRESHOLD\_1/2/3/4 (08h/09h/0Ah/0Bh)—R/W Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME | OCT7  | OCT6  | OCT5  | OCT4  | OCT3  | OCT2  | OCT1  | OCT0  |

| POR  | 1     | 1     | 0     | 1     | 0     | 0     | 0     | 1     |

Note: In the MAX34408, OCT3 and OCT4 can be written to and read from but they have no affect on the device.

| BIT | NAME            | DESCRIPTION                                                                                                                                                                                                                                                               |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | OCT7 to<br>OCT0 | These bits select the digital overcurrent threshold for each channel. The formula for selecting the threshold is as shown in Table 13. If the threshold is set to FFh, the digital comparator is disabled and the output of the comparator is unconditionally deasserted. |

#### Table 13. Overcurrent Threshold Register Configuration Formula

| Overcurrent Threshold<br>Analog Voltage at the<br>IN+/IN- Pins | ÷ | 0.01225 | = | Ratio to Full<br>Scale | x | 256 | = | Rounded<br>Decimal<br>Value | = | Overcurrent Threshold<br>Register Setting |

|----------------------------------------------------------------|---|---------|---|------------------------|---|-----|---|-----------------------------|---|-------------------------------------------|

|----------------------------------------------------------------|---|---------|---|------------------------|---|-----|---|-----------------------------|---|-------------------------------------------|

#### Table 14. Overcurrent Threshold Register Example

| 10mV | ÷ | 0.01225 | = | 0.816 | х | 256 | = | 209 | = | D1h |

|------|---|---------|---|-------|---|-----|---|-----|---|-----|

#### DEVICE\_ID\_&\_REVISION (0Ch)

The DEVICE\_ID\_&\_REVISION command returns a fixed device ID and a factory programmed revision. The DEVICE\_ID\_&\_REVISION byte command is described in Table 15.

#### Table 15. DEVICE\_ID\_&\_REVISION (0Ch)—Read Byte

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2       | BIT 1 | BIT 0 |

|------|-------|-------|-------|-------|-------|-------------|-------|-------|

| NAME | ID4   | ID3   | ID2   | ID1   | ID0   | REV2        | REV1  | REV0  |

| POR  | 0     | 0     | 0     | 0     | 1     | Factory set |       |       |

| BIT | NAME         | DESCRIPTION                                                                |

|-----|--------------|----------------------------------------------------------------------------|

| 7:3 | ID4 to ID0   | These bits report the device identification (ID). The ID is fixed at 01h.  |

| 2:0 | REV2 to REV0 | These bits report the device revision. The device revision is factory set. |

# SMBus Dual/Quad Current Monitor

#### DATE\_CODE\_YEAR (0Dh)

The DATE\_CODE\_YEAR command returns a factory programmed date code. The DATE\_CODE\_YEAR byte command is described in <u>Table 16</u>.

#### Table 16. DATE\_CODE\_YEAR (0Dh)—Read Byte

|      |       |       | · · · | -     |        |       |       |       |

|------|-------|-------|-------|-------|--------|-------|-------|-------|

| BIT  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2 | BIT 1 | BIT 0 |

| NAME | 0     | 0     | YY5   | YY4   | YY3    | YY2   | YY1   | YY0   |

| POR  |       |       |       | Facto | ry Set |       |       |       |

| BIT | NAME       | DESCRIPTION                                                                                                           |                                                                                                        |  |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |            | These bits report the last two decimal digits of the The year is reported as a binary decimal. Some of the year 2063. | e calendar year in which the device was tested.<br>examples are listed below. The range is valid until |  |  |  |  |

| 5:0 | YY5 to YY0 | YY[5:0]                                                                                                               | YEAR                                                                                                   |  |  |  |  |

|     |            | 0Ch                                                                                                                   | 2012                                                                                                   |  |  |  |  |

|     |            | 0Dh                                                                                                                   | 2013                                                                                                   |  |  |  |  |

|     |            | 14h                                                                                                                   | 2020                                                                                                   |  |  |  |  |

#### DATE\_CODE\_WORK\_WEEK (0Eh)

The DATE\_CODE\_WORK\_WEEK command returns a factory-programmed date code. The DATE\_CODE\_WORK\_WEEK byte command is described in <u>Table 17</u>.

#### Table 17. DATE\_CODE\_WORK\_WEEK (0Eh)—Read Byte

| BIT  | BIT 7 | BIT 6       | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|------|-------|-------------|-------|-------|-------|-------|-------|-------|

| NAME | 0     | 0           | WW5   | WW4   | WW3   | WW2   | WW1   | WW0   |

| POR  |       | Factory Set |       |       |       |       |       |       |

| BIT | NAME          | DESCRIPTION |                                                                                                          |  |  |  |  |

|-----|---------------|-------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |               |             | h the device was tested. The work week is reported<br>elow. 00h (0 decimal) and 36h (54 decimal) through |  |  |  |  |

| 5:0 | WW5 to<br>WW0 | WW[5:0]     | WORK WEEK                                                                                                |  |  |  |  |

|     |               | 06h         | 6                                                                                                        |  |  |  |  |

|     |               | 0Dh         | 13                                                                                                       |  |  |  |  |

|     |               | 2Bh         | 43                                                                                                       |  |  |  |  |

## SMBus Dual/Quad Current Monitor

#### **Applications Information**

#### Sense Resistor, R<sub>SENSE</sub>

Adjust the R<sub>SENSE</sub> value to monitor higher or lower current levels. Select R<sub>SENSE</sub> based on the following criteria:

**Resistor Value:** Select an  $R_{SENSE}$  resistor value in which the largest expected current results in a 10mV full-scale current-sense voltage. Select  $R_{SENSE}$  in accordance to the following equation and see Table 18 for examples:

R<sub>SENSE</sub> = 10mV/(Max Current)

**Power Dissipation:** Select a sense resistor that is rated for the max expected current and power dissipation (wattage). The sense resistor's value might drift if it is allowed to heat up excessively.

#### Accuracy

Current measurement accuracy increases the closer the measured current readings are to the 12.25mV full-scale current-sense voltage. This is because offsets become less significant when the sense voltage is larger. For best performance, select  $R_{SENSE}$  to provide approximately 10mV of sense voltage for the full-scale current in each application. Figure 5 shows the error contributed by the input offset vs. reading percentage of full scale.

#### Table 18. RSENSE Example Values

| R <sub>SENSE</sub> (mΩ) | MAX CURRENT (A) |

|-------------------------|-----------------|

| 0.25                    | 40              |

| 0.5                     | 20              |

| 1                       | 10              |

| 5                       | 2               |

| 10                      | 1               |

| 50                      | 0.2             |

| 100                     | 0.1             |

| 200                     | 0.05            |

| 500                     | 0.02            |

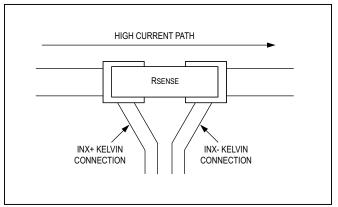

#### **Kelvin Connections**

Because of the high currents that flow through R<sub>SENSE</sub>, take care to eliminate parasitic trace resistance from causing errors in the sense voltage. Use Kelvin (force and sense) PCB layout techniques as shown in Figure 6.

Figure 5. Input Offset Error

Figure 6. Kelvin Connection Layout Example

## SMBus Dual/Quad Current Monitor

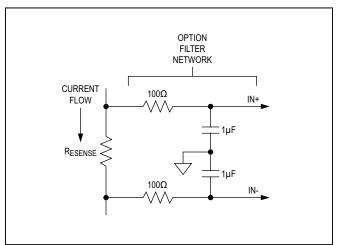

#### **Optional Filter Network**

For noisy environments, a simple lowpass filter can be placed at the devices' amplifier inputs as shown in Figure 7. The 100 $\Omega$  resistor and 1µF capacitor provide a 1.6kHz rolloff frequency. To achieve the most effective results, use the filter in conjunction with the device's digital averaging as described in the *CONTROL (01h)* section.

#### Layout Considerations

For noisy digital environments, the use of a multilayer PCB with separate ground and power-supply planes is recommended. Keep digital signals far away from the sensitive analog inputs. Unshielded long traces at the input terminals of the amplifier can degrade performance due to noise pickup. The analog differential current-sense traces should be routed close together to maximize common-mode rejection.

#### **Power-Supply Decoupling**

To achieve the best results when using these devices, decouple the  $V_{DD}$  power supply with a  $0.1\mu$ F capacitor. Use a high-quality, ceramic, surface-mount capacitor if possible. Surface-mount components minimize lead inductance, which improves performance, and ceramic capacitors tend to have adequate high-frequency response for decoupling applications.

Figure 7. Filter Network

## **Ordering Information**

| PART         | CONFIGURATION | PIN-PACKAGE |

|--------------|---------------|-------------|

| MAX34408ETE+ | Dual          | 16 TQFN-EP* |

| MAX34409ETE+ | Quad          | 16 TQFN-EP* |

+Denotes a lead (Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND        |  |

|------------|---------|----------------|-------------|--|

| TYPE       | CODE    | NO.            | PATTERN NO. |  |

| 16 TQFN-EP | T1644+4 | <u>21-0139</u> | 90-0070     |  |

# SMBus Dual/Quad Current Monitor

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                           | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------|------------------|

| 0                  | 9/13             | Initial release                       | —                |

| 1                  | 1/15             | Updated Benefits and Features section | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.