# TC14433/A

# 3-1/2 Digit, Analog-to-Digital Converter

#### Features:

- Accuracy: ±0.05% of Reading ±1 Count

- Two Voltage Ranges: 1.999V and 199.9 mV

- · Up to 25 Conversions Per Second

- Z<sub>IN</sub> > 1000M Ohms

- Single Positive Voltage Reference

- Auto-Polarity and Auto-Zero

- Overrange and Underrange Signals Available

- Operates in Auto-Ranging Circuits

- Uses On-Chip System Clock or External Clock

- Wide Supply Range: ±4.5V to ±8V

#### **Applications:**

- Portable Instruments

- Digital Voltmeters

- Digital Panel Meters

- Digital Scales

- Digital Thermometers

- Remote A/D Sensing Systems

- MPU Systems

#### **Device Selection Table**

| Part Number | Package                 | Temperature<br>Range |

|-------------|-------------------------|----------------------|

| TC14433AEJG | 24-Pin CERDIP<br>(Wide) | -40°C to +85°C       |

| TC14433AELI | 28-Pin PLCC             | -40°C to +85°C       |

| TC14433AEPG | 24-Pin PDIP<br>(Wide)   | -40°C to +85°C       |

| TC14433COG  | 24-Pin SOIC<br>(Wide)   | 0°C to +70°C         |

| TC14433EJG  | 24-Pin CERDIP<br>(Wide) | -40°C to +85°C       |

| TC14433ELI  | 28-Pin PLCC             | -40°C to +85°C       |

| TC14433EPG  | 24-Pin PDIP<br>(Wide)   | -40°C to +85°C       |

### **General Description**

The TC14433 is a low-power, high-performance, monolithic CMOS 3-1/2 digit A/D converter. The TC14433 combines both analog and digital circuits on a single IC, thus minimizing the number of external components.

This dual slope A/D converter provides automatic polarity and zero correction with the addition of two external resistors and two capacitors. The full scale voltage range of this ratiometric IC extends from 199.9 millivolts to 1.999 volts. The TC14433 can operate over a wide range of power supply voltages, including batteries and standard 5-volt supplies.

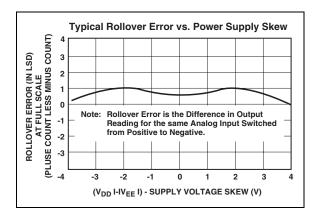

The TC14433A features improved performance over the industry standard TC14433. Rollover, which is the measurement of identical positive and negative signals, is specified to have the same reading within one count for the TC14433A. Power consumption of the TC14433A is typically 4 mW, approximately onehalf that of the industry standard TC14433.

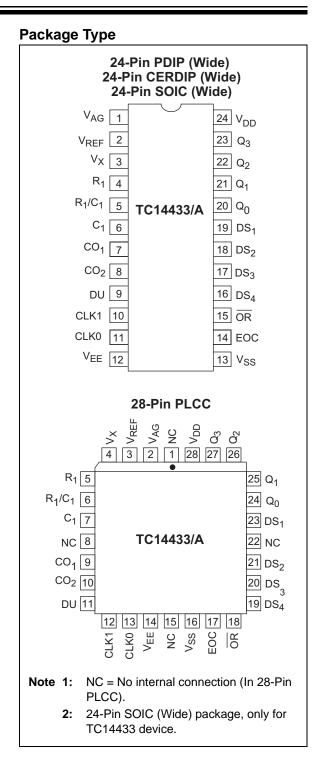

The TC14433/A is available in 24-Pin PDIP, 24-Pin CERDIP, 24-Pin SOIC (TC14433 device only), and 28-Pin PLCC packages.

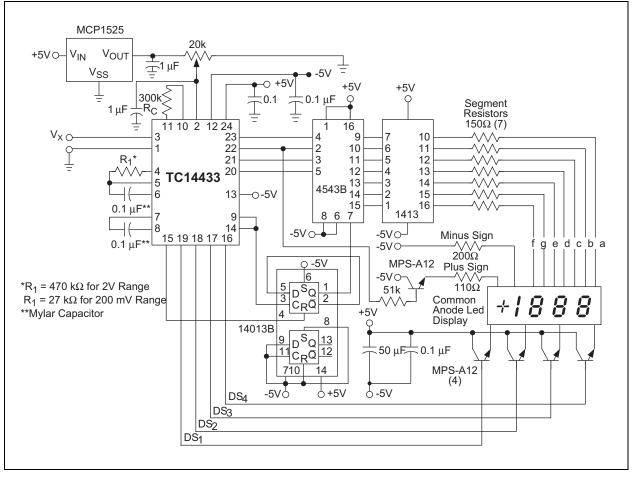

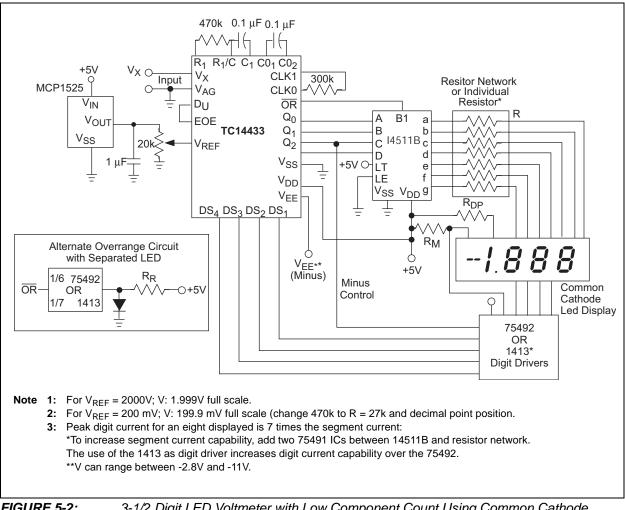

## **Typical Application**

## 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings\***

| Supply Voltage ( $V_{DD} - V_{EE}$ )0.5V to +18V |

|--------------------------------------------------|

| Voltage on Any Pin:                              |

| Reference to $V_{EE}$ 0.5V to ( $V_{DD}$ + 0.5)  |

| DC Current, Any Pin:±10 mA                       |

| Power Dissipation ( $T_A \le 70^{\circ}$ C):     |

| Plastic PLCC1.0W                                 |

| Plastic PDIP940W                                 |

| SOIC                                             |

| CERDIP 1.45W                                     |

| Operating Temperature Range 0°C to +70°C         |

| Storage Temperature Range65°C to +160°C          |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

| TABLE 1-1: TC14433/A ELE | ECTRICAL SPECIFICATIONS |

|--------------------------|-------------------------|

|--------------------------|-------------------------|

**Electrical Characteristics:**  $V_{DD}$  = +5V,  $V_{EE}$  = -5V,  $C_1$  = 0.1  $\mu$ F, (Mylar),  $C_0$  = 0.1  $\mu$ F,  $R_C$  = 300 kΩ,  $R_1$  = 470 kΩ @  $V_{REF}$  = 2V,  $R_1$  = 27 kΩ @  $V_{REF}$  = 200 mV,  $T_A$  = 25°C, unless otherwise specified.

| Symbol          | Parameter                                                        | Min      | Тур   | Max      | Min | Тур | Max | Units      | Test Conditions                                                          |  |

|-----------------|------------------------------------------------------------------|----------|-------|----------|-----|-----|-----|------------|--------------------------------------------------------------------------|--|

| Analog I        | Analog Input                                                     |          |       |          |     |     |     |            |                                                                          |  |

| SYE             | Rollover Error (Positive) and<br>Negative Full Scale<br>Symmetry | -1       | —     | +1       | _   | —   | —   | Count<br>s | 200 mV Full Scale<br>V <sub>IN</sub> -V <sub>IN</sub> = +V <sub>IN</sub> |  |

| NL              | Linearity Output Reading                                         | -0.05    | +0.05 | +0.05    |     | —   | —   | %rdg       | $V_{REF} = 2V$                                                           |  |

|                 | (Note 1)                                                         | -1 count | —     | +1 count |     | —   | —   | %rdg       | $V_{REF} = 200 \text{ mV}$                                               |  |

| SOR             | Stability Output Reading (Note 2)                                |          | —     | 2        | _   | —   | —   | LSD        | V <sub>X</sub> = 1.99V,<br>V <sub>REF</sub> = 2V                         |  |

|                 |                                                                  |          | —     | 3        | _   | —   | —   | LSD        | V <sub>X</sub> = 199 mV,<br>V <sub>REF</sub> = 200 mV                    |  |

| ZOR             | Zero Output Reading                                              | —        | 0     | 0        | _   | —   | —   | LSD        | $V_X = 0V, V_{REF} = 2V$                                                 |  |

| I <sub>IN</sub> | Bias Current: Analog Input                                       | -        | ±20   | ±100     | _   | —   | —   | pА         |                                                                          |  |

|                 | Reference Input<br>Analog Ground                                 | _        | ±20   | ±100     | _   | —   | —   | pА         |                                                                          |  |

|                 | Analog Ground                                                    | —        | ±20   | ±100     | _   |     | _   | pА         |                                                                          |  |

| CMRR            | Common mode Rejection                                            | _        | 65    | —        |     | —   | _   | dB         | $V_X = 1.4V, V_{REF} = 2V,$<br>$F_{OC} = 32 \text{ kHz}$                 |  |

**Note 1:** Accuracy – The accuracy of the meter at full scale is the accuracy of the setting of the reference voltage. Zero is recalculated during each conversion cycle. The meaningful specification is linearity. In other words, the deviation from correct reading for all inputs other than positive full scale and zero is defined as the linearity specification.

2: The LSD stability for 200 mV scale is defined as the range that the LSD will occupy 95% of the time.

**3:** Pin numbers refer to 24-pin PDIP.

#### TABLE 1-1: TC14433/A ELECTRICAL SPECIFICATIONS (CONTINUED)

|                                                   | al Characteristics: $V_{DD} = +5V$ ,<br>$V_{REF} = 200 \text{ mV}$ , $T_A = 25^{\circ}C$ , ur | V <sub>EE</sub> = -5V, | C <sub>1</sub> = 0.1 | μF, (Mylar) |       | , | ; = 300 k | Ω, R <sub>1</sub> = 4 | 70 kΩ @ $V_{REF}$ = 2V, R <sub>1</sub> =                                                  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|----------------------|-------------|-------|---|-----------|-----------------------|-------------------------------------------------------------------------------------------|

| Symbol                                            |                                                                                               |                        |                      |             |       |   |           | Test Conditions       |                                                                                           |

| Digital                                           |                                                                                               |                        |                      |             |       |   |           |                       |                                                                                           |

| V <sub>OL</sub>                                   | Output Voltage<br>(Pins 14 to 23) (Note 3)                                                    | _                      | 0                    | 0.05        | _     | — | 0.05      | V                     | V <sub>SS</sub> = 0V, "0" Level                                                           |

|                                                   |                                                                                               | _                      | -5                   | -4.95       | —     |   | -4.95     | V                     | V <sub>SS</sub> = -5V, "0" Level                                                          |

| V <sub>OH</sub>                                   | Output Voltage<br>(Pins 14 to 23) (Note 3)                                                    | 4.95                   | 5                    | _           | 4.95  | — | —         | V                     | V <sub>SS</sub> = 0V, "1" Level                                                           |

|                                                   |                                                                                               | 4.95                   | 5                    | _           | 4.95  | — | —         | V                     | V <sub>SS</sub> = -5V, "1" Level                                                          |

| I <sub>OH</sub> Output Current<br>(Pins 14 to 23) | Output Current<br>(Pins 14 to 23)                                                             | -0.2                   | -0.36                | _           | -0.14 | — | —         | mA                    | V <sub>SS</sub> = 0V, V <sub>OH</sub> = 4.6V<br>Source                                    |

|                                                   |                                                                                               | - 0.5                  | -0.9                 | —           | -0.35 | — | -         | mA                    | V <sub>SS</sub> = -5V, V <sub>OH</sub> = 5V<br>Source                                     |

| I <sub>OL</sub> Output Current<br>(Pins 14 to 23) |                                                                                               | 0.51                   | 0.88                 | _           | 0.36  | — | —         | mA                    | $V_{SS} = 0V, V_{OL} = 0.4V$<br>Sink                                                      |

|                                                   |                                                                                               | 1.3                    | 2.25                 | _           | 0.9   | — | —         | mA                    | V <sub>SS</sub> = -5V,<br>V <sub>OL</sub> = -4.5V Sink                                    |

| f <sub>CLK</sub>                                  | Clock Frequency                                                                               | _                      | 66                   | _           | —     | _ | —         | kHz                   | R <sub>C</sub> = 300 kΩ                                                                   |

| I <sub>DU</sub>                                   | Input Current -DU                                                                             | _                      | ±0.00<br>001         | ±0.3        | -     | — | ±1        | μA                    |                                                                                           |

| Power                                             |                                                                                               |                        |                      |             |       |   |           |                       |                                                                                           |

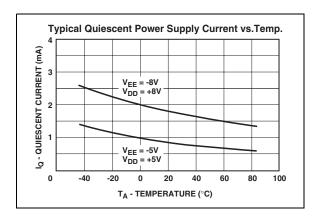

| l <sub>Q</sub>                                    | Quiescent Current: 14433A:                                                                    | _                      |                      | _           | —     | — | _         |                       | $V_{DD}$ to $V_{EE}$ , $I_{SS} = 0$                                                       |

|                                                   |                                                                                               | _                      | 0.4                  | 2           | —     | _ | 3.7       | mA                    | V <sub>DD</sub> = 5, V <sub>EE</sub> = -5                                                 |

|                                                   |                                                                                               | _                      | 1.4                  | 4           | —     | _ | 7.4       | mA                    | V <sub>DD</sub> = 8, V <sub>EE</sub> = -8                                                 |

|                                                   | Quiescent Current: 14433:                                                                     |                        |                      |             | —     |   | _         | _                     | $V_{DD}$ to $V_{EE}$ , $I_{SS} = 0$                                                       |

|                                                   |                                                                                               | _                      | 0.9                  | 2           | —     | — | 3.7       | mA                    | $V_{DD} = 5, V_{EE} = -5$                                                                 |

|                                                   |                                                                                               | _                      | 1.8                  | 4           | —     | — | 7.4       | mA                    | $V_{DD} = 8, V_{EE} = -8$                                                                 |

| PSRR                                              | Supply Rejection                                                                              | _                      | 0.5                  | _           | —     | — | -         | mV/V                  | $V_{DD}$ to $V_{EE}$ , $I_{SS} = 0$ ,<br>$V_{REF} = 2V$ ,<br>$V_{DD} = 5$ , $V_{EE} = -5$ |

**Note 1:** Accuracy – The accuracy of the meter at full scale is the accuracy of the setting of the reference voltage. Zero is recalculated during each conversion cycle. The meaningful specification is linearity. In other words, the deviation from correct reading for all inputs other than positive full scale and zero is defined as the linearity specification.

2: The LSD stability for 200 mV scale is defined as the range that the LSD will occupy 95% of the time.

**3:** Pin numbers refer to 24-pin PDIP.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

| Pin No.<br>(24-Pin PDIP)<br>(24-Pin CERDIP)<br>(24-Pin SOIC) | Pin No.<br>(28-Pin<br>PLCC) | Symbol           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------------------------------------------------------------|-----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                            | 2                           | V <sub>AG</sub>  | This is the analog ground. It has a high input impedance. The pin determines the reference level for the unknown input voltage ( $V_X$ ) and the reference voltage ( $V_{REF}$ ).                                                                                                                                                                                                                                                                   |  |  |  |  |

| 2                                                            | 3                           | V <sub>REF</sub> | Reference voltage – Full scale output is equal to the voltage applied to $V_R$<br>Therefore, full scale voltage of 1.999V requires 2V reference and 199.9 m<br>full scale requires a 200 mV reference. $V_{REF}$ functions as system reset als<br>When switched to $V_{EE}$ , the system is reset to the beginning of the<br>conversion cycle.                                                                                                      |  |  |  |  |

| 3                                                            | 4                           | V <sub>X</sub>   | The unknown input voltage ( $V_X$ ) is measured as a ratio of the reference voltage ( $V_{REF}$ ) in a ratiometric A/D conversion.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 4                                                            | 5                           | R <sub>1</sub>   | This pin is for external components used for the integration function in the dual slope conversion. Typical values are 0.1 $\mu$ F (Mylar) capacitor for C <sub>1</sub> .                                                                                                                                                                                                                                                                           |  |  |  |  |

| 5                                                            | 6                           | $R_1/C_1$        | $R_1 = 470 \text{ k}\Omega$ (resistor) for 2V full scale.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 6                                                            | 7                           | C <sub>1</sub>   | $R_1 = 27 \text{ k}\Omega$ (resistor) for 200 mV full scale. Clock frequency of 66 kHz gives 250 msec conversion time.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 7                                                            | 9                           | CO <sub>1</sub>  | These pins are used for connecting the offset correction capacitor. The recommended value is 0.1 $\mu\text{F}.$                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 8                                                            | 10                          | CO <sub>2</sub>  | These pins are used for connecting the offset correction capacitor. The recommended value is 0.1 $\mu\text{F}.$                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 9                                                            | 11                          | DU               | Display update input pin. When DU is connected to the EOC output, exconversion is displayed. New data will be strobed into the output latched during the conversion cycle if a positive edge is received on DU, prior to ramp down cycle. When this pin is driven from an external source, the voltage should be referenced to $V_{SS}$ .                                                                                                           |  |  |  |  |

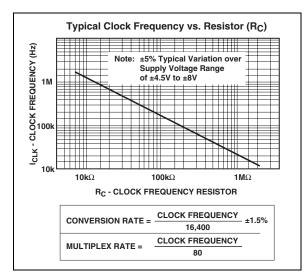

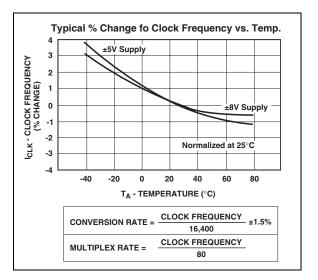

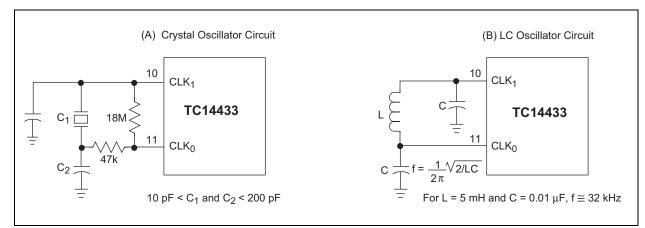

| 10                                                           | 12                          | CLK <sub>1</sub> | Clock input pins. The TC14433 has its own oscillator system clock. Connecting a single resistor between $CLK_1$ and $CLK_0$ sets the clock frequency.                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 11                                                           | 13                          | CLK <sub>0</sub> | A crystal or OC circuit may be inserted in lieu of a resistor for improved CLK <sub>1</sub> , the clock input, can be driven from an external clock source, which need only have standard CMOS output drive. This pin is referenced to V <sub>EE</sub> for external clock inputs. A 300 k $\Omega$ resistor yields a clock frequency of about 66 kHz. See <b>Section 3.0 "Typical Characteristics"</b> . (Also see Figure for alternate circuits.)  |  |  |  |  |

| 12                                                           | 14                          | V <sub>EE</sub>  | Negative power current. Connection pin for the most negative supply. Please note the current for the output drive circuit is returned through V <sub>SS</sub> . Typical supply current is 0.8 mA.                                                                                                                                                                                                                                                   |  |  |  |  |

| 13                                                           | 16                          | V <sub>SS</sub>  | Negative power supply for output circuitry. This pin sets the low voltage level for the output pins (BCD, Digit Selects, EOC, OR). When connected to analog ground, the output voltage is from analog ground to V <sub>DD</sub> . If connected to V <sub>EE</sub> , the output swing is from V <sub>EE</sub> to V <sub>DD</sub> . The recommended operating range for V <sub>SS</sub> is between the V <sub>DD</sub> -3 volts and V <sub>EE</sub> . |  |  |  |  |

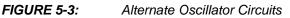

| 14                                                           | 17                          | EOC              | End of conversion output generates a pulse at the end of each conversion cycle. This generated pulse width is equal to one half the period of the system clock.                                                                                                                                                                                                                                                                                     |  |  |  |  |

TABLE 2-1: PIN FUNCTION TABLE

| Pin No.<br>(24-Pin PDIP)<br>(24-Pin CERDIP)<br>(24-Pin SOIC) | Pin No.<br>(28-Pin<br>PLCC) | Symbol          | Description                                                                                                                                             |  |  |  |

|--------------------------------------------------------------|-----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15                                                           | 18                          | OR              | Overrange pin. Normally this pin is set high. When $V_{X}$ exceeds $V_{REF}$ the OR is low.                                                             |  |  |  |

| 16                                                           | 19                          | DS <sub>4</sub> | Digit select pin. The digit select output goes high when the respective digit is selected. The MSD (1/2 digit turns on immediately after an EOC pulse). |  |  |  |

| 17                                                           | 20                          | DS <sub>3</sub> | The remaining digits turn on in sequence from MSD to LSD.                                                                                               |  |  |  |

| 18                                                           | 21                          | DS <sub>2</sub> | To ensure that the BCD data has settled, an inter digit blanking time of tw clock periods is included.                                                  |  |  |  |

| 19                                                           | 23                          | DS <sub>1</sub> | Clock frequency divided by 80 equals multiplex rate. For example, a system clock of 60 kHz gives a multiplex rate of 0.8 kHz.                           |  |  |  |

| 20                                                           | 24                          | Q <sub>0</sub>  | See Figure for digit select timing diagram.                                                                                                             |  |  |  |

| 21                                                           | 25                          | Q <sub>1</sub>  | BCD data output pin. Multiplexed BCD outputs contain three full digits of information during digit select $DS_2$ , $DS_3$ , $DS_4$ .                    |  |  |  |

| 22                                                           | 26                          | Q <sub>2</sub>  | During $DS_1$ , the 1/2 digit, overrange, underrange and polarity information is available.                                                             |  |  |  |

| 23                                                           | 27                          | Q <sub>3</sub>  | Refer to the Truth Table 5-1.                                                                                                                           |  |  |  |

| 24                                                           | 28                          | V <sub>DD</sub> | Positive power supply. This is the most positive power supply pin.                                                                                      |  |  |  |

|                                                              | 1                           | NC              | Not Used.                                                                                                                                               |  |  |  |

|                                                              | 8                           | NC              | Not Used.                                                                                                                                               |  |  |  |

| _                                                            | 15                          | NC              | Not Used.                                                                                                                                               |  |  |  |

|                                                              | 22                          | NC              | Not Used.                                                                                                                                               |  |  |  |

# TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

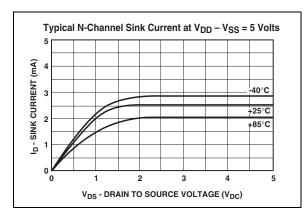

# 3.0 TYPICAL CHARACTERISTICS

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

# 4.0 DETAILED DESCRIPTION

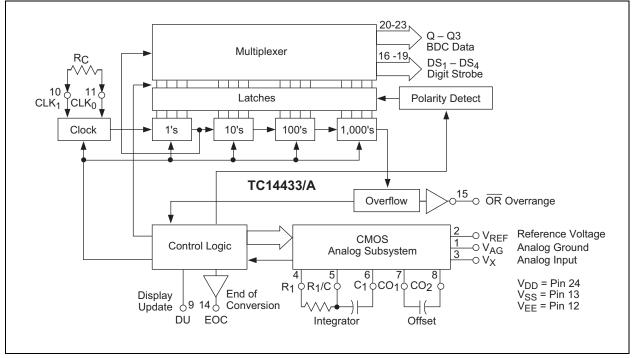

The TC14433 CMOS IC becomes a modified dualslope A/D with a minimum of external components. This IC has the customary CMOS digital logic circuitry, as well as CMOS analog circuitry. It provides the user with digital functions such as (counters, latches, multiplexers), and analog functions such as (operational amplifiers and comparators) on a single chip. Refer to the Functional Block diagram, Figure .

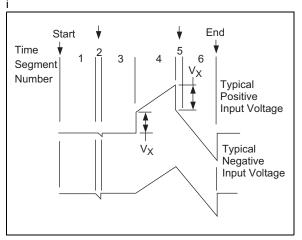

Features of the TC14433/A include auto-zero, high input impedances and auto-polarity. Low power consumption and a wide range of power supply voltages are also advantages of this CMOS device. The system's auto-zero function compensates for the offset voltage of the internal amplifiers and comparators. In this "ratiometric system," the output reading is the ratio of the unknown voltage to the reference voltage, where a ratio of 1 is equal to the maximum count of 1999. It takes approximately 16,000 clock periods to complete one conversion cycle. Each conversion cycle may be divided into 6 segments. Figure shows the conversion cycle in 6 segments for both positive and negative inputs.

FIGURE 4-1:

Integrator Waveforms at Pin 6

**Segment 1** – The offset capacitor ( $C_O$ ), which compensates for the input offset voltages of the buffer and integrator amplifiers, is charged during this period. However, the integrator capacitor is shorted. This segment requires 4000 clock periods.

**Segment 2** – During this segment, the integrator output decreases to the comparator threshold voltage. At this time, a number of counts equivalent to the input offset voltage of the comparator is stored in the offset latches for later use in the auto-zero process. The time for this segment is variable and less than 800 clock periods.

**Segment 3** – This segment of the conversion cycle is the same as Segment 1.

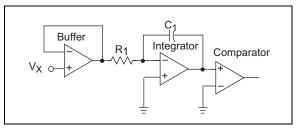

**Segment 4** – Segment 4 is an up going ramp cycle with the unknown input voltage ( $V_X$  as the input to the integrator. Figure 4-2 shows the equivalent configuration of the analog section of the TC14433. The actual configuration of the analog section is dependent upon the polarity of the input voltage during the previous conversion cycle.

FIGURE 4-2: Equivalent Circuit Diagrams of the Analog Section During Segment 4 of the Timing Cycle

**Segment 5** – This segment is a down-going ramp period with the reference voltage as the input to the integrator. Segment 5 of the conversion cycle has a time equal to the number of counts stored in the offset storage latches during Segment 2. As a result, the system zeros automatically.

**Segment 6** – This is an extension of Segment 5. The time period for this portion is 4000 clock periods. The results of the A/D conversion cycle are determined in this portion of the conversion cycle.

FIGURE 4-3:

Functional Block Diagram

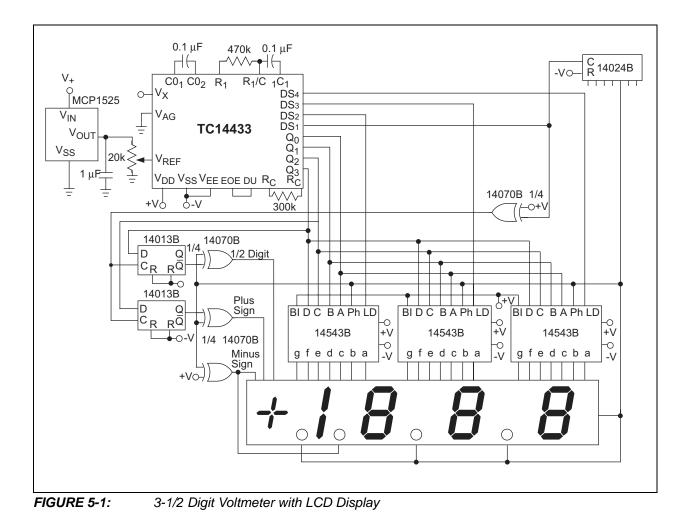

# 5.0 TYPICAL APPLICATIONS

The Typical Application circuit is an example of a 3-1/2 digit voltmeter using the TC14433 with Commonanode displays. This system requires a 2.5V reference. Full scale may be adjusted to 1.999V or 199.9 mV. Input overrange is indicated by flashing a display. This display uses LEDs with common anode digit lines. Power supply for this system is shown as a dual  $\pm$ 5V supply; however, the TC14433 will operate over a wide voltage range

The circuit in Figure shows a 3-1/2 digit LCD voltmeter. The 14024B provides the low frequency square wave signal drive to the LCD backplane. Dual power supplies are shown here; however, one supply may be used when V<sub>SS</sub> is connected to V<sub>EE</sub>. In this case, V<sub>AG</sub> must be at least 2.8V above V<sub>EE</sub>.

When only segments b and c of the decoder are connected to the 1/2 digit of the display, 4, 0, 7 and 3 appear as 1.

The overrange indication ( $Q_3 = 0$  and  $Q_0 = 1$ ) occurs when the count is greater than 1999; (e.g., 1.999V for a reference of 2V) The underrange indication, useful for auto-ranging circuits, occurs when the count is less than 180; (e.g., 0.180V for a reference of 2V).

| Note: | If the most significant digit is connected to |

|-------|-----------------------------------------------|

|       | a display other than a "1" only, such as a    |

|       | full digit display, segments other than b     |

|       | and c must be disconnected. The BCD to        |

|       | 7-segment decoder must blank on BCD           |

|       | inputs 1010 to 1111 (see Table 5-1).          |

| Coded<br>Condition<br>of MSD | Q<br>3 | Q<br>2 | <b>Q</b><br>1 | Q<br>o | BDC   | to 7-Segment<br>Decoding |

|------------------------------|--------|--------|---------------|--------|-------|--------------------------|

| +0                           | 1      | 1      | 1             | 0      |       | Blank                    |

| -0                           | 1      | 0      | 1             | 0      |       | Blank                    |

| +0 UR                        | 1      | 1      | 1             | 1      |       | Blank                    |

| -0 UR                        | 1      | 0      | 1             | 1      |       | Blank                    |

| +1                           | 0      | 1      | 0             | 0      | 4 – 1 | Hook up                  |

| -1                           | 0      | 0      | 0             | 0      | 0-1   | only segments            |

| +1 OR                        | 0      | 1      | 1             | 1      | 7 – 1 | b and c to MSD           |

| -1 OR                        | 0      | 0      | 1             | 1      | 3–1   |                          |

TABLE 5-1: TRUTH TABLE

Note 1:  $Q_3 - 1/2$  digit, low for "1", high for "0".  $Q_2$  - Polarity: "1" = positive, "0" = negative.  $Q_0$  - Out of range condition exists if  $Q_0$  = 1. When used in conjunction with  $Q_3$ , the type of out of range condition is indicated; i.e.,  $Q_3$ = 0  $\rightarrow$  OR or  $Q_3$  = 1  $\rightarrow$  UR.

Figure is an example of a 3-1/2 digit LED voltmeter with a minimum of external components, (only 11 additional components). In this circuit, the 14511B provides the segment drive and the 75492 or 1413 provides sink for digit current. Display is blanked during the overrange condition.

3-1/2 Digit LED Voltmeter with Low Component Count Using Common Cathode Display

FIGURE 5-4: Digit Select Timing Diagram

# 6.0 PACKAGING INFORMATION

### 6.1 Package Marking Information

Package marking data not available at this time.

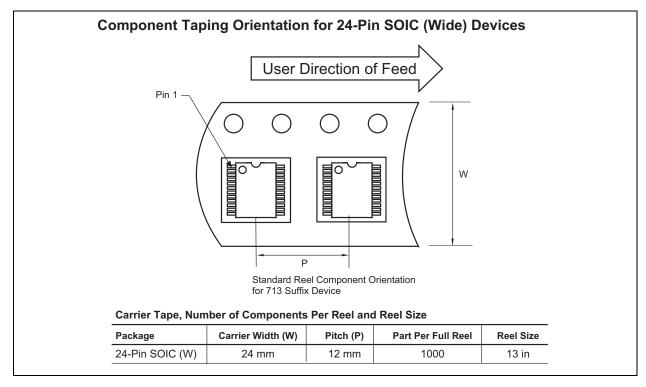

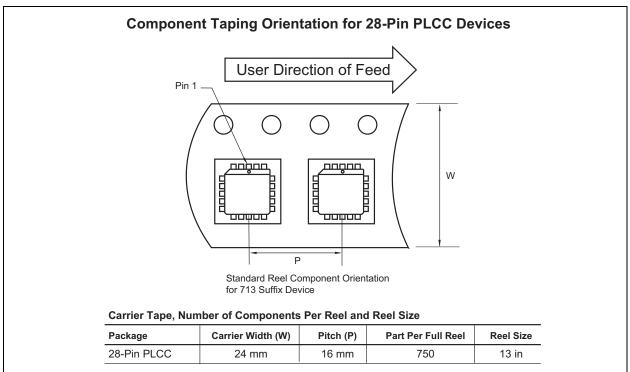

### 6.2 Taping Form

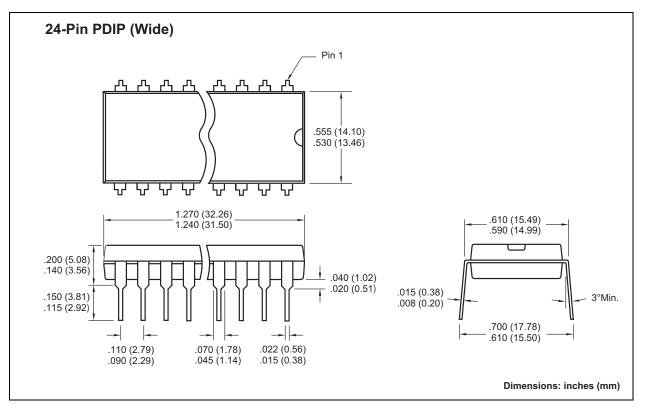

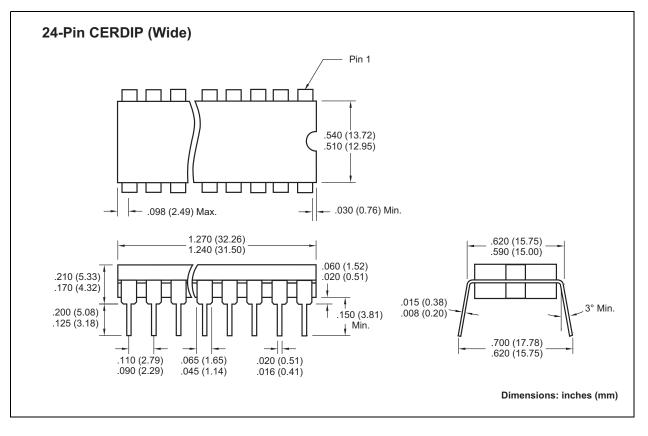

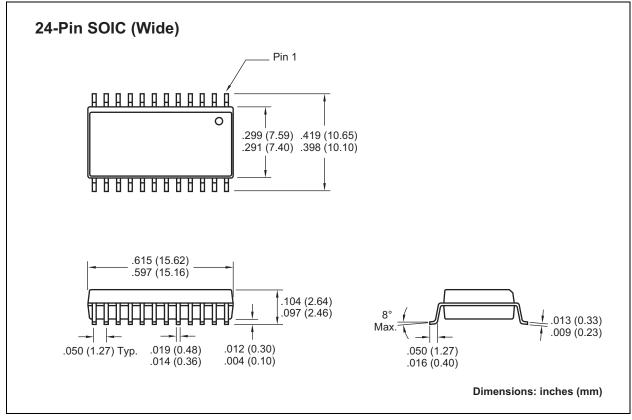

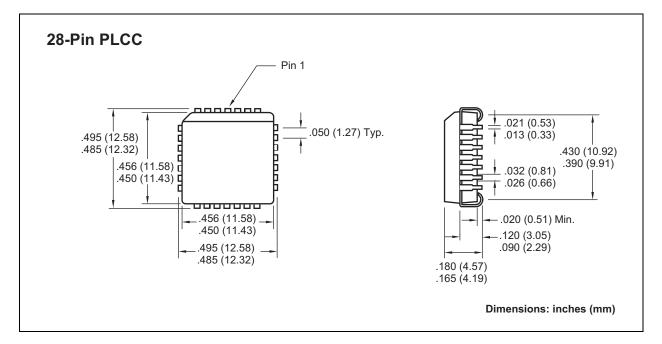

#### 6.3 Package Dimensions

## **Package Dimensions (Continued)**

# SALES AND SUPPORT

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, Real ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and Zena are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**San Jose** Mountain View, CA Tel: 650-215-1444 Fax: 650-961-0286

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8676-6200 Fax: 86-28-8676-6599

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-2229-0061 Fax: 91-80-2229-0062

India - New Delhi Tel: 91-11-5160-8631 Fax: 91-11-5160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Gumi** Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069 Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-399 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820