# **PNX15xx Series Data Book**

Volume 1 of 1 Connected Media Processor

Rev. 3 — 17 March 2006

## **Table of Contents**

## **Chapter 1: Integrated Circuit Data**

| 1.    | Introduction1-1                                           |

|-------|-----------------------------------------------------------|

| 2.    | Pin Description 1-1                                       |

| 2.1   | Boundary Scan Notice1-1                                   |

| 2.2   | I/O Circuit Summary1-1                                    |

| 2.3   | Signal Pin List 1-3                                       |

| 2.3.1 | Power Pin List 1-19                                       |

| 2.3.2 | Pin Reference Voltage 1-20                                |

| 3.    | Absolute Maximum Ratings 1-20                             |

| 4.    | PNX15xx Series Operating Conditions . 1-21                |

| 4.1   | PNX1500 Device                                            |

| 4.2   | PNX1501 Device 1-22                                       |

| 4.3   | PNX1502 Device 1-22                                       |

| 4.4   | PNX1503 Device 1-23                                       |

| 5.    | Power Considerations 1-23                                 |

| 5.1   | Power Supply Sequencing 1-23                              |

| 5.2   | Leakage current Power Consumption 1-24                    |

| 5.3   | Standby Power Consumption                                 |

| 5.4   | Power Consumption                                         |

| 5.4.1 | Typical Power Consumption for Typical<br>Applications1-24 |

| 5.4.2 | Expected Maximum Currents                                 |

| 6.    | DC/AC I/O Characteristics 1-25                            |

| 6.1   | Input Clock Specification1-26                             |

| 6.2   | SSTL_2 type I/O Circuit                                   |

| 6.3   | BPX2T14MCP Type I/O Circuit                               |

| 6.4   | BPTS1CHP and BPTS1CP Type I/O Circuit . 1-29              |

| 6.5   | BPTS3CHP and BPTS3CP Type I/O Circuit. 1-30               |

| 6.6   | IPCHP and IPCP Type I/O Circuit 1-31                      |

| 6.7   | BPT3MCHDT5V and BPT3MCHT5V Type I/O<br>Circuit1-31        |

| 6.8   | IIC3M4SDAT5V and IIC3M4SCLT5V type I/O<br>circuit1-32     |

## **Chapter 2: Overview**

| 1.  | Introduction                            | 6.2  |

|-----|-----------------------------------------|------|

| 1.1 | PNX15xx Series Functional Overview 2-1  | 7.   |

| 1.2 | PNX15xx Series Features Summary 2-3     | 7.1  |

| 2.  | PNX15xx Series Functional Block Diagram | 7.2  |

|     | 2-5                                     | 7.3  |

| 3.  | System Resources                        | 7.4  |

| 3.1 | System Reset 2-6                        | 7.5  |

| 3.2 | System Booting 2-6                      | 7.5. |

| 3.3 | Clock System                            |      |

| 3.4 | Power Management                        | 8.   |

| 3.5 | Semaphores 2-8                          | 8.1  |

| 3.6 | I2C Interface 2-8                       | 8.2  |

| 4.  | System Memory                           | 9.   |

| 4.1 | MMI - Main Memory Interface             | 9.1  |

| 4.2 | Flash 2-9                               | 9.2  |

| 5.  | TM3260 VLIW Media Processor Core 2-10   | 9.3  |

| 6.  | MPEG Decoding2-12                       | 9.4  |

| 6.1 | VLD2-12                                 | 10.  |

| PN | <b>X1</b> | 5xx | Se | ries |

|----|-----------|-----|----|------|

|    |           |     |    |      |

| 6.9    | PCIT5V type I/O circuit                          |

|--------|--------------------------------------------------|

| 7.     | I/O Timing Specification1-32                     |

| 7.1    | Reset                                            |

| 7.2    | DDR DRAM Interface 1-33                          |

| 7.3    | PCI Bus Interface1-34                            |

| 7.4    | QVCP, LCD and FGPO Interfaces 1-36               |

| 7.5    | VIP and FGPI Interfaces1-37                      |

| 7.6    | 10/100 LAN In MII Mode1-38                       |

| 7.7    | 10/100 LAN In RMII Mode1-38                      |

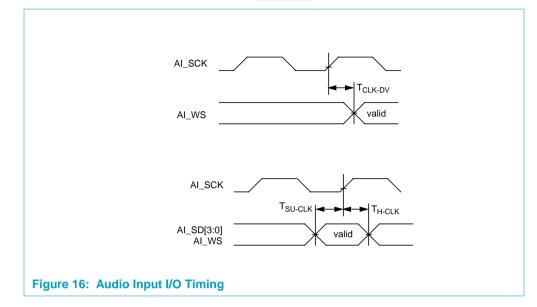

| 7.8    | Audio Input Interface1-39                        |

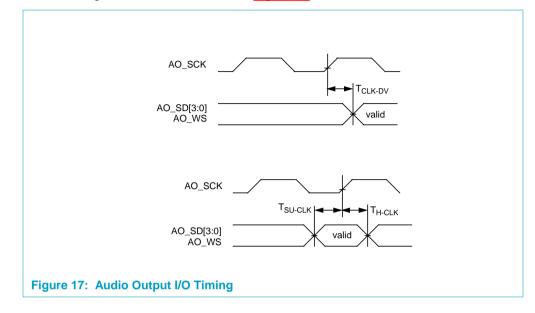

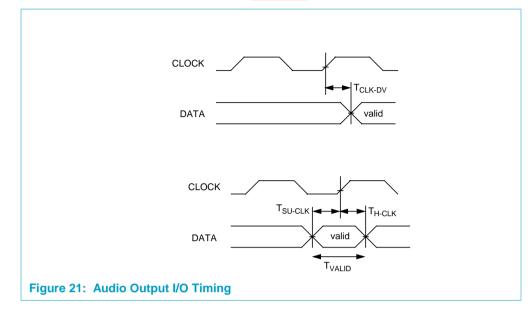

| 7.9    | Audio Output Interface 1-40                      |

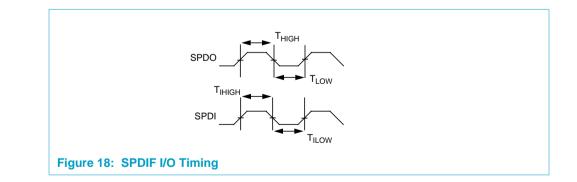

| 7.10   | SPDIF I/O Interface1-41                          |

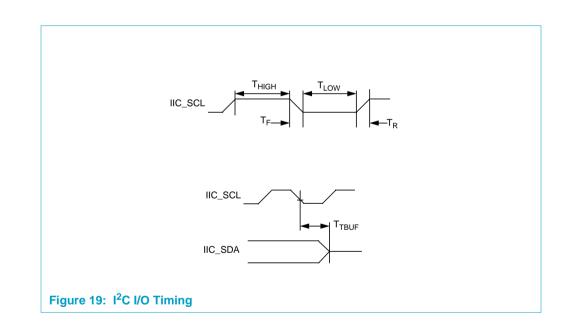

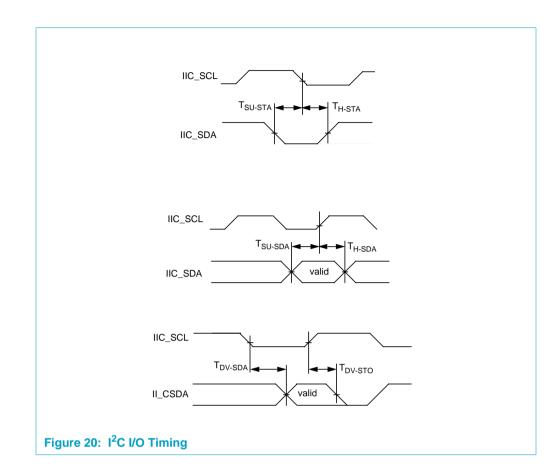

| 7.11   | I2C I/O Interface1-42                            |

| 7.12   | GPIO Interface1-43                               |

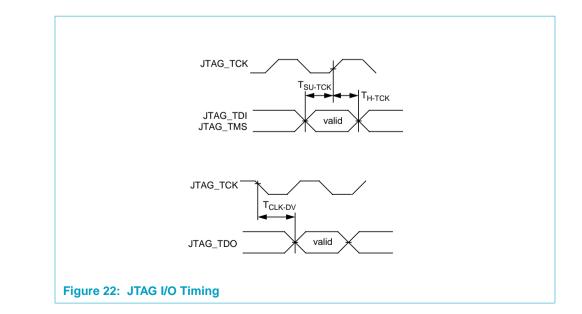

| 7.13   | JTAG Interface1-44                               |

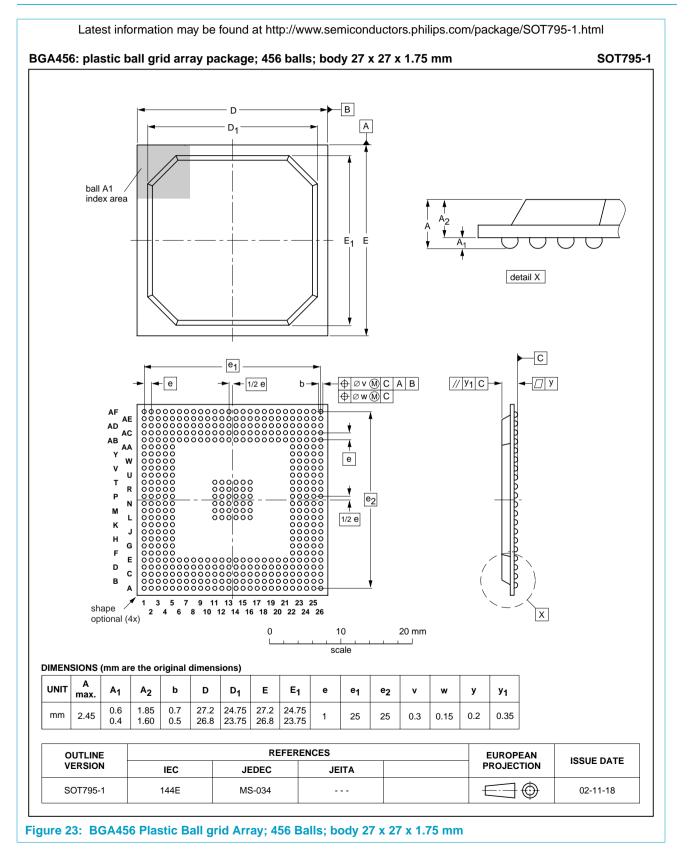

| 8.     | Package Outline1-45                              |

| 9.     | BGA Ball Assignment1-46                          |

| 10.    | Board Design Guidelines1-48                      |

| 10.1   | Power Supplies Decoupling1-48                    |

| 10.2   | Analog Supplies                                  |

| 10.2.1 | The 3.3 V Analog Supply1-49                      |

| 10.2.2 | The SoC Core, VDDA, Analog Supply1-49            |

| 10.3   | DDR SDRAM interface1-50                          |

| 10.3.1 | Do DDR Devices Require Termination? 1-51         |

| 10.3.2 | What if I really want to use termination for the |

|        | PNX1500?1-51                                     |

| 10.4   | Package Handling, Soldering and Thermal          |

|        | Properties1-52                                   |

| 11.    | Miscellaneous1-52                                |

| 12.    | Soft Errors Due to Radiation                     |

| 13.    | Ordering Information1-53                         |

|        |                                                  |

| 6.2                                   | DVD De-scrambler                                                                                                                                                                                             |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.                                    | Image Processing2-12                                                                                                                                                                                         |

| 7.1                                   | Pixel Format2-12                                                                                                                                                                                             |

| 7.2                                   | Video Input Processor2-13                                                                                                                                                                                    |

| 7.3                                   | Memory Based Scaler2-14                                                                                                                                                                                      |

| 7.4                                   | 2D Drawing and DMA Engine2-15                                                                                                                                                                                |

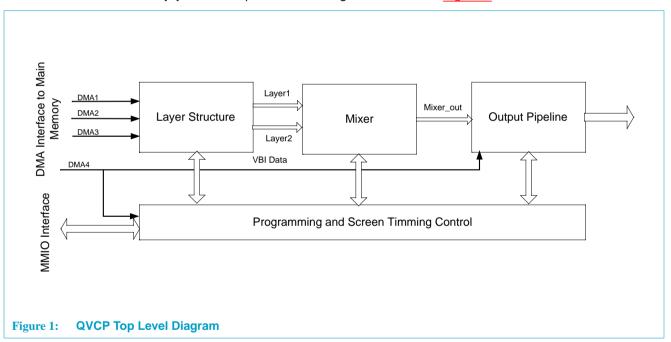

| 7.5                                   | Quality Video Composition Processor2-15                                                                                                                                                                      |

| 7.5.1                                 | External Video Improvement Post Processing .2-                                                                                                                                                               |

|                                       | 16                                                                                                                                                                                                           |

|                                       |                                                                                                                                                                                                              |

| 8.                                    | Audio processing and Input/Output2-17                                                                                                                                                                        |

| <b>8.</b><br>8.1                      | Audio processing and Input/Output2-17<br>Audio Processing2-17                                                                                                                                                |

|                                       |                                                                                                                                                                                                              |

| 8.1                                   | Audio Processing2-17                                                                                                                                                                                         |

| 8.1<br>8.2                            | Audio Processing       2-17         Audio Inputs and Outputs       2-17                                                                                                                                      |

| 8.1<br>8.2<br><b>9.</b>               | Audio Processing       2-17         Audio Inputs and Outputs       2-17         General Purpose Interfaces       2-18                                                                                        |

| 8.1<br>8.2<br><b>9.</b><br>9.1        | Audio Processing       2-17         Audio Inputs and Outputs       2-17         General Purpose Interfaces       2-18         Video/Data Input Router       2-18                                             |

| 8.1<br>8.2<br><b>9.</b><br>9.1<br>9.2 | Audio Processing       2-17         Audio Inputs and Outputs       2-17         General Purpose Interfaces       2-18         Video/Data Input Router       2-18         Video/Data Output Router       2-19 |

| 8.1<br>8.2<br>9.<br>9.1<br>9.2<br>9.3 | Audio Processing2-17Audio Inputs and Outputs2-17General Purpose Interfaces2-18Video/Data Input Router2-18Video/Data Output Router2-19Fast General Purpose Input2-20                                          |

| 10.1   | GPIO - General Purpose Software I/O and         |

|--------|-------------------------------------------------|

|        | Flexible Serial Interface2-21                   |

| 10.1.1 | software I/O                                    |

| 10.1.2 | timestamping2-22                                |

| 10.1.3 | event sequence monitoring and signal generation |

|        | 2-22                                            |

| 10.1.4 | GPIO pin reset value 2-22                       |

| 10.2   | IR Remote Control Receiver and Blaster 2-23     |

|        |                                                 |

### **Chapter 3: System On Chip Resources**

| 1.    | Introduction                                |

|-------|---------------------------------------------|

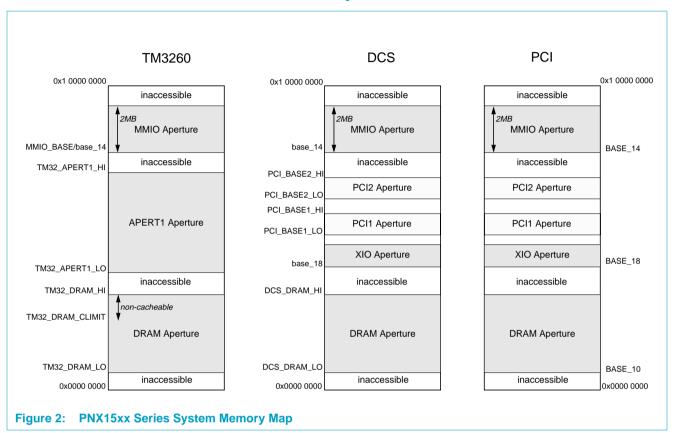

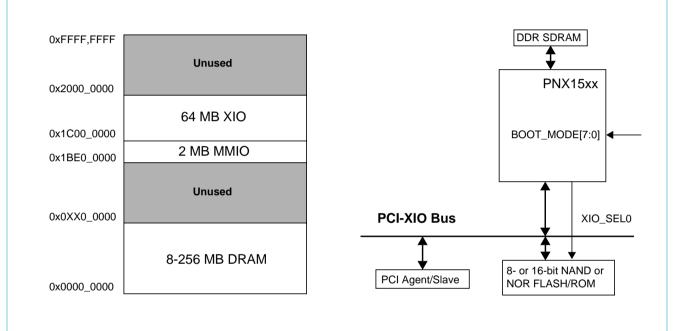

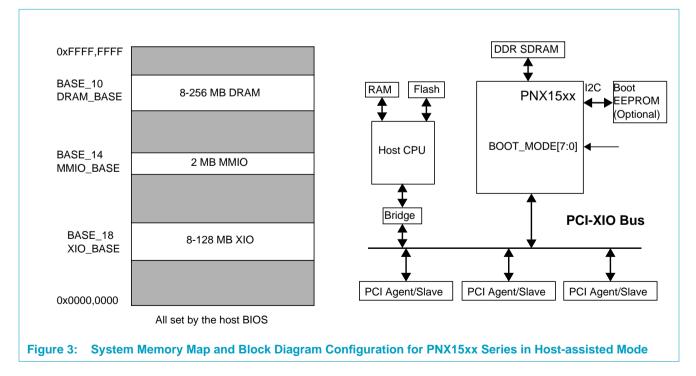

| 2.    | System Memory Map 3-1                       |

| 2.1   | The PCI View                                |

| 2.2   | The CPU View                                |

| 2.3   | The DCS View Or The System View             |

| 2.4   | The Programmable DCS Apertures              |

| 2.4.1 | DCS DRAM Aperture Control MMIO Registers3-6 |

| 2.5   | Aperture Boundaries 3-6                     |

| 3.    | System Principles 3-7                       |

| 3.1   | Module ID                                   |

| 3.2   | Powerdown bit                               |

| 3.3   | System Module MMIO registers                |

| 4.    | System Endian Mode                          |

| 4.1   | System Endian Mode MMIO registers 3-9       |

| 5.    | System Semaphores 3-9                       |

| 5.1   | Semaphore Specification                     |

| 5.2   | Construction of a 12-bit ID                 |

| 5.3   | The Master Semaphore                        |

### **Chapter 4: Reset**

| 1.           | Introduction4-1                                           | 2.4 | The External Software Reset4-6 |

|--------------|-----------------------------------------------------------|-----|--------------------------------|

| 2.           | Functional Description 4-1                                | 3.  | Timing Description4-7          |

| 2.1          | RESET_IN_N or POR_IN_N? 4-3                               | 3.1 | The Hardware Timing4-7         |

| 2.2          | The watchdog Timer 4-4                                    | 3.2 | The Software Timing4-8         |

| 2.2.1        | The Non Interrupt Mode 4-4                                | 4.  | Register Definitions4-9        |

| 2.2.2<br>2.3 | The Interrupt Mode.    4-5      The Software Reset    4-6 | 5.  | References                     |

### **Chapter 5: The Clock Module**

| 1.    | Introduction                        | 2.8.1  | Wake-Up from Power Down5-17                      |

|-------|-------------------------------------|--------|--------------------------------------------------|

| 2.    | Functional Description              | 2.9    | Clock Detection5-18                              |

| 2.1   | The Modules and their Clocks        | 2.10   | VDO Clocks                                       |

| 2.2   | Clock Sources for PNX15xx Series    | 2.11   | GPIO Clocks5-20                                  |

| 2.2.1 | PLL Specification                   | 2.11.1 | Setting GPIO[14:12]/GCLOCK[2:0] as Clock         |

| 2.2.2 | The Clock Dividers 5-10             |        | Outputs5-20                                      |

| 2.2.3 | The DDS Clocks 5-11                 | 2.11.2 | GPIO[6:4]/CLOCK[6:4] as Clock Outputs5-20        |

| 2.2.4 | DDS and PLL Assignment Summary 5-11 | 2.12   | Clock Block Diagrams5-20                         |

| 2.2.5 | External Clocks                     | 2.12.1 | TM3260, DDR and QVCP clocks                      |

| 2.3   | Clock Control Logic 5-13            | 2.12.2 | Clock Dividers5-23                               |

| 2.4   | Bypass Clock Sources                | 2.12.3 | Internal PNX15xx Series Clock from Dividers 5-24 |

| 2.5   | Power-up and Reset sequence         | 2.12.4 | GPIO Clocks5-26                                  |

| 2.6   | Clock Stretching                    | 2.12.5 | External Clocks5-27                              |

| 2.7   | Clock Frequency Determination       | 2.12.6 | SPDO5-31                                         |

| 2.8   | Power Down                          | 3.     | Registers Definition                             |

| 10.3   | PCI-2.2 & XIO-16 Bus Interface Unit2-23         |

|--------|-------------------------------------------------|

| 10.3.1 | PCI Capabilities2-23                            |

| 10.3.2 | Simple Peripheral Capabilities ('XIO-8/16')2-24 |

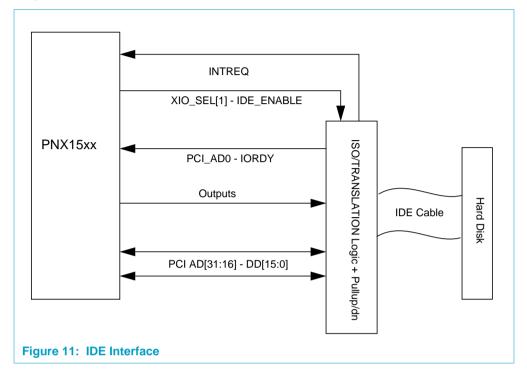

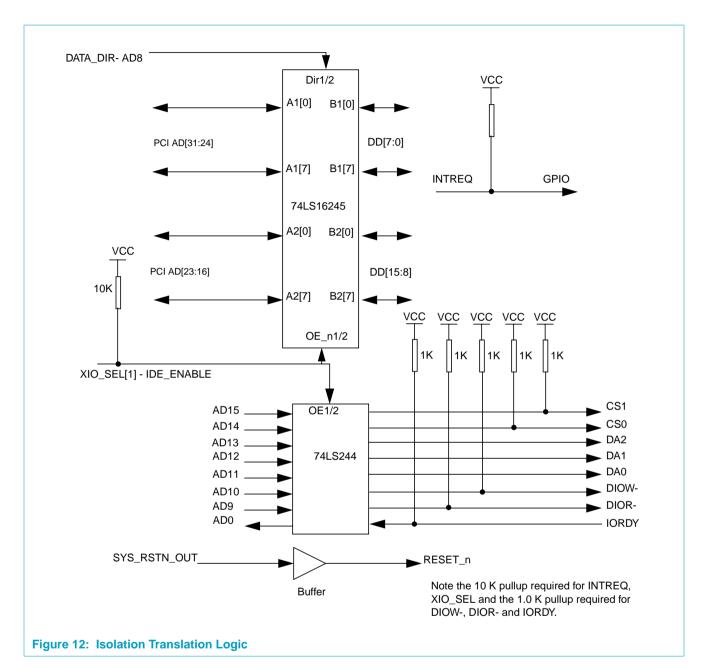

| 10.3.3 | IDE Drive Interface2-26                         |

| 10.4   | 10/100 Ethernet MAC2-26                         |

| 11.    | Endian Modes2-26                                |

| 12.    | System Debug2-27                                |

| 5.4   | Usage Notes                                    |

|-------|------------------------------------------------|

| 5.5   | Semaphore MMIO Registers                       |

| 6.    | System Related Information for TM32603-12      |

| 6.1   | Interrupts                                     |

| 6.2   | Timers                                         |

| 6.3   | System Parameters for TM3260                   |

| 6.3.1 | TM3260 System Parameters MMIO Registers . 3-   |

|       | 16                                             |

| 7.    | Video Input and Output Routers3-16             |

| 7.1   | MMIO Registers for the Input/Output Video/Data |

|       | Router3-17                                     |

| 8.    | Miscellaneous                                  |

| 8.1   | Miscellaneous System MMIO registers3-27        |

| 9.    | System Registers Map Summary3-29               |

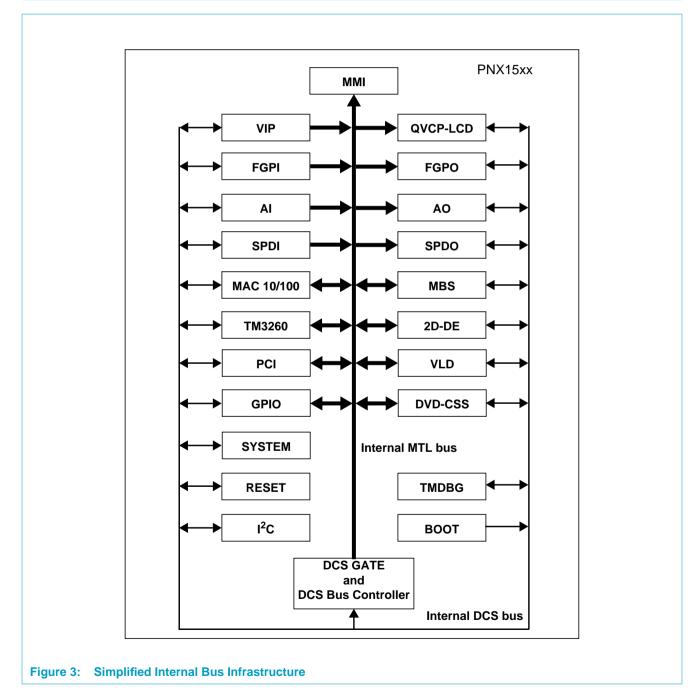

| 10.   | Simplified Internal Bus Infrastructure3-30     |

| 11.   | MMIO Memory MAP                                |

| 12.   | References                                     |

|       |                                                |

## **Philips Semiconductors**

### Volume 1 of 1

### **Chapter 6: Boot Module**

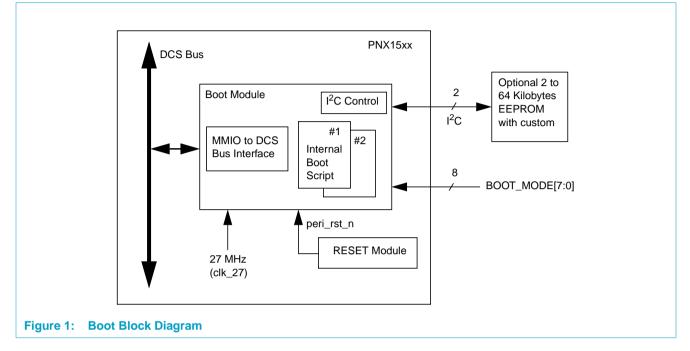

| 1.    | Introduction6-1                                |

|-------|------------------------------------------------|

| 2.    | Functional Description6-1                      |

| 2.1   | The Boot Modes 6-2                             |

| 2.2   | Boot Module Operation 6-4                      |

| 2.2.1 | MMIO Bus Interface 6-4                         |

| 2.2.2 | I2C Master 6-4                                 |

| 2.2.3 | Boot Control/State Machine 6-5                 |

| 2.3   | The Boot Command Language                      |

| 3.    | PNX15xx Series Boot Scripts Content 6-6        |

| 3.1   | The Common Behavior                            |

| 3.1.1 | Binary Sequence for the Common Boot Script 6-9 |

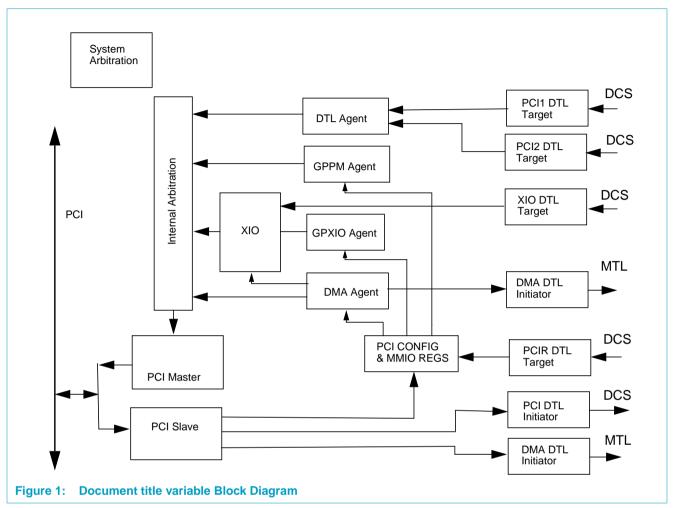

### **Chapter 7: PCI-XIO Module**

| 1.    | Introduction                                      | 4      |

|-------|---------------------------------------------------|--------|

| 2.    | Functional Description7-2                         | 4      |

| 2.1   | Document title variable Block Level Diagram . 7-3 | 4      |

| 2.2   | Architecture                                      | 4      |

| 3.    | <b>Operation</b>                                  | 4      |

| 3.1   | Overview                                          | 4<br>4 |

| 3.1.1 | NAND-Flash Interface Operation                    | 4      |

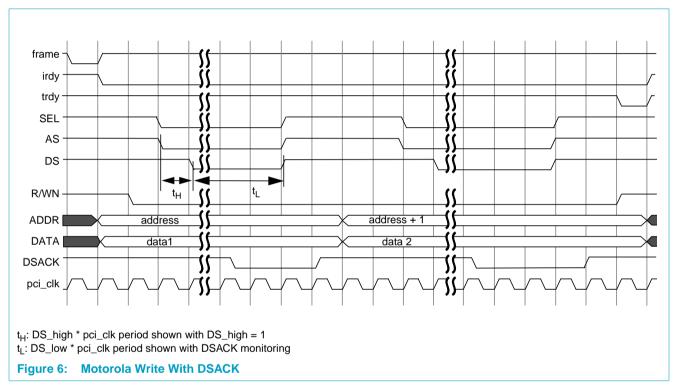

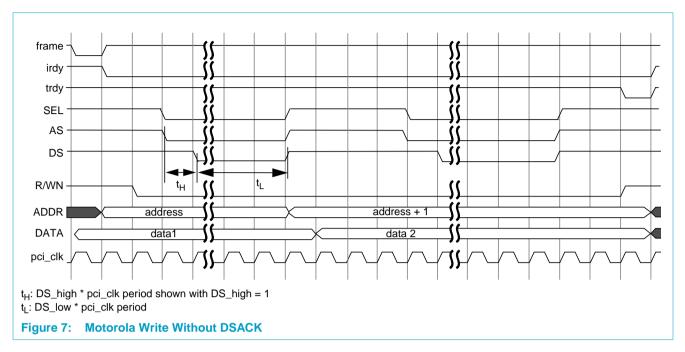

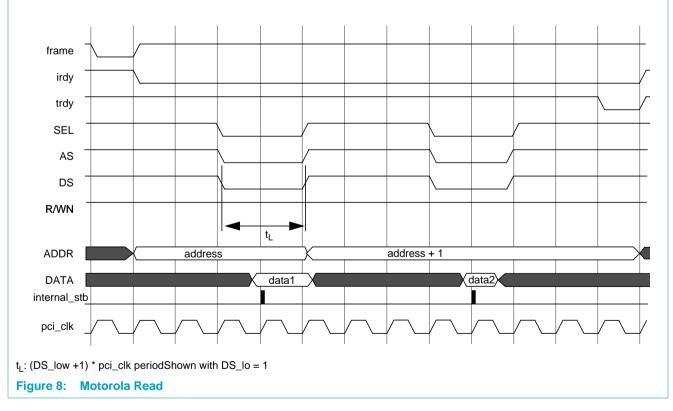

| 3.1.2 | Motorola Style Interface                          | 4      |

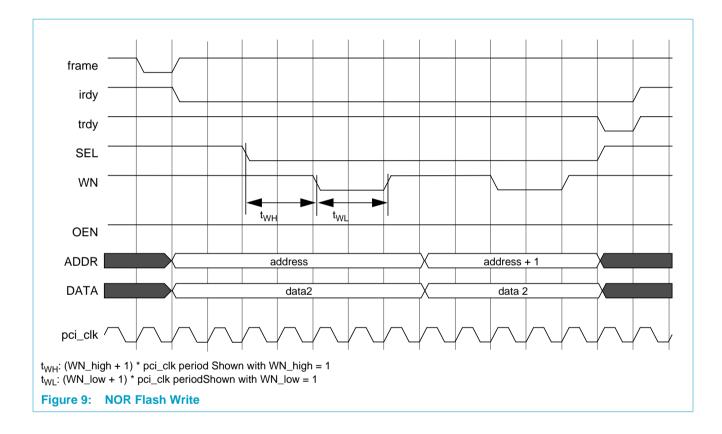

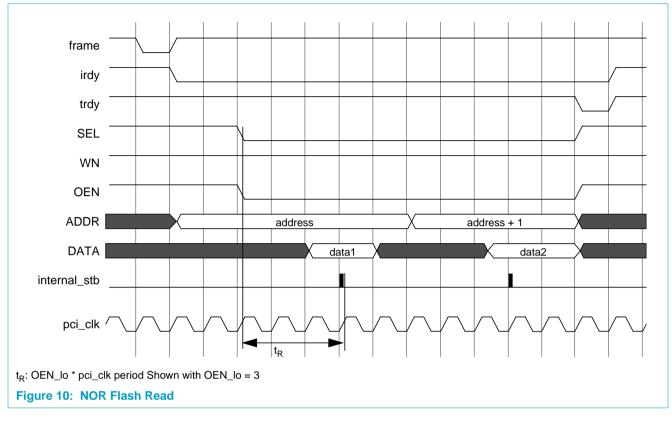

| 3.1.3 | NOR Flash Interface 7-12                          | 4      |

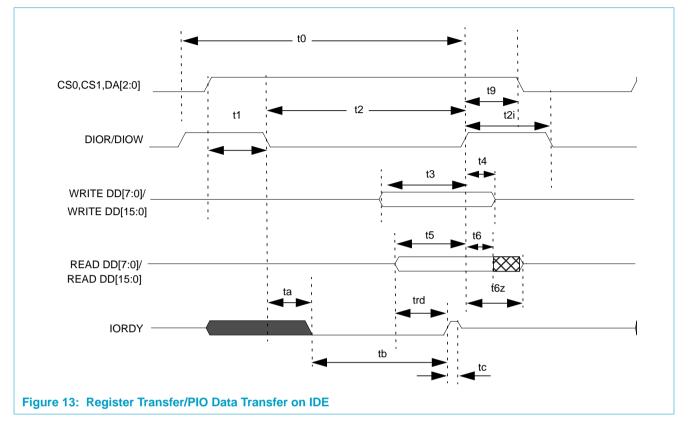

| 3.1.4 | IDE Description7-13                               | -      |

| 3.2   | PCI Interrupt Enable Register                     | 5      |

### **Chapter 8: General Purpose Input Output Pins**

| 1.    | Introduction8-1                         | 3.1  |

|-------|-----------------------------------------|------|

| 2.    | Functional Description8-2               | 3.2  |

| 2.1   | GPIO: The Basic Pin Behavior8-2         | 4.   |

| 2.1.1 | GPIO Mode settings8-4                   | 4.1  |

| 2.1.2 | GPIO Data Settings MMIO Registers 8-4   | 4.2  |

| 2.1.3 | GPIO Pin Status Reading 8-6             | 4.3  |

| 2.2   | GPIO: The Event Monitoring Mode         | 4.4  |

| 2.2.1 | Timestamp Reference clock               |      |

| 2.2.2 | Timestamp format 8-7                    | 4.5  |

| 2.3   | GPIO: The Signal Monitoring & Pattern   |      |

|       | Generation Modes8-7                     | 4.6  |

| 2.3.1 | The Signal Monitoring Mode 8-8          | 4.7  |

| 2.3.2 | The Signal Pattern Generation Mode 8-11 | 4.8  |

| 2.4   | GPIO Error Behaviour                    | 4.9  |

| 2.4.1 | GPIO Frequency Restrictions 8-15        | 4.10 |

| 2.5   | The GPIO Clock Pins                     | 4.11 |

| 2.6   | GPIO Interrupts8-17                     |      |

| 2.7   | Timer Sources8-18                       | 4.12 |

| 2.8   | Wake-up Interrupt8-18                   |      |

| 2.9   | External Watchdog8-18                   | 4.13 |

| 3.    | IR Applications                         | 4.14 |

| -     | FF                                      | 4.15 |

| 3.2   | Registers Description5-34                                 |

|-------|-----------------------------------------------------------|

|       |                                                           |

| 3.2   | The Specifics of the Boot From Flash Memory Devices6-10   |

| 3.2.1 | Binary Sequence for the Section of the Flash Boot<br>6-12 |

| 3.3   | The Specifics of the Host-Assisted Mode 6-12              |

| 4.    | The Boot From an I2C EEPROM6-14                           |

| 4.1   | External I2C Boot EEPROM Types6-14                        |

| 4.2   | The Boot Commands and The Endian Mode. 6-15               |

| 4.    | Application Notes                             |

|-------|-----------------------------------------------|

| 4.1   | DTL Interface                                 |

| 4.2   | System Memory Bus Interface, the MTL Bus 7-19 |

| 4.3   | XIO Interface                                 |

| 4.3.1 | Motorola Interface                            |

| 4.3.2 | NAND-Flash Interface                          |

| 4.3.3 | NOR Flash Interface7-20                       |

| 4.3.4 | IDE Interface                                 |

| 4.4   | PCI Endian Support7-21                        |

| 4.5   | General Notes7-21                             |

| 5.    | Register Descriptions7-21                     |

| 5.1   | Register Summary7-22                          |

|   | Duty-cycle programming8-19                        |

|---|---------------------------------------------------|

| 2 | Spike Filtering8-20                               |

|   | MMIO Registers8-21                                |

|   | GPIO Mode Control Registers8-24                   |

| 2 | GPIO Data Control8-26                             |

| 3 | Readable Internal PNX15xx Series Signals8-26      |

| ŀ | Sampling and Pattern Generation Control           |

|   | Registers for the FIFO Queues8-27                 |

| 5 | Signal and Event Monitoring Control Registers for |

|   | the Timestamp Units8-34                           |

| 6 | Timestamp Unit Registers                          |

| , | GPIO Time Counter8-34                             |

| 3 | GPIO TM3260 Timer Input Select8-35                |

| ) | GPIO Interrupt Status8-35                         |

| 0 | Clock Out Select8-36                              |

| 1 | GPIO Interrupt Registers for the FIFO Queues      |

|   | (One for each FIFO Queue)8-37                     |

| 2 | GPIO Module Status Register for all 12            |

|   | Timestamp Units8-38                               |

| 3 | GPIO POWERDOWN8-43                                |

| 4 | GPIO Module ID8-43                                |

| 5 | GPIO IO_SEL Selection Values                      |

|   |                                                   |

4.3

5.

# PNX15xx Series

## **Chapter 9: DDR Controller**

| 1.    | Introduction                                    |

|-------|-------------------------------------------------|

| 2.    | Functional Description                          |

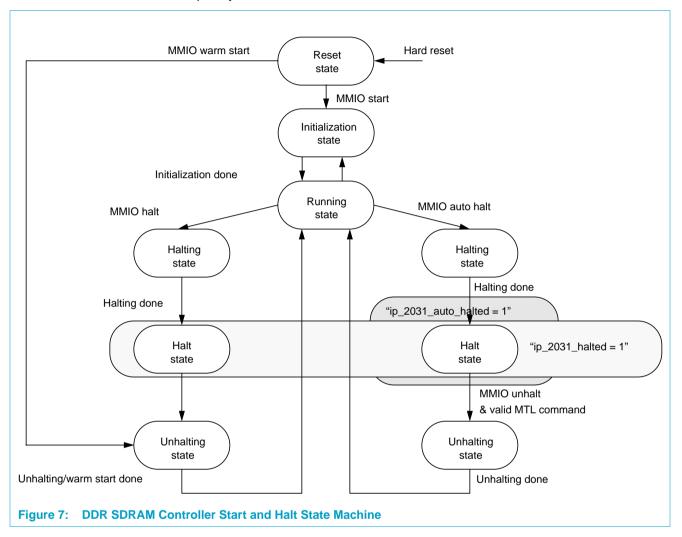

| 2.1   | Start and Warm Start 9-2                        |

| 2.1.1 | The Start Mode 9-2                              |

| 2.1.2 | Warm Start                                      |

| 2.1.3 | Observing Start State 9-3                       |

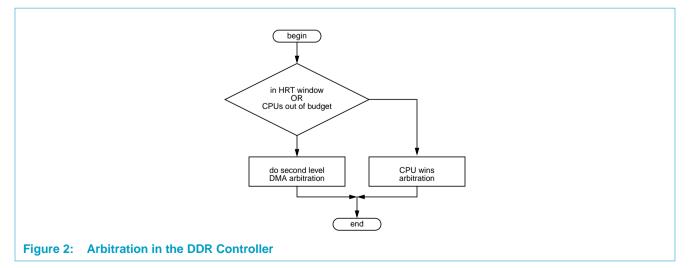

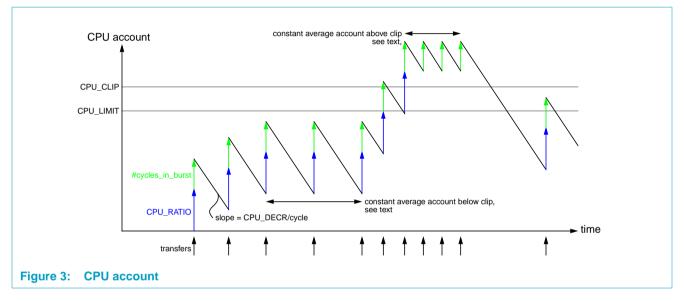

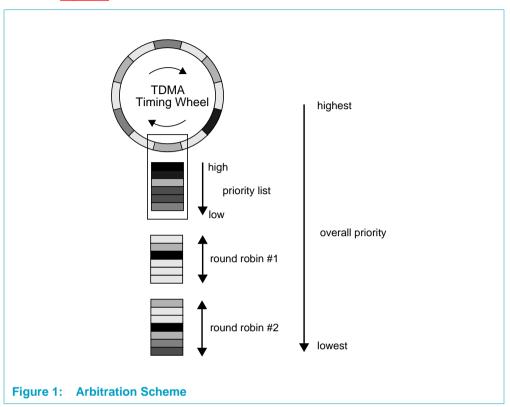

| 2.2   | Arbitration9-3                                  |

| 2.2.1 | The First Level of Arbitration: Between the DMA |

|       | and the CPU9-3                                  |

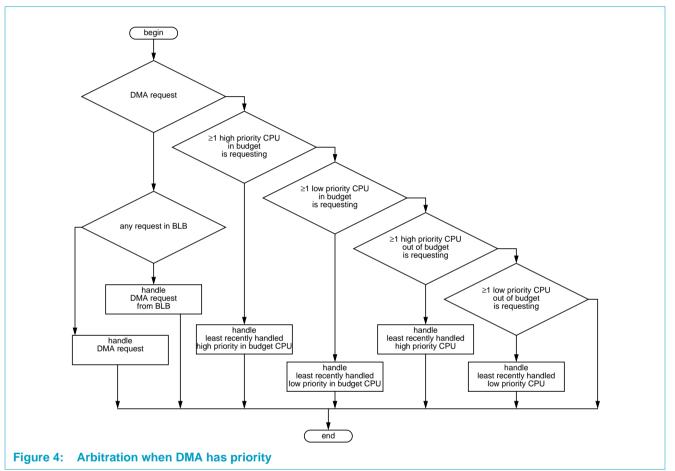

| 2.2.2 | Second Level of Arbitration 9-6                 |

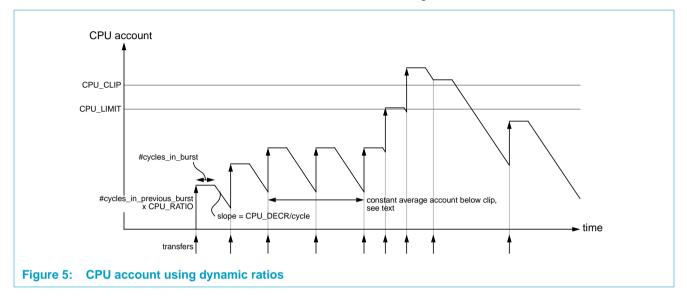

| 2.2.3 | Dynamic Ratios                                  |

| 2.2.4 | Pre-Emption                                     |

| 2.2.5 | Back Log Buffer (BLB)                           |

| 2.2.6 | PMAN (Hub) versus DDR Controller Interaction 9- |

|       | 9                                               |

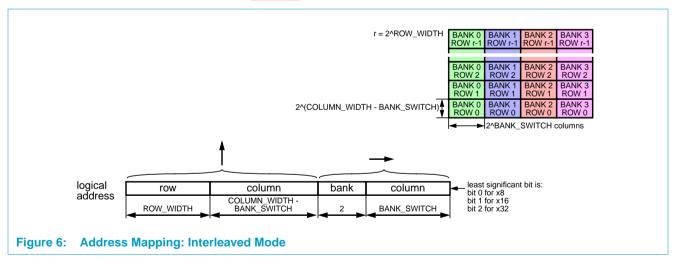

| 2.3   | Addressing                                      |

| 2.3.1 | Memory Region Mapping Scheme                    |

| 2.3.2 | DDR Memory Rank Locations                       |

| 2.4   | Clock Programming 9-13                          |

| 2.5   | Power Management                                |

| 2.5.1 | Halting and Unhalting                           |

| 2.5.2 | MMIO Directed Halt 9-14                         |

| 2.5.3 | Auto Halt                                       |

| 2.5.4 | Observing Halt Mode                             |

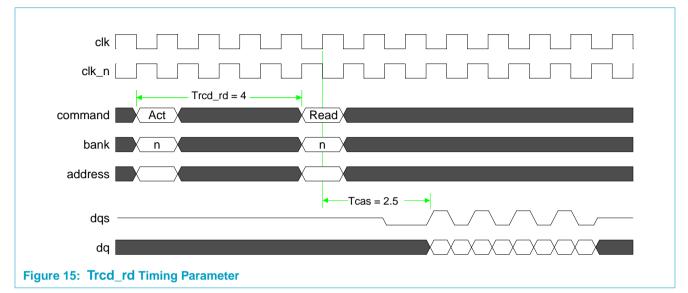

## **Chapter 10: LCD Controller**

| 1.  | Introduction                        | 3.2 |

|-----|-------------------------------------|-----|

| 1.1 | LCD Controller Features 10-1        | 3.2 |

| 2.  | Functional Description 10-1         | 3.2 |

| 2.1 | Overview 10-1                       | 3.2 |

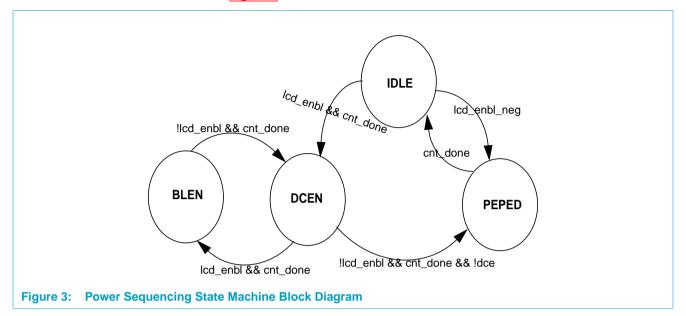

| 2.2 | Power Sequencing 10-2               | 3.3 |

| 3.  | <b>Operation</b> 10-3               | 3.4 |

| 3.1 | Overview 10-3                       | 4.  |

| 3.2 | Power Sequencing State Machine 10-3 | 4.1 |

## Chapter 11: QVCP

| 1.    | Introduction11-1                             |  |

|-------|----------------------------------------------|--|

| 1.1   | Features 11-2                                |  |

| 2.    | Functional Description                       |  |

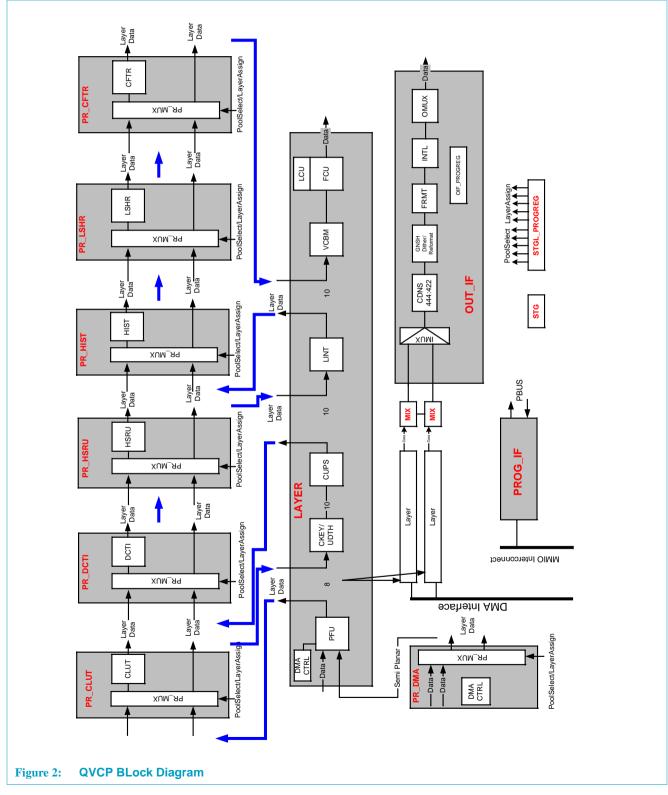

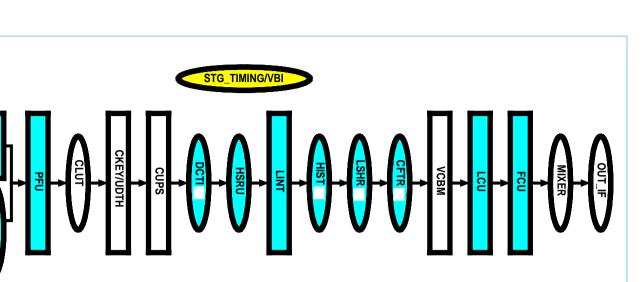

| 2.1   | QVCP Block Diagram 11-4                      |  |

| 2.2   | Architecture 11-5                            |  |

| 2.3   | Layer Resources and Functions 11-6           |  |

| 2.3.1 | Memory Access Control (DMA CTRL) 11-6        |  |

| 2.3.2 | Pixel Formatter Unit (PFU) 11-7              |  |

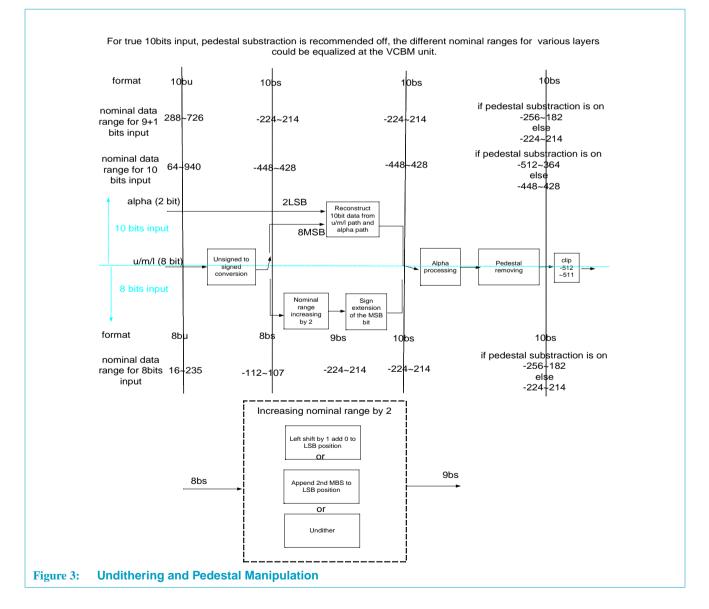

| 2.3.3 | Chroma Key and Undither (CKEY/UDTH) Unit 11- |  |

|       | 7                                            |  |

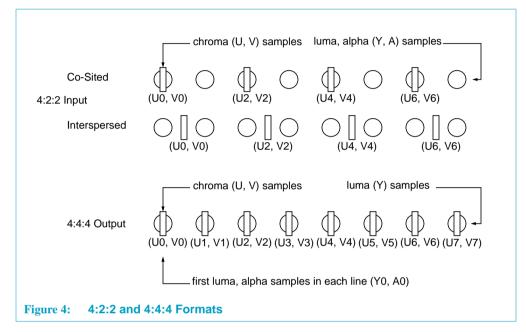

| 2.3.4 | Chroma Upsample Filter (CUPS) 11-11          |  |

| 2.3.5 | Linear Interpolator (LINT) 11-11             |  |

| 2.3.6 | Video/Graphics Contrast Brightness Matrix    |  |

|       | (VCBM)11-11                                  |  |

| 2.3.7 | Layer and Fetch Control 11-12                |  |

| 2.4   | Pool Resources and Functions 11-13           |  |

| 2.4.1 | CLUT (Color Look Up Table) 11-13             |  |

|       |                                              |  |

| 2.5.5 | Sequence of Actions                   |

|-------|---------------------------------------|

| 3.    | Application Notes                     |

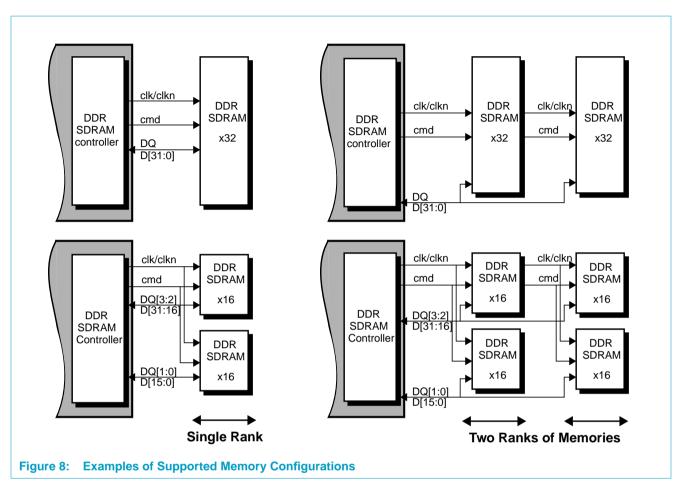

| 3.1   | Memory Configurations                 |

| 3.2   | Error Signaling9-17                   |

| 3.3   | Latency                               |

| 3.4   | Data Coherency9-18                    |

| 3.5   | Programming the Internal Arbiter      |

| 3.6   | The DDR Controller and the DDR Memory |

|       | Devices9-20                           |

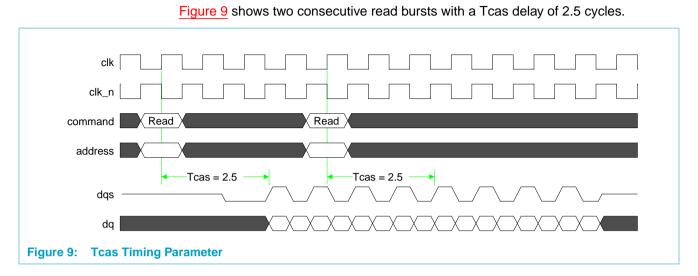

| 4.    | Timing Diagrams and Tables9-20        |

| 4.0.1 | Tcas Timing Parameter                 |

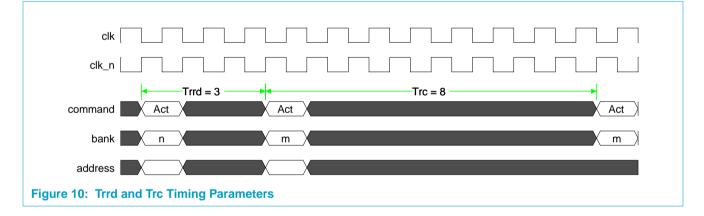

| 4.1   | Trrd and Trc Timing Parameters        |

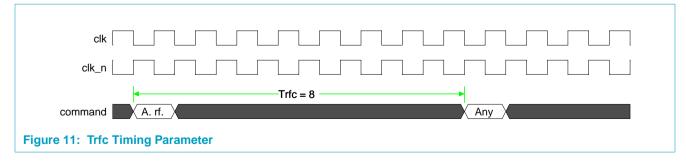

| 4.2   | Trfc Timing Parameter9-21             |

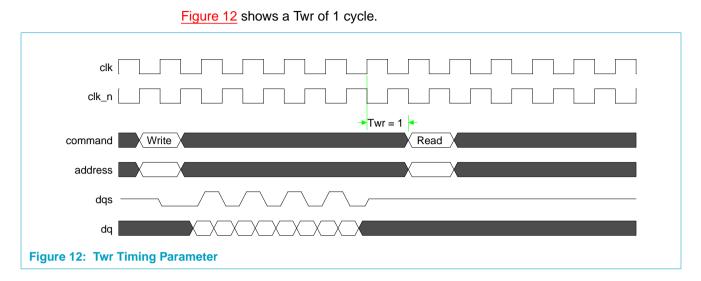

| 4.3   | Twr Timing Parameter9-22              |

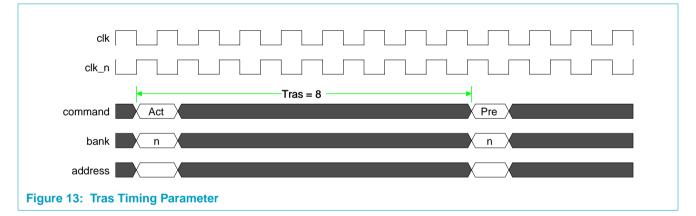

| 4.4   | Tras Timing Parameter                 |

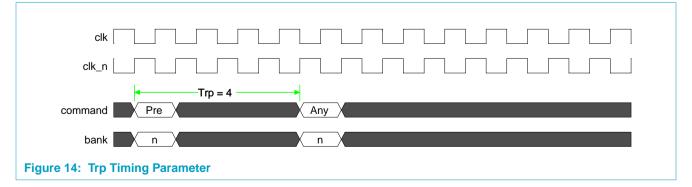

| 4.5   | Trp Timing Parameter                  |

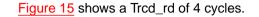

| 4.6   | Trcd_rd Timing Parameter              |

| 4.7   | Trcd_wr Timing Parameter              |

| 5.    | Register Descriptions                 |

| 5.1   | Register Summary9-24                  |

| 5.2   | Register Table9-25                    |

| 6.    | <b>References</b>                     |

| .2.1 | IDLE state10-4            |

|------|---------------------------|

| .2.2 | DCEN state10-4            |

| .2.3 | BLEN state 10-5           |

| .2.4 | PEPED state10-5           |

| .3   | Counter 10-5              |

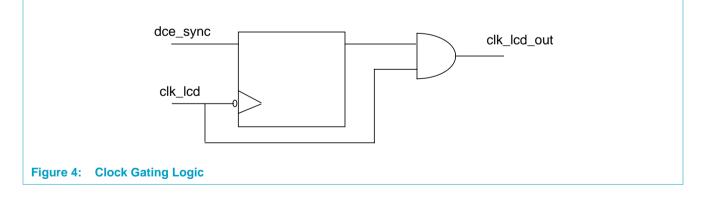

| .4   | Gating Logic 10-5         |

|      | Register Descriptions10-6 |

| .1   | LCD MMIO Registers 10-7   |

|      |                           |

| 2.4.2 | DCTI (Digital Chroma/Color Transient<br>Improvement)11-13 |

|-------|-----------------------------------------------------------|

| 2.4.3 | HSRU (Horizontal Sample Rate Upconverter). 11-<br>13      |

| 2.4.4 | HIST (Histogram Modification) Unit                        |

| 2.4.5 | LSHR (Luminance/Luma Sharpening) Unit . 11-14             |

| 2.4.6 | Color Features (CFTR) Unit                                |

| 2.4.7 | PLAN (Semi Planar DMA) Unit11-15                          |

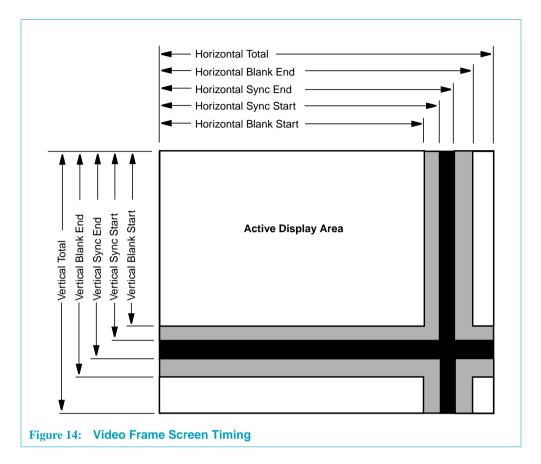

| 2.5   | Screen Timing Generator                                   |

| 2.6   | Mixer Structure11-16                                      |

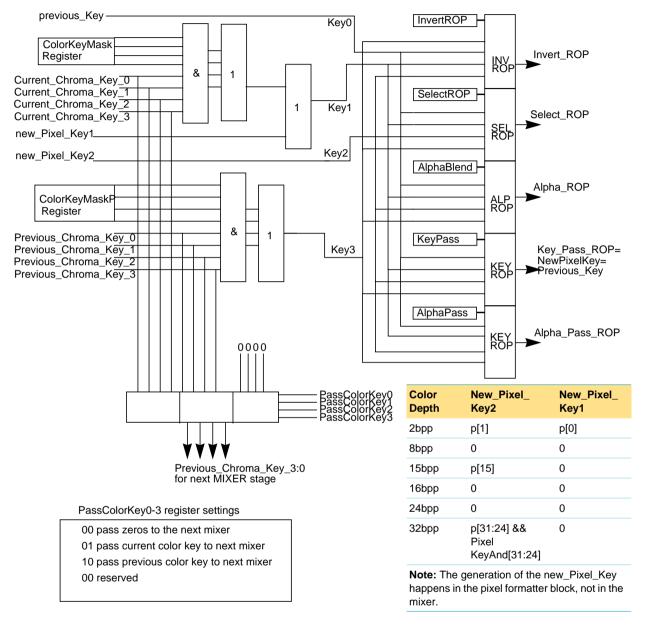

| 2.6.1 | Key Generation11-18                                       |

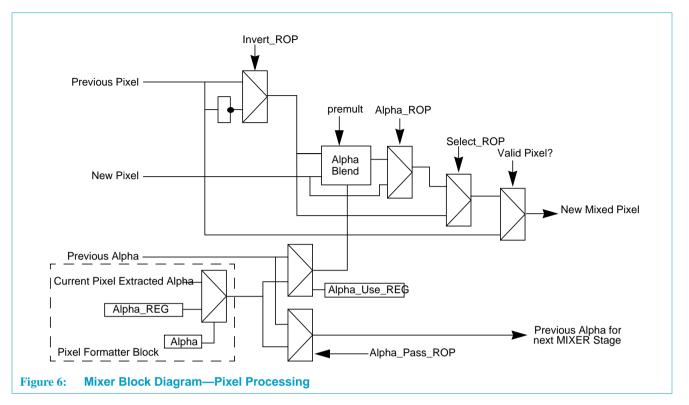

| 2.6.2 | Alpha Blending11-19                                       |

| 2.7   | Output Pipeline Structure                                 |

| 2.7.1 | Supported Output Formats11-20                             |

| 2.7.2 | Layer Selection11-20                                      |

| 2.7.3 | Chrominance Downsampling (CDNS)11-20                      |

| 2.7.4 | Gamma Correction and Noise Shaping (GNSH& ONSH)11-20      |

| 2.7.5<br>2.7.6 | Output Interface Modes                        |

|----------------|-----------------------------------------------|

| 3.             | Programming and Resource Assignment           |

|                | 11-23                                         |

| 3.1            | MMIO and Task Based Programming 11-23         |

| 3.2            | Setup Order for the QVCP 11-24                |

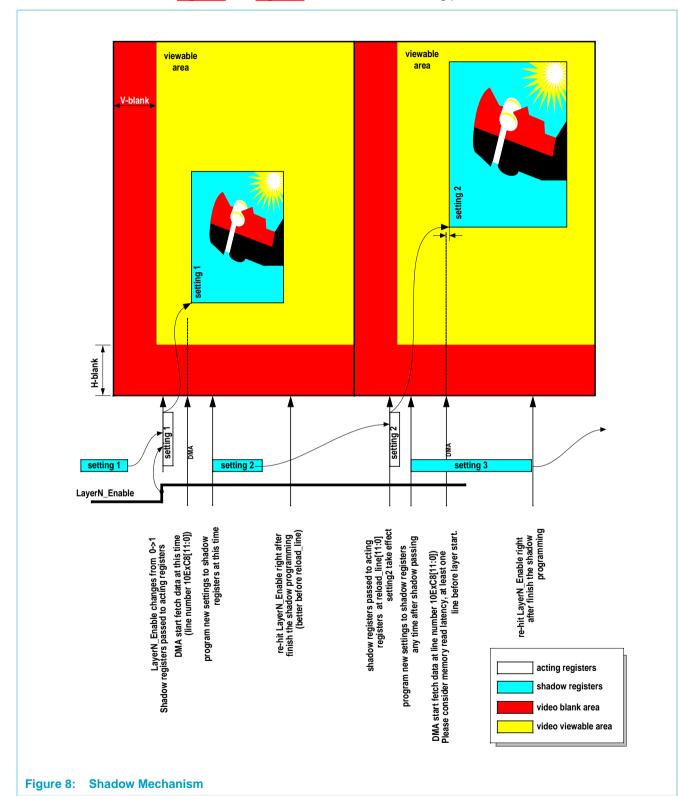

| 3.2.1          | Shadow Registers 11-25                        |

| 3.2.2          | Fast Access Registers 11-29                   |

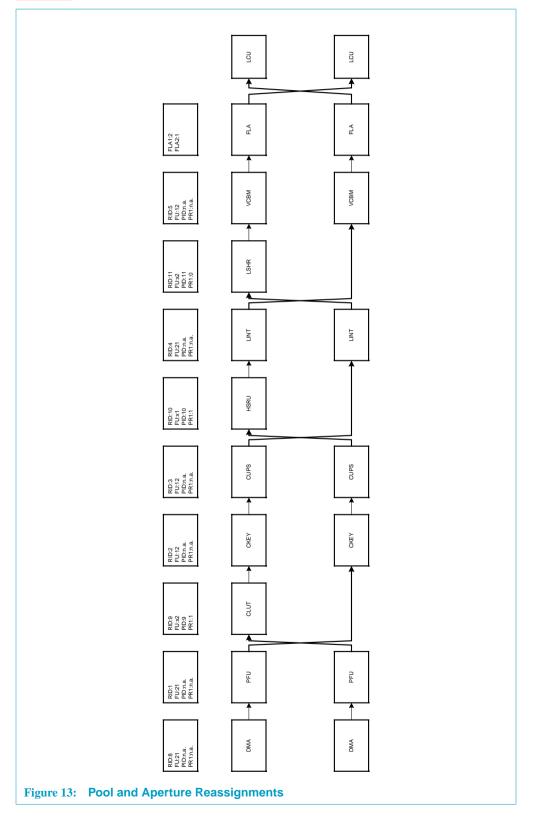

| 3.3            | Programming of Layer and Pool Resources 11-30 |

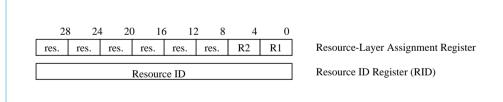

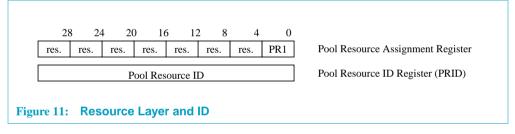

| 3.3.1          | Resource Assignment and Selection 11-30       |

| 3.3.2          | Aperture Assignment 11-30                     |

| 3.3.3          | Data Flow Selection 11-32                     |

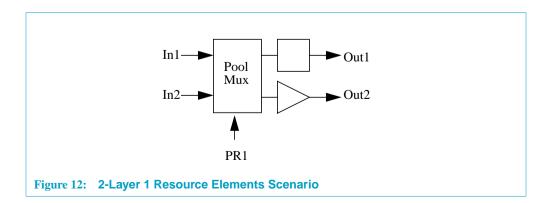

| 3.3.4          | Pool Resource Assignment Example 11-34        |

| 3.4            | Programming the STG 11-35                     |

| 3.4.1          | Changing Timing 11-36                         |

| 3.5            | Programming QVCP for Different Output Formats |

|                | 11-36                                         |

| 4.             | Application Notes11-37                        |

## **Chapter 12: Video Input Processor**

| 1.    | Introduction12-1                  | 2.5.2 |

|-------|-----------------------------------|-------|

| 1.1   | Features 12-1                     | 2.5.3 |

| 2.    | Functional Description 12-2       | 2.5.4 |

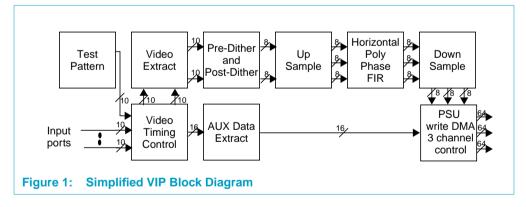

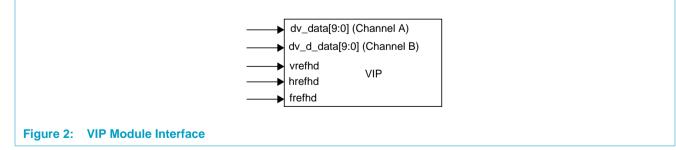

| 2.1   | VIP Block Level Diagram 12-2      | 2.5.5 |

| 2.2   | Chip I/O and Connections 12-3     | 0.5   |

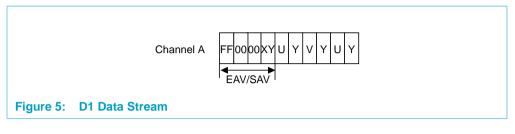

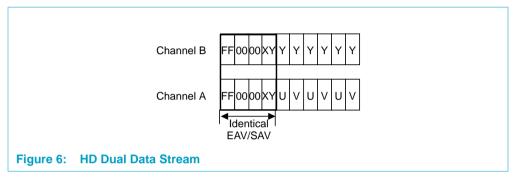

| 2.2.1 | Data Routing and Video Modes 12-3 | 2.5.6 |

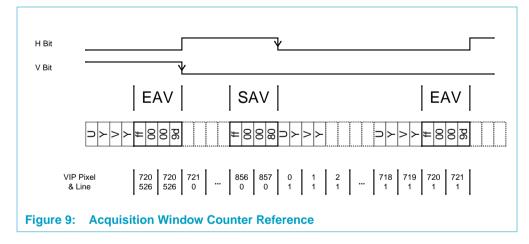

| 2.2.2 | Input Timing 12-4                 | 2.5.7 |

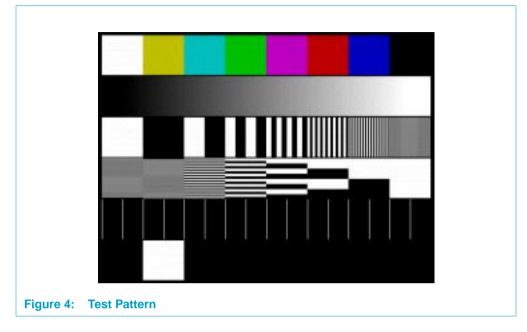

| 2.3   | Test Pattern Generator 12-4       | 2.5.8 |

| 2.4   | Input Formats 12-5                | 3.    |

| 2.5   | Video Data Path 12-8              | 3.1   |

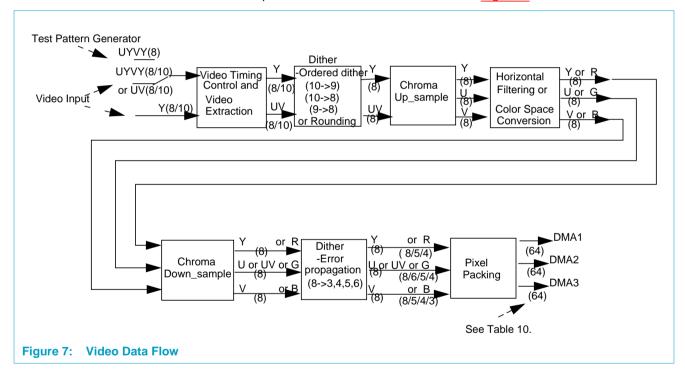

| 2.5.1 | Video Data Flow 12-8              | 3.2   |

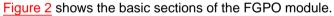

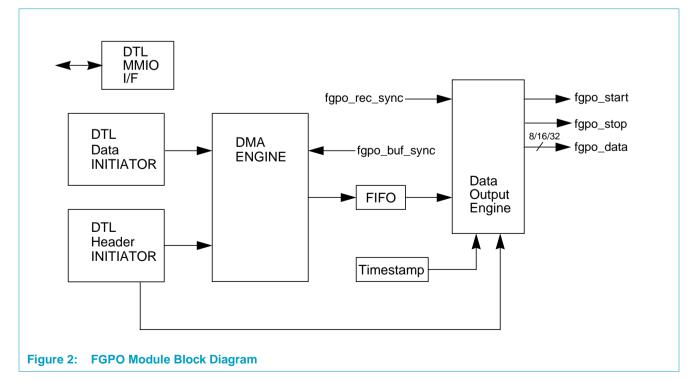

### Chapter 13: FGPO: Fast General Purpose Output

| 1.    | Introduction                          | 2.8   |

|-------|---------------------------------------|-------|

| 1.1   | FGPO Overview 13-2                    | 2.9   |

| 1.2   | FGPO to VDO pin mapping 13-3          | 2.10  |

| 1.3   | DTL MMIO Interface 13-3               | 2.11  |

| 1.4   | Header Initiator 13-3                 | 2.12  |

| 1.5   | Data Initiator                        | 2.13  |

| 1.6   | Record Output Mode 13-3               | 3.    |

| 1.7   | Message Passing Mode 13-4             | 3.1   |

| 2.    | Functional Description                | 3.1.1 |

| 2.1   | Reset                                 | 3.1.2 |

| 2.2   | Base Addresses 13-6                   | 3.1.3 |

| 2.3   | Sample (data) Size 13-6               | 3.1.4 |

| 2.4   | Record or Message Size 13-7           | 3.1.5 |

| 2.5   | Records or Messages Per Buffer 13-7   | 3.2   |

| 2.6   | Stride                                | 3.3   |

| 2.7   | Interrupt Events                      | 3.4   |

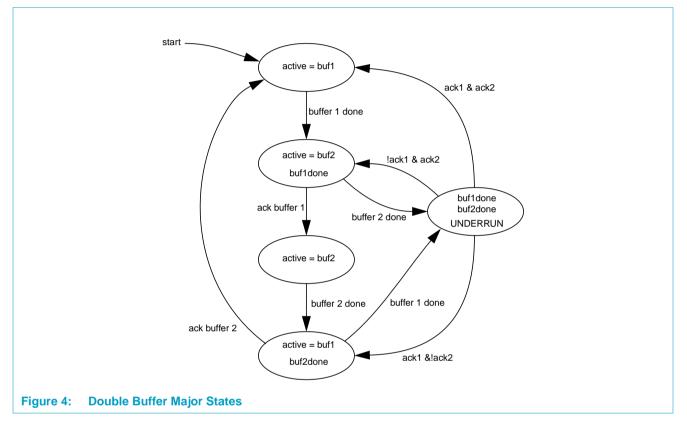

| 2.7.1 | BUF1DONE and BUF2DONE Interrupts 13-7 | 3.4.1 |

| 2.7.2 | THRESH1_REACHED and                   | 3.4.2 |

|       | THRESH2_REACHED Interrupts13-7        | 4.    |

| 2.7.3 | UNDERRUN Interrupt 13-8               | 4.1   |

| 2.7.4 | MBE Interrupt 13-8                    | 4.2   |

| 4.1   | Special Features11-37                |

|-------|--------------------------------------|

| 4.1.1 | Signature Analysis11-37              |

| 4.2   | Programming Help11-37                |

| 4.3   | LINT Parameters11-38                 |

| 4.4   | HSRU Parameters11-38                 |

| 4.5   | LSHR Parameters11-39                 |

| 4.6   | DCTI Parameters11-40                 |

| 4.7   | CFTR Parameters11-40                 |

| 4.8   | Underflow Behavior11-40              |

| 4.8.1 | Layer Underflow11-41                 |

| 4.8.2 | Underflow Symptom 11-41              |

| 4.8.3 | Underflow Recovery 11-41             |

| 4.8.4 | Underflow Trouble-shooting           |

| 4.8.5 | Underflow Handling11-41              |

| 4.9   | Setting QVCP for External VSYNC11-41 |

| 4.10  | Clock Calculations11-42              |

| 5.    | Register Descriptions11-43           |

| 5.1   | Register Summary11-43                |

| 5.2   | Register Tables                      |

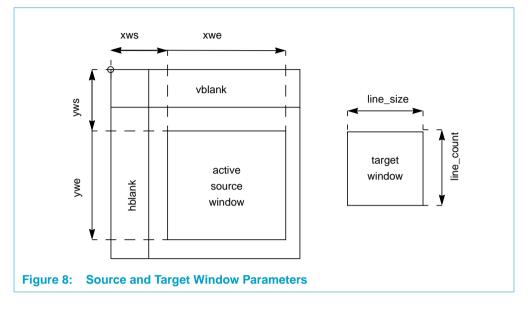

| 5.2 | Video Data Acquisition                             |

|-----|----------------------------------------------------|

| 5.3 | Internal Timing12-9                                |

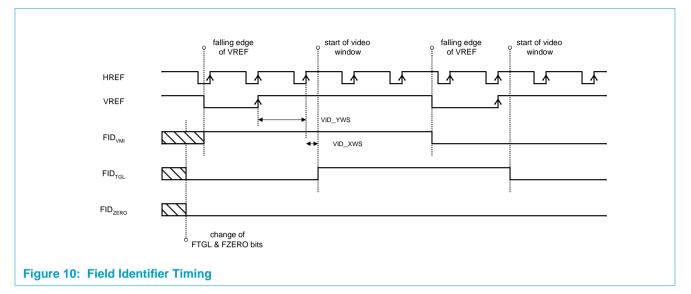

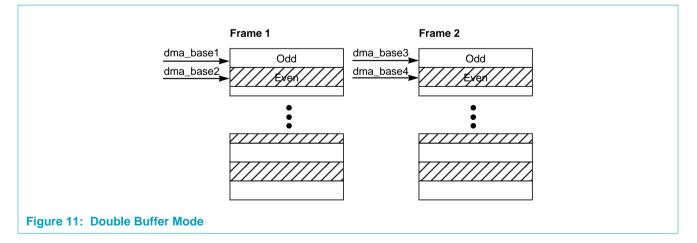

| 5.4 | Field Identifier Generation                        |

| 5.5 | Horizontal Video Filters (Sampling, Scaling, Color |

|     | Space Conversion)12-12                             |

| 5.6 | Video Data Write to Memory12-13                    |

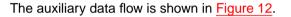

| 5.7 | Auxiliary Data Path 12-15                          |

| 5.8 | Interrupt Generation                               |

|     | Register Descriptions12-19                         |

| l   | Register Summary12-19                              |

| 2   | Register Table 12-21                               |

|     |                                                    |

| .8   | Record or Message Counters                |

|------|-------------------------------------------|

| .9   | Timestamp                                 |

| .10  | Variable Length 13-10                     |

| .11  | Output Time Registers                     |

| .12  | Double Buffer Operation13-10              |

| .13  | Single Buffer Operation13-11              |

|      | <b>Operation</b>                          |

| .1   | Both Operating Modes                      |

| .1.1 | Setup                                     |

| .1.2 | Interrupt Service Routines                |

| .1.3 | Optimized DMA Transfers                   |

| .1.4 | Terminating DMA Transfers                 |

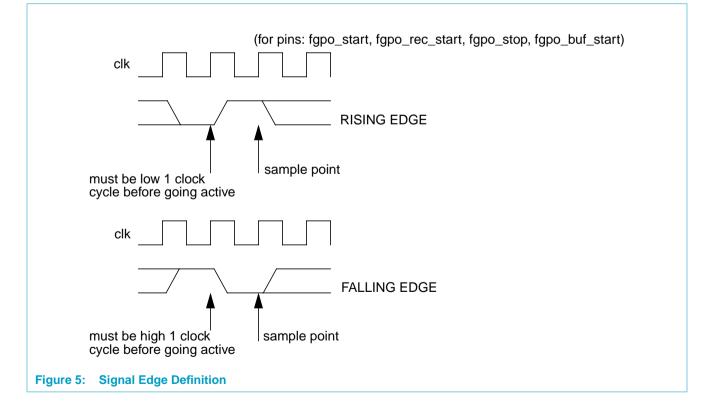

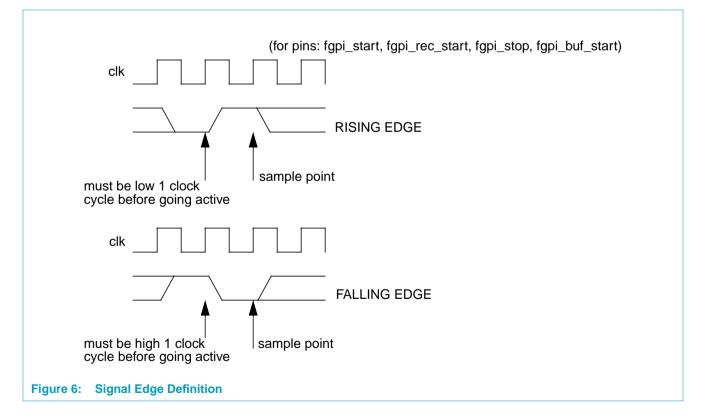

| .1.5 | Signal Edge Definitions                   |

| .2   | Message Passing Mode13-13                 |

| .3   | PNX1300 Series Message Passing Mode 13-13 |

| .4   | Record Output Mode13-13                   |

| .4.1 | Record Synchronization Events             |

| .4.2 | Buffer Synchronization Events             |

|      | Register Descriptions13-15                |

| .1   | Mode Register Setup13-15                  |

| .2   | Status Registers                          |

|      |                                           |

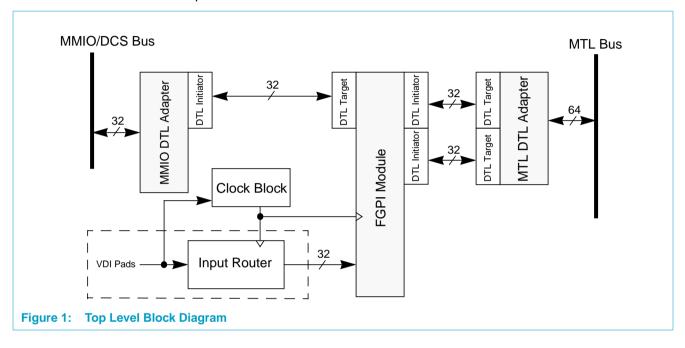

### Chapter 14: FGPI: Fast General Purpose Interface

| 1.    | Introduction14-1                                      | 2.8 |

|-------|-------------------------------------------------------|-----|

| 1.1   | FGPI Overview 14-2                                    | 2.9 |

| 1.2   | VDI to FGPI pin mapping 14-3                          | 2.1 |

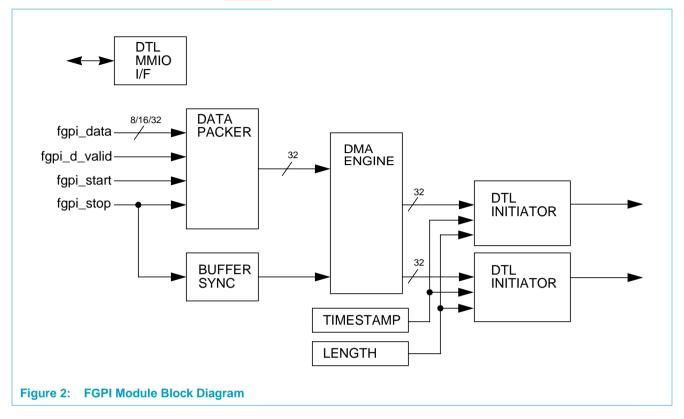

| 1.3   | DTL MMIO Interface 14-3                               | 2.1 |

| 1.4   | Data Packer14-3                                       | 2.1 |

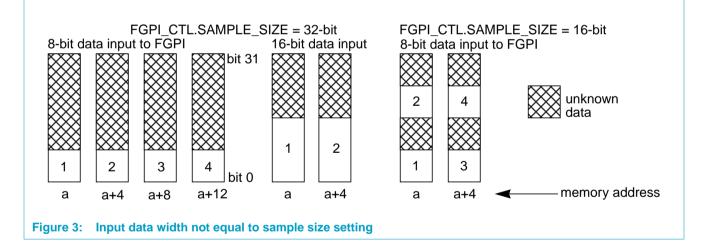

| 1.4.1 | 8-Bit Sample Packing Mode 14-4                        | 2.1 |

| 1.4.2 | 16-bit Sample Packing Mode 14-4                       | 3.  |

| 1.4.3 | 32-bit Sample Mode 14-4                               | 3.1 |

| 1.5   | Record Capture Mode 14-4                              | 3.1 |

| 1.6   | Message Passing Mode 14-4                             | 3.1 |

| 2.    | Functional Description14-6                            | 3.1 |

| 2.1   | Reset                                                 | 3.1 |

| 2.2   | Base Addresses 14-7                                   | 3.1 |

| 2.3   | Sample (data) Size 14-7                               | 3.2 |

| 2.4   | Record or Message Size 14-7                           | 3.2 |

| 2.5   | Records or Messages Per Buffer 14-8                   | 3.3 |

| 2.6   | Stride                                                | 3.4 |

| 2.7   | Interrupt Events 14-8                                 | 3.4 |

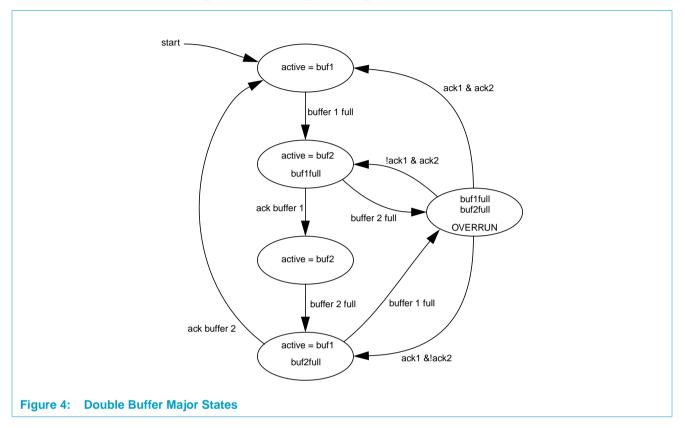

| 2.7.1 | BUF1FULL and BUF2FULL Interrupts 14-8                 | 3.4 |

| 2.7.2 | THRESH1_REACHED and                                   | 3.4 |

|       | THRESH2_REACHED Interrupts14-8                        |     |

| 2.7.3 | OVERRUN Interrupt14-8                                 | 4.  |

| 2.7.4 | MBE Interrupt 14-9                                    | 4.1 |

| 2.7.5 | OVERFLOW Interrupt (Message Passing Mode<br>Only)14-9 | 4.2 |

| Record or Message Counters14-9            |

|-------------------------------------------|

| Timestamp14-9                             |

| Variable Length14-10                      |

| Double Buffer Operation14-10              |

| Single Buffer Operation14-11              |

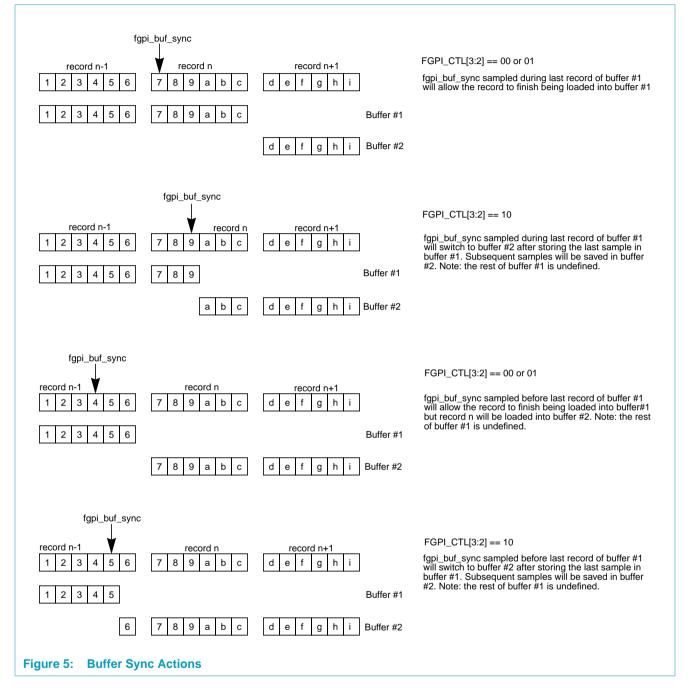

| Buffer Synchronization                    |

| <b>Operation</b>                          |

| Both Operating Modes                      |

| Setup                                     |

| Interrupt Service Routines14-13           |

| Optimized DMA Transfers 14-13             |

| Terminating DMA Transfers14-13            |

| Signal Edge Definitions14-13              |

| Message Passing Mode14-14                 |

| Minimum Message/Record Size14-14          |

| PNX1300 Series Message Passing Mode 14-15 |

| Record Capture Mode14-15                  |

| Record Synchronization14-15               |

| Buffer Synchronization                    |

| Setup and Operation with Input Router     |

| VDI_MODE[7] = 114-16                      |

| Register Descriptions14-18                |

| Mode Registers                            |

| Status Registers14-21                     |

|                                           |

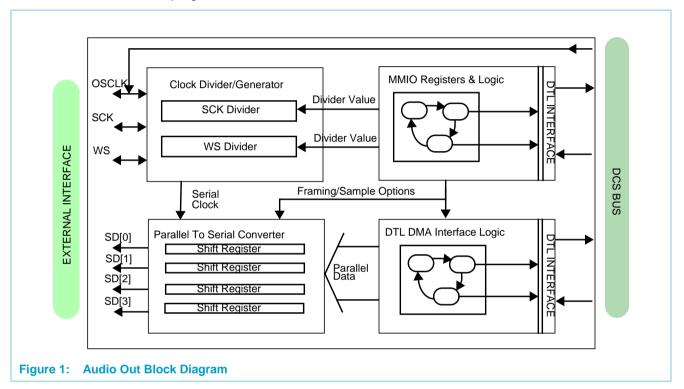

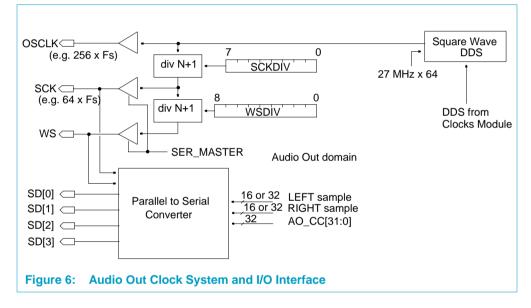

## Chapter 15: Audio Output

| 1.    | Introduction15-1              | 2.6.3 |

|-------|-------------------------------|-------|

| 1.1   | Features                      | 2.7   |

| 2.    | Functional Description        | 2.8   |

| 2.1   | External Interface 15-2       | 2.9   |

| 2.2   | Memory Data Formats 15-4      | 3.    |

| 2.2.1 | Endian Control 15-4           | 3.1   |

| 2.3   | Audio Out Data DMA Operation  | 3.1.1 |

| 2.3.1 | TRANS_ENABLE                  | 3.1.2 |

| 2.4   | Interrupts 15-6               | 3.2   |

| 2.4.1 | Interrupt Latency 15-6        | 3.3   |

| 2.5   | Timestamp Events 15-6         | 3.4   |

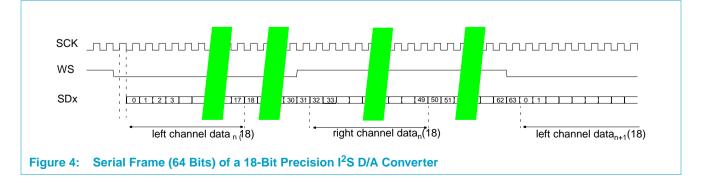

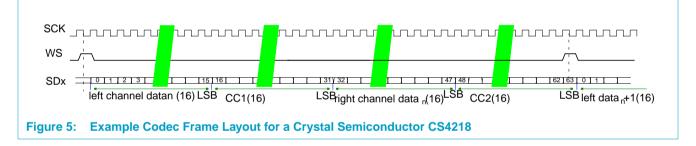

| 2.6   | Serial Data Framing 15-6      | 4.    |

| 2.6.1 | Serial Frame Limitations 15-8 | 4.1   |

| 2.6.2 | WS Characteristics15-8        | 4.2   |

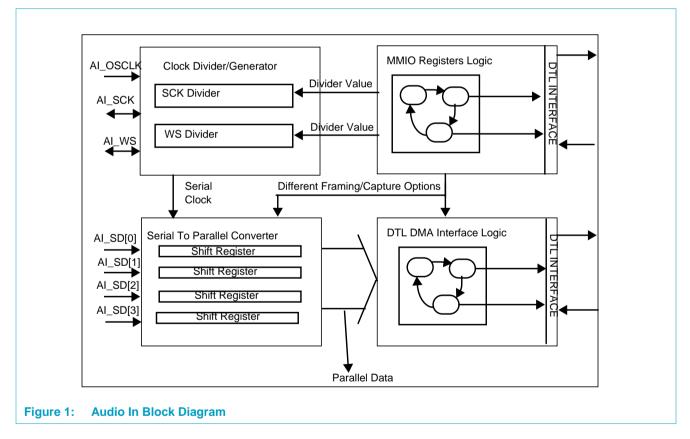

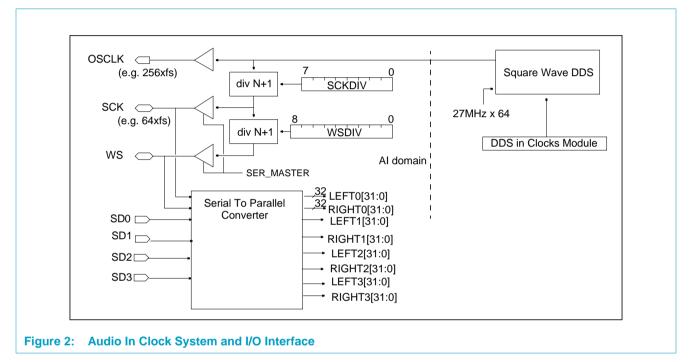

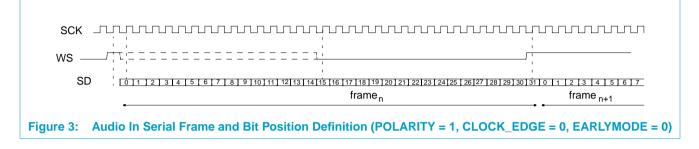

### Chapter 16: Audio Input

| 1.    | Introduction16-1                     | 3.4        |

|-------|--------------------------------------|------------|

| 1.1   | Features                             | 3.5        |

| 2.    | Functional Description16-2           | 3.5.1      |

| 2.1   | Chip Level External Interface        | 3.6        |

| 2.2   | General Operations                   | 3.7        |

| 3.    | <b>Operation</b>                     | 3.8<br>3.9 |

| 3.1   | Clock Programming 16-5               | 3.9        |

| 3.1.1 | Clock System Operation 16-5          | 3.11       |

| 3.2   | Reset-Related Issues 16-6            | 3.12       |

| 3.3   | Register Programming Guidelines 16-7 | 3.13       |

| 2.6.3 | I <sup>2</sup> S Serial Framing Example15-8 |

|-------|---------------------------------------------|

| 2.7   | Codec Control                               |

| 2.8   | Data Bus Latency and HBE15-10               |

| 2.9   | Error Behavior15-11                         |

| 3.    | <b>Operation</b>                            |

| 3.1   | Clock Programming15-12                      |

| 3.1.1 | Sample Clock Generator                      |

| 3.1.2 | Clock System Operation15-13                 |

| 3.2   | Reset-Related Issues 15-14                  |

| 3.3   | Register Programming Guidelines 15-14       |

| 3.4   | Power Management 15-14                      |

| 4.    | Register Descriptions15-15                  |

| 4.1   | Register Summary15-15                       |

| 4.2   | Register Table                              |

|       |                                             |

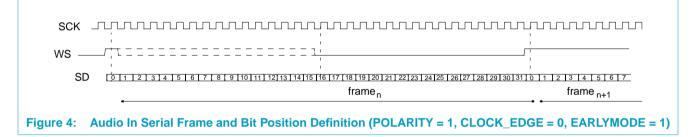

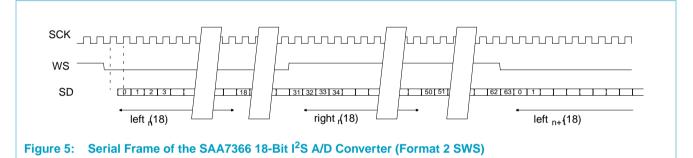

| Serial Data Framing          | 16-7 |

|------------------------------|------|

| Memory Data Formats10        |      |

| Endian Control10             | 6-10 |

| Memory Buffers and Capture10 | 6-11 |

| Data Bus Latency and HBE10   | 6-11 |

| Error Behavior10             | ô-12 |

| Interrupts10                 | ô-12 |

| Timestamp Events10           | 6-13 |

| Diagnostic Mode10            | ô-13 |

| Software Reset10             | ô-14 |

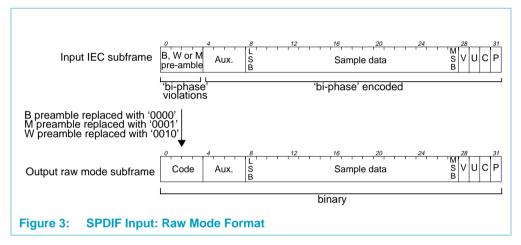

| Raw Mode10                   | ô-15 |

|                              |      |

## **Philips Semiconductors**

### Volume 1 of 1

| 4. | Register Descriptions | 16-15 | 4.1 |

|----|-----------------------|-------|-----|

|    |                       |       |     |

## Chapter 17: SPDIF Output

| 1.    | Introduction17-1                     |

|-------|--------------------------------------|

| 1.1   | Features 17-1                        |

| 2.    | Functional Description 17-2          |

| 2.1   | Architecture 17-2                    |

| 2.2   | General Operations 17-2              |

| 3.    | <b>Operation</b> 17-2                |

| 3.1   | Clock Programming 17-2               |

| 3.1.1 | Sample Rate Programming 17-2         |

| 3.2   | Register Programming Guidelines 17-3 |

| 3.3   | Data Formatting 17-4                 |

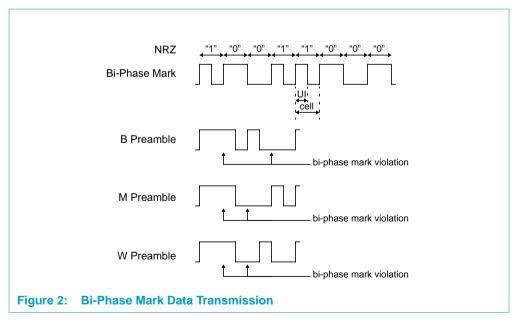

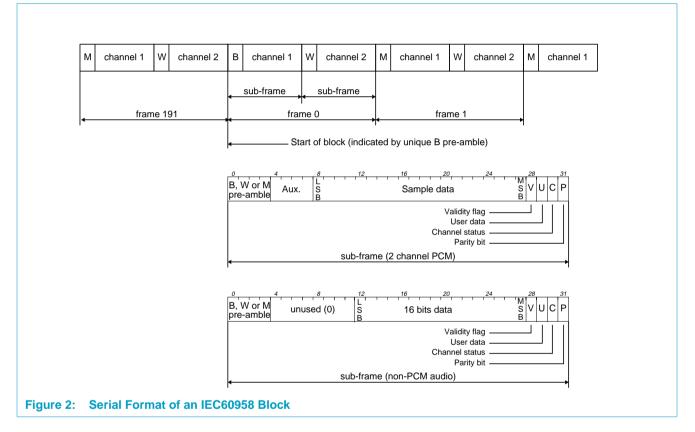

| 3.3.1 | IEC-60958 Serial Format 17-4         |

| 3.3.2 | Transparent Mode 17-6                |

## Chapter 18: SPDIF Input

| Introduction18-1                            |

|---------------------------------------------|

| Features                                    |

| Functional Description                      |

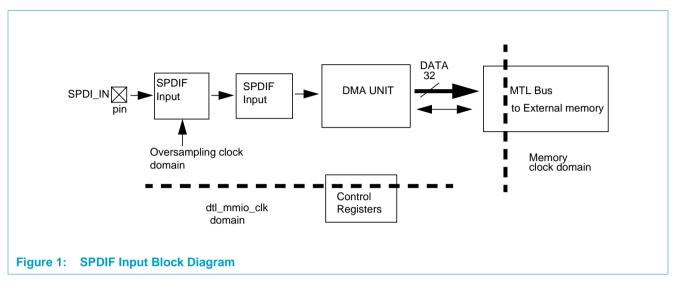

| SPDIF Input Block Level Diagram 18-1        |

| Architecture                                |

| Functional Modes 18-2                       |

| General Operations 18-3                     |

| Received Serial Format                      |

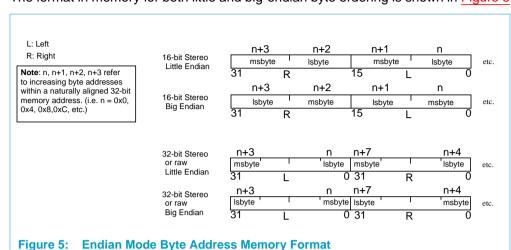

| Memory Formats 18-3                         |

| SPDIF Input Endian Mode 18-4                |

| Bandwidth and Latency Requirements 18-5     |

| <b>Operation</b>                            |

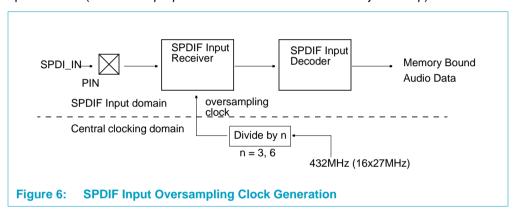

| Clock Programming 18-6                      |

| SPDIF Input Clock Domains                   |

| SPDIF Receiver Sample Rate Tolerance and    |

| IEC6095818-6                                |

| SPDIF Input Receiver Jitter Tolerance 18-6  |

| SPDIF Input and the Oversampling Clock 18-7 |

| Register Programming Guidelines 18-7        |

| SPDIF Input Register Set 18-7               |

| SPDI_STATUS Register Functions 18-8         |

|                                             |

## Chapter 19: Memory Based Scaler

| 1.    | Introduction                   |

|-------|--------------------------------|

| 2.    | Functional Description         |

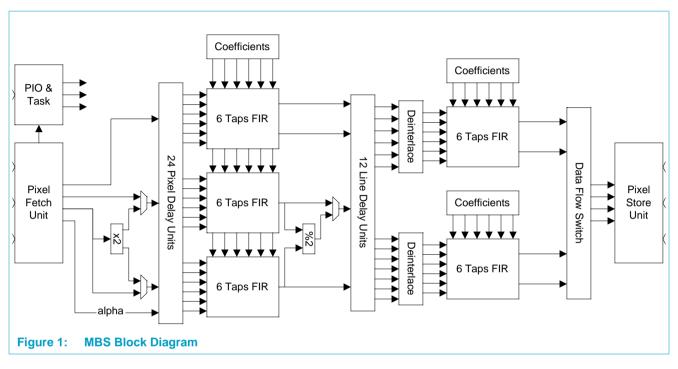

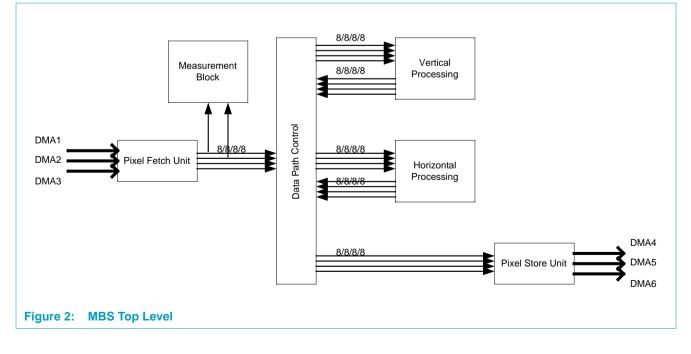

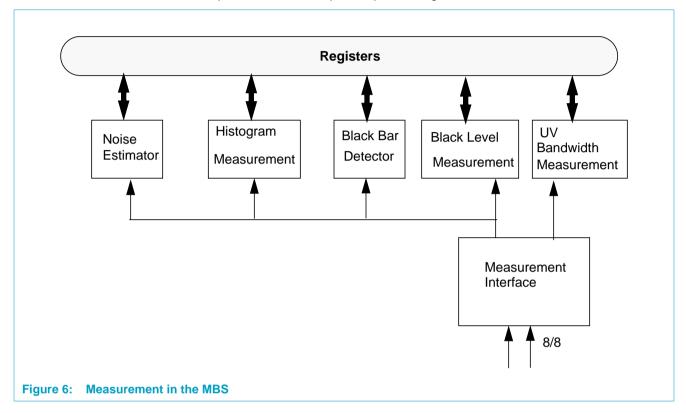

| 2.1   | MBS Block Level Diagram 19-3   |

| 2.2   | Data Flow                      |

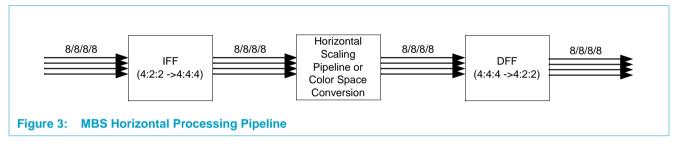

| 2.2.1 | Horizontal Processing Pipeline |

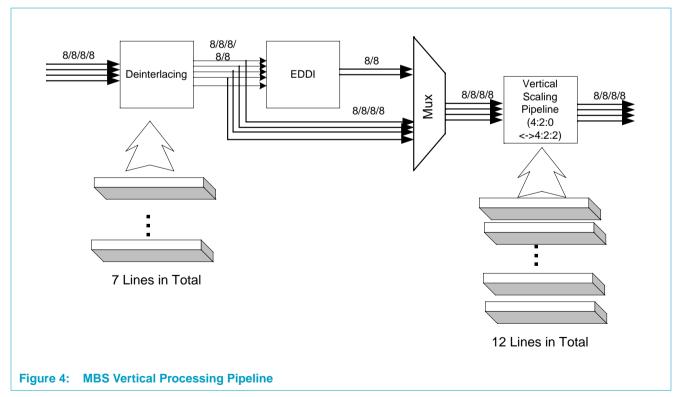

| 2.2.2 | Vertical Processing Pipeline   |

| 2.3   | Data Processing in MBS 19-5    |

| 2.4   | General Operations 19-6        |

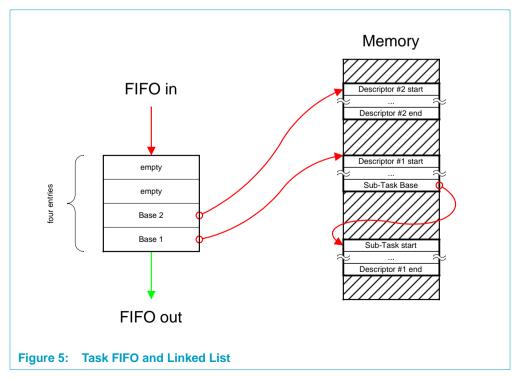

| 2.4.1 | Task Control 19-6              |

| 2.4.2 | Video Source Controls          |

| 2.4.3 | Horizontal Video Filters 19-8  |

| Register Table 16- |

|--------------------|

|--------------------|

| 3.4                           | Errors and Interrupts17-6                                                                                    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------|

| 3.4.1                         | DMA Error Conditions                                                                                         |

| 3.4.2                         | HBE and Latency 17-7                                                                                         |

| 3.4.3                         | Interrupts17-7                                                                                               |

| 3.4.4                         | Timestamp Events                                                                                             |

| ~ -                           |                                                                                                              |

| 3.5                           | Endian Mode 17-8                                                                                             |

| 3.5<br><b>4.</b>              | Endian Mode         17-8           Signal Description         17-8                                           |

|                               |                                                                                                              |

| 4.                            | Signal Description17-8                                                                                       |

| <b>4.</b><br>4.1              | Signal Description                                                                                           |

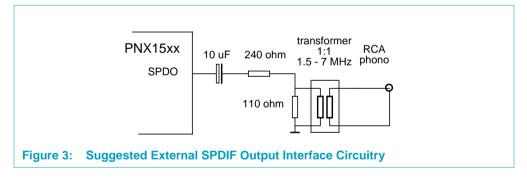

| <b>4.</b><br>4.1<br><b>5.</b> | Signal Description       17-8         External Interface       17-8         Register Descriptions       17-8 |

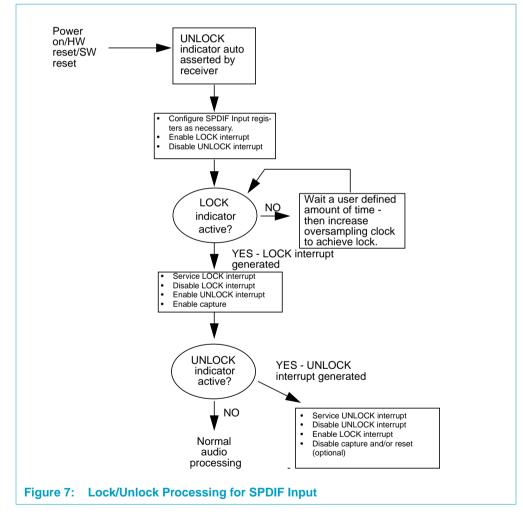

| 3.2.3  | LOCK and UNLOCK State Behavior 18-8          |

|--------|----------------------------------------------|

| 3.2.4  | UNLOCK Error Behavior and DMA18-8            |

| 3.2.5  | SPDI_CTL and Functions                       |

| 3.2.6  | SPDI_CBITSx and Channel Status Bits 18-10    |

| 3.2.7  | SPDI_UBITSx and User Bits                    |

| 3.2.8  | SPDI_BASEx and SPDI_SIZE Registers and       |

|        | Memory Buffers18-12                          |

| 3.2.9  | SPDI_SMPMASK and Sample Size Masking . 18-   |

|        | 12                                           |

| 3.2.10 | SPDI_BPTR and the Start of an IEC60958 Block |

|        | 18-12                                        |

| 3.2.11 | Interrupts                                   |

| 3.2.12 | Event Timestamping18-13                      |

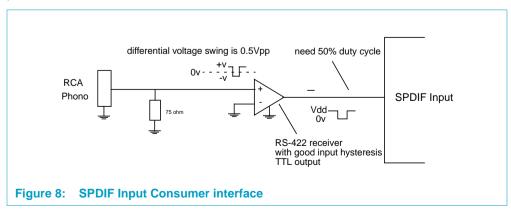

| 4.     | Signal Descriptions                          |

| 4.1    | External Interface Pins                      |

| 4.1.1  | System Interface Requirements                |

| 5.     | Register Descriptions                        |

| 5.1    | Register Summary                             |

| 5.1.1  | SPDIF Input Interrupt Registers              |

| 5.2    | Register Table                               |

| J.Z    | Neyister rable 10-17                         |

| 2.4.4  | Vertical Video Filters     |

|--------|----------------------------|

| 2.4.5  | De-Interlacing in MBS19-10 |

| 2.4.6  | Color-Key Processing       |

| 2.4.7  | Alpha Processing19-11      |

| 2.4.8  | Video Data Output19-11     |

| 2.4.9  | Address Generation 19-12   |

| 2.4.10 | Interrupt Generation 19-12 |

| 2.4.11 | Measurement Functions      |

| 3.     | Register Descriptions19-14 |

| 3.1    | Register Summary 19-14     |

| 3.2    | Register Table             |

|        |                            |

### Chapter 20: 2D Drawing Engine

| 1.     | Introduction                               | 2.2.  |

|--------|--------------------------------------------|-------|

| 1.1    | Features                                   | 2.3   |

| 2.     | Functional Description                     | 2.3.  |

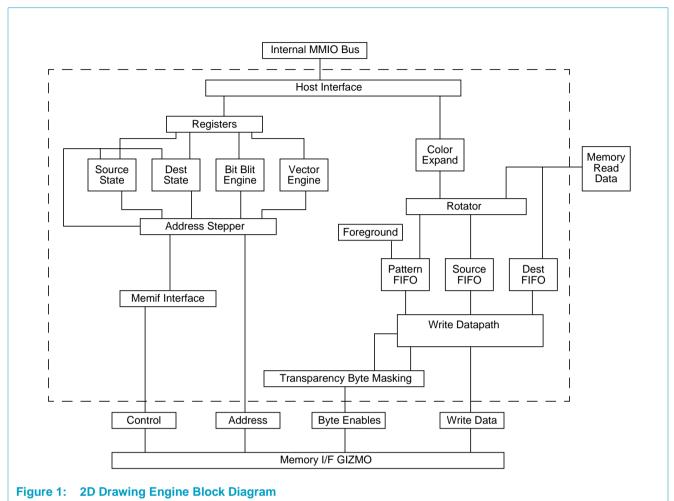

| 2.1    | 2D Drawing Engine Block Level Diagram 20-2 | 2.3.  |

| 2.2    | Architecture                               | 2.3.  |

| 2.2.1  | Registers                                  | 2.3.4 |

| 2.2.2  | Host Interface 20-2                        | 2.3.  |

| 2.2.3  | Color Expand                               | 2.3.  |

| 2.2.4  | Rotator                                    | 3.    |

| 2.2.5  | Source FIFO 20-3                           | 3.1   |

| 2.2.6  | Pattern FIFO 20-3                          | 3.1.  |

| 2.2.7  | Destination FIFO 20-3                      | 3.1.  |

| 2.2.8  | Write Datapath 20-3                        | 3.1.3 |

| 2.2.9  | Source State 20-3                          | 3.1.4 |

| 2.2.10 | Destination State 20-3                     | 3.1.  |

| 2.2.11 | Address Stepper 20-3                       | 3.1.0 |

| 2.2.12 | Bit BLT Engine 20-4                        | 4.    |

| 2.2.13 | Vector Engine 20-4                         | 4.1   |

| 2.2.14 | Memory Interface 20-4                      | 4.2   |

## Chapter 21: MPEG-1 and MPEG-2 Variable Length Decoder

| 1.    | Introduction                               |

|-------|--------------------------------------------|

| 1.1   | Features                                   |

| 2.    | Functional Description                     |

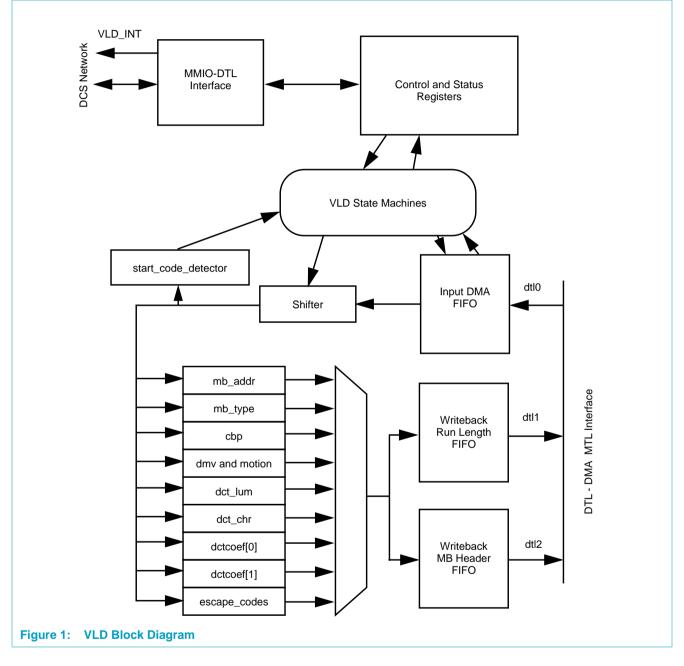

| 2.1   | VLD Block Level Diagram                    |

| 3.    | <b>Operation</b>                           |

| 3.1   | Reset-Related Issues 21-3                  |

| 3.2   | VLD MMIO Registers 21-4                    |

| 3.2.1 | VLD Status (VLD_MC_STATUS)                 |

| 3.2.2 | VLD Interrupt Enable (VLD_IE)              |

| 3.2.3 | VLD Control (VLD_CTL) 21-5                 |

| 3.2.4 | VLD DMA Current Read Address               |

|       | (VLD_INP_ADR) and                          |

|       | Read Count (VLD_INP_CNT)21-6               |

| 3.2.5 | VLD DMA Macroblock Header Current Write    |

|       | Address (VLD_MBH_ADR)21-6                  |

| 3.2.6 | VLD DMA Macroblock Header Current Write    |

|       | Count21-6                                  |

| 3.2.7 | VLD DMA Run-Level Current Write Address    |

|       | (VLD_RL_ADR)21-7                           |

| 3.2.8 | VLD DMA Run-Level Current Write Count 21-7 |

| 3.2.9 | VLD Command (VLD_COMMAND) 21-7             |

| 2.2.15 | Byte Masking 20-4               |

|--------|---------------------------------|

| 2.3    | General Operations20-4          |

| 2.3.1  | Raster Operations               |

| 2.3.2  | Alpha Blending                  |

| 2.3.3  | Source Data Location and Type   |

| 2.3.4  | Patterns                        |

| 2.3.5  | Transparency                    |

| 2.3.6  | Block Writes                    |

| 3.     | <b>Operation</b>                |

| 3.1    | Register Programming Guidelines |

| 3.1.1  | Alpha Blending                  |

| 3.1.2  | Mono Expand                     |

| 3.1.3  | Mono BLT Register Setup         |

| 3.1.4  | Solid Fill Setup20-11           |

| 3.1.5  | Color BLT Setup                 |

| 3.1.6  | PatRam                          |

| 4.     | Register Descriptions20-13      |

| 4.1    | Register Summary20-14           |

| 4.2    | Register Tables                 |

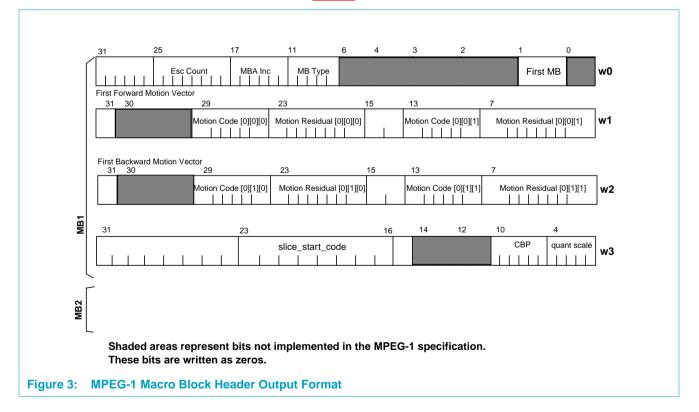

| 3.2.10 | VLD Shift Register (VLD_SR)21-9             |

|--------|---------------------------------------------|

| 3.2.11 | VLD Quantizer Scale (VLD_QS)21-9            |

| 3.2.12 | VLD Picture Info (VLD_PI)21-9               |

| 3.2.13 | VLD Bit Count (VLD_BIT_CNT)                 |

| 3.3    | VLD Operation                               |

| 3.3.1  | VLD Input                                   |

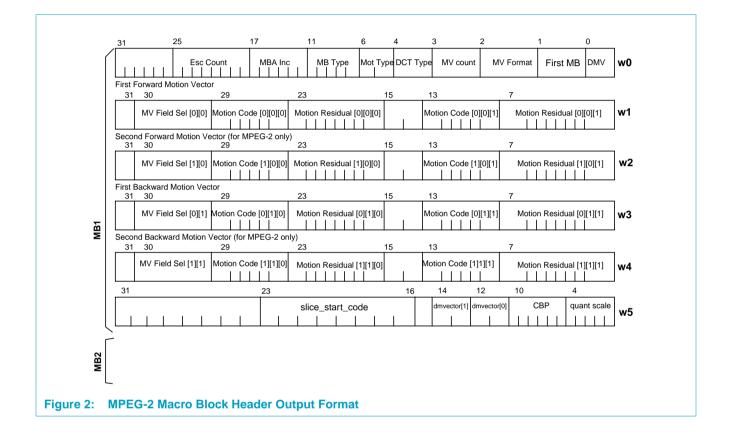

| 3.3.2  | VLD Output                                  |

| 3.3.3  | Restart the VLD Parsing                     |

| 3.4    | Error Handling                              |

| 3.4.1  | Unexpected Start Code                       |

| 3.4.2  | RL Overflow                                 |

| 3.4.3  | Flush                                       |

| 4.     | Application Notes                           |

| 4.0.1  | PNX1300 Series versus PNX15xx Series VLD21- |

|        | 15                                          |

| 5.     | Register Descriptions                       |

| 5.1    | PNX1300 Series and PNX15xx Series Register  |

|        | Differences21-15                            |

| 5.2    | VLD Register Summary                        |

| 5.3    | Register Table                              |

|        | -                                           |

## **Chapter 22: Digital Video Disc Descrambler**

| 1.  | Introduction                | 1. | Introduction |

|-----|-----------------------------|----|--------------|

| 1.1 | Functional Description 22-1 |    |              |

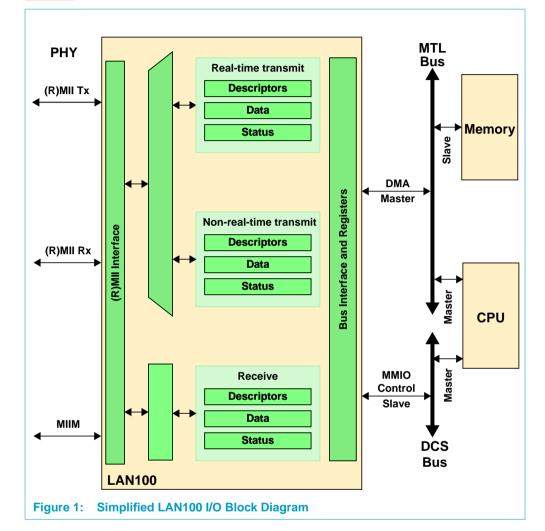

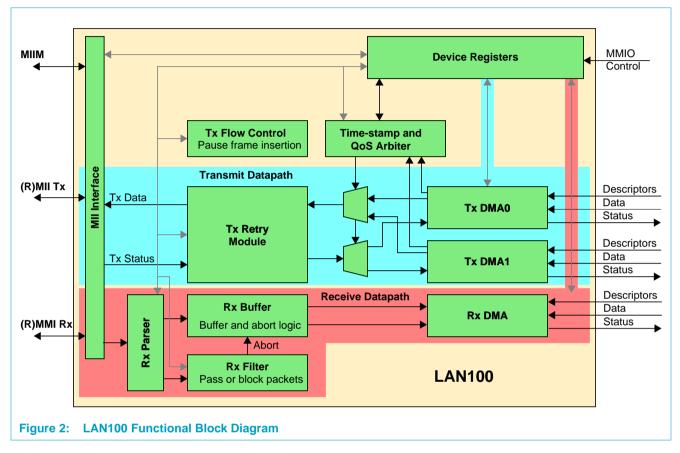

## Chapter 23: LAN100 — Ethernet Media Access Controller

| 1.1 | Features 23-1                             | 2.3 | Description               |

|-----|-------------------------------------------|-----|---------------------------|

| 2.  | Functional Description                    | 3.  | Register Descriptions23-5 |

| 2.1 | Chip I/O and System Interconnections 23-2 | 3.1 | Register Summary23-5      |

| 2.2 | Functional Block Diagram                  | 3.2 | Register Definitions23-8  |

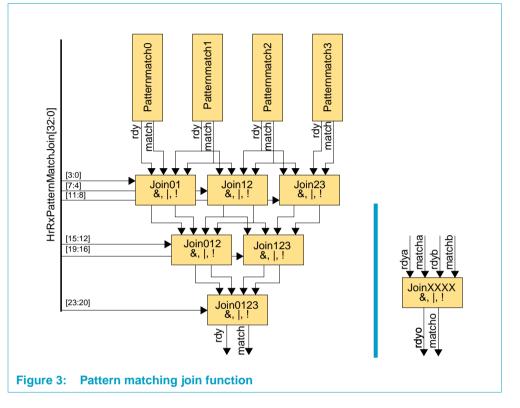

| 3.3   | Pattern Matching Join Register                     |

|-------|----------------------------------------------------|

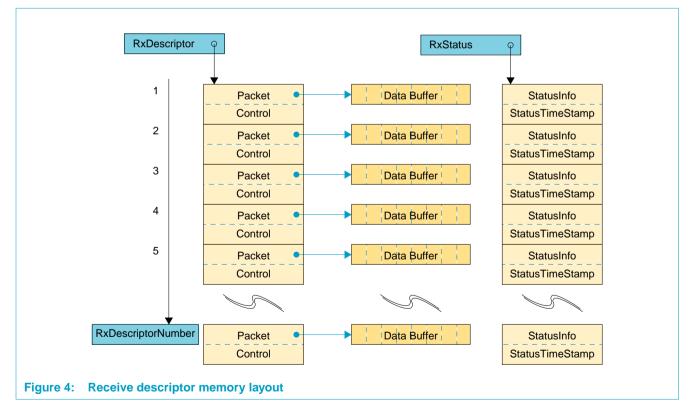

| 4.    | Descriptor and Status Formats 23-27                |

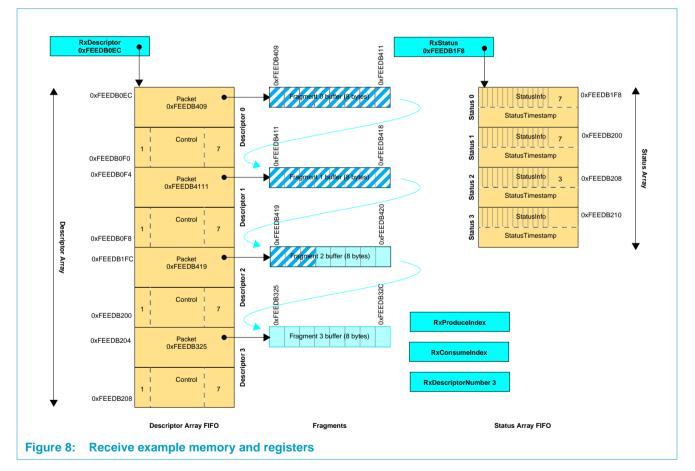

| 4.1   | Receive Descriptors and Status 23-27               |

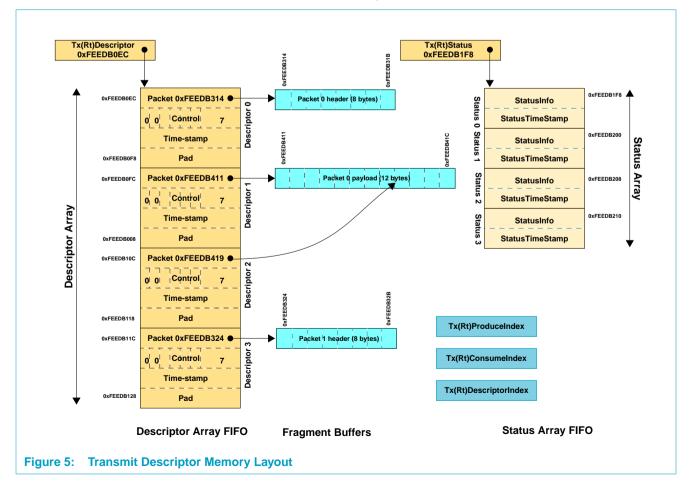

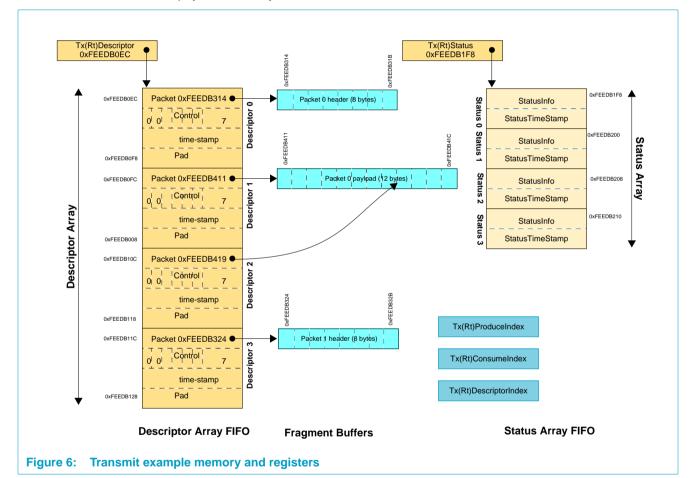

| 4.2   | Transmit Descriptors and Status                    |

| 5.    | LAN100 Functions                                   |

| 5.1   | MMIO Interface 23-33                               |

| 5.1.1 | Overview                                           |

| 5.2   | Direct Memory Access                               |

| 5.2.1 | Descriptor FIFOs 23-34                             |

| 5.2.2 | Ownership of Descriptors 23-34                     |

| 5.2.3 | Sequential Order with Wrap-around 23-35            |

| 5.2.4 | Full and Empty State of FIFOs 23-35                |

| 5.2.5 | Interrupt Bit 23-36                                |

| 5.2.6 | Packet Fragments 23-36                             |

| 5.3   | Initialization 23-37                               |

| 5.4   | Transmit process 23-38                             |

| 5.4.1 | Overview                                           |

| 5.4.2 | Device Driver Sets Up Descriptors and Data23-38    |

| 5.4.3 | Tx(Rt) DMA Manager Reads Tx(Rt) Descriptor         |

|       | Arrays23-39                                        |

| 5.4.4 | Tx(Rt) DMA manager transmits data 23-39            |

| 5.4.5 | Update ConsumeIndex 23-40                          |

| 5.4.6 | Write Transmission Status 23-40                    |

| 5.4.7 | Transmission Error Handling 23-40                  |

| 5.4.8 | Transmit Triggers Interrupts                       |

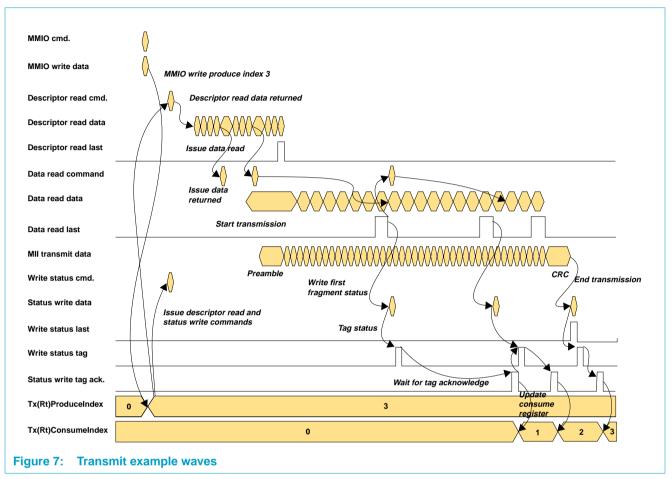

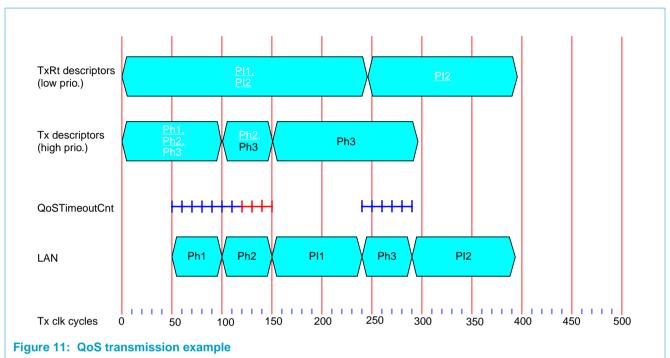

| 5.4.9 | Transmit example 23-42                             |

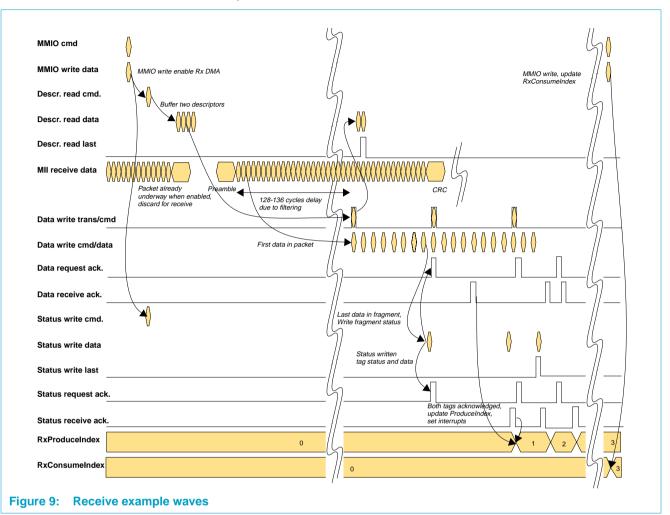

| 5.5   | Receive process 23-45                              |

| 5.5.1 | Device Driver Sets Up Descriptors 23-46            |

| 5.5.2 | Rx DMA Manager Reads Rx Descriptor Arrays<br>23-46 |

| 5.5.3 | Rx DMA Manager Receives Data 23-46                 |

| 5.5.4 | Update ProduceIndex 23-47                          |

| 5.5.5 | Write Reception Status 23-47                       |

| 5.5.6 | Reception Error Handling 23-47                     |

| 5.5.7 | Receive Triggers Interrupts 23-48                  |

| 5.5.8 | Device Driver Processes Receive Data 23-49         |

| 5.5.9 | Receive example 23-49                              |

| 5.6   | Transmission Retry 23-53                           |

| 5.7   | time-stamps                                        |

| 5.8   | Transmission modes 23-53                           |

| 5.8.1 | Overview                                           |

## Chapter 24: TM3260 Debug

| 1.    | Introduction                             | 3.    |

|-------|------------------------------------------|-------|

| 1.1   | Features 24-1                            | 3.1   |

| 2.    | Functional Description                   | 3.1.1 |

| 2.1   | General Operations 24-1                  | 3.2   |

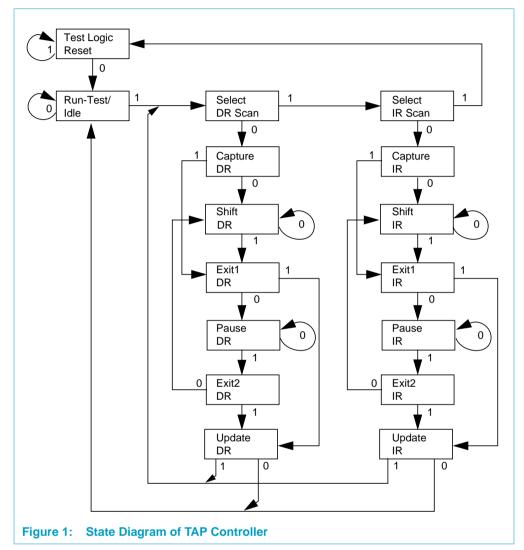

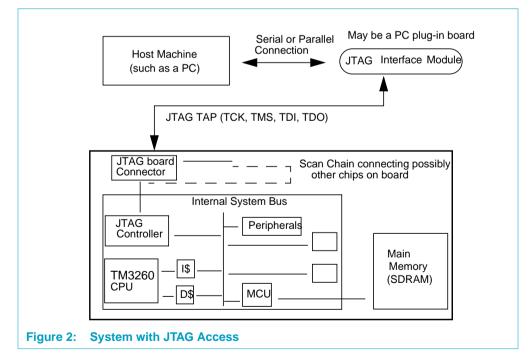

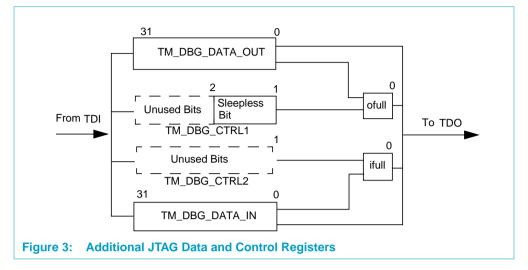

| 2.1.1 | Test Access Port (TAP) 24-1              | 4.    |

| 2.1.2 | TAP Controller 24-2                      | 4.1   |

| 2.1.3 | PNX15xx Series JTAG Instruction Set 24-4 |       |

## Chapter 25: I<sup>2</sup>C Interface

| 1.  | Introduction           | 2.1 |

|-----|------------------------|-----|

| 1.1 | Features               | 2.1 |

| 2.  | Functional Description | 2.1 |

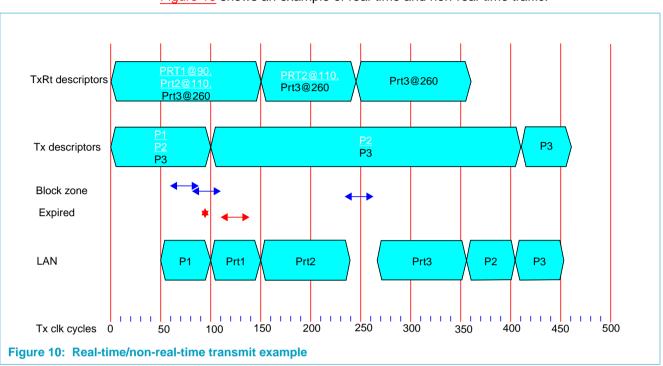

| 5.8.2  | Real-time/non-real-time transmission mode 23-54   |

|--------|---------------------------------------------------|

| 5.8.3  | Quality-of-service Transmission Mode23-57         |

| 5.9    | Duplex Modes                                      |

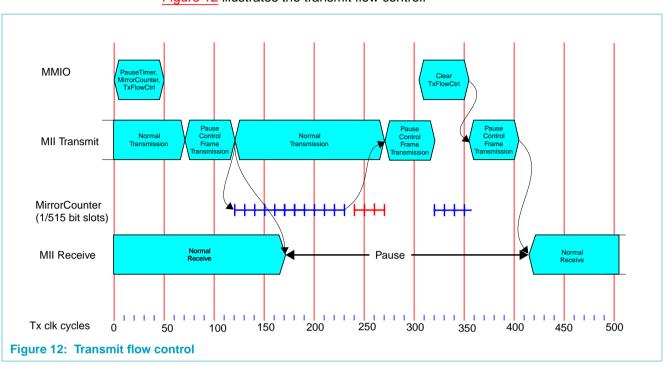

| 5.10   | IEEE 802.3/Clause 31 Flow Control23-59            |

| 5.10.1 | Overview                                          |

| 5.10.2 | Receive Flow Control                              |

| 5.10.3 | Transmit Flow Control                             |

| 5.11   | Half-duplex Mode Back Pressure23-61               |

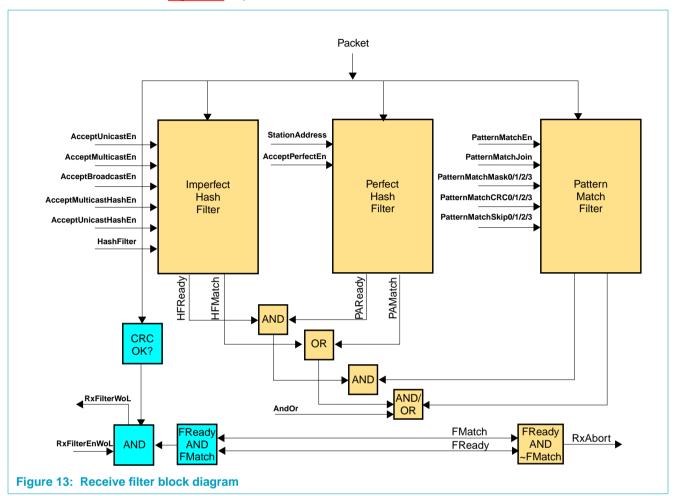

| 5.12   | Receive filtering23-62                            |

| 5.12.1 | Overview                                          |

| 5.12.2 | Unicast, Broadcast and Multicast23-64             |

| 5.12.3 | Perfect Address Match23-64                        |

| 5.12.4 | Imperfect Hash Filtering23-64                     |

| 5.12.5 | Pattern Match Filtering and Logic Functions 23-65 |

| 5.12.6 | Enabling and Disabling Filtering23-66             |

| 5.12.7 | Runt Frames23-66                                  |

| 5.13   | Wake-up on LAN23-66                               |

| 5.13.1 | Overview23-66                                     |

| 5.13.2 | Filtering for WoL23-67                            |

| 5.13.3 | Magic Packet WoL23-67                             |

| 5.14   | Enabling and Disabling Receive and Transmit 23-   |

|        | 68                                                |

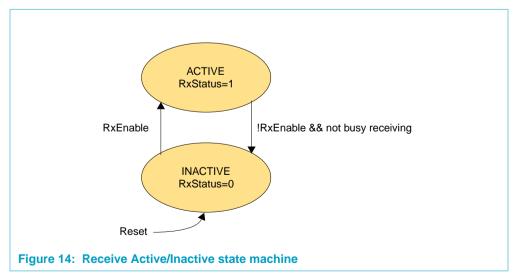

| 5.14.1 | Enabling and Disabling Reception 23-68            |

| 5.14.2 | Enabling and Disabling Transmission 23-69         |

| 5.15   | Transmission Padding and CRC23-69                 |

| 5.16   | Huge Frames and Frame Length Checking. 23-70      |

| 5.17   | Statistics Counters23-71                          |

| 5.18   | Status Vectors23-71                               |

| 5.19   | Reset                                             |

| 5.19.1 | Hard Reset                                        |

| 5.19.2 | Soft Reset23-71                                   |

| 6. 5   | System Integration23-73                           |

| 6.1    | MII Interface I/O23-73                            |

| 6.2    | Power Management                                  |

| 6.2.1  | Sleep Mode                                        |

| 6.2.2  | Coma Mode                                         |

| 6.3    | Disabling the LAN10023-75                         |

| 6.4    | Little/big Endian23-75                            |

| 6.5    | Interrupts                                        |

| 6.6    | Errors and Aborts23-75                            |

| 6.7    | Cache coherency23-76                              |

|        |                                                   |

|    | <b>Operation</b>                           |

|----|--------------------------------------------|

|    | Register Programming Guidelines            |

| .1 | Handshaking and Communication Protocol24-5 |

|    | Debug Settings24-6                         |

|    | Register Descriptions24-7                  |

|    | Register Summary24-9                       |

| 1   | General Operations25-2            |

|-----|-----------------------------------|

| 1.1 | IIC Arbitration and Control Logic |

| 1.2 | Serial Clock Generator25-3        |

## **Philips Semiconductors**

### Volume 1 of 1

| 2.1.3 | Bit Counter                          |

|-------|--------------------------------------|

| 2.1.4 | Control Register 25-3                |

| 2.1.5 | Status Decoder and Register 25-3     |

| 2.1.6 | Input Filter 25-3                    |

| 2.1.7 | Address Register and Comparator 25-3 |

| 2.1.8 | Data Shift Register 25-4             |

| Chapter | 26: | Memory | Arbiter |

|---------|-----|--------|---------|

|---------|-----|--------|---------|

| 1.    | Introduction           | 2. |

|-------|------------------------|----|

| 1.1   | Features               | 3. |

| 2.    | Functional Description | 3. |

| 2.1   | Arbiter Features       | 3. |

| 2.2   | ID Mapping             | 4. |

| 2.2.1 | DCS Gate               | 4. |

| 2.3   | Arbitration Algorithm  |    |

### **Chapter 27: Power Management**

| 1.    | Power Management Mechanisms 27-1                           |

|-------|------------------------------------------------------------|

| 1.1   | Clock Management 27-1                                      |

| 1.1.1 | Essential Operating Infrastructure During<br>Powerdown27-1 |

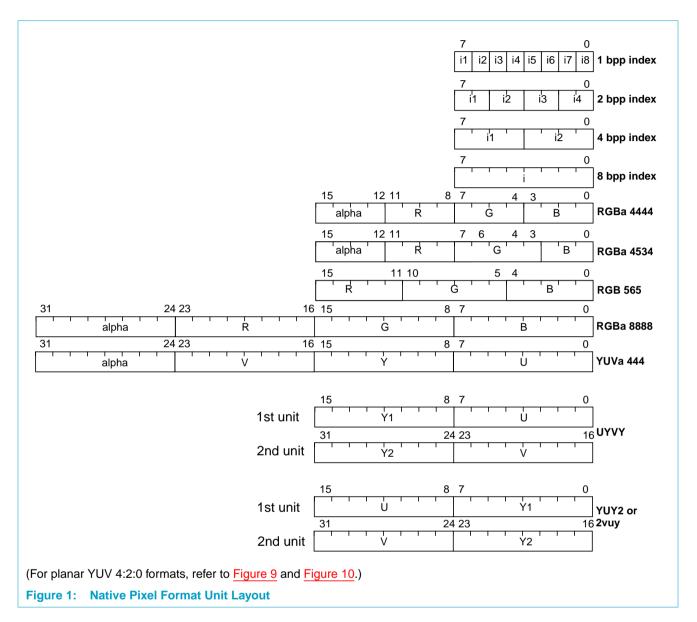

### **Chapter 28: Pixel Formats**

| 1.    | Introduction                                |

|-------|---------------------------------------------|

| 2.    | Summary of Native Pixel Formats 28-2        |

| 3.    | Native Pixel Format Representation 28-3     |

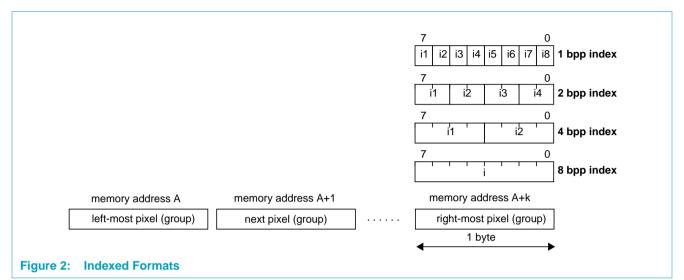

| 3.1   | Indexed Formats 28-3                        |

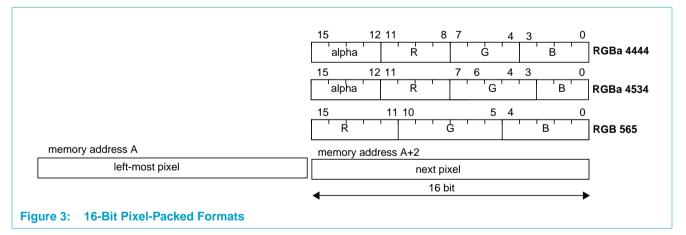

| 3.2   | 16-Bit Pixel-Packed Formats 28-4            |

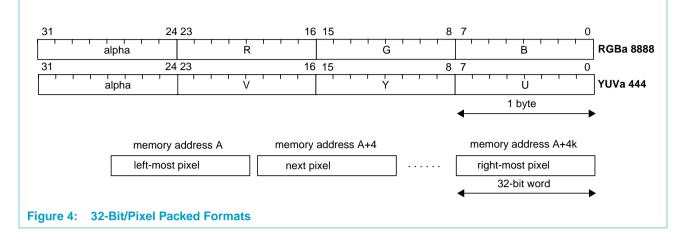

| 3.3   | 32-Bit Pixel-Packed Formats 28-4            |

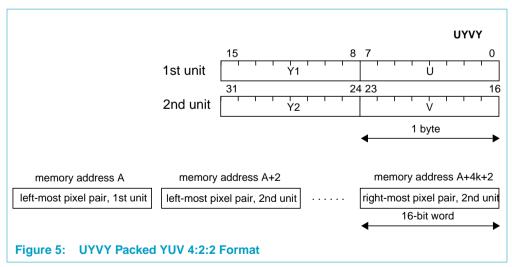

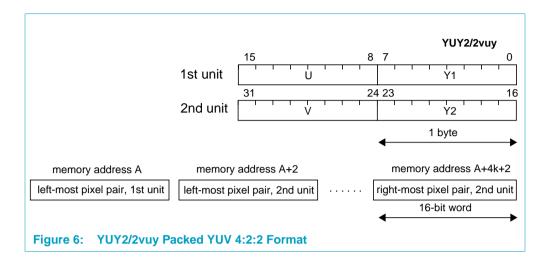

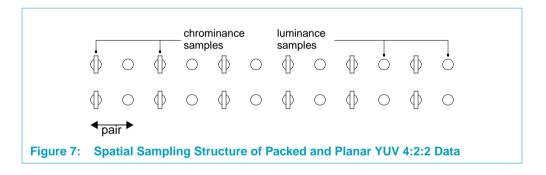

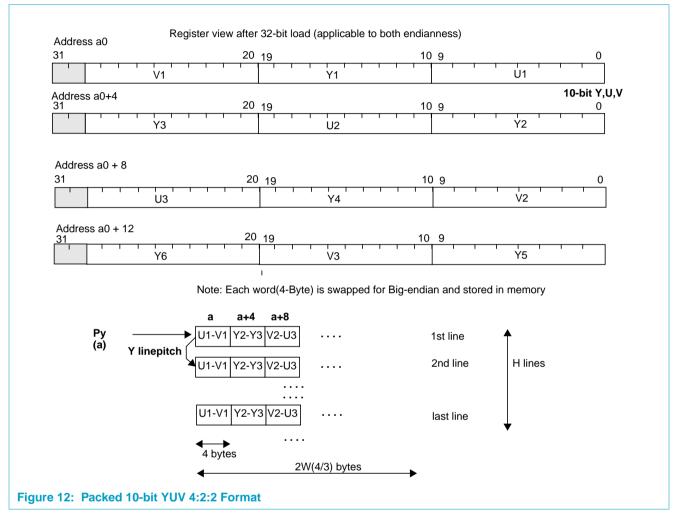

| 3.4   | Packed YUV 4:2:2 Formats 28-5               |

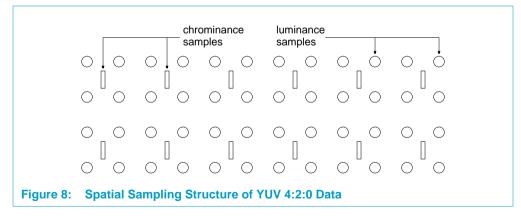

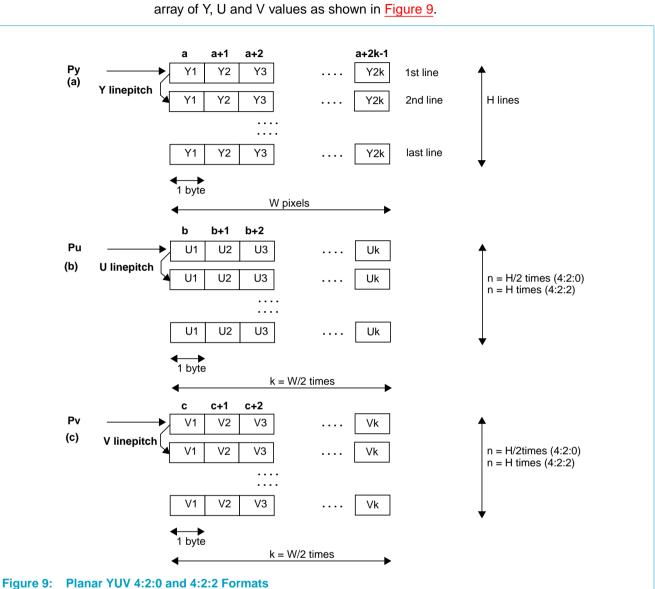

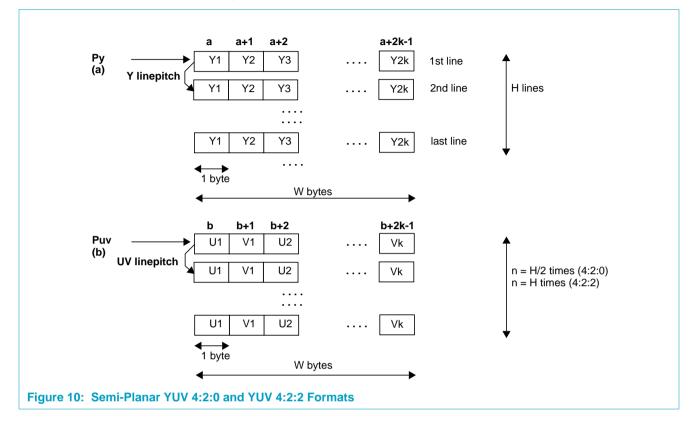

| 3.5   | Planar YUV 4:2:0 and YUV 4:2:2 Formats 28-6 |

| 3.5.1 | Planar Variants 28-6                        |

## Chapter 29: Endian Mode

| 1.               | Introduction                                           |

|------------------|--------------------------------------------------------|

| 1.1              | Features                                               |

| 2.               | Functional Description                                 |

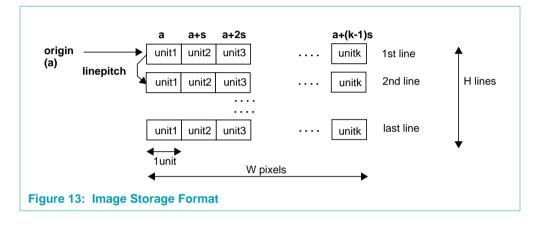

| 2.1              | Endian Mode System Block Diagram 29-2                  |

| 3.               | Endian Mode Theory 29-4                                |

| 3.1              | Law 1: The "CPU Rule" 29-4                             |

| 3.2              | Law 2: The "DMA Convention Rule"                       |

|                  |                                                        |

| 4.               | PNX15xx Series Endian Mode Architecture                |

| 4.               | PNX15xx Series Endian Mode Architecture<br>Details29-7 |

| <b>4.</b><br>4.1 |                                                        |

|                  | Details29-7                                            |

| 4.1              | Details29-7<br>Global Endian Mode                      |

| 4.1<br>4.2       | Details 29-7<br>Global Endian Mode                     |

### Chapter 30: DCS Network

| 2. | Functional Description |  |

|----|------------------------|--|

|----|------------------------|--|

| 3.  | Register Descriptions |

|-----|-----------------------|

| 3.1 | Register Tables25-8   |

|     |                       |

|     |                       |

|     |                       |

Modes of Operation ......25-4

2.1.9

2.1.10

| 2.3.1 | Arbiter Startup Behavior        |

|-------|---------------------------------|

| 3.    | <b>Operation</b>                |

| 3.1   | Clock Programming26-6           |

| 3.2   | Register Programming Guidelines |

| 4.    | Register Descriptions26-7       |

| 4.1   | Register Table                  |

| 1.1.2 | Module Powerdown Sequence              |

|-------|----------------------------------------|

| 1.1.3 | Peripheral Module Wakeup Sequence 27-2 |

| 1.1.4 | TM3260 Powerdown Modes                 |

| 1.1.5 | SDRAM Controller27-3                   |

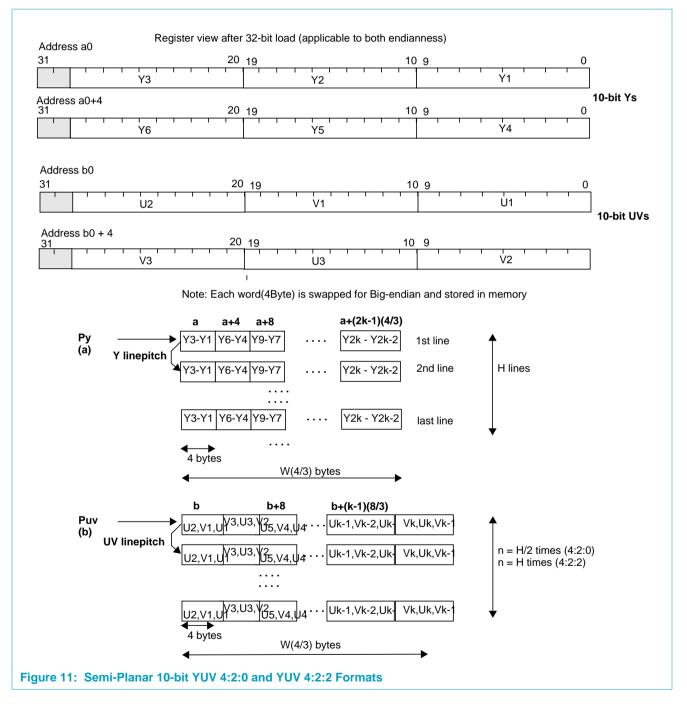

| 3.5.2 | Semi-Planar 10-Bit YUV 4:2:2 and 4:2:0 Formats 28-9 |

|-------|-----------------------------------------------------|

| 3.5.3 | Packed 10-bit YUV 4:2:2 format                      |

| 4.    | Universal Converter                                 |

| 5.    | Alpha Value and Pixel Transparency28-11             |

| 6.    | RGB and YUV Values                                  |

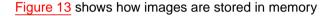

| 7.    | Image Storage Format                                |

| 8.    | System Endian Mode                                  |

|       |                                                     |

| 5.    | Example: Audio In—Programmer's View 29-<br>9 |

|-------|----------------------------------------------|

| 6.    | Implementation Details                       |

| 6.1   | PMAN Network Endian Block Diagram 29-10      |

| 6.2   | DMA Across a DTL Interface                   |

| 6.2.1 | DTL Data Ordering Rules                      |

| 6.2.2 | Address Invariant Data Ordering Rules 29-12  |

| 6.3   | Data Transfers Across the DCS Network 29-12  |

| 6.4   | DMA Across the MTL Bus                       |

| 6.5   | DTL-to-MTL Adapters                          |

| 6.6   | PCI Interface                                |

| 7.    | Detailed Example                             |

| 1.    | Introduction                                 |

2.1

2.2

## **Philips Semiconductors**

## Volume 1 of 1

| 2.3              | Programmable Timeout  |

|------------------|-----------------------|

| 2.3.1            | Arbitration           |

| 2.4              | Endian Mode           |

| 3.               | Register Descriptions |

| з.               |                       |

| <b>3.</b><br>3.1 | Register Summary      |

## Chapter 31: TM3260 VLIW CPU

| 1. | Introduction         |

|----|----------------------|

| 1  | Data sheet status    |

| 2. | Definitions          |

| 3. | Disclaimers          |

| 4. | Licenses             |

| 5. | Trademarks4          |

| 6. | Contact information4 |

## **Chapter 1: Integrated Circuit Data**

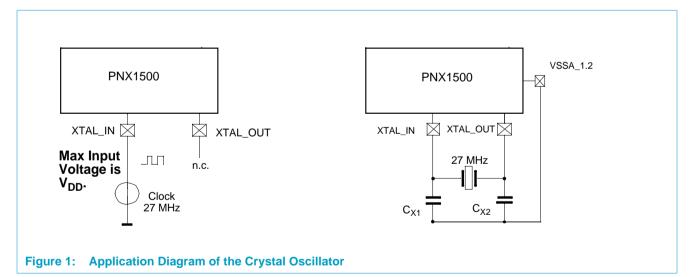

| Figure 1:  | Application Diagram of the Crystal Oscillator                        |

|------------|----------------------------------------------------------------------|

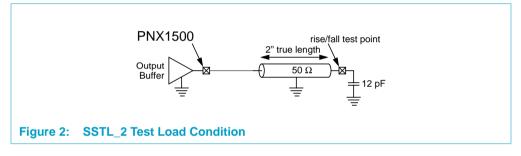

| Figure 2:  | SSTL_2 Test Load Condition1-27                                       |

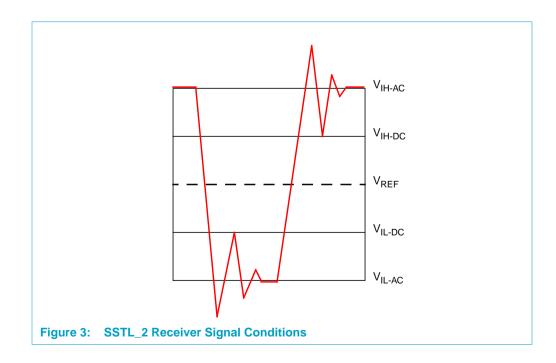

| Figure 3:  | SSTL_2 Receiver Signal Conditions                                    |

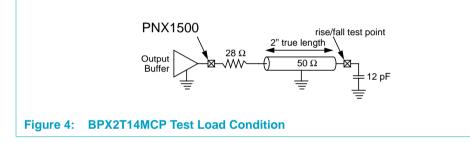

| Figure 4:  | BPX2T14MCP Test Load Condition                                       |

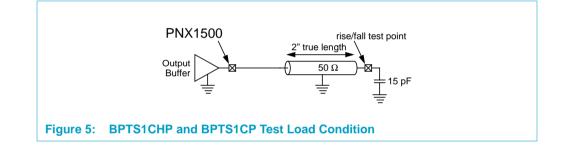

| Figure 5:  | BPTS1CHP and BPTS1CP Test Load Condition1-29                         |

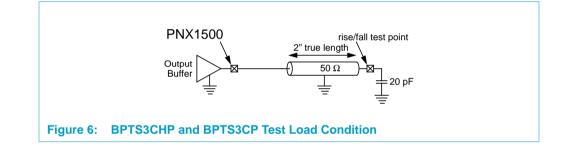

| Figure 6:  | BPTS3CHP and BPTS3CP Test Load Condition1-30                         |

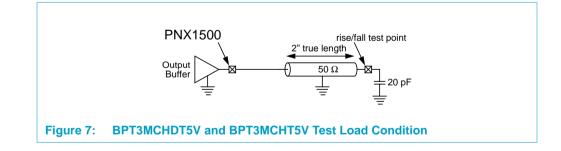

| Figure 7:  | BPT3MCHDT5V and BPT3MCHT5V Test Load Condition1-31                   |

| Figure 8:  | PCI Tval(min) and Slew Rate Test Load Condition                      |

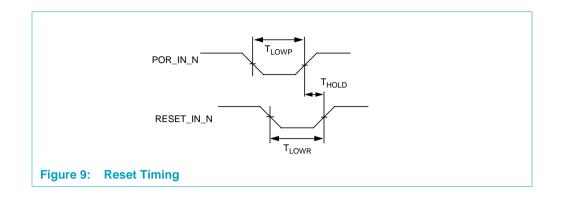

| Figure 9:  | Reset Timing1-33                                                     |

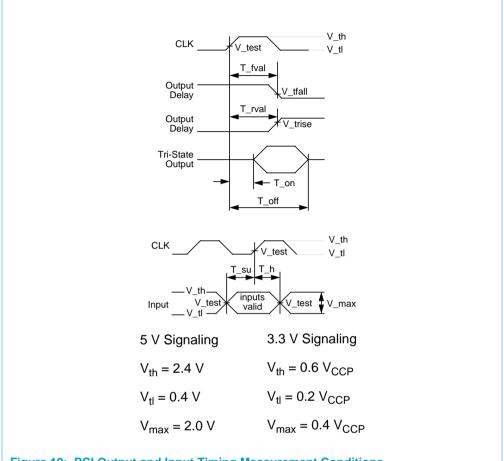

| Figure 10: | PCI Output and Input Timing Measurement Conditions                   |

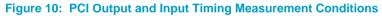

| Figure 11: | PCI Tval(max) Rising and Falling Edge1-35                            |

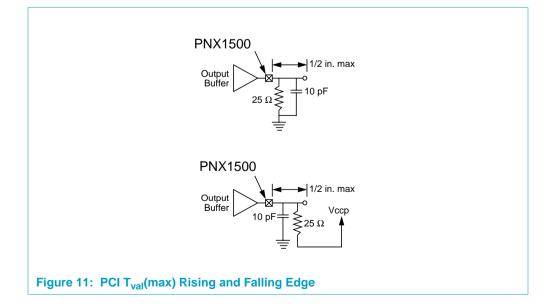

| Figure 12: | QVCP and FGPO I/O Timing1-37                                         |

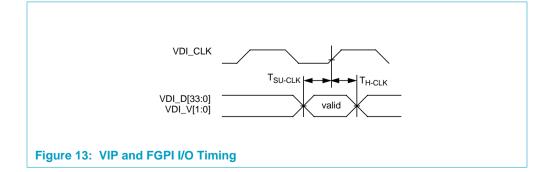

| Figure 13: | VIP and FGPI I/O Timing1-37                                          |

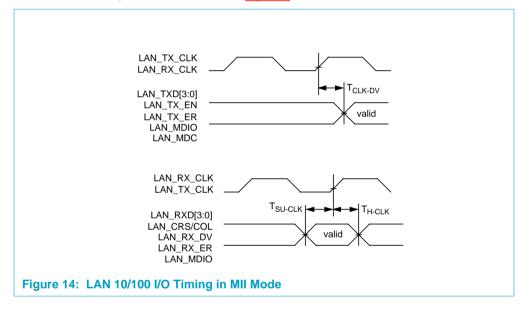

| Figure 14: | LAN 10/100 I/O Timing in MII Mode                                    |

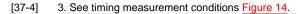

| Figure 15: | LAN 10/100 I/O Timing in RMII Mode                                   |

| Figure 16: | Audio Input I/O Timing                                               |

| Figure 17: | Audio Output I/O Timing                                              |

| Figure 18: | SPDIF I/O Timing                                                     |

| Figure 19: | I2C I/O Timing                                                       |

| Figure 20: | I2C I/O Timing                                                       |

| Figure 21: | Audio Output I/O Timing                                              |

| Figure 22: | JTAG I/O Timing                                                      |

| Figure 23: | BGA456 Plastic Ball grid Array; 456 Balls; body 27 x 27 x 1.75 mm    |

| Figure 24: | BGA Bottom View Pin Assignment                                       |

| Figure 25: | BGA Top View Pin Assignment1-47                                      |

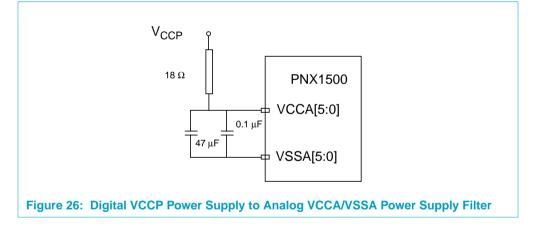

| Figure 26: | Digital VCCP Power Supply to Analog VCCA/VSSA Power Supply Filter    |

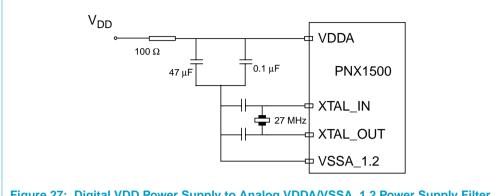

| Figure 27: | Digital VDD Power Supply to Analog VDDA/VSSA_1.2 Power Supply Filter |

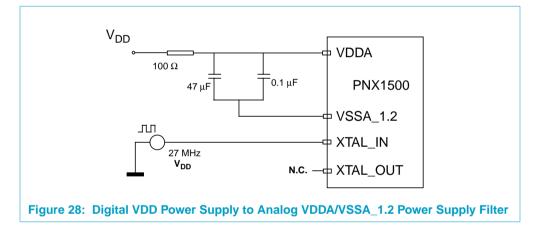

| Figure 28: | Digital VDD Power Supply to Analog VDDA/VSSA_1.2 Power Supply Filter |

### **Chapter 2: Overview**

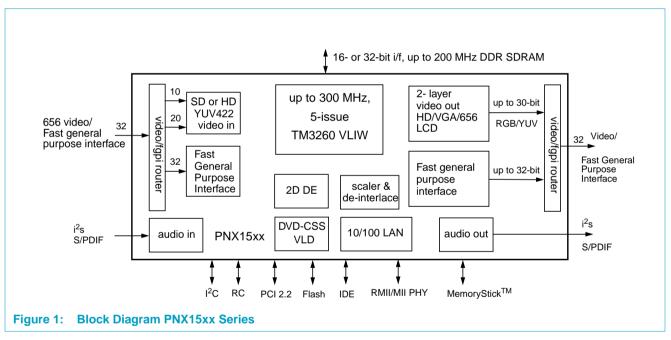

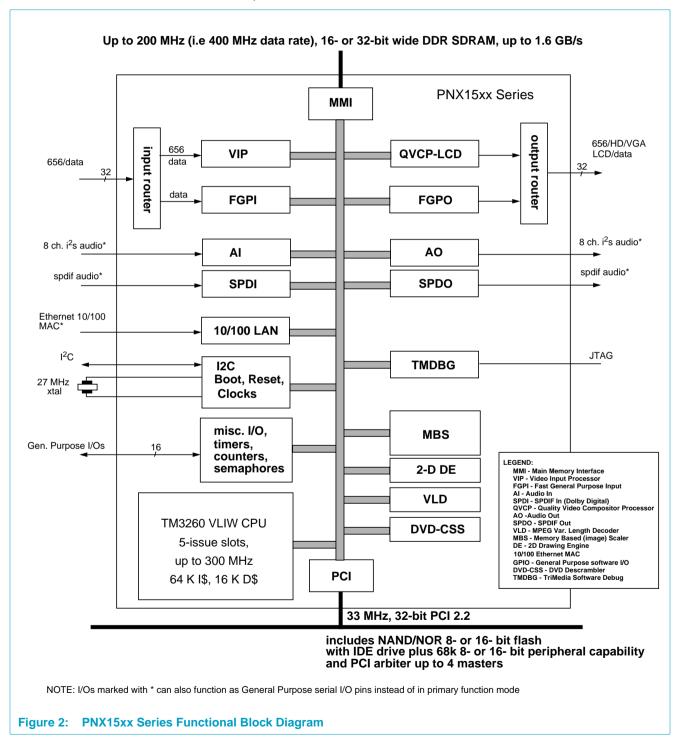

| Figure 1: | Block Diagram PNX15xx Series            | . 2-1 |

|-----------|-----------------------------------------|-------|

| Figure 2: | PNX15xx Series Functional Block Diagram | .2-5  |

### **Chapter 3: System On Chip Resources**

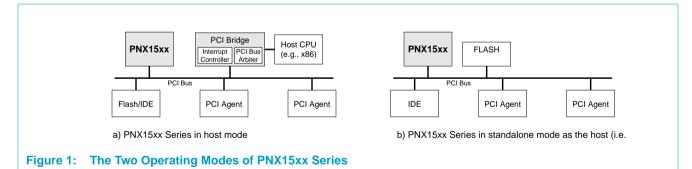

| Figure 1: | The Two Operating Modes of PNX15xx Series |

|-----------|-------------------------------------------|

| Figure 2: | PNX15xx Series System Memory Map          |

| Figure 3: | Simplified Internal Bus Infrastructure    |

### **Chapter 4: Reset**

| Figure 1: | Reset Module Block Diagram4-3         |  |

|-----------|---------------------------------------|--|

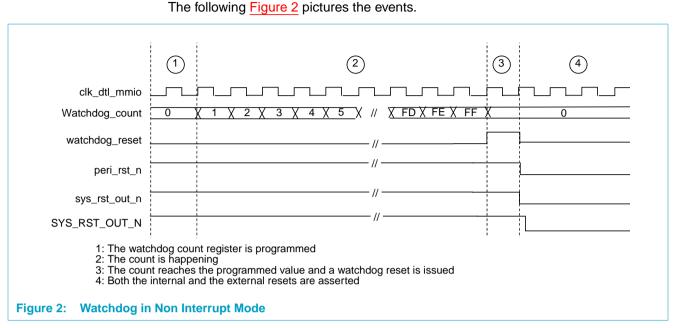

| Figure 2: | Watchdog in Non Interrupt Mode4-5     |  |

| Figure 3: | Watchdog in Interrupt Mode4-6         |  |

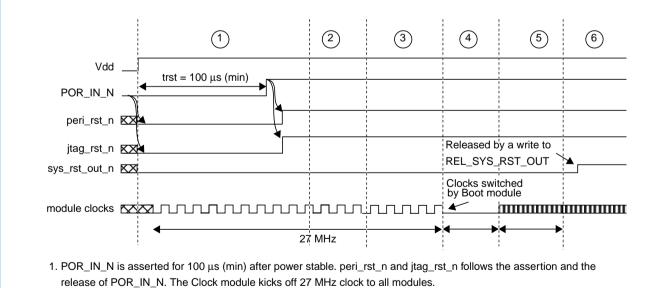

| Figure 4: | POR_IN_N Timing and Reset Sequence4-7 |  |

### Chapter 5: The Clock Module

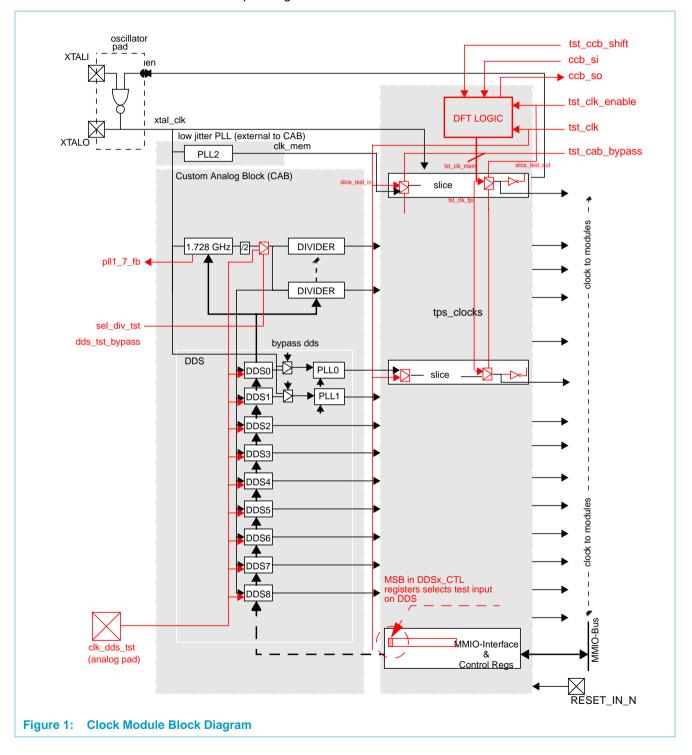

| Figure 1: | Clock Module Block Diagram5-3            |

|-----------|------------------------------------------|

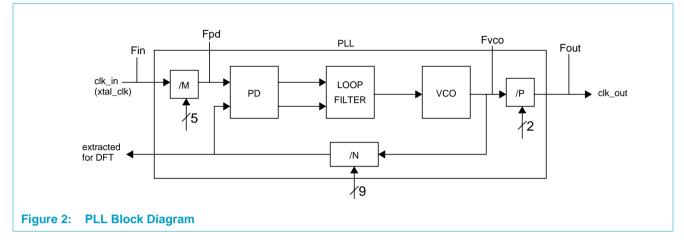

| Figure 2: | PLL Block Diagram5-8                     |

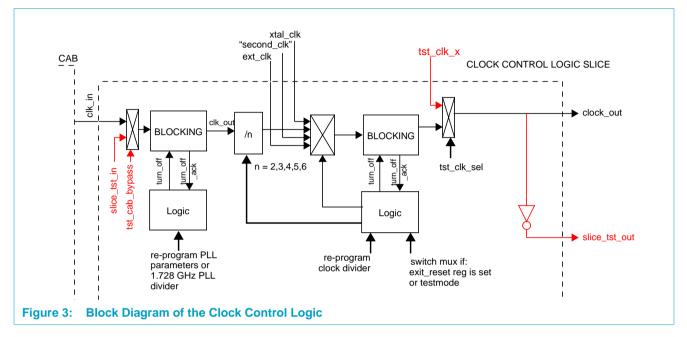

| Figure 3: | Block Diagram of the Clock Control Logic |

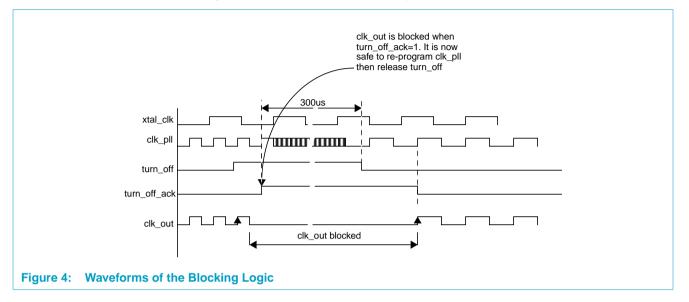

| Figure 4: | Waveforms of the Blocking Logic5-14      |

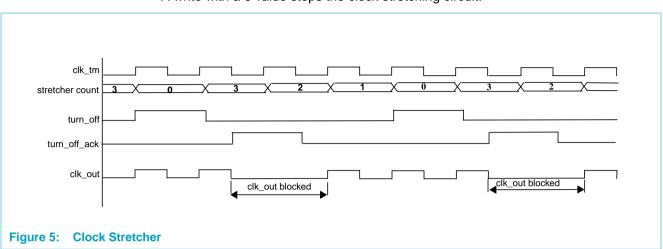

| Clock Stretcher                                                         |

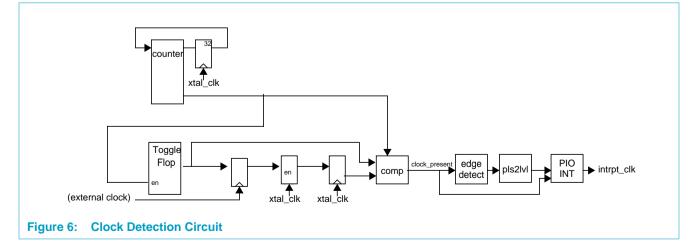

|-------------------------------------------------------------------------|

| Clock Detection Circuit                                                 |

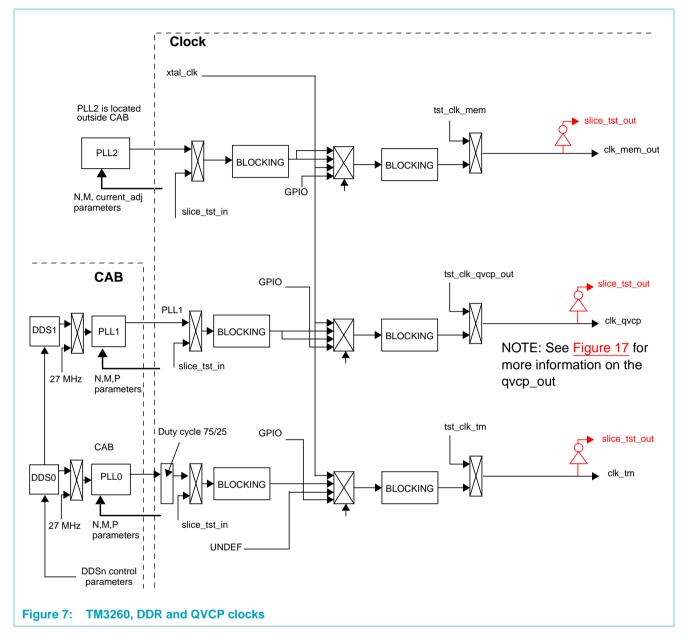

| TM3260, DDR and QVCP clocks                                             |

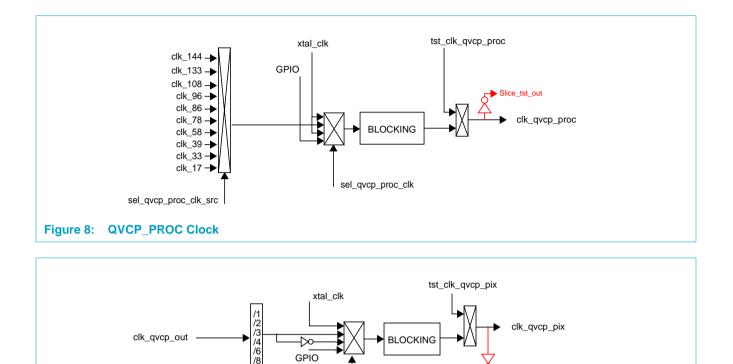

| QVCP_PROC Clock                                                         |

| QVCP_PIX Clock                                                          |

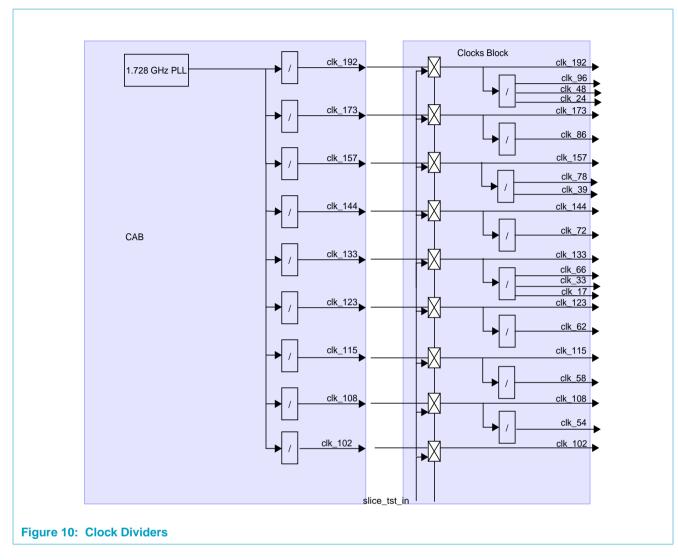

| Clock Dividers                                                          |

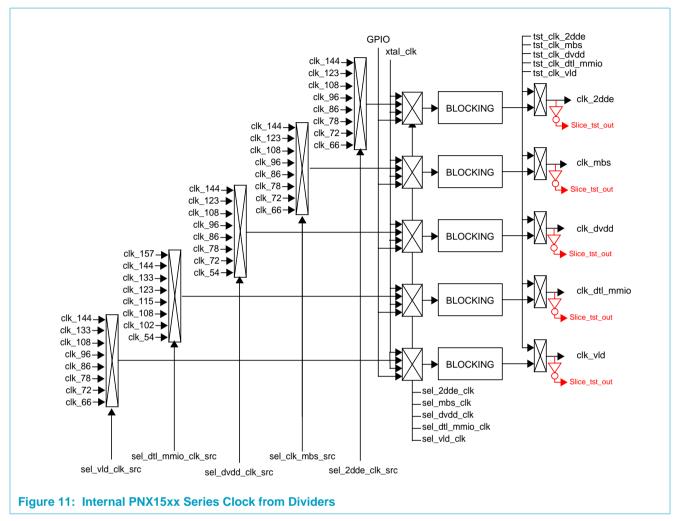

| Internal PNX15xx Series Clock from Dividers                             |

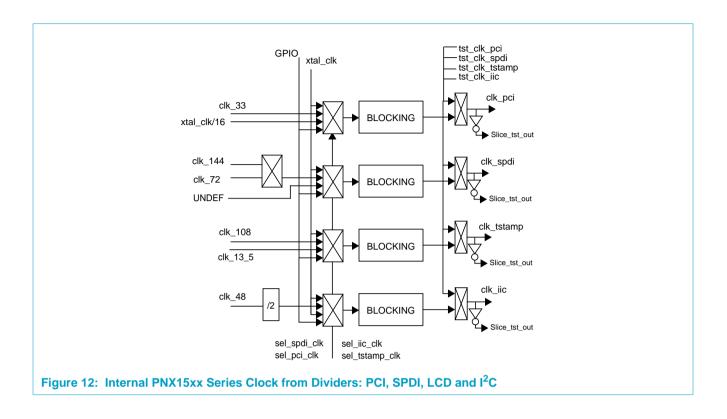

| Internal PNX15xx Series Clock from Dividers: PCI, SPDI, LCD and I2C5-25 |

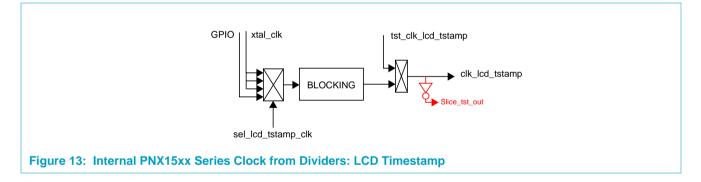

| Internal PNX15xx Series Clock from Dividers: LCD Timestamp5-25          |

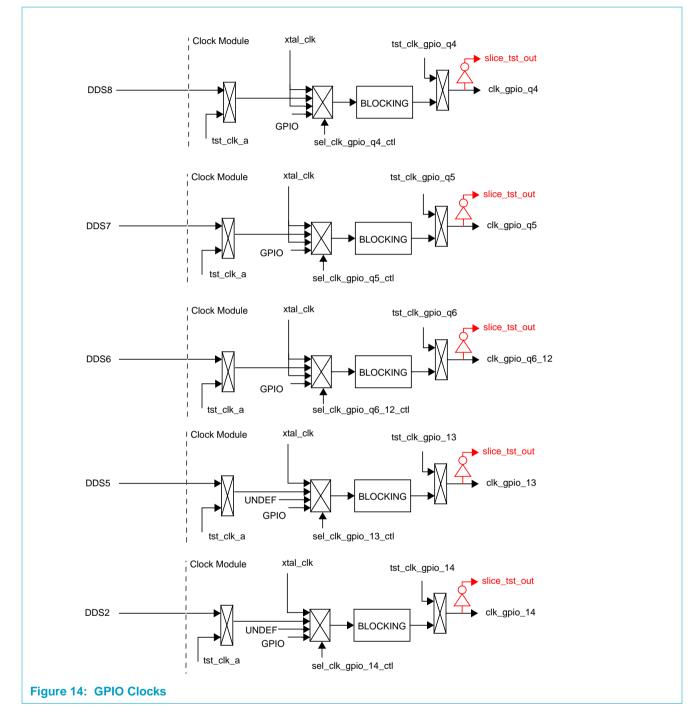

| GPIO Clocks                                                             |

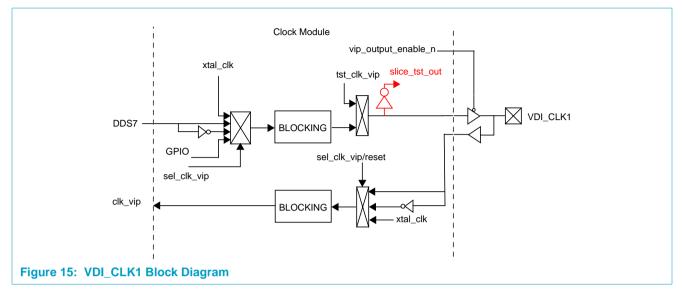

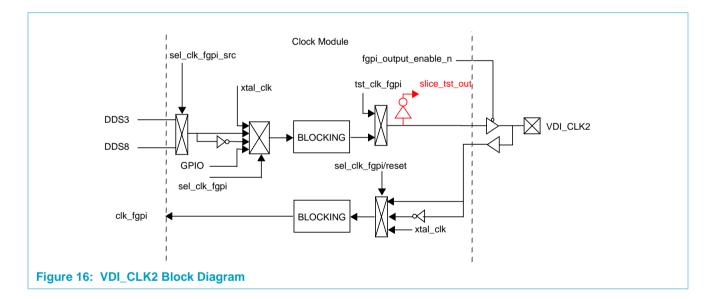

| VDI_CLK1 Block Diagram5-27                                              |

| VDI_CLK2 Block Diagram5-27                                              |

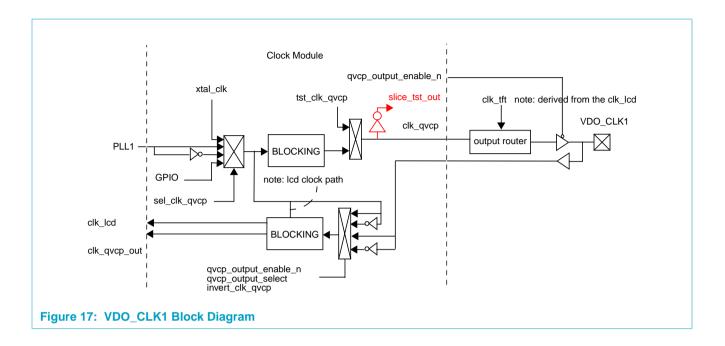

| VDO_CLK1 Block Diagram                                                  |

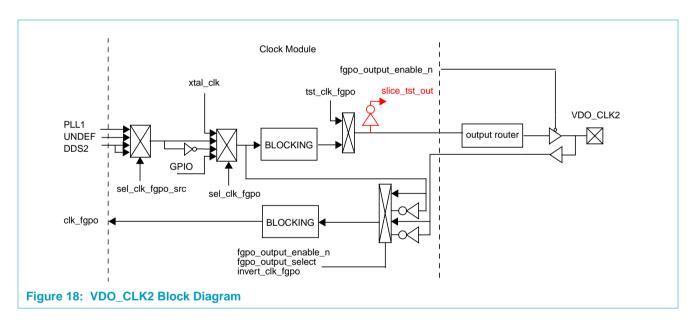

| VDO_CLK2 Block Diagram                                                  |

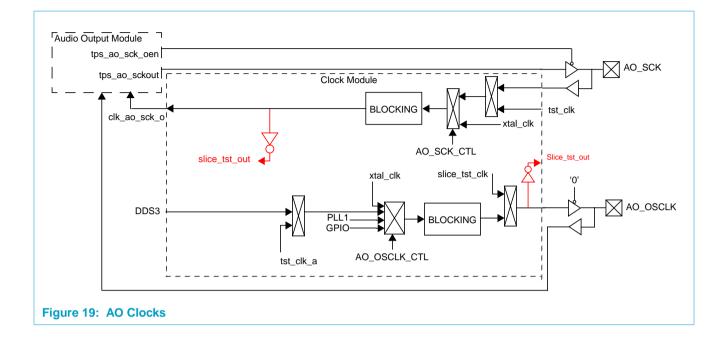

| AO Clocks                                                               |

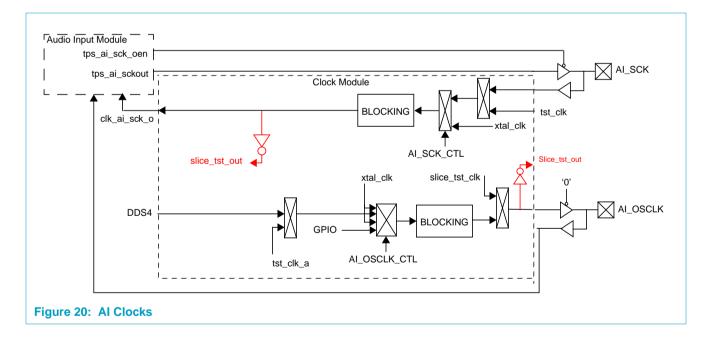

| AI Clocks                                                               |

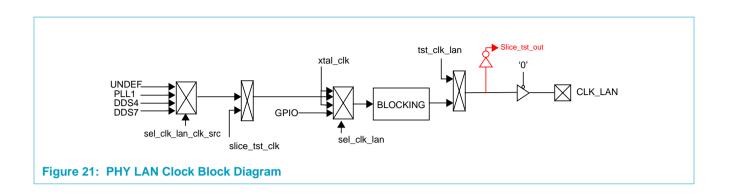

| PHY LAN Clock Block Diagram                                             |

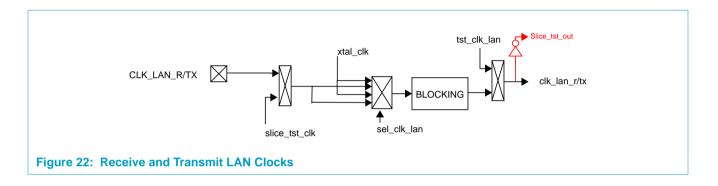

| Receive and Transmit LAN Clocks                                         |

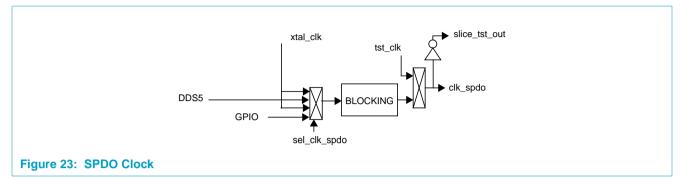

| SPDO Clock                                                              |

|                                                                         |

## **Chapter 6: Boot Module**

| Figure 1: | Boot Block Diagram                                                                            | -4 |

|-----------|-----------------------------------------------------------------------------------------------|----|

| Figure 2: | System Memory Map and Block Diagram Configuration for PNX15xx Series in Standalone Mode6-1    | 0  |

| Figure 3: | System Memory Map and Block Diagram Configuration for PNX15xx Series in Host-assisted Mode6-1 | 13 |

### **Chapter 7: PCI-XIO Module**

| Figure 1:  | Document title variable Block Diagram                |

|------------|------------------------------------------------------|

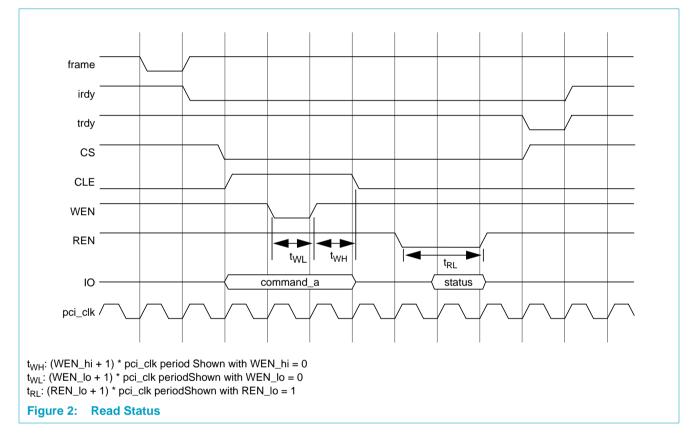

| Figure 2:  | Read Status                                          |

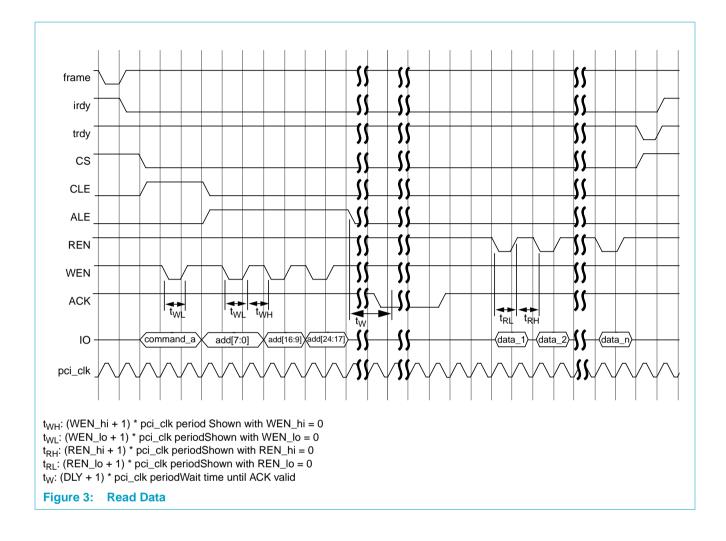

| Figure 3:  | Read Data                                            |

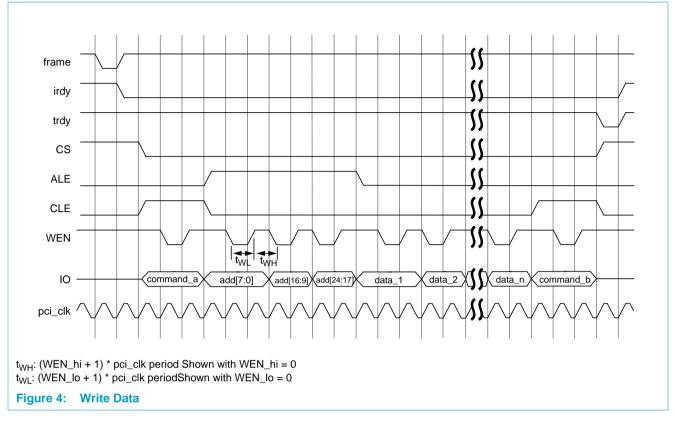

| Figure 4:  | Write Data                                           |

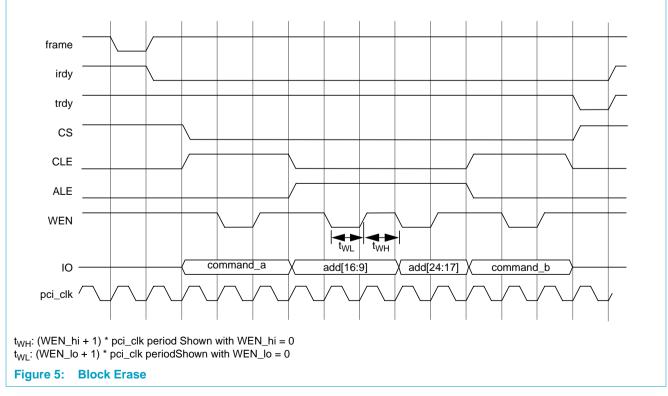

| Figure 5:  | Block Erase                                          |

| Figure 6:  | Motorola Write With DSACK                            |

| Figure 7:  | Motorola Write Without DSACK                         |

| Figure 8:  | Motorola Read                                        |

| Figure 9:  | NOR Flash Write                                      |

| Figure 10: | NOR Flash Read7-13                                   |

| Figure 11: | IDE Interface                                        |

| Figure 12: | Isolation Translation Logic                          |

| Figure 13: | Register Transfer/PIO Data Transfer on IDE           |

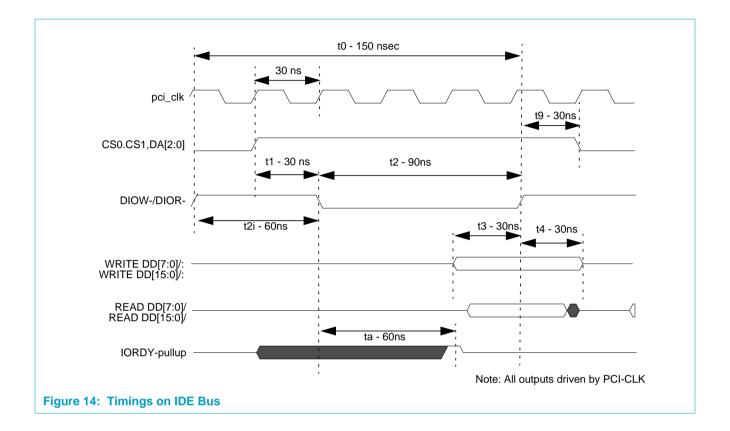

| Figure 14: | Timings on IDE Bus                                   |

| Figure 15: | IDE Transaction, Flow Controlled by Device IORDY7-18 |

## **Chapter 8: General Purpose Input Output Pins**

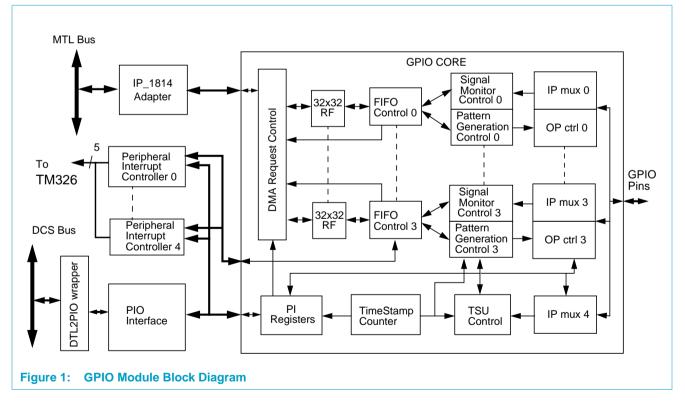

| Figure 1: | GPIO Module Block Diagram.                              | 8-2    |

|-----------|---------------------------------------------------------|--------|

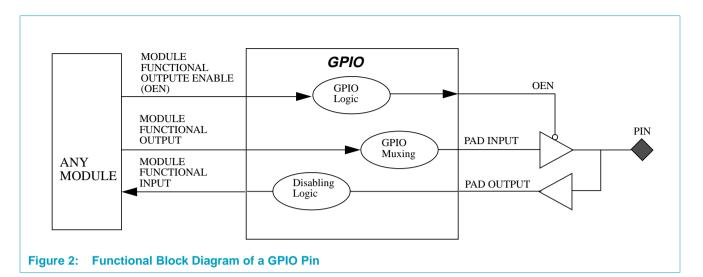

| Figure 2: | Functional Block Diagram of a GPIO Pin                  | 8-4    |

| Figure 3: | 32-bit Timestamp Format                                 | 8-7    |

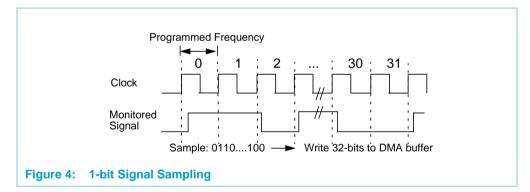

| Figure 4: | 1-bit Signal Sampling.                                  | . 8-10 |

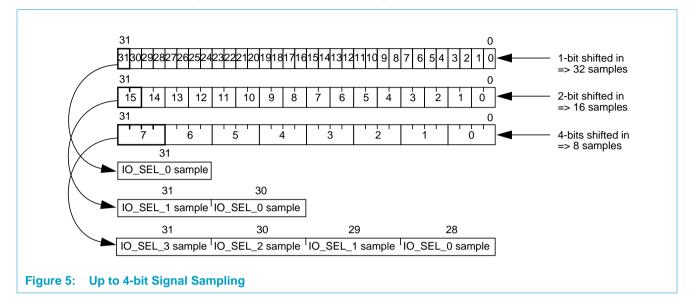

| Figure 5: | Up to 4-bit Signal Sampling                             | . 8-11 |

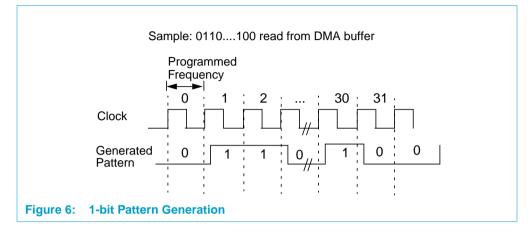

| Figure 6: | 1-bit Pattern Generation                                | . 8-13 |

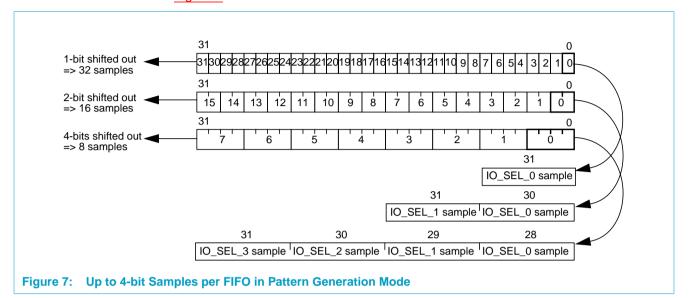

| Figure 7: | Up to 4-bit Samples per FIFO in Pattern Generation Mode | .8-14  |

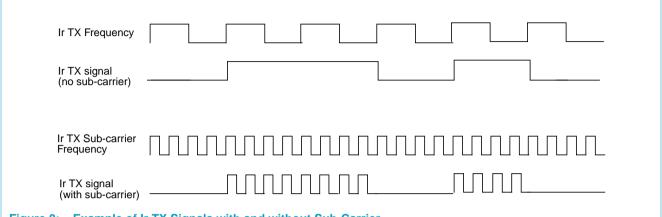

| Figure 8: | Example of Ir TX Signals with and without Sub-Carrier   | . 8-19 |

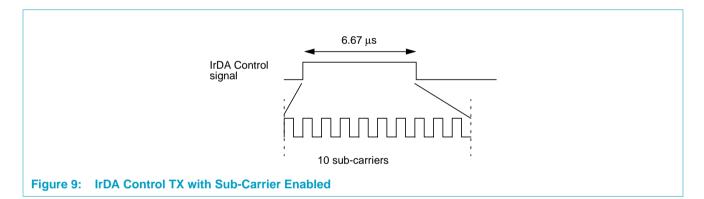

| Figure 9:  | IrDA Control TX with Sub-Carrier Enabled  | 8-19 |

|------------|-------------------------------------------|------|

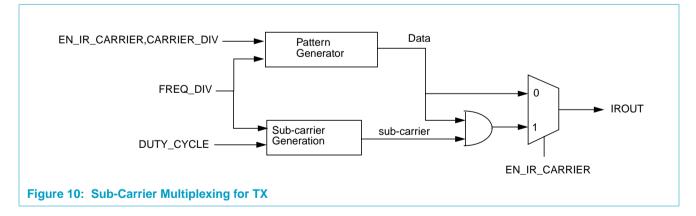

| Figure 10: | Sub-Carrier Multiplexing for TX           | 8-19 |

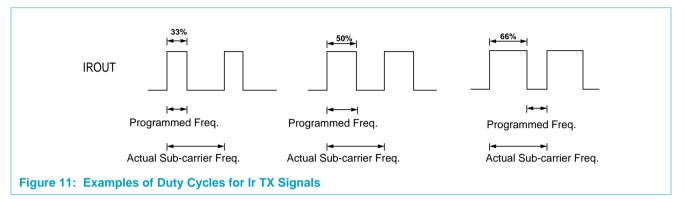

| Figure 11: | Examples of Duty Cycles for Ir TX Signals | 8-20 |

### **Chapter 9: DDR Controller**

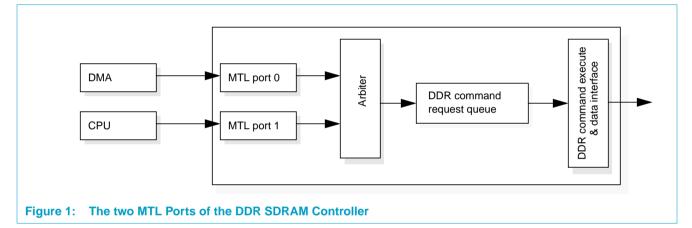

| Figure 1:  | The two MTL Ports of the DDR SDRAM Controller         |

|------------|-------------------------------------------------------|

| Figure 2:  | Arbitration in the DDR Controller                     |

| Figure 3:  | CPU account                                           |

| Figure 4:  | Arbitration when DMA has priority9-6                  |

| Figure 5:  | CPU account using dynamic ratios9-7                   |

| Figure 6:  | Address Mapping: Interleaved Mode                     |