# TOSHIBA

## **TOSHIBA CORPORATION**

Semiconductor Company

## Preface

Thank you very much for making use of Toshiba microcomputer LSI. Before using this LSI, refer to section "Points of Note and Restrictions". Especially, take care below cautions.

#### \*\*CAUTION\*\*

#### How to release the HALT mode

Usually, interrupts can release all halts stats. However, the interrupts = ( $\overline{\text{NMI}}$ , INT0, INTRTC), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 5 clocks of f<sub>FPH</sub>) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interupt request is kept on hold internally.)

If another interupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

20070701-EN

## CMOS 16-Bit Microcontrollers TMP91FW27UG / TMP91FW27FG

### 1. Outline and Features

TMP91FW27 is a high-speed 16-bit microcontroller designed for the control of various mid-to large-scale equipment.

TMP91FW27UG and TMP91FW27FG come in a 64-pin flat package. Listed below are the features.

- (1) High-speed 16-bit CPU (900/L1 CPU)

- Instruction mnemonics are upward-compatible with TLCS-90/900

- 16 Mbytes of linear address space

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

- Micro DMA: 4 channels (593 ns /2 bytes at 27 MHz)

- (2) Minimum instruction execution time: 148 ns (at 27/MHz)

- (3) Built-in RAM: 12 Kbytes

Built-in ROM: 128-Kbyte Flash memory

4-Kbyte mask ROM (used for booting)

#### **RESTRICTIONS ON PRODUCT USE**

• The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

This product uses the Super Flash® technology under the license of Silicon Storage Technology,Inc. Super Flash® is a registered trademark of Silicon Storage Technology,Inc.

- (4) External memory expansion

- Expandable up to 16 Mbytes (shared program/data area)

- Can simultaneously support 8-/16-bit width external data bus (Dynamic data bus sizing)

- (5) 8-bit timers: 6 channels

- (6) 16-bit timers: 1 channel

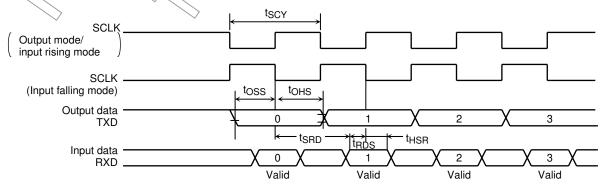

- (7) General-purpose serial interface: 2 channels

- UART/Synchronous mode: 2 channels

- IrDA Ver.1.0 (115.2 kbps) mode selectable: 1 channel

- (8) Serial bus interface: 1 channel

- I<sup>2</sup>C bus mode/clock synchronous mode selectable

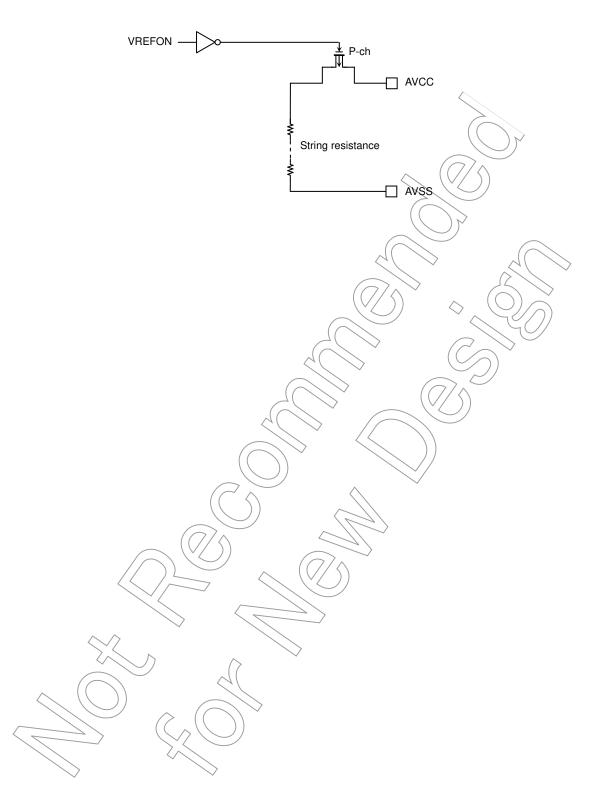

- (9) 10-bit AD converter (sample hold circuit is inside): 4 channels

- (10) Watchdog timer

- (11) Special timer for CLOCK

- (12) Chip select/Wait controller: 4 blocks

- (13) Interrupts: 34 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 21 internal interrupts: 7 priority levels are selectable

- 4 external interrupts: 7 priority levels are selectable (among 3 interrupts are selectable edge mode)

- (14) Input/output ports: 53 pins

- (15) Stand-by function

- Three Halt modes: IDLE2 (programmable), IDLE1 and STOP

- (16) Clock controller

- Clock gear function: Select a High-frequency clock fc to fc/16

- Special timer for CLOCK (fs = 32/768 kHz)

- (17) Operating voltage

- Vcc = 2.7 V to 3.6 V (fc max = 27 MHz, flash memory read operation)

- Vcg = 2.2 V to 3.6 V (fc max = 16 MHz, flash memory read operation)

- $V_{cc} = 2.7 \text{ V}$  to 3.6 V (fc max = 27 MHz, flash memory erase/program operations)

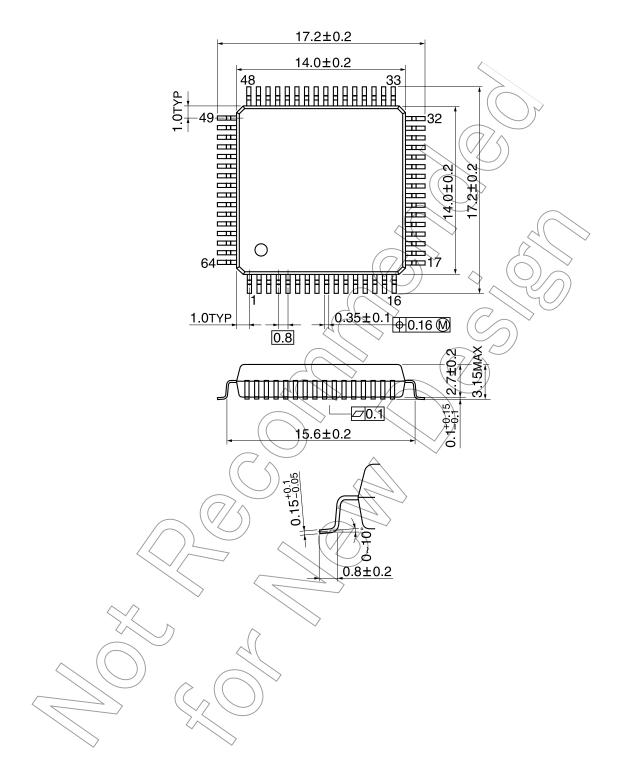

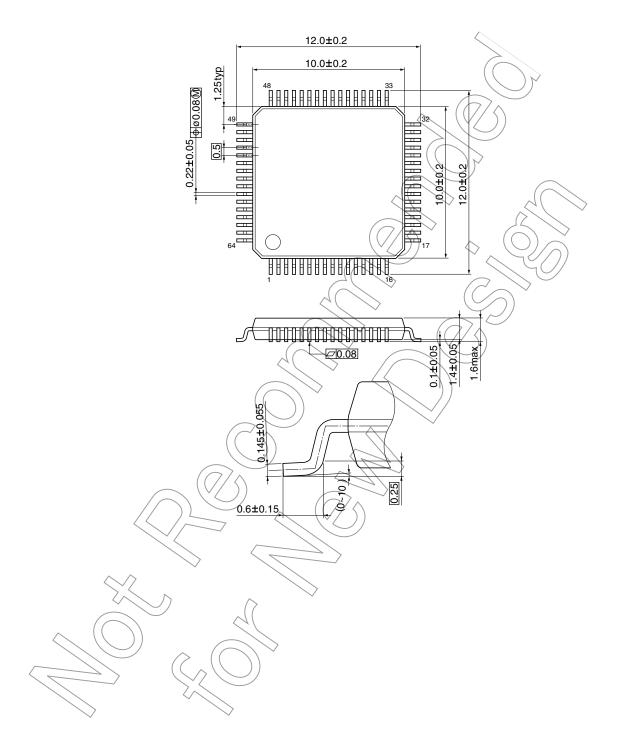

(18)Package

- LQFP64-P-1010-0.50D (TMP91FW27UG)

- QFP64-P-1414-0.80A (TMP91FW27FG)

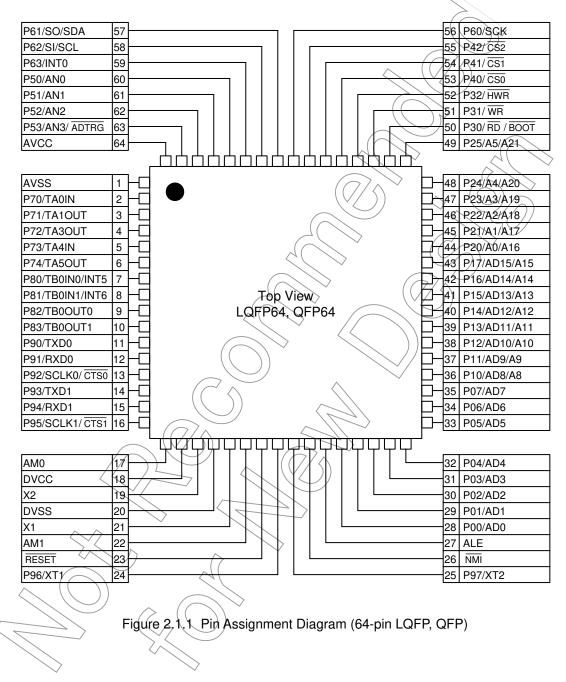

## 2. Pin Assignment and Pin Functions

The assignment of input/output pins for the TMP91FW27, their names and functions are as follows:

#### 2.1 Pin Assignment Diagram

Figure 2.1.1 shows the pin assignment of the TMP91FW27UG and TMP91FW27FG.

## 2.2 Pin Names and Functions

The names of the input/output pins and their functions are described below. Table 2.2.1 and Table 2.2.2 show Pin names and functions.

| Pin Names   | Number of<br>Pins         | I/O       | Functions                                                                                                                                                                                                                       |

|-------------|---------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00 to P07  | 8                         | I/O       | Port 0: I/O port that allows I/O to be selected at the bit level                                                                                                                                                                |

| AD0 to AD7  |                           | I/O       | Address data (lower): 0 to 7 of address/data bus                                                                                                                                                                                |

| P10 to P17  | 8                         | I/O       | Port1: I/O port that allows I/O to be selected at the bit level                                                                                                                                                                 |

| AD8 to AD15 |                           | I/O       | Address data (upper): 8 to 15 of address/data bus                                                                                                                                                                               |

| A8 to A15   |                           | Output    | Address: 8 to 15 of address bus                                                                                                                                                                                                 |

| P20 to P25  | 6                         | I/O       | Port 2: I/O port that allows I/O to be selected at the bit level                                                                                                                                                                |

| A0 to A5    |                           | Output    | Address: 0 to 5 of address bus                                                                                                                                                                                                  |

| A16 to A21  |                           | Output    | Address: 16 to 21 of address bus                                                                                                                                                                                                |

| P30         | 1                         | Output    | Port 30: Output Port                                                                                                                                                                                                            |

| RD          |                           | Output    | Read: Strobe signal for reading external memory<br>When read internal area also, output $\overline{RD}$ by setting to P3 <p30> = 0 and<br/>P3FC<p30f> = 1.<br/>This pin sets single boot mode (only during reset).</p30f></p30> |

|             |                           |           | For the details, please refer to section 3.2,3, "Operation modes".                                                                                                                                                              |

| P31         | 1                         | Output    | Port 31: Qutput port                                                                                                                                                                                                            |

| WR          |                           | Output    | Write: Strobe signal for writing data to pins AD0 to AD7                                                                                                                                                                        |

| P32         | 1                         | I/O       | Port 32: I/O port (with pull-up resistor)                                                                                                                                                                                       |

| HWR         |                           | Output    | High Write: Strobe signal for writing data to pins AD8 to AD15                                                                                                                                                                  |

| P40         | 1                         | I/O       | Port 40: I/O port (with pull-up resistor)                                                                                                                                                                                       |

| CS0         |                           | Output    | Chip select 0: Outputs "0" when address is within specified address area.                                                                                                                                                       |

| P41         | 1                         | I/O ((    | Port41: I/O port (with pull-up resistor)                                                                                                                                                                                        |

| CS1         |                           | Output    | Chip select 1: Outputs "0" when address is within specified address area.                                                                                                                                                       |

| P42         | 1                         | I/Q (     | Port 42: I/O port (with pull-up resistor)                                                                                                                                                                                       |

| CS2         |                           | Output )  | Chip select 2: Outputs "0" when address is within specified address area.                                                                                                                                                       |

| P50 to P53  | 4                         | Input     | Port 5: Input port                                                                                                                                                                                                              |

| AN0 to AN3  |                           | ( (Input) | Analog input: Analog input pins of the AD converter                                                                                                                                                                             |

| ADTRG       |                           | Input     | AD trigger Pin used to request AD start (shared with P53).                                                                                                                                                                      |

| P60         | /1                        | 149       | Rort 60: I/O port)                                                                                                                                                                                                              |

| SCK         |                           | 1/0       | Serial bus interface clock I/O at SIO mode                                                                                                                                                                                      |

| P61         | 1                         | 10        | Port 61: 1/O port                                                                                                                                                                                                               |

| SO          | ~                         | Output    | Serial bus interface send data at SIO mode                                                                                                                                                                                      |

| SDA         |                           | I/O       | Serial bus interface send/receive data at I <sup>2</sup> C mode                                                                                                                                                                 |

|             | $\langle \rangle \rangle$ | $\land$   | Open-drain output mode by programmable                                                                                                                                                                                          |

| P62         | 1                         | I/O 📈 (   | Port 62: I/O port                                                                                                                                                                                                               |

| SI 🔨 ((     |                           | Input     | Serial bus interface receive data at SIO mode                                                                                                                                                                                   |

| SCL         |                           | 1/0       | Serial bus interface clock I/O at I <sup>2</sup> C mode                                                                                                                                                                         |

|             |                           |           | Open-drain output mode by programmable                                                                                                                                                                                          |

| P63         | - 1                       |           | Port 63: I/O port (Schmitt input)                                                                                                                                                                                               |

| INT0        |                           |           | Interrupt request pin 0: Interrupt request pin with level/ rising/falling edge                                                                                                                                                  |

| P70         | 1                         | 1/0       | Port 70: I/O port                                                                                                                                                                                                               |

| TAOIN       |                           | Input     | 8-bit timer 0 input: Input pin of 8-bit timer TMRA0                                                                                                                                                                             |

| P71         | 1                         | I/O       | Port 71: I/O port                                                                                                                                                                                                               |

| TA1OUT      |                           | Output    | 8-bit timer 1 output: Output pin of 8-bit timer TMRA0 or TMRA1                                                                                                                                                                  |

| P72         | 1                         | I/O       | Port 72: I/O port                                                                                                                                                                                                               |

| TA3OUT      |                           | Output    | 8-bit timer 3 output: Output pin of 8-bit timer TMRA2 or TMRA3                                                                                                                                                                  |

Table 2.2.1 Pin Names and Functions (1/2)

| Pin Names   | Number of<br>Pins | I/O                           | Functions                                                                          |

|-------------|-------------------|-------------------------------|------------------------------------------------------------------------------------|

| P73         | 1                 | I/O                           | Port 73: I/O port                                                                  |

| TA4IN       |                   | Input                         | 8-bit timer 4 Input: Input pin of 8-bit timer TMRA4                                |

| P74         | 1                 | I/O                           | Port 74: I/O port                                                                  |

| TA5OUT      |                   | Output                        | 8-bit timer 5 output: Output pin of 8-bit timer /MRA4 or TMRA5                     |

| P80         | 1                 | I/O                           | Port 80: I/O port                                                                  |

| TB0IN0      |                   | Input                         | 16-bit timer 0 Input 0: Input of count/capture-trigger in 16-bit timer TMRB0       |

| INT5        |                   | Input                         | Interrupt request pin 5: Interrupt request pin/with selectable rising/falling edge |

| P81         | 1                 | I/O                           | Port 81: I/O port                                                                  |

| TB0IN1      |                   | Input                         | 16-bit timer 0 Input 1: Input of count/capture trigger in 16-bit timer TMRB0       |

| INT6        |                   | Input                         | Interrupt request pin 6: Interrupt request pin of rising edge                      |

| P82         | 1                 | I/O                           | Port 82: I/O port                                                                  |

| TB0OUT0     |                   | Output                        | 16-bit timer 0 output 0: Outpit pin of 16-bit timer TMRB0                          |

| P83         | 1                 | I/O                           | Port 83: I/O port                                                                  |

| TB0OUT1     |                   | Output                        | 16-bit timer 0 output 1: Output pin of 16-bit timer TMRB0                          |

| P90         | 1                 | I/O                           | Port 90: I/O port                                                                  |

| TXD0        |                   | Output                        | Serial 0 send data: Open-drain output pin by programmable                          |

| P91         | 1                 | I/O                           | Port 91: I/O port                                                                  |

| RXD0        |                   | Input                         | Serial 0 receive data                                                              |

| P92         | 1                 | I/O                           | Port 92: I/O port                                                                  |

| SCLK0       |                   | I/O                           | Serial O clock I/O                                                                 |

| CTS0        |                   | Input                         | Serial 0 data send enable (Clear to send)                                          |

| P93         | 1                 | I/O                           | Port 93: I/O port                                                                  |

| TXD1        |                   | Output                        | Serial 1 send data: Open-drain output pin by programmable                          |

| P94         | 1                 | I/O ((                        | Port 94: 1/O port                                                                  |

| RXD1        |                   | Input                         | Serial 1 receive data                                                              |

| P95         | 1                 | 1/0                           | Port 95: I/O port                                                                  |

| SCLK1       |                   | I/Q (                         | Serial 1 clock I/O                                                                 |

| CTS1        |                   | Input                         | Serial 1 data send enable (Clear to send)                                          |

| P96         | 1                 | $(\mathcal{P} )$              | Port 96: I/O port. Open-drain output pin.                                          |

| XT1         | 6                 | (Input)                       | Low frequency oscillator connection pin                                            |

| P97         | 1/                | )/0                           | Port 97: I/O port. Open-drain output pin.                                          |

| XT2         |                   | Output                        | Low frequency oscillator connection pin                                            |

| ALE         | 1                 | Output                        | Address latch enable (It can be set as prohibition of an output for noize          |

|             |                   | $\rightarrow$                 | reduction.)                                                                        |

| NMI         | 1                 | Input                         | Non-Maskable interrupt request pin: Interrupt request pin with programmable        |

|             | ZA A              |                               | falling edge level or with both edge levels programmable (Schmitt input).          |

| AM0 and AM1 | 2                 | Input                         | Operation mode:                                                                    |

| ((          |                   |                               | Fixed to AM1 = "1" and AM0 = "1".                                                  |

| RESET       |                   | Input                         | Reset: Initialize LSI. (Schmitt input, with pull-up resistor)                      |

| AVCC        | 1                 | $\langle (() \rangle \rangle$ | Pin used to both power supply pin for AD converter and standard power supply       |

|             | $\geq$            | $\bigvee \bigvee$             | for AD converter (H).                                                              |

| AVSS        | 1                 |                               | Pin used to both GND pin for AD converter (0 V) and standard power supply          |

| $\sim$      |                   | $\searrow$                    | pin for AD converter (L).                                                          |

| X1/X2       | 2                 | I/O                           | High frequency oscillator connection pin.                                          |

| DVCC        | 1                 |                               | Power supply pins (All DVCC pins should be connected with the power                |

|             |                   |                               | Supply pin).                                                                       |

| DVSS        | 1                 |                               | GND pins (All pins shuold be connected with GND(0V).)                              |

|  | Table 2.2.2 | Pin Names and Functions (2/2) |

|--|-------------|-------------------------------|

|--|-------------|-------------------------------|

## 3. Functional Description

This section shows the hardware configuration of the TMP91FW27 and explains how it operates.

This device is a version of the created by replacing the predecessor's internal mask ROM with a 128-Kbyte internal flash memory and expanding its internal RAM size to 12 Kbytes. The configuration and the functionality of this device are the same as those of the TMP91CP27. For the functions of this device that are not described here, refer to the TMP91CP27 data sheet.

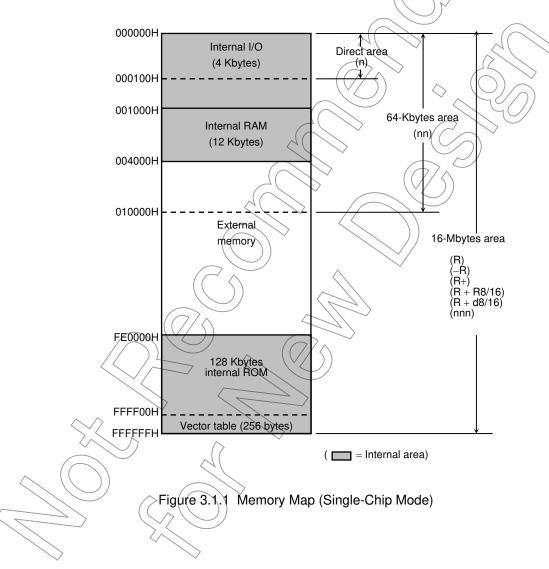

#### 3.1 Memory Map

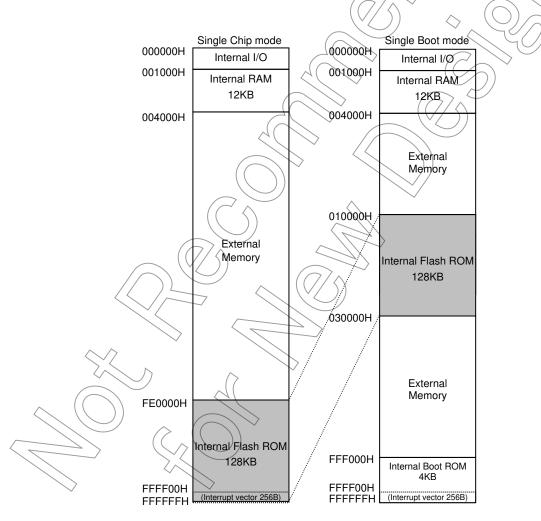

Figure 3.1.1 shows a memory map of the TMP91FW27 in single-chip mode and its memory areas that can be accessed in each addressing mode of the CPU.

#### 3.2 Flash Memory

The TMP91FW27 incorporates flash memory that can be electrically erased and programmed using a single 3V power supply.

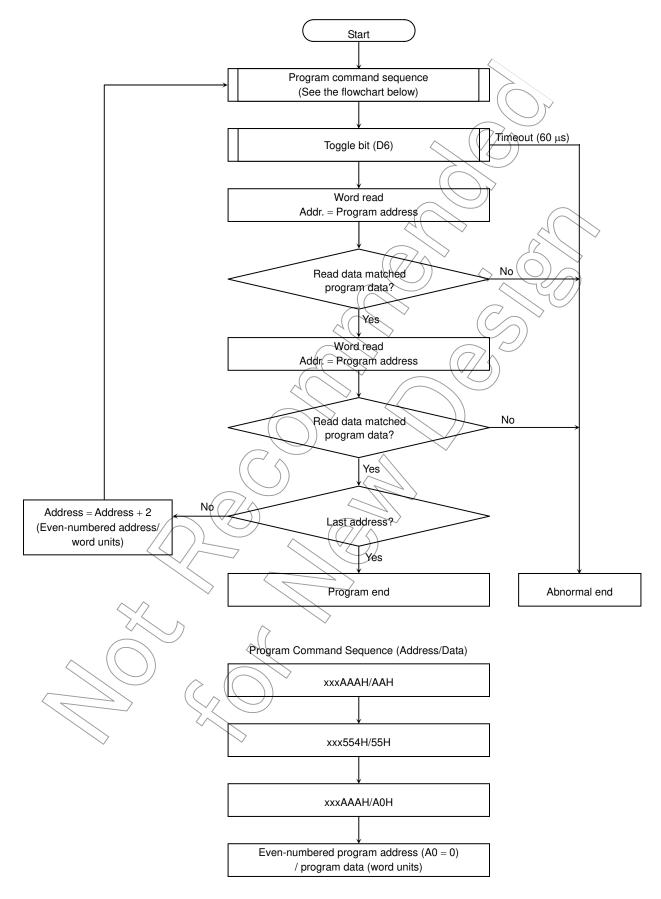

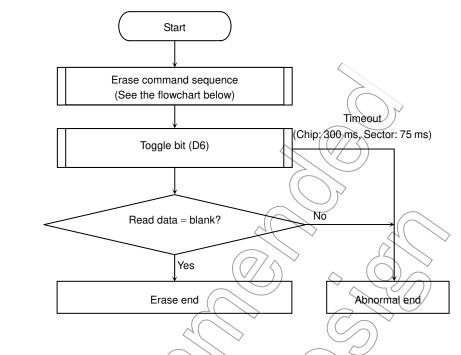

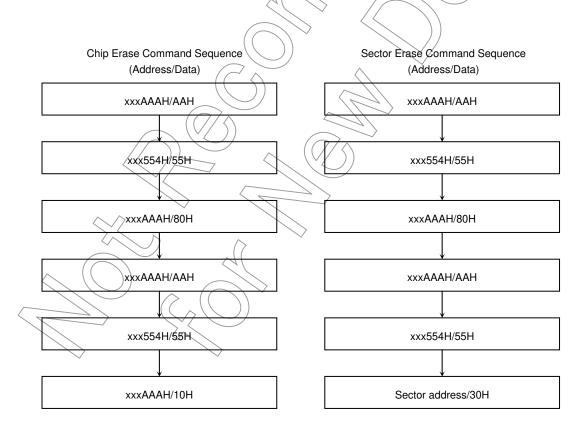

The flash memory is programmed and erased using JEDEC-standard commands. After a program or erase command is input, the corresponding operation is automatically performed internally. Erase operations can be performed by the entire chip (chip erase) or on a sector basis (sector erase).

The configuration and operations of the flash memory are described below.

#### 3.2.1 Features

- Power supply voltage for program/erase operations

Sector size

Vcc = 2.7 V to 3.6 V (-10 °C to 40 °C)

A Kbytes × 32

- Configuration 64 K × 16 bits (128 Kbytes)

- Functions Single-word programming Chip erase Sector erase Data polling/Toggle bit

- Mode control JEDEC-standard commands

Programming method

- On-board programming Parallel programmer

- Security Write protection Read protection

#### 3.2.2 Block Diagram

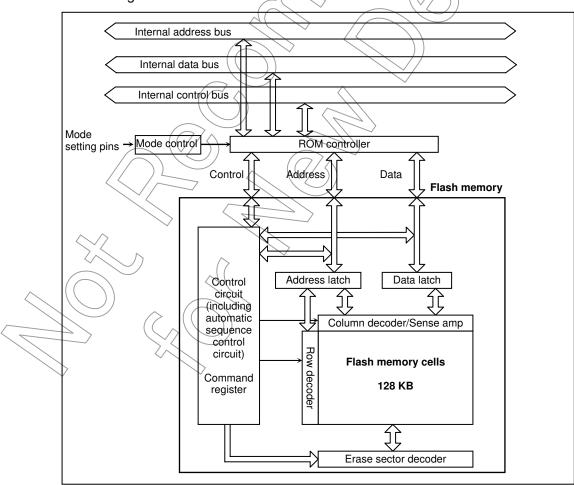

Figure 3.2.1 Block Diagram of Flash Memory Unit

#### 3.2.3 Operation Modes

#### 3.2.3.1 Overview

The following three types of operation modes are available to control program/erase operations on the flash memory.

|                               | Table 3.2.1 Description of Operation Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Mode Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

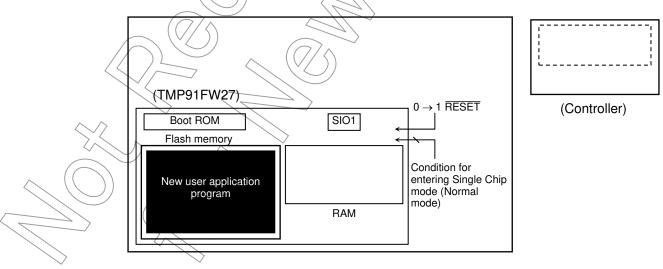

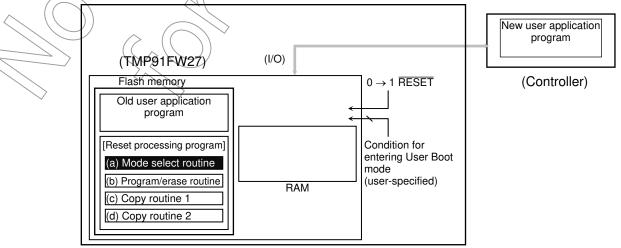

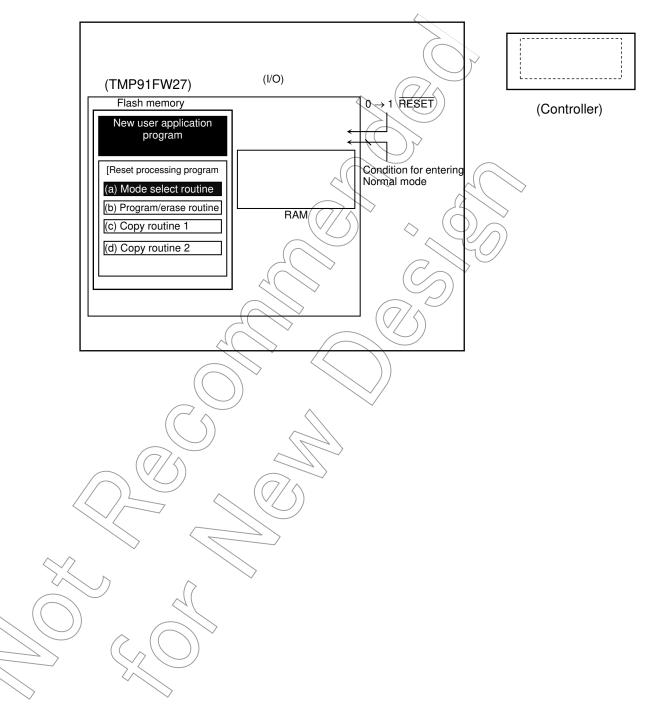

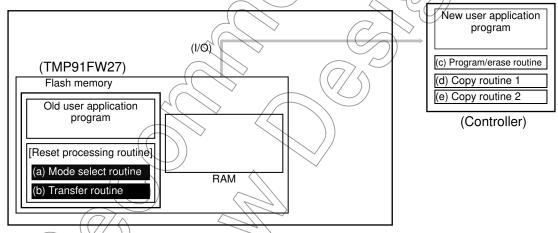

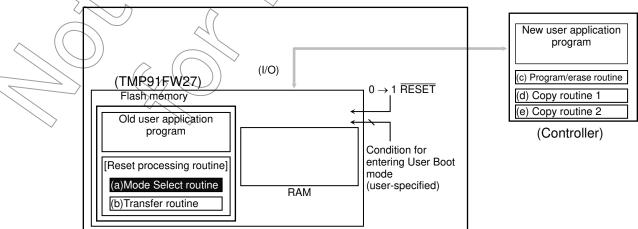

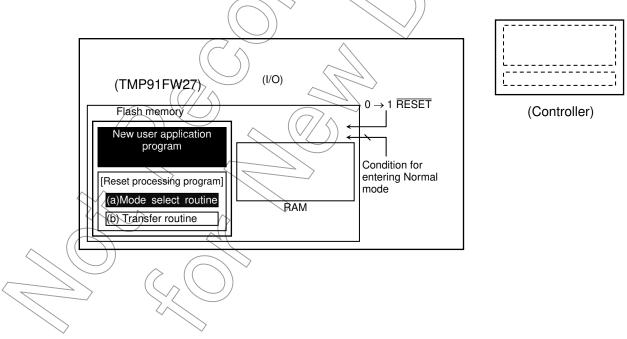

| Single Chip mode              | After reset release, the device starts up from the internal flash memory.<br>Single Chip mode is further divided into two modes: "Normal mode" is a mode in which user application<br>programs are executed, and "User Boot mode" is used to program the flash memory on-board.<br>The means of switching between these two modes can be set by the user as desired. For example, it can<br>be set so that Port $00 = "1"$ selects Normal mode and Port $00 = "0"$ selects User Boot mode. The user<br>must include a routine to handle mode switching in a user application program. |

| Normal mode<br>User Boot mode | In this mode, the device starts up from a user application program.<br>In this mode, the flash memory can be programmed by a user-specified method.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Single Boot mode              | After reset release, the device starts up from the internal boot ROM (mask ROM). The boot ROM includes<br>an algorithm which allows a program for programming/erasing the flash memory on-board via a serial port<br>to be transferred to the device's internal RAM. The transferred program is then executed in the internal<br>RAM so that the flash memory can be programmed/erased by receiving data from an external host and<br>issuing program/erase commands.                                                                                                                 |

| Programmer mode               | This mode enables the internal flash memory to be programmed/erased using a general-purpose programmer. For programmers that can be used, please contact your local Toshiba sales representative.                                                                                                                                                                                                                                                                                                                                                                                     |

## Table 3.2.1 Description of Operation Modes

Of the modes listed in Table 3.2.1, the internal flash memory can be programmed in User Boot mode, Single Boot mode and Programmer mode.

The mode in which the flash memory can be programmed/erased while mounted on the user board is defined as the on-board programming mode. Of the modes listed above, Single Boot mode and User Boot mode are classified as on-board programming modes. Single Boot mode supports Toshiba's proprietary programming/erase method using serial I/O. User Boot mode (within Single Chip mode) allows the flash memory to be programmed/erased by a user-specified method.

Programmer mode is provided with a read protect function which prohibits reading of ROM data. By enabling the read protect function upon completion of programming, the user can protect ROM data from being read by third parties.

The operation mode — Single Chip mode, Single Boot mode or Programmer mode — is determined during reset by externally setting the input levels on the AM0, AM1 and  $\overline{\text{BOOT}}$  (P30) pins.

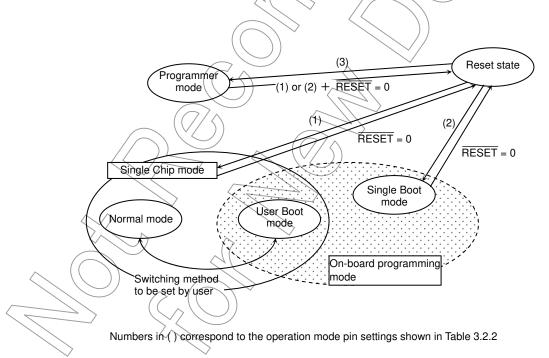

Except in Programmer mode which is entered with  $\overline{\text{RESET}}$  held at "0", the CPU will start operating in the selected mode after the reset state is released. Once the operation mode has been set, make sure that the input levels on the mode setting pins are not changed during operation. Table 3.2.2 shows how to set each operation mode, and Figure 3.2.2 shows a mode transition diagram.

|     | Operation Made                              |               | (Input Pins |         |  |  |

|-----|---------------------------------------------|---------------|-------------|---------|--|--|

|     | Operation Mode                              | RESET         | воот (Р30)  | AM1 AM0 |  |  |

| (1) | Single Chip mode (Normal or User Boot mode) | $\mathcal{A}$ | >1          | 1/1     |  |  |

| (2) | Single Boot mode                            |               | 0           | ()≯ 1   |  |  |

| (3) | Programmer mode                             | $(0 \land$    | $\sim$ _    |         |  |  |

|     |                                             |               | $\sim$      |         |  |  |

#### Table 3.2.2 Operation Mode Pin Settings

Although P30 is an output port, it becomes an input port with pull-up resistor only during a reset. After a reset, P30 operates as follows depending on the operation mode.

- Single chip mode: Output port (Without pull-up resistor)

- Single boot mode: Pull-up (Input gate is invalid, and output gate is in high impedance.)

Figure 3.2.2 Mode Transition Diagram

#### 3.2.3.2 Reset Operation

To reset the device, hold the  $\overline{\text{RESET}}$  input at "0" for at least 10 system clocks while the power supply voltage is within the rated operating voltage range and the internal high-frequency oscillator is oscillating stably.

#### 3.2.3.3 Memory Map for Each Operation Mode

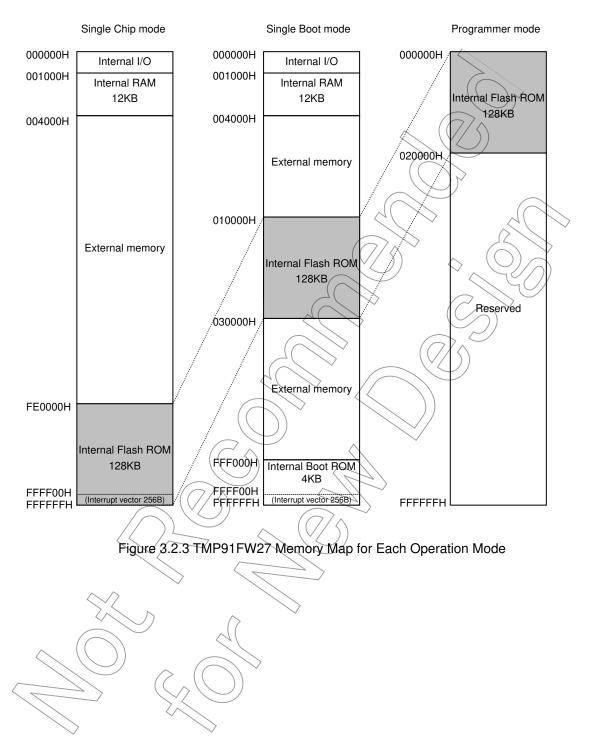

In this product, the memory map varies with operation mode. The memory map and sector address ranges for each operation mode are shown below.

|           | Single Chip Mode   | Single Boot Mode  |                  |

|-----------|--------------------|-------------------|------------------|

| Sector-0  | FE0000H to FE0FFFH | 10000H to 10FFFH  |                  |

| Sector-1  | FE1000H to FE1FFFH | 11000H to 11FFFH  |                  |

| Sector-2  | FE2000H to FE2FFFH | 12000H to 12FFFH  |                  |

| Sector-3  | FE3000H to FE3FFFH | 13000H to 13FFFH  |                  |

| Sector-4  | FE4000H to FE4FFFH | 14000H to 14FFFH  |                  |

| Sector-5  | FE5000H to FE5FFFH | 15000H to 15FFFH  | 2                |

| Sector-6  | FE6000H to FE6FFFH | 16000H to 16FFFH  | )                |

| Sector-7  | FE7000H to FE7FFFH | 17000H to 17FFFH  |                  |

| Sector-8  | FE8000H to FE8FFFH | 18000H to 18FFFH) |                  |

| Sector-9  | FE9000H to FE9FFFH | 19000H to 19FEEH  |                  |

| Sector-10 | FEA000H to FEAFFFH | 1A000H to TAFFFH  |                  |

| Sector-11 | FEB000H to FEBFFFH | 1B000H to 1BFFFH  |                  |

| Sector-12 | FEC000H to FECFFFH | 1C000H to 1CFFFH  | $\bigcirc$       |

| Sector-13 | FED000H to FEDFFFH | C1D000H to 1DFFFH | $\downarrow$ ( ) |

| Sector-14 | FEE000H to FEEFFFH | TE000H to 1EFFFH  | $\searrow$       |

| Sector-15 | FEF000H to FEFFFFH | 1F000H to 1FFFFH  | $\backslash$     |

| Sector-16 | FF0000H to FF0FFFH | 20000H to 20EFFH  | )/a              |

| Sector-17 | FF1000H to FF1FFFH | 21000H to 21FFFH  | $\zeta()$        |

| Sector-18 | FF2000H to FF2FFFH | 22000H to 22FFFH  |                  |

| Sector-19 | FF3000H to FF3FFEH | 23000H to 23FFFH  |                  |

| Sector-20 | FF4000H to FF4FFFH | 24000H to 24FFFH  |                  |

| Sector-21 | FF5000H to FF5FFFH | 25000H to 25FEFH  |                  |

| Sector-22 | FF6000H to FF6FFFH | 26000H tø 26FFFH  |                  |

| Sector-23 | FF7000H to FF7FFFH | 27000H to 27FFFH  |                  |

| Sector-24 | FF8000H to FF8FFFH | 28000H to 28FFFH  |                  |

| Sector-25 | FF9000H to FF9FFFH | 29000H to 29FFFH  |                  |

| Sector-26 | FFA000H to FFAFFFH | 2A000H to 2AFFFH  |                  |

| Sector-27 | FEB000H to FFBFFFH | 2B000H to 2BFFFH  |                  |

| Sector-28 | FFC000H to FFCFFFH | 2C000H to 2CFFFH  |                  |

| Sector-29 | FED000H to FFDFFFH | 2D000H to 2DFFFH  |                  |

| Sector-30 | FFE000H to FFEFFFH | 2E000H to 2EFFFH  |                  |

| Sector-31 | KFF000H to FFFFFH  | 2F000H to 2FFFFH  |                  |

Table 3.2.3 Sector Address Ranges for Each Operation Mode

#### 3.2.4 Single Boot Mode

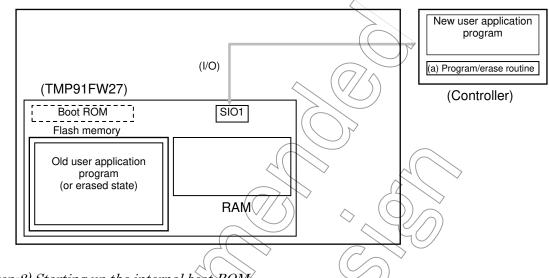

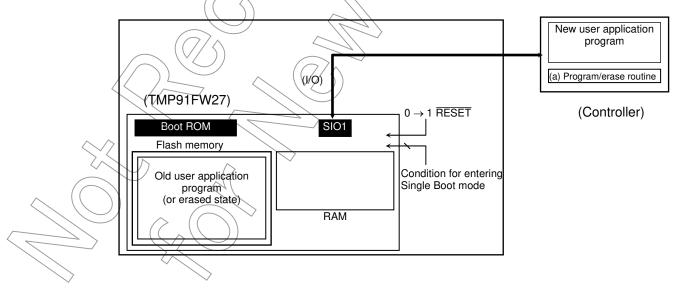

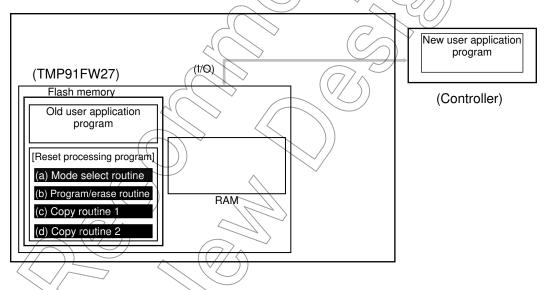

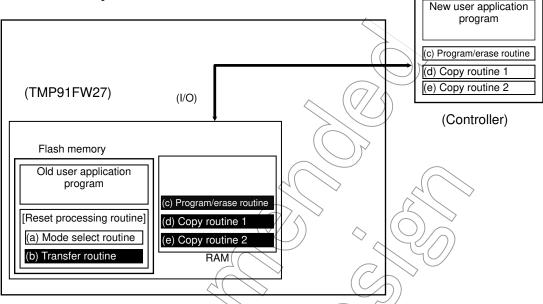

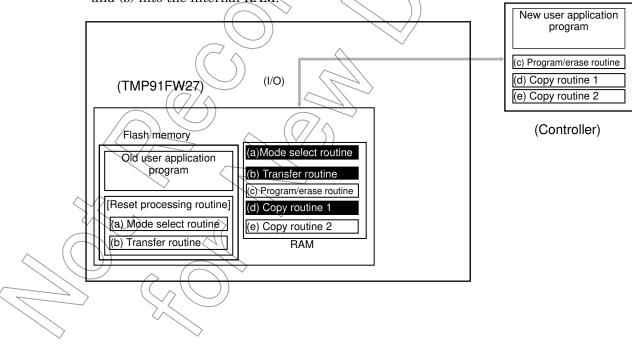

In Single Boot mode, the internal boot ROM (mask ROM) is activated to transfer a program/erase routine (user-created boot program) from an external source into the internal RAM. This program/erase routine is then used to program/erase the flash memory. In this mode, the internal boot ROM is mapped into an area containing the interrupt vector table, in which the boot ROM program is executed. The flash memory is mapped into an address space different from the one into which the boot ROM is mapped (see Figure 3.2.3).

The device's SIO (SIO1) and the controller are connected to transfer the program/erase routine from the controller to the device's internal RAM. This program/erase routine is then executed to program/erase the flash memory.

The program/erase routine is executed by sending commands and write data from the controller. The communications protocol between the device and the controller is described later in this manual. Before the program/erase routine can be transferred to the RAM, user password verification is performed to ensure the security of user ROM data. If the password is not verified correctly, the RAM transfer operation cannot be performed. In Single Boot mode, disable interrupts and use the interrupt request flags to check for an interrupt request.

Note: In Single Boot mode, the boot-ROM programs are executed in Normal mode. Do not change to another operation mode in the program/erase routine.

#### 3.2.4.1 Using the program/erase algorithm in the internal boot ROM

#### (Step-1) Environment setup

Since the program/erase routine and write data are transferred via SIO (SIO1), connect the device's SIO (SIO1) and the controller on the board. The user must prepare the program/erase routine (a) on the controller.

(Step-2) Starting up the internal boot ROM

Release the reset with the relevant input pins set for entering Single Boot mode. When the internal boot ROM starts up, the program/erase routine (a) is transferred from the controller to the internal RAM via SIO according to the communications procedure for Single Boot mode. Before this can be carried out, the password entered by the user is verified against the password written in the user application program. (If the flash memory has been erased, 12 bytes of "0xFF" are used as the password.)

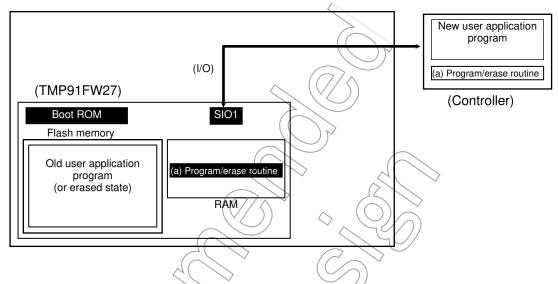

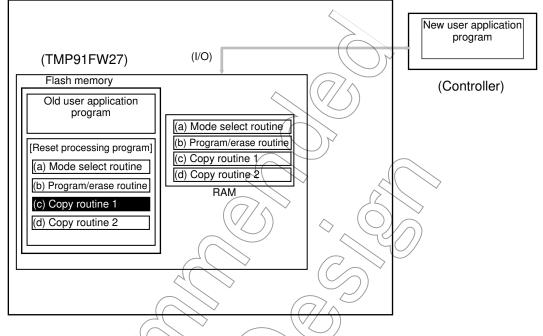

#### (Step-3) Copying the program/erase routine to the RAM

After password verification is completed, the boot ROM copies the program/erase routine (a) from the controller to the RAM using serial communications. The program/erase routine must be stored within the RAM address range of 001000H to 003DFFH.

(Step-4) Executing the program/erase routine in the RAM

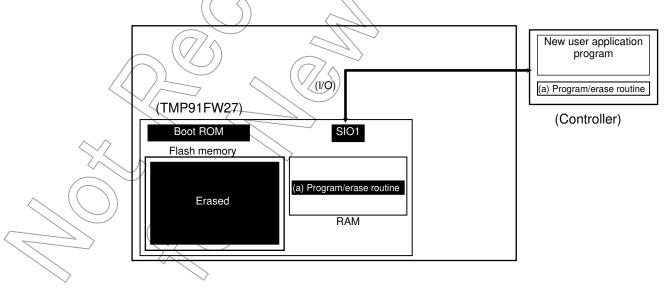

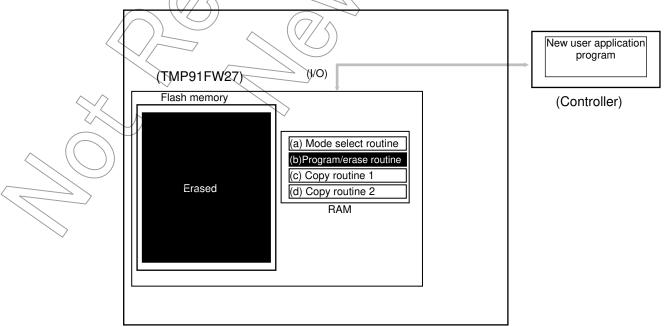

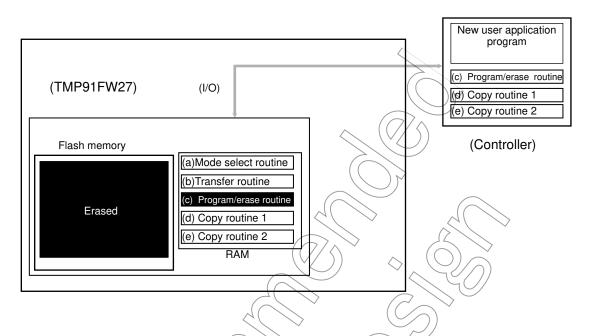

Control jumps to the program/erase routine (a) in the RAM. If necessary, the old user application program(is erased (sector/erase or chip erase).

Note: The boot ROM is provided with an erase command, which enables the entire chip to be erased from the controller without using the program/erase routine. It it is necessary to erase data on a sector basis, incorporate the necessary code in the program/erase routine.

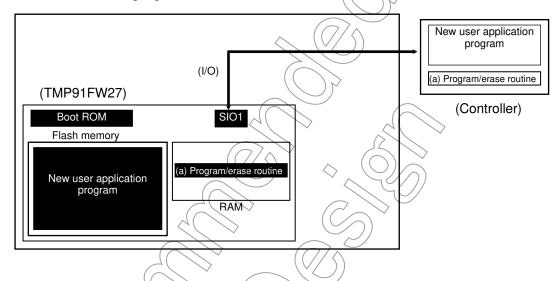

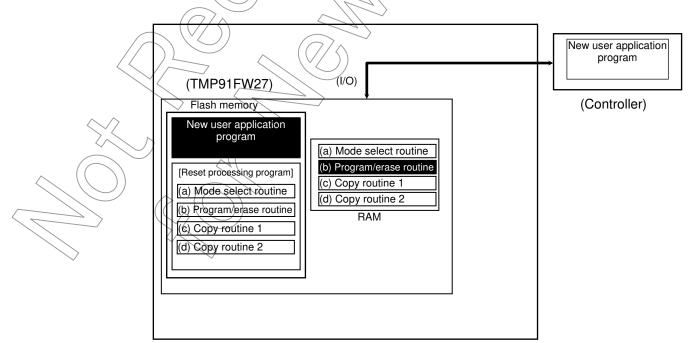

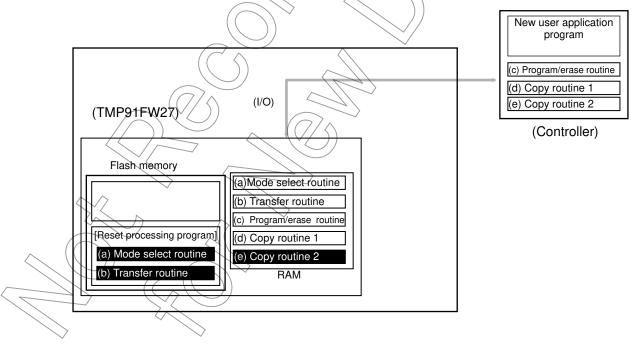

(Step-5) Copying the new user application program

The program/erase routine (a) loads the new user application program from the controller into the erased area of the flash memory.

In the example below, the new user application program is transferred under the same communications conditions as those used for transferring the program/erase routine. However, after the program/erase routine has been transferred, this routine can be used to change the transfer settings (data bus and transfer source). Configure the board hardware and program/erase routine as desired.

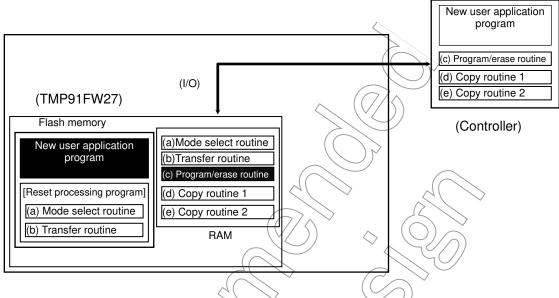

(Step-6) Executing the new user application program

After the programming operation has been completed, turn off the power to the board and remove the cable connecting the device and the controller. Then, turn on the power again and start up the device in Single Chip mode to execute the new user application program.

#### 3.2.4.2 Connection Examples for Single Boot Mode

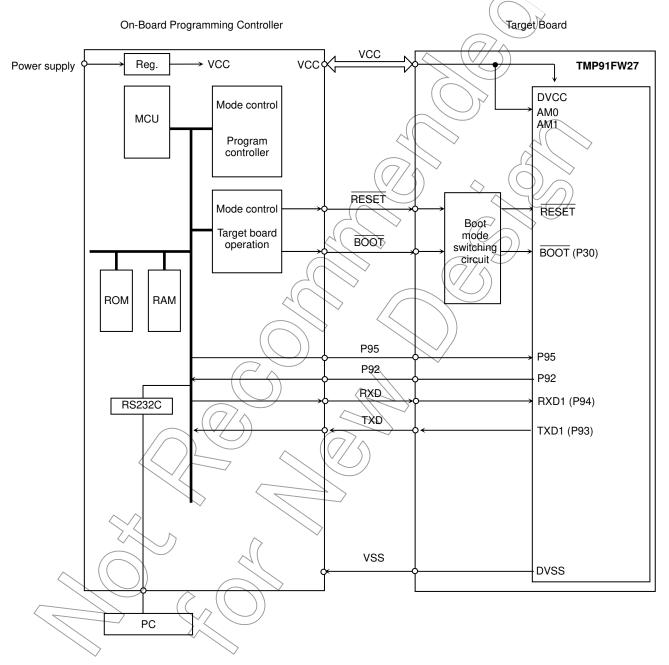

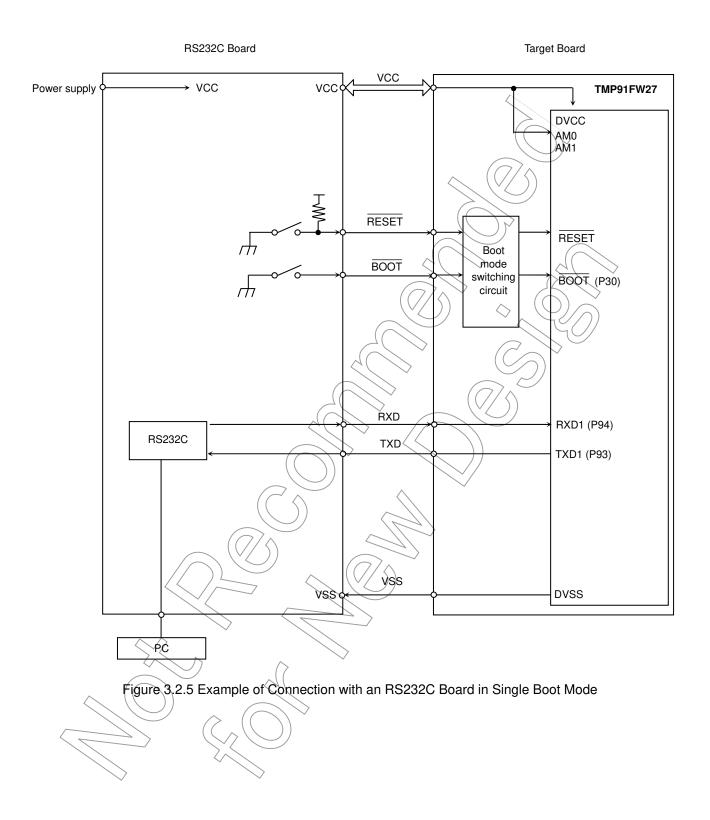

In Single Boot mode the flash memory is programmed by serial transfer. Therefore, on-board programming is performed by connecting the device's SIO (SIO1) and the controller (programming tool) and sending commands from the controller to the device. Figure 3.2.4 shows an example of connection between the target board and a programming controller. Figure 3.2.5 shows an example of connection between the target board and a RS232C board.

Figure 3.2.4 Example of Connection with an External Controller in Single Boot Mode

#### 3.2.4.3 Mode Setting

To perform on-board programming, the device must be started up in Single Boot mode by setting the input pins as shown below.

- AM0,AM1 = 1

- $\cdot \overline{\text{BOOT}} = 0$

- $\overline{\text{RESET}}$  = 0  $\rightarrow$  1

Set the AM0, AM1, and  $\overline{\text{BOOT}}$  pins as shown above with the RESET pin held at "0". Then, setting the RESET pin to "1" will start up the device in Single Boot mode.

#### 3.2.4.4 Memory Maps

Figure 3.2.6 shows a comparison of the memory map for Normal mode (in Single Chip mode) and the memory map for Single Boot mode. In Single Boot mode, the flash memory is mapped to addresses 10000H to 2FFFFH (physical addresses) and the boot ROM (mask ROM) is mapped to addresses FFF000H to FFFFFFH.

Figure 3.2.6 Comparison of Memory Maps

#### 3.2.4.5 Interface Specifications

The SIO communications format in Single Boot mode is shown below. The device supports the UART (asynchronous communications) serial operation mode.

To perform on-board programming, the same communications format must also be set on the programming controller's side.

#### UART (asynchronous) communications

- Communications channel: SIO channel 1 (For the pins to be used) see Table 3.2.4.)

- Serial transfer mode : UART (asynchronous communications) mode

- Data length :8 bits

- : None • Parity bit

- Stop bit

- : 1 bit: See Table 3.2.5 and Table 3.2.6. • Baud rate

| Table 3.2.4 Pin Connections |          |                   |      |               |  |  |  |  |  |

|-----------------------------|----------|-------------------|------|---------------|--|--|--|--|--|

| Pi                          | ns       | Ú                 | ART  |               |  |  |  |  |  |

| Power supply                | DVCC     | $\langle \rangle$ | 0    | $\mathcal{C}$ |  |  |  |  |  |

| pins                        | DVSS     | $\langle \rangle$ | 0    |               |  |  |  |  |  |

| Mode setting pins           | AM1,AM0, |                   | ~ /  | $\sim$        |  |  |  |  |  |

|                             | BOOT     | /                 | 0 (( | 7/            |  |  |  |  |  |

| Reset pin                   | RESET    |                   | 0    |               |  |  |  |  |  |

| Communications              | TXD1     |                   | 0    |               |  |  |  |  |  |

| pins                        | RXD1     |                   | 0)   |               |  |  |  |  |  |

Note: Unused pins are in the initial state after reset release.

#### Table 3.2.5 Baud Rate Table

| SIO                                       | Transfer Rate | e (bps)       | $\langle \mathcal{A} \rangle$ | 4     |      |

|-------------------------------------------|---------------|---------------|-------------------------------|-------|------|

| UART                                      | 115200        | 57600         | 38400                         | 19200 | 9600 |

|                                           |               |               |                               |       |      |

|                                           |               |               | $\rightarrow$                 |       |      |

|                                           | 4             | $\rightarrow$ |                               |       |      |

| $ \ge                                   $ |               |               |                               |       |      |

|              |                           | (%)                       |           |            |              |             | 0               |             |                           |             |             |         |                |                     |             | ž                                                                                                                                                                                                                                                                                                                                                                            | the                                                                                                                                                                    |

|--------------|---------------------------|---------------------------|-----------|------------|--------------|-------------|-----------------|-------------|---------------------------|-------------|-------------|---------|----------------|---------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 115200                    | (sdq)                     |           |            |              |             | 115200          |             |                           |             |             |         |                | <                   | A           | A A A A A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                                                                                        | orted range.<br>(microcontroller clock frequency), the transfer baud rate error of the flash memory programming controller and the<br>total                            |

|              | 00                        | (%)                       |           |            |              |             | 0               |             | 0                         |             | 0           | '       | H              |                     | J)          | speed clock.<br>Single Boot c                                                                                                                                                                                                                                                                                                                                                | programming                                                                                                                                                            |

|              | 57600                     | (sdq)                     | —         | -          |              | _           | 57600           | -           | 57600                     |             | 57600       |         | $\mathcal{YH}$ | 57600               |             | ed as a high-s                                                                                                                                                                                                                                                                                                                                                               | lash memory                                                                                                                                                            |

|              | 38400                     | (%)                       |           | +1.73      |              | 0           | 0               |             |                           | +1.73       | 6//         |         | +1.73          | $\langle 2 \rangle$ | -0.13       | must be select<br>not be possit                                                                                                                                                                                                                                                                                                                                              | error of the t                                                                                                                                                         |

|              | 78E                       | (sdq)                     | —         | £906£      |              | 38400       | 38400           | -           | $\sim + (-)$              | 39063       | 38400       | 38400   | £906£          |                     | 38352       | e Boot mode.                                                                                                                                                                                                                                                                                                                                                                 | sfer baud rate                                                                                                                                                         |

|              | 19200                     | (%)                       | —         | +1.73      | 0            | 0           | 0               | J-0.162     | $\langle \rangle \rangle$ | +1.73       | 0           |         | +1.73          | )) -                | -0.13       | used in Singl<br>the reference<br>eference frequ                                                                                                                                                                                                                                                                                                                             | ncy), the trans                                                                                                                                                        |

|              | 361                       | (sdq)                     | —         | 19531      | 19200        | 19200       | (19200)         | 16261       | 19200                     | 19531       | 00261       | 19200   | 19531          | —                   | 19176       | iit that can be<br>mode, one of<br>ed as each re                                                                                                                                                                                                                                                                                                                             | clock frequer                                                                                                                                                          |

|              | 9600                      | Error (%)                 | +0.16     | EZ:L+      | O            |             | S) <sup>0</sup> | ,40.16      | 0                         | (EL:4+)     |             | 0       | +1.73          | 0                   | -0.13       | scillation circu<br>g Single Boot<br>iat are detect                                                                                                                                                                                                                                                                                                                          | əd range.<br>licrocontroller<br>al                                                                                                                                     |

|              | 96                        | Baud Rate<br>(bps)        | 9615      | 6766       | 0096         | 0096        | 0096            | 1/51/96     | 0096                      | 9266        | 0096        | 0096    | 9926           | 0096                | 9588        | high-speed o<br>memory usin,<br>requencies th                                                                                                                                                                                                                                                                                                                                | of the supported<br>frequency (mic                                                                                                                                     |

| $\checkmark$ | Rate (bps)                | Supported Range<br>(MHz)  | 7.83_8,14 | 9.64~10.02 | ~10.84~11.28 | 12.05-12.53 | 14.46~15.04     | 15.66~16.29 | 18.07~18.80               | 19.27~20.05 | 21.68~22.56 |         | 24.09~20.00    | 25.29~26.32         | 26.50~27.57 | The frequency of the high-speed oscillation circuit that can be used in Single Boot mode.<br>To program the flash memory using Single Boot mode, one of the reference frequencies must be selected as a high-speed clock.<br>The range of clock frequencies that are detected as each reference frequency. It may not be possible to perform Single Boot operations at clock | frequencies outside of the supported range.<br>To automatically detect the reference frequency (microcontri<br>oscillation frequency error must he within +2% in total |

|              | Reference Baud Rate (bps) | Reference Frequency (MHz) | 8         | 10         | 11.0592      | 12.2880     | 14.7456         | 16          | 18.4320                   | 20          | 22.1184     | 24.5760 | 25             | 25.8048             | 27          | Reference frequency: The frequency of the high-speed oscillation circuit that can be used in Single Boot mode.<br>To program the flash memory using Single Boot mode, one of the reference frequencies i<br>Supported Range: The range of clock frequencies that are detected as each reference frequency. It may                                                            | frequencies outside of the supp<br>Note: To automatically detect the reference frequency<br>oscillation frequency error must he within +2% in                          |

Table 3.2.6 Correspondence between Operating Frequency and Baud Rate in Single Boot Mode

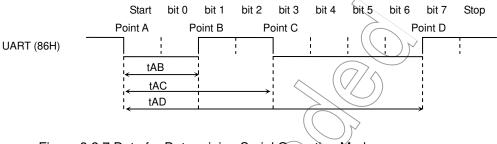

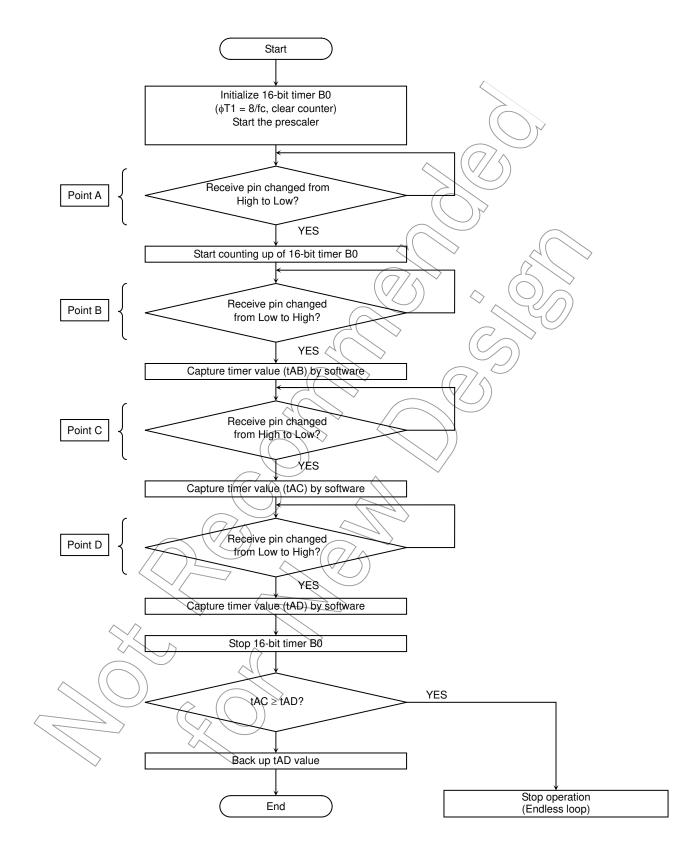

#### 3.2.4.6 Data Transfer Formats

Table 3.2.7 to Table 3.2.13 show the operation command data and the data transfer format for each operation mode.

|        | Table 3.2.7 (             | Operation Command Data   |

|--------|---------------------------|--------------------------|

|        | Operation Command<br>Data | Operation Mode           |

|        | 10H                       | RAM Transfer             |

|        | 20H                       | Flash Memory SUM         |

|        | 30H                       | Product Information Read |

|        | 40H                       | Flash Memory Chip Erase  |

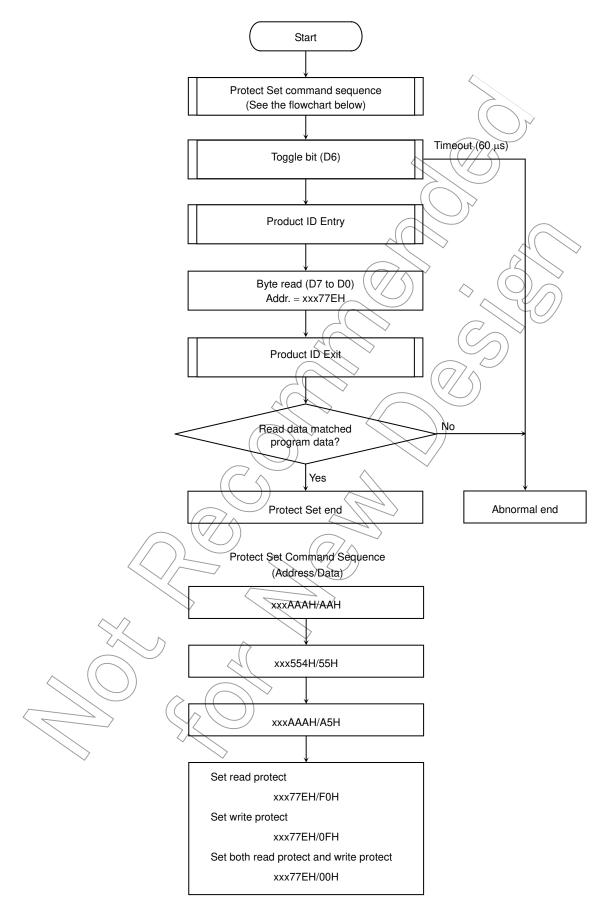

|        | 60H                       | Flash Memory Protect Set |

|        | 60H                       | Flash Memory Protect Set |

|        |                           |                          |

| $\leq$ |                           | $\searrow$               |

|        | $\geq$                    |                          |

|        |                           |                          |

|        |                           |                          |

| Table 3.2.7 | Operation Command Data |

|-------------|------------------------|

| Transfer<br>Byte<br>Number         Transfer Data<br>from Controller to Device         Baud<br>Rate         Transfer Data<br>from Device to Controller           Boot<br>ROM         1st byte         Baud rate setting<br>UART         Desired<br>Boot         Desired<br>Note 11         ACK response to baud rate setting<br>Normal (baud rate cannot be set,<br>operation is definitated.)           3rd byte         Operation command data         (10H)         ACK response to baud rate cannot be set,<br>operation is definitated.)           3rd byte         Operation command data         (10H)         ACK response to operation command<br>(Note 2)           3rd byte         Operation command data         (10H)           4th byte         -         ACK response to operation command<br>(Note 2)           18th byte         Password data (12 bytes)<br>to<br>(02FEF4H to 02FEFFH)         10H           19th byte         RAM storage start address 31 to 16 (Note 3)         -           20th byte         RAM storage start address 31 to 24 (Note 3)         -           23rd byte         RAM storage start address 31 to 3 (Note 3)         -           23rd byte         RAM storage byte count 15 to 3 (Note 3)         -           25th byte         RAM storage data         -           10H         -         -           27th byte         RAM storage data         -           10H         - <td< th=""><th><b></b></th><th></th><th></th><th>5</th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b></b>   |              |                                             | 5                  |                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|---------------------------------------------|--------------------|-----------------------------------------|

| ROM     Laky as both of a base of the set of the se |           | Byte         |                                             |                    |                                         |

| ROM     Laky as both of a base of the set of the se | Boot      | 1st byte     | Baud rate setting                           | Desired            |                                         |

| 2nd byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | TSI Dyle     |                                             |                    |                                         |

| 2.10 S y 0     Normal (bauG rate OK)     1       3rd byte     Operation command data     (10H)       4th byte     —       4th byte     —       5th byte     Password data (12 bytes)       16th byte     (02FEF4H to 02FEFFH)       17th byte     CHECKSUM value for 5th to 16th bytes       18th byte     —       20th byte     RAM storage start address 23 to 16 (Note 3)       21st byte     RAM storage start address 45 to 8 (Note 3)       22nd byte     RAM storage start address 7 to 0 (Note 3)       23th byte     CHECKSUM value for 19th jo 24th bytes       10th byte     CHECKSUM value for 19th jo 24th bytes       21st byte     RAM storage start address 7 to 0 (Note 3)       23rd byte     RAM storage start address 7 to 0 (Note 3)       26th byte     CHECKSUM value for 19th jo 24th bytes       (In+1)th byte,     CHECKSUM value for 19th jo 24th bytes       (In+1)th byte,     CHECKSUM value for 27th to m1th bytes       (In+1)th byte,     —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |              | UARI 800                                    | (Note 1)           |                                         |

| 3rd byte     Operation command data     (10H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | 2nd byte     | —                                           |                    |                                         |

| 3rd byte       Operation command data       (10H)         4th byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |              |                                             |                    |                                         |

| 3rd byte       Operation command data       (10H)         4th byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |              |                                             |                    |                                         |

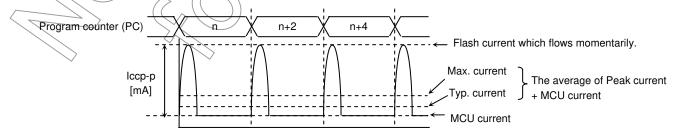

| 4th byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |              |                                             |                    | operation is terminated.)               |