### SN54AS825, SN54AS826 SN74AS825, SN74AS826

# 8-BIT BUS INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS D0825 LINE 1984 - REVISED JANUARY 1986

- Functionally Equivalent to AMD's AM29825 and AM29826

- Improved IOH Specifications

- Multiple Output Enables Allow Multiuser Control of the Interface

- Outputs Have Undershoot Protection Circuitry

- Power-Up High-Impedance State

- Package Options Include Both Plastic and Ceramic Chip Carriers in Addition to Plastic and Ceramic DIPs

- Buffered Control Inputs to Reduce DC Loading Effect

- Dependable Texas Instruments Quality and Reliability

#### description

These 8-bit flip-flops feature three-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing multiuser registers, I/O ports, bidirectional bus drivers, and working registers.

With the clock enable ( $\overline{\text{CLKEN}}$ ) low, the eight D-type edge-triggered flip-flops enter data on the low-to-high transitions of the clock. Taking:  $\overline{\text{CLKEN}}$  high will disable the clock buffer, thus latching the outputs. The 'AS825 has non-inverting D inputs and the 'AS826 has inverting  $\overline{\text{D}}$  inputs. Taking the  $\overline{\text{CLR}}$  input low causes the eight  $\Omega$  outputs to go low independently of the clock.

Multiuser buffered output-control inputs ( $\overline{OC}1$ ,  $\overline{OC}2$ , and  $\overline{OC}3$ ) can be used to place the eight outputs in either a normal logic state (high or low level) or a high-impedance state. In the high-impedance state the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive the bus lines in a busorganized system without need for interface or pull-up components. The output controls do not affect the internal operation of the flip-flops. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

SN54AS825 . . . JT PACKAGE SN74AS825 . . . DW OR NT PACKAGE (TOP VIEW)

SN54AS825 . . . FK PACKAGE SN74AS825 . . . FN PACKAGE

(TOP VIEW)

SN54AS826 . . . JT PACKAGE SN74AS826 . . . DW OR NT PACKAGE

(TOP VIEW)

SN54AS826 . . . FK PACKAGE SN74AS826 . . . FN PACKAGE

(TOP VIEW)

NC - No internal connection

Copyright © 1984, Texas Instruments Incorporated

The SN54AS' family is characterized for operation over the full military temperature range of  $-55\,^{\circ}$ C to 125 °C. The SN74AS' family is characterized for operation from 0 °C to 70 °C.

#### 'AS825 FUNCTION TABLE

|     |     | INPUTS |          |   | OUTPUT |

|-----|-----|--------|----------|---|--------|

| ÖC+ | CLR | CLKEN  | CLK      | D | a      |

| L   |     | X      | X        | Х |        |

| L   | н   | L      | <b>†</b> | н | н      |

| ١٤  | н   | L      | <b>†</b> | L | L      |

| ال  | н   | н      | X        | Х | σo     |

| lн  | х   | ×      | X        | X | z      |

$\overline{OC}^* = H$  if any of  $\overline{OC}1$ ,  $\overline{OC}2$ , or  $\overline{OC}3$  are high.  $\overline{OC}^* = L$  if all of  $\overline{OC}1$ ,  $\overline{OC}2$ , and  $\overline{OC}3$  are low.

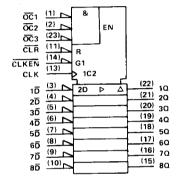

#### 'AS825 logic symbol†

| OC1     (11)     8       OC2     (22)       OC3     (23)       CLK     (11)     R       CLKEN     (13)     1C2       1D     (4)     2D     Δ       2D     (22)     1Q       3D     (5)     (20)     3Q       4D     (7)     (18)     5Q       6D     (8)     (17)     6Q       8D     (10)     (15)     8Q |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

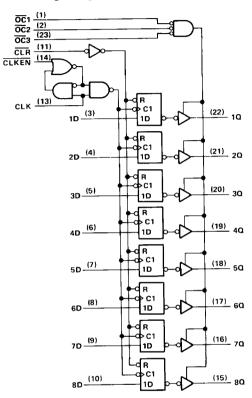

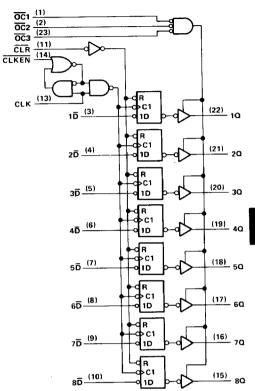

#### 'AS825 logic diagram (positive logic)

Pin numbers are for DW, JT, and NT packages.

#### 'AS826 FUNCTION TABLE

|     |     | INPUTS |     |   | OUTPUT |

|-----|-----|--------|-----|---|--------|

| ōc∗ | CLR | CLKEN  | CLK | O | a      |

| L   | L   | Х      | Х   | X | L      |

| ا ا | н   | L      | Ť   | Н | L      |

| اد  | н   | L      | 1   | L | н      |

| L   | н   | н      | X   | Х | $a_0$  |

| н   | x   | х      | x   | Х | Z      |

$\overline{OC}^* = H \text{ if any of } \overline{OC}1, \overline{OC}2, \text{ or } \overline{OC}3 \text{ are high.}$

$\overline{OC}^* = L$  if all of  $\overline{OC}1$ ,  $\overline{OC}2$ , and  $\overline{OC}3$  are low.

#### 'AS826 logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12

#### 'AS826 logic diagram (positive logic)

Pin numbers shown are for DW, JT, and NT packages.

# SN54AS825, SN54AS826, SN74AS825, SN74AS826 8-BIT BUS INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS

| bsolute maximum ratings over operating free-air temperature range (unless otherwise noted)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Supply voltage, VCC         7           Input voltage         7           Voltage applied to a disabled 3-state output         5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V  |

| Operating free-air temperature range:       -55 °C to 125 °C to 12 | ۰C |

#### recommended operating conditions

|                 |                              |                   | SN54AS825<br>SN54AS826 |     | SN74AS825<br>SN74AS826 |     |     | UNIT |    |

|-----------------|------------------------------|-------------------|------------------------|-----|------------------------|-----|-----|------|----|

|                 |                              |                   | MIN                    | NOM | MAX                    | MIN | NOM | MAX  | 1  |

| VCC             | Supply voltage               |                   | 4.5                    | 5   | 5.5                    | 4.5 | 5   | 5.5  | ٧  |

| VIH             | High-level input voltage     |                   | 2                      |     |                        | 2   |     |      | V  |

| VIL             | Low-level input voltage      |                   |                        |     | 0.8                    |     |     | 0.8  | V  |

| IOH             | High-level output current    |                   |                        |     | - 24                   |     |     | - 24 | mA |

| loL             | Low-level output current     |                   |                        |     | 32                     |     |     | 48   | mA |

| ·OL             |                              | CLR low           | 5                      |     |                        | 4   |     |      | ns |

| tw              | Pulse duration               | CLK high or low   | 9                      |     | -                      | 8   |     |      |    |

| -               |                              | CLR inactive      | 8                      |     |                        | В   |     |      |    |

|                 | Setup time before CLK1       | Data              | 7                      |     |                        | 6   |     |      | ns |

| t <sub>su</sub> | octup time porete care       | CLKEN high or low | 7                      |     |                        | 6   |     |      | 1  |

| th              | Hold time, CLKEN or data a   |                   | 0                      |     |                        | 0   |     |      | ns |

| T <sub>A</sub>  | Operating free-air temperatu |                   | - 55                   |     | 125                    | 0   |     | 70   | °C |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |         | TEST CONDITIONS                   |                               | SN54AS825<br>SN54AS826 |                              |       | SN74AS825<br>SN74AS826 |                      |       | UNIT          |  |

|-----------------|---------|-----------------------------------|-------------------------------|------------------------|------------------------------|-------|------------------------|----------------------|-------|---------------|--|

|                 |         |                                   |                               | MIN                    | AIN TYP <sup>†</sup> MAX MIN |       | TYP <sup>†</sup>       | TYP <sup>†</sup> MAX |       |               |  |

| VIK             |         | V <sub>CC</sub> = 4.5 V,          | i <sub>I</sub> = -18 mA       |                        |                              | -1.2  |                        |                      | -1.2  | ٧             |  |

| *IK             |         | V <sub>CC</sub> = 4.5 V to 5.5 V, |                               | V <sub>CC</sub> -      | V <sub>CC</sub> - 2          |       |                        | V <sub>CC</sub> -2   |       |               |  |

| Vон             |         | V <sub>CC</sub> = 4.5 V,          | I <sub>OH</sub> = -15 mA      | 2.4                    | 3.2                          |       | 2.4                    | 3.2                  | -     |               |  |

| • ОП            |         | $V_{CC} = 4.5 \text{ V},$         | I <sub>OH</sub> = -24 mA      | 2                      |                              |       | 2                      |                      |       |               |  |

| VOL             |         | V <sub>CC</sub> = 4.5 V,          | I <sub>OL</sub> = 32 mA       |                        | 0.3                          | 0.5   |                        |                      |       | $\Box$ $\lor$ |  |

|                 |         | $V_{CC} = 4.5 \text{ V},$         | I <sub>OL</sub> = 48 mA       |                        |                              |       |                        | 0.35                 | 0.5   | L.            |  |

| lozh            |         | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.7 V        |                        |                              | 50    |                        |                      | 50    | μA            |  |

| OZL             |         | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 0.4 V        |                        |                              | - 50  |                        |                      | 50    | μΑ            |  |

| li              |         | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 7 V          |                        |                              | 0.1   |                        |                      | 0.1   | mA            |  |

| <del>1</del> н  |         | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 2.7 V        |                        |                              | 20    |                        |                      | 20    | μA            |  |

| lir<br>I        |         | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 0.4 V        |                        |                              | -0.5  |                        |                      | -0.5  | mA            |  |

| 10 <sup>‡</sup> |         | V <sub>CC</sub> = 5.5 V,          | $V_{\Omega} = 2.25 \text{ V}$ | - 30                   |                              | - 112 | - 30                   |                      | - 112 | mA            |  |

| 10              |         | 700                               | Outputs high                  |                        | 45                           | 73    |                        | 45                   | 73    |               |  |

| - 1             | 'AS825  | V <sub>CC</sub> = 5.5 V           | Outputs low                   |                        | 56                           | 90    |                        | 56                   | 90    | mA            |  |

| lcc             |         | 100                               | Outputs disabled              |                        | 59                           | 95    |                        | 59                   | 95    | 7             |  |

|                 | 'A\$826 |                                   | Outputs high                  |                        | 45                           | 73    |                        | 45                   | 73    |               |  |

|                 |         | $V_{CC} = 5.5 \text{ V}$          | Outputs low                   |                        | 56                           | 90    |                        | 56                   | 90    | mA            |  |

| 1               |         | 3.0                               | Outputs disabled              |                        | 59                           | 95    |                        | 59                   | 95    | 1             |  |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 \text{ °C}$ . ‡ The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current,  $I_{OS}$ .

## switching characteristics (see Note 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | $V_{CC}=4.5$ V to 5.5 V, $C_L=50$ pF, $R1=500$ $\Omega$ , $R2=500$ $\Omega$ , $T_A=MIN$ to MAX |      |                        |     |          |

|------------------|-----------------|----------------|------------------------------------------------------------------------------------------------|------|------------------------|-----|----------|

|                  |                 |                | SN54AS825<br>SN54AS826                                                                         |      | SN74AS825<br>SN74AS826 |     |          |

|                  |                 |                | MIN                                                                                            | MAX  | MIN                    | MAX | <u> </u> |

| •                |                 |                | 3.5                                                                                            | 9    | 3.5                    | 7.5 | ns       |

| tpLH             | CLK             | Any Q          | 3.5                                                                                            | 11.5 | 3.5                    | 11  | 1        |

| <sup>t</sup> PHL | ČLR             | Any Q          | 3.5                                                                                            | 14   | 3.5                    | 13  | ns       |

| tPHL             |                 |                | 4                                                                                              | 12   | 4                      | 11  | пѕ       |

| tPZH             | <u> </u>        | Any Q          | 4                                                                                              | 13   | 4                      | 12  | 1115     |

| tPZL             |                 |                | 2                                                                                              | 10   | 2                      | 8   |          |

| t <sub>PHZ</sub> | ōc              | Any Q          | 2                                                                                              | 10   | 2                      | 8   | ns       |

| <sup>†</sup> PLZ |                 |                |                                                                                                |      |                        |     |          |

NOTE 1: Load circuit and voltage waveforms are shown in Section 1.

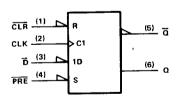

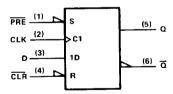

#### D flip-flop signal conventions

It is normal TI practice to name the outputs and other inputs of a D-type flip-flop and to draw its logic symbol based on the assumption of true data (D) inputs. Then outputs that produce data in phase with the data inputs are called  $\overline{\Omega}$  and those producing complementary data are called  $\overline{\Omega}$ . An input that causes a  $\Omega$  output to go high or a  $\overline{\Omega}$  output to go low is called Preset; an input that causes a  $\overline{\Omega}$  output to go high or a  $\Omega$  output to go low is called Clear. Bars are used over these pin names (PRE and  $\overline{CLR}$ ) if they are active-low.

The devices on this data sheet are second-source designs and the pin-name convention used by the original manufacturer has been retained. That makes it necessary to designate the inputs and outputs of the inverting circuit  $\overline{D}$  and  $\overline{Q}$ . In some applications it may be advantageous to redesignate the inputs and outputs as D and  $\overline{Q}$ . In that case, outputs should be renamed as shown below. Also shown are corresponding changes in the graphical symbol. Arbitrary pin numbers are shown in parentheses.

Notice that Q and  $\overline{Q}$  exchange names, which causes Preset and Clear to do likewise. Also notice that the polarity indicators ( $\searrow$ ) on  $\overline{PRE}$  and  $\overline{CLR}$  remain since these inputs are still active-low, but that the presence or absence of the polarity indicator changes at  $\overline{D}$ , Q, and  $\overline{Q}$ . Of course pin 5 (Q) is still in phase with the data input D, but now both are considered active high.