# **PF1550**

Power management integrated circuit (PMIC) for low power application processors

Rev. 7 — 29 September 2021

Product data sheet

# **1** General description

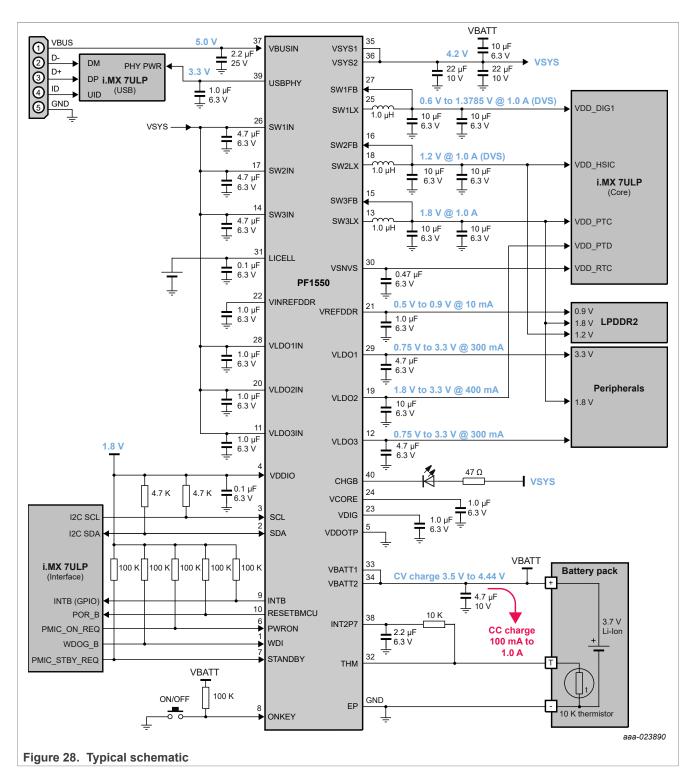

The PF1550 is a power management integrated circuit (PMIC) designed specifically for use with i.MX processors on low-power portable, smart wearable and Internet-of-Things (IoT) applications. It is also capable of providing full power solution to i.MX 7ULP, i.MX 6SL, 6UL, 6ULL, and 6SX processors.

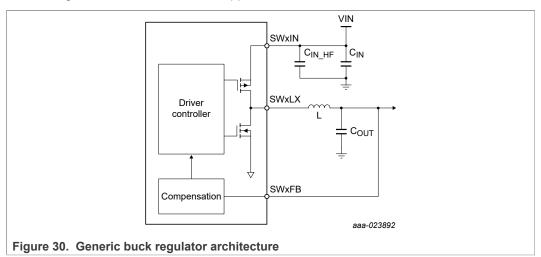

With three high-efficiency buck converter, three linear regulators, RTC supply, and battery linear charger, the PF1550 can provide power for a complete battery-powered system, including application processors, memory, and system peripherals.

# 1.1 Features and benefits

This section summarizes the PF1550 features:

- Input voltage range to PMIC VBUSIN pin via USB bus or AC adapter: 4.1 V to 6.0 V

- Buck converters:

- SW1, 1.0 A; 0.6 V to 1.3875 V in 12.5 mV steps, or 1.1 V to 3.3 V in variable steps

- SW2, 1.0 A; 0.6 V to 1.3875 V in 12.5 mV steps, or 1.1 V to 3.3 V in variable steps

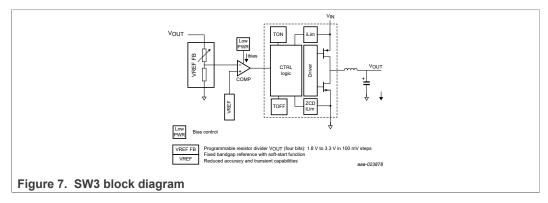

- SW3, 1.0 A; 1.8 V to 3.3 V in 100 mV steps

- Soft start

- Quiescent current 1.0 µA in ULP mode with light load

- Peak efficiency > 90 %

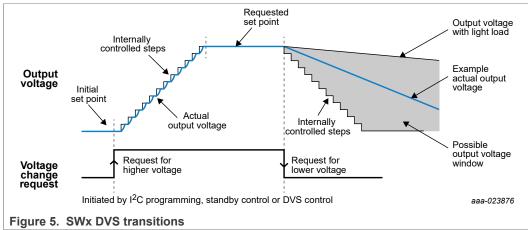

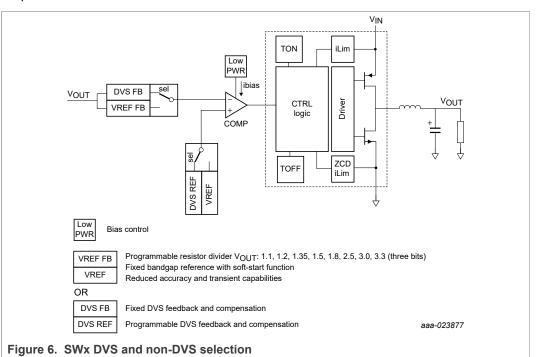

- Dynamic voltage scaling on SW1 and SW2

- Modes: forced PWM quasi-fixed frequency mode, adaptive variable-frequency mode

- Programmable output voltage, current limit, and soft start

- LDO regulators

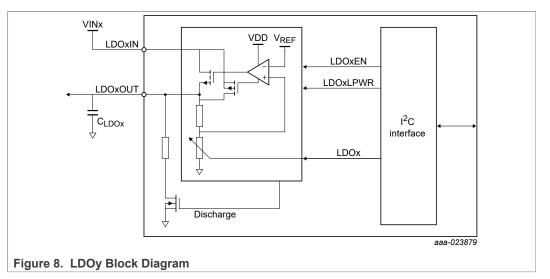

- LDO1, 0.75 V to 1.5 V/1.8 to 3.3 V, 300 mA with load switch mode

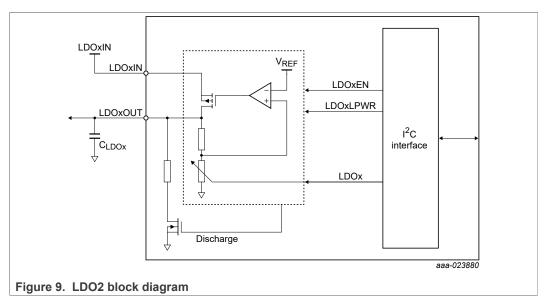

- LDO2, 1.8 V to 3.3 V, 400 mA

- LDO3, 0.75 V to 1.5 V/1.8 V to 3.3 V, 300 mA with load switch mode

- Quiescent current < 1.5 µA in Low-power mode

- Programmable output voltage

- Soft start and ramp

- Current limit protection

- Battery charger

- Supports single-cell Lithium Ion/Lithium Polymer batteries

- Linear charging (10 mA to 1500 mA input limit)

- Up to 6.5 V input operating range

- VSYS regulator can withstand transient and DC inputs from 0 V up to +22 V

- Programmable charge voltage (3.5 V to 4.44 V)

- Programmable charge current (100 mA to 1000 mA)

- Programmable charge termination current (5.0 mA to 50 mA)

- Integrated 50 mΩ battery isolation MOSFET for operation with no/low battery

- Battery supplement mode

- Battery discharge overcurrent protection, up to 3.0 A

- USB\_PHY low dropout linear regulator

- Programmable LED driver (status indicator)

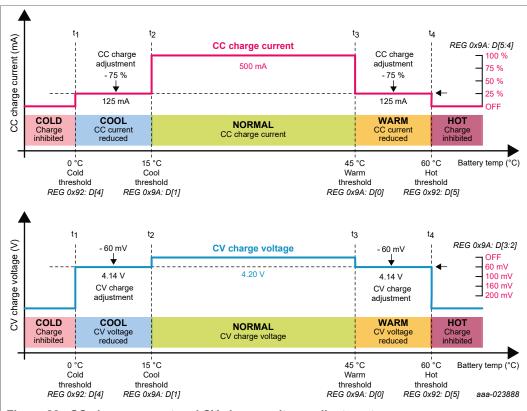

- JEITA-compliant battery temp sensing and charger control

- Key charging parameters can be configured and permanently stored in OTP

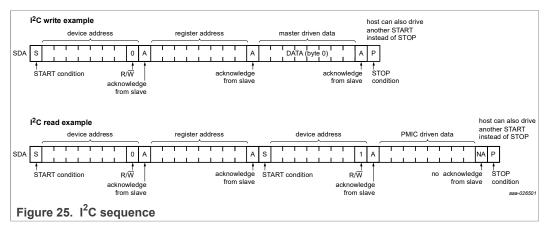

- I<sup>2</sup>C Control Interface permitting processor control and event detection

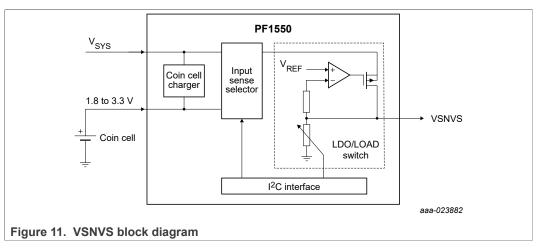

- LDO/switch supply

- RTC supply VSNVS 3.0 V, 2.0 mA

- Battery backed memory including coin cell charger

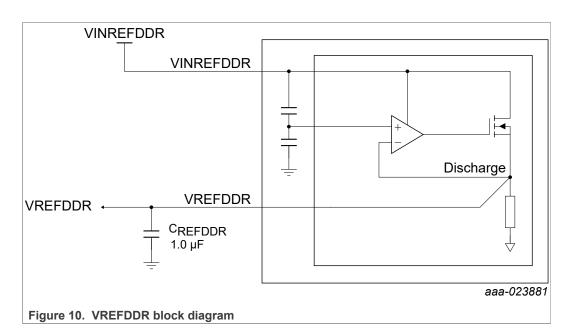

- DDR memory reference voltage, VREFDDR, 0.5 V to 0.9 V, 10 mA

- OTP (One time programmable) memory for device configuration

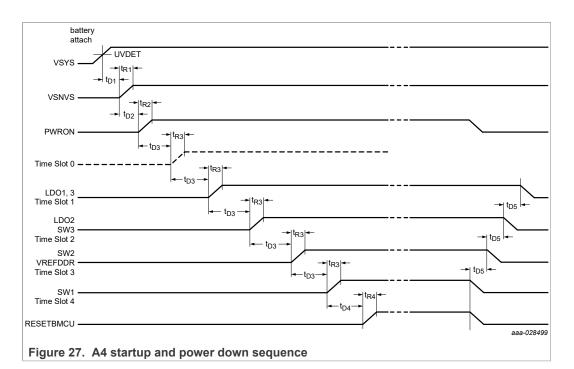

- User programmable start-up sequence, timing, soft-start, and power-down sequence

Programmable regulator output voltages and charger parameters

- I<sup>2</sup>C interface

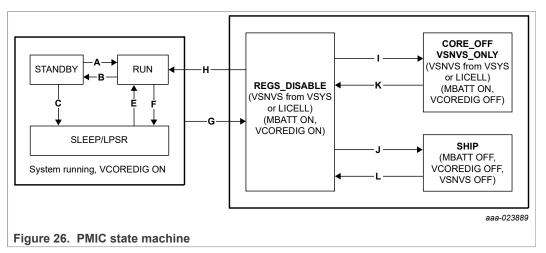

- User programmable Standby, Sleep/Low-power, and Off (REGS\_DISABLE) modes

- Ambient temperature range -40 °C to 105 °C

# **1.2 Applications**

- Smart mobile/wearable devices

- Low-power IoT applications

- Wireless game controllers

- Embedded monitoring systems

- Home automation

- POS

- E-Read

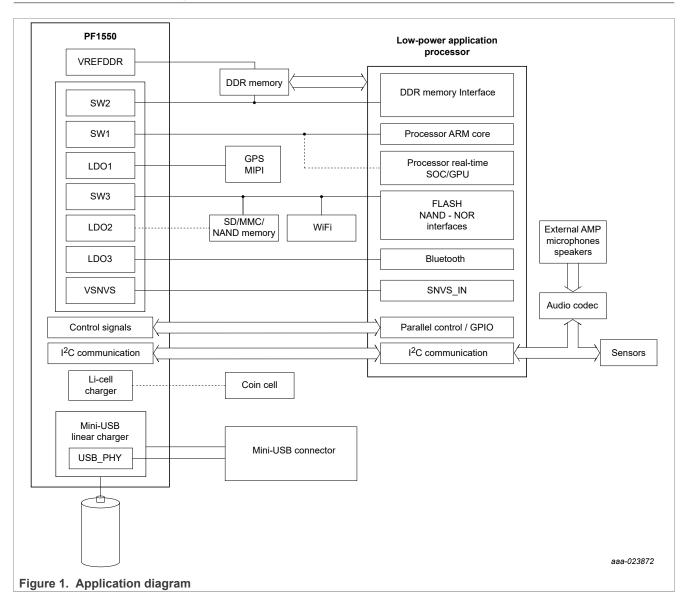

# 2 Application diagram

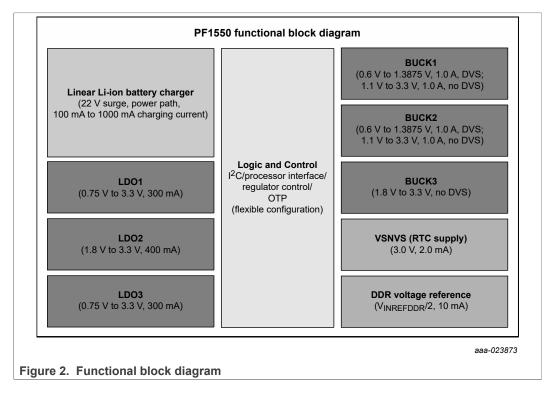

# 2.1 Functional block diagram

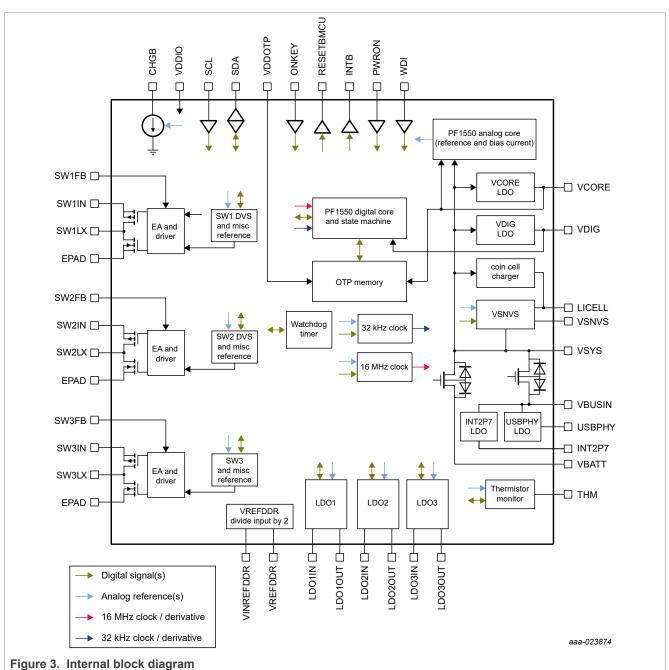

# 2.2 Internal block diagram

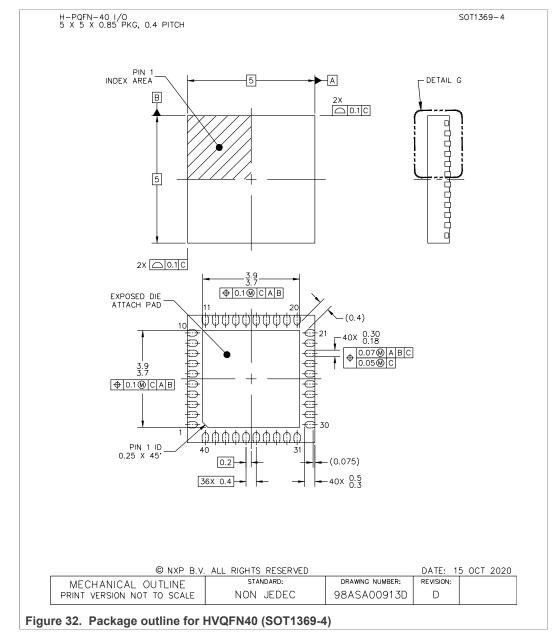

# 3 Orderable parts

The PF1550 is available only with preprogrammed configurations. These preprogrammed devices are identified using the program code from <u>Table 1</u>, which also list the associated NXP reference designs where applicable. Details of the OTP programming for each device can be found in <u>Table 85</u>.

#### Table 1. Orderable part variations

| Part number <sup>[1]</sup> | Temperature (T <sub>A</sub> ) | Package                                                     | Programming options                        |

|----------------------------|-------------------------------|-------------------------------------------------------------|--------------------------------------------|

| MC32PF1550A0EP             |                               |                                                             | 0 - Not programmed                         |

| MC32PF1550A1EP             |                               |                                                             | 1 (Default)                                |

| MC32PF1550A2EP             |                               |                                                             | 2 (i.MX 7ULP with LPDDR3) <sup>[2]</sup>   |

| MC32PF1550A3EP             |                               |                                                             | 3 (i.MX 6UL with DDR3L)                    |

| MC32PF1550A4EP             | -40 °C to 85 °C (for use      |                                                             | 4 (i.MX 7ULP with LPDDR3)                  |

| MC32PF1550A5EP             | in consumer applications)     |                                                             | 5 (i.MX 6UL with DDR3)                     |

| MC32PF1550A6EP             |                               |                                                             | 6 (i.MX 6ULL with DDR3L)                   |

| MC32PF1550A7EP             |                               |                                                             | 7 (i.MX 6UL with LPDDR2)                   |

| MC32PF1550A8EP             |                               | 98ASA00913D, 40-pin QFN 5.0<br>mm x 5.0 mm with exposed pad | 8 (i.MX 6UL with DDR3L, Edge<br>Sensitive) |

| MC32PF1550A9EP             |                               |                                                             | 9 (i.MX RT1050)                            |

| MC34PF1550A0EP             |                               |                                                             | 0 - Not programmed                         |

| MC34PF1550A1EP             |                               |                                                             | 1 (Default)                                |

| MC34PF1550A2EP             |                               |                                                             | 2 (i.MX 7ULP with LPDDR3) [2]              |

| MC34PF1550A3EP             |                               |                                                             | 3 (i.MX 6UL with DDR3L)                    |

| MC34PF1550A4EP             | -40 °C to 105 °C (for use     |                                                             | 4 (i.MX 7ULP with LPDDR3)                  |

| MC34PF1550A5EP             | in industrial applications)   |                                                             | 5 (i.MX 6UL with DDR3)                     |

| MC34PF1550A6EP             |                               |                                                             | 6 (i.MX 6ULL with DDR3L)                   |

| MC34PF1550A7EP             |                               |                                                             | 7 (i.MX 6UL with LPDDR2)                   |

| MC34PF1550A8EP             |                               |                                                             | 8 (i.MX 6UL with DDR3L, Edge<br>Sensitive) |

| MC34PF1550A9EP             |                               |                                                             | 9 (i.MX RT1050)                            |

For tape and reel, add an R2 suffix to the part number. For internal validation only [1] [2]

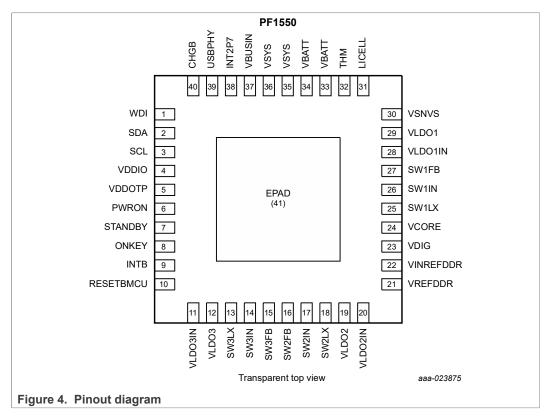

# 4 Pinning information

# 4.1 Pinning

# 4.2 Pin definitions

| LD03LD03LD03LD0312VLD03LD03 output13SW3LXLD03 output14SW3INBuck 3Buck 3 switching node15SW3FBBuck 3 output voltage feedback16SW2FBBuck 2 output voltage feedback17SW2INBuck 2Buck 2 output voltage feedback18SW2LXBuck 2 switching node19VLD02LD02LD0220VLD02INLD02LD02 output21VREFDDRVREFDDRVREFDDR output22VINREFDDRVCOREVDIG regulator output (used within PF1550)23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREBuck 1Buck 1 input supply25SW1LXBuck 1Buck 1 input supply26SW1INBuck 1Buck 1 input supply27SW1FBLD01LD0128VLD01INLD01LD0129VLD01LD01LD0131LICELLVSNVS31LICELLARAGER33VBATTCHARGER33VSYSIC core33VSYSIC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin number | Pin name  | Block   | Description                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|---------|--------------------------------------------------|

| 3     SCL     UOs     SCL when used in <sup>2</sup> C mode       4     VDDIO     VDDOTP     Connect to ground in application       5     VDDOTP     VDDOTP     Connect to ground in application       6     PWRON     PWRON     STANDBY       7     STANDBY     VDS     ONKEY push-button input       8     ONKEY     VDS     OKKEY push-button input       9     INTB     INTB open-drain output     INTB open-drain output       11     VLDO3IN     LDO3     ESETEMCU     ESETEMCU       12     VLDO3     LDO3     EUG3     Buck 3 subthing node       13     SW3LX     Buck 3 unput voltage feedback       14     SW3IN     Buck 2     Buck 3 output voltage feedback       16     SW3FB     Buck 2     Buck 2 output voltage feedback       16     SW2FB     Buck 2     Buck 2 output voltage feedback       17     SW2IN     Buck 2     Buck 2 output voltage feedback       18     SW2LX     Buck 2 subthing node     Input supply       20     VLDO2IN     LDO2     IDO2 input supply       21     VREFDDR     VEFDR     VEFDR       22     VINREFDDR     ECore     VEFDD input supply       23     VDIG     Buck 1     Buck 1 switching node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1          | WDI       |         | Watchdog input from processor                    |

| 4     VDDIO     VDDOTP     VDopty voltage<br>Connect to voltage rail between 1.7 V and 3.3 V       5     VDDOTP     VDDOTP     Connect to ground in application       6     PWRON     STANDBY     STANDBY       8     ONKEY     I/Os     STANDBY input       7     STANDBY     I/Os     ONKEY push-button input       9     INTB     I/OS     ONKEY push-button input       10     RESETBMCU     RESETBMCU     RESETBMCU open-drain output       11     VLDO3IN     LO03     I/DO3 input supply       12     VLD03N     Buck 3     Buck 3 switching node       13     SW3LX     Buck 3     Buck 3 output voltage feedback       14     SW3IN     Buck 2     Buck 2 output voltage feedback       15     SW3FB     Buck 2     Buck 2 output voltage feedback       16     SW2LX     Buck 2     Buck 2 output voltage feedback       17     SW2IN     Buck 2     Buck 2 output voltage feedback       18     SW2LX     Buck 2     Buck 2     Buck 2       19     VLDO2IN     LDO2     LDO2     I/DO2 input supply       21     VREFDDR     REFDDR     VREFDDR input supply       22     VINREFDDR     I/Core     VDIC regulator output (used within PF1550)       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          | SDA       |         | SDA when used in I <sup>2</sup> C mode           |

| Image: style | 3          | SCL       | I/Os    | SCL when used in I <sup>2</sup> C mode           |

| 6PWRONPWRON input7STANDEYSTANDEY8ONKEYI/OSSTANDEY input9INTBONKEY push-button input10RESETBMCURESETBMCU open-drain output11VLDO3INLDO3IDO3 input supply12VLDO3DO4IDO3 input supply13SW3LXBuck 3Buck 3 input supply14SW3INBuck 3Buck 3 output voltage feedback16SW3FBBuck 2 output voltage feedback17SW2INBuck 2Buck 2 output voltage feedback18SW2LXLDO2LDO219VLDO2LDO2LDO219VLDO2LDO2LDO210VREFDDRVREFDDRVREFDDR output supply22VINREFDDRVEEFDDRVEEFDDR output (used within PF1550)23VDIGLOC1Euch 1 input supply24VCOREEuch 1 input supply25SW1LXBuck 1Buck 1 input supply26SW1NBuck 1Buck 1 input supply27SW1FBLDO1LDO128VLD01NLDO1LDO129VLD01NLDO1LDO130VSNVSVSNVSVSNVS regulator output31LICELLCorreVSNVS regulator output33VSNVSVSNVSSNVS regulator output34VLD01NLDO1Correetion35VSNSCorreetionConnection34VSNSMain input voltag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4          | VDDIO     |         |                                                  |

| 7STANDBYSTANDBY8ONKEYI/OsSTANDBY input9INTBI/OsONKEY push-button input10RESETBMCUINTB output11VLD03INLD03LD03 input supply12VLD03LD03LD03 output13SW3LXBuck 3Buck 3 switching node14SW3FBBuck 3Buck 3 output voltage feedback16SW2FBBuck 2Buck 2 output voltage feedback17SW2INBuck 2Buck 2 switching node18SW2LXBuck 2 switching node19VLD02LD02LD02100VLD02LD0220VLD02LD0221VREFDDRVREFDDR output22VINREFDRCore23VDIGCore24VCOREBuck 1 switching node25SW1LXBuck 126SW1NBuck 127SW1FBBuck 128VLD01LD0129VLD01LD0120VLD1LD0121VSNVSSuck 1 input supply22SW1FBBuck 123SW1FBBuck 124CoreVDIG regulator output (used within PF1550)25SW1FBCore26SW1FBBuck 127SW1FBBuck 128VLD01LD129VLD01Core31LICELLCoin cell input32THMCoin cell in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5          | VDDOTP    | VDDOTP  | Connect to ground in application                 |

| NKEY         Vos         ONKEY push-button input           9         INTB         INTB         INTB pen-drain output           10         RESETBMCU         RESETBMCU open-drain output           11         VLD03         LD03         ID03 input supply           12         VLD03         Buck 3         Buck 3 output supply           13         SW3LX         Buck 3 witching node           14         SW3IN         Buck 3 output voltage feedback           16         SW2FB         Buck 2 output voltage feedback           17         SW2IN         Buck 2 switching node           18         SW2KX         Buck 2 output voltage feedback           19         VLD02         LD02         LD02 uput supply           18         SW2KX         Buck 2 mut supply         LD02 input supply           19         VLD02         LD02         LD02 uput supply         LD02 input supply           21         VREFDDR         VREFDDR output         VREFDR output         REFOR           22         VINEFDDR         IC core         VDG regulator output (used within PF 1550)         UC input supply           23         VD1G         LD1         Buck 1 input supply         Buck 1 input supply         Buck 1 input supply         Buck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6          | PWRON     |         | PWRON input                                      |

| 9INTBINTB open-drain output10RESETBMCURESETBMCU open-drain output11VLDO3INLDO3LDO3 input supply12VLDO3LDO3LDO3 output13SW3LXBuck 3Buck 3 switching node14SW3INBuck 3Buck 3 input supply15SW3FBBuck 2 output voltage feedback16SW2FBBuck 2 output voltage feedback17SW2INBuck 218SW2LXBuck 2 output voltage feedback19VLDO2LDO219VLDO2LDO210VLDO2LDO220VLDO2LDO221VREFDDRVREFDDR output22VINREFDDRVREFDDR output23VDIGIC core24VCOREBuck 125SW1LXBuck 126SW1INBuck 127SW1FBLDO128VLDO1INLDO129VLDO1LDO129VLDO1VSNS30VSNSVSNS31LICELLVSNS' regulator output33THMCHARGER33VSYSC core34WattMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7          | STANDBY   |         | STANDBY input                                    |

| Nome     Reset TBMCU     Reset TBMCU       11     VLDO3IN     LDO3       12     VLDO3     LDO3       13     SW3LX     Buck 3       14     SW3IN     Buck 3       15     SW3FB     Buck 3 output voltage feedback       16     SW2FB     Buck 2 output voltage feedback       17     SW2IN     Buck 2       18     SW2FB     Buck 2       19     VLDO2     LDO2       100     VLDO2     LDO2       101     VREFDDR     VREFDDR       11     VREFDDR     VREFDDR       12     VINREFDR     Prefedback       13     SW1LX     Buck 1       14     SW2FB     LDO2       15     SW1LX     Prefedback       16     SW2FB     VLDO2       17     SW2FB     Prefedback       18     SW2LX     Buck 2 output voltage feedback       19     VLDO2     LDO2     LDO2 input supply       21     VREFDDR     VREFDDR     VREFDDR input supply       22     VINREFDR     Prefedback input     VECore       24     VCORE     Ecore     DO1 input supply       25     SW1LX     Buck 1     Buck 1 input supply       26     SW1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8          | ONKEY     | I/Os    | ONKEY push-button input                          |

| 11VLD03IN<br>LD03LD03LD03 input supply<br>LD03 output12VLD03LD03LD03 output13SW3LXBuck 3Buck 3 switching node14SW3INBuck 3Buck 3 input supply15SW3FBBuck 3 output voltage feedback16SW2FBBuck 2Buck 2 output voltage feedback17SW2INBuck 2Buck 2 output voltage feedback18SW2LXBuck 2Buck 2 output voltage feedback19VLD02LD02LD0220VLD02INLD02LD0221VREFDDRVREFDDR output22VINREFDDRVREFDDR output23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREBuck 1Buck 1 switching node25SW1LXBuck 1Buck 1 input supply26SW1INBuck 1Buck 1 input supply27SW1FBLD01LD0128VLD01INLD0129VLD01VONS29VLD01VONS31LICELLVSNVS33VBATTCHARGER34VBATTCHARGER35KYSIC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9          | INTB      |         | INTB open-drain output                           |

| LD03LD03LD03LD0312VLD03LD03 output13SW3LXLD03 output14SW3INBuck 3Buck 3 switching node15SW3FBBuck 3 output voltage feedback16SW2FBBuck 2 output voltage feedback17SW2INBuck 2Buck 2 output voltage feedback18SW2LXBuck 2 switching node19VLD02LD02LD0220VLD02INLD02LD02 output21VREFDDRVREFDDRVREFDDR output22VINREFDDRVCOREVDIG regulator output (used within PF1550)23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREBuck 1Buck 1 input supply25SW1LXBuck 1Buck 1 input supply26SW1INBuck 1Buck 1 input supply27SW1FBLD01LD0128VLD01INLD01LD0129VLD01LD01LD0131LICELLVSNVS31LICELLARAGER33VBATTCHARGER33VSYSIC core33VSYSIC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10         | RESETBMCU |         | RESETBMCU open-drain output                      |

| 12VLDO3LDO3 output13SW3LXBuck 3Buck 3 switching node14SW3INBuck 3Buck 3 sinpt supply15SW3FBBuck 3Buck 3 output voltage feedback16SW2FBBuck 2Buck 2 output voltage feedback17SW2INBuck 2Buck 2 switching node18SW2LXBuck 2 switching node19VLDO2LDO220VLDO2INLDO221VREFDDRVREFDDR22VINREFDDRVREFDDR output23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREBuck 1Buck 1 switching node25SW1INBuck 1Buck 1 switching node26SW1INBuck 1Buck 1 input supply27SV1FBLDO1LDO128VLDO1INLDO129VLDO1VSNVS30VSNVSVSNVS31LICELLConnect in put32VBATTCHARGER33VBATTGonnect thermistor to ground from this pin34VSYSIC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11         | VLDO3IN   | 1000    | LDO3 input supply                                |

| 14SW3INBuck 3Buck 3 input supply15SW3FBBuck 3 output voltage feedback16SW2FBBuck 2 output voltage feedback17SW2INBuck 2Buck 2 input supply18SW2LXBuck 2 input supply19VLD02LD0220VLD02INLD0221VREFDDRVREFDDR output22VINREFDDRVREFDDR output23VDIGIC core24VCOREBuck 125SW1LXBuck 126SW1INBuck 127SW1FBLD0128VLD01INLD0129VLD01LD0130VSNVSVSNVS31LICELLVSNVS33VBATTCore33VSSCore34VSSMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12         | VLDO3     | LDO3    | LDO3 output                                      |

| SW3FB     Buck 3 output voltage feedback       16     SW2FB     Buck 2 output voltage feedback       17     SW2IN     Buck 2     Buck 2 output voltage feedback       18     SW2LX     Buck 2 input supply       18     SW2LX     Buck 2 switching node       19     VLD02     LD02     LD02       20     VLD02IN     LD02     LD02 output       21     VREFDDR     VREFDDR output     VREFDDR output       22     VINREFDR     VREFDDR     VREFDDR output       23     VDIG     IC core     VDIG regulator output (used within PF1550)       24     VCORE     IC core     Buck 1 input supply       25     SW1IN     Buck 1     Buck 1 input supply       26     SW1IN     Buck 1     Buck 1 input supply       27     SW1FB     LD01     LD01       28     VLD01IN     LD01     Buck 1     Buck 1 input supply       29     VLD01     LD01     LD01 output     Coin cell input       31     LICELL     VSNVS     VSNVS regulator output for output for output       33     VBATT     Coin cell input     Battery input       33     VSNS     Core     Main input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13         | SW3LX     |         | Buck 3 switching node                            |

| InterpretationSW2FBBuck 2Buck 2 output voltage feedback17SW2INBuck 2Buck 2 input supply18SW2LXBuck 2 witching node19VLDO2LDO2LDO2 output20VLDO2INLDO2LDO2 output21VREFDDRVREFDDRVREFDDR output22VINREFDDRVREFDDRVREFDDR output23VDGLC coreVDIG regulator output (used within PF1550)24VCOREIC coreBuck 1 witching node25SW1LXBuck 1Buck 1 input supply26SW1INBuck 1Buck 1 input supply27SW1FBLDO1LDO128VLDO1INLDO1LDO129VLD01LDO1VSNVS31LICELLVSNVSVSNVS regulator output31LICELLThermistor connection<br>Connect thermistor to ground from this pin33VBATTIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14         | SW3IN     | Buck 3  | Buck 3 input supply                              |

| 17SW2INBuck 2Buck 2 input supply18SW2LXBuck 2 switching node19VLDO2LDO220VLDO2INLDO221VREFDDRVREFDDR22VINREFDDRVREFDDR23VDIGIC core24VCOREIC core25SW1LXBuck 126SW1INBuck 127SW1FBBuck 128VLDO1INLDO129VLDO1DD130VSNVSVSNVS31LICELLVSNVS31LICELLTHM33VBATTCHARGER35VSYSIC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15         | SW3FB     |         | Buck 3 output voltage feedback                   |

| 18     SW2LX     Buck 2 switching node       19     VLDO2     LDO2     LDO2 output       20     VLDO2IN     LDO2     LDO2 input supply       21     VREFDDR     VREFDDR output       22     VINREFDDR     VREFDDR input supply       23     VDIG     IC core     VDIG regulator output (used within PF1550)       24     VCORE     IC core     Buck 1 switching node       25     SW1LX     Buck 1     Buck 1 switching node       26     SW1IN     Buck 1     Buck 1 input supply       27     SW1FB     Buch 1     Buck 1 feedback input       28     VLDO1     LDO1     LDO1 output       30     VSNVS     VSNVS     VSNVS regulator output (used within PF1550)       31     LICELL     VSNVS     VSNVS       31     LICELL     VSNVS     VSNVS regulator output       33     VBATT     CHARGER     Thermistor connection<br>Connect thermistor to ground from this pin       33     VSYS     IC core     Main input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16         | SW2FB     |         | Buck 2 output voltage feedback                   |

| 19VLDO2LDO2LDO2LDO2 output20VLDO2INLDO2LDO2 outputLDO2 input supply21VREFDDRVREFDDRVREFDDR output22VINREFDDRVREFDDRVREFDDR input supply23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREIC coreBuck 1 switching node25SW1LXBuck 1Buck 1 switching node26SW1INBuck 1Buck 1 feedback input27SW1FBLDO1LDO128VLDO1INLDO1LDO1 output29VLD01VSNVSVSNVS31LICELLVSNVSVSNVS regulator output32THMCHARGERThermistor connection<br>Connect thermistor to ground from this pin33VSYSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17         | SW2IN     | Buck 2  | Buck 2 input supply                              |

| 20VLD02INLD02LD02 input supply21VREFDDRVREFDDRVREFDDR output22VINREFDDRVREFDDRVREFDDR input supply23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREIC coreVDIG regulator output (used within PF1550)25SW1LXBuck 1Buck 1 switching node26SW1INBuck 1Buck 1 feedback input27SW1FBLD01LD0128VLD01INLD01LD01 input supply29VLD01VSNVSVSNVS31LICELLVSNVSVSNVS regulator output32THMCHARGERThermistor connection<br>Connect thermistor to ground from this pin33VSNYSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18         | SW2LX     |         | Buck 2 switching node                            |

| 20VLDO2INLDO2 input supply21VREFDDRVREFDDRVREFDDR output22VINREFDDRVREFDDRVREFDDR input supply23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREEt coreBuck 1 switching node25SW1LXEt coreBuck 1 switching node26SW1INEt coreBuck 1 input supply27SW1FBEt coreBuck 1 input supply28VLDO1INEt DO1Et DO1 input supply29VLDO1Et DO1Et DO1 input supply30VSNVSVSNVSVSNVS regulator output31LICELLVSNVSVSNVS regulator output33FHMEt ARGERThermistor connection<br>Connect thermistor to ground from this pin33VSSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19         | VLDO2     | 1.500   | LDO2 output                                      |

| 22VINREFDDRVREFDDRVREFDDR23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREIC coreVDIG regulator output (used within PF1550)25SW1LXBuck 1Buck 1 switching node26SW1INBuck 1Buck 1 input supply27SW1FBBuck 1Buck 1 feedback input28VLDO1INLDO1LDO129VLDO1VSNVSVSNVS30VSNVSVSNVSVSNVS regulator output31LICELLVENVSCoin cell input32THMCHARGERThermistor connection<br>Connect thermistor to ground from this pin33VSYSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20         | VLDO2IN   | LDO2    | LDO2 input supply                                |

| 22VINREFDDRVREFDDR input supply23VDIGIC coreVDIG regulator output (used within PF1550)24VCOREEc coreVDIG regulator output (used within PF1550)25SW1LXBuck 1Buck 1 switching node26SW1INBuck 1Buck 1 input supply27SW1FBEuD01Buck 1 feedback input28VLD01INLD01LD01 input supply29VLD01CONSVSNVS31LICELLVSNVSVSNVS regulator output32THMEuAARGERThermistor connection<br>Connect thermistor to ground from this pin33VSN3VSN3Battery input34VSYSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21         | VREFDDR   |         | VREFDDR output                                   |

| 24VCOREIC coreVCORE regulator output (used within PF1550)25SW1LXABuck 1 switching node26SW1INBuck 1Buck 1 switching node27SW1FBBuck 1Buck 1 input supply28VLD01INLD01LD01 input supply29VLD01CO1LD01 input supply30VSNVSVSNVSVSNVS regulator output31LICELLVSNVSVSNVS regulator output32THMCHARGERThermistor connection<br>Connect thermistor to ground from this pin33VBATTIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22         | VINREFDDR |         | VREFDDR input supply                             |

| 24VCOREVCOREVCORE regulator output (used within PF1550)25SW1LXBuck 1Buck 1 switching node26SW1INBuck 1Buck 1 input supply27SW1FBBuck 1 feedback input28VLD01INLD01Buck 1 feedback input29VLD01LD01LD01 output30VSNVSVSNVSVSNVS regulator output31LICELLVSNVSVSNVS regulator output32THMPARTFCHARGERThermistor connection<br>Connect thermistor to ground from this pin33VSNSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23         | VDIG      | 10      | VDIG regulator output (used within PF1550)       |

| 26SW1INBuck 1Buck 1 input supply27SW1FBBuck 1 feedback input28VLD01INLD01LD01 input supply29VLD01VSNVSLD01 output30VSNVSVSNVSVSNVS regulator output31LICELLVSNVSCoin cell input32THMCHARGERThermistor connection<br>Connect thermistor to ground from this pin33VSNSLC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24         | VCORE     | IC core | VCORE regulator output (used within PF1550)      |

| 27     SW1FB     Buck 1 feedback input       28     VLD01IN     LD01       29     VLD01     LD01       30     VSNVS     VSNVS       31     LICELL       32     THM       33     VBATT       34     VSYS       35     VSYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25         | SW1LX     |         | Buck 1 switching node                            |

| 28VLDO1IN<br>29LDO1LDO1LDO1 input supply<br>LDO1 output29VLDO1LDO1LDO1 output30VSNVSVSNVSVSNVS regulator output31LICELLVSNVSCoin cell input32THMAARGERThermistor connection<br>Connect thermistor to ground from this pin33VBATTAARGERBattery input35VSYSIC coreMain input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26         | SW1IN     | Buck 1  | Buck 1 input supply                              |

| LDO1     LDO1       29     VLDO1       30     VSNVS       31     LICELL       32     THM       33     A       34     VBATT       35     VSYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27         | SW1FB     |         | Buck 1 feedback input                            |

| 29     VLDO1     LDO1 output       30     VSNVS     VSNVS       31     LICELL     Coin cell input       32     THM     Thermistor connection<br>Connect thermistor to ground from this pin       33     VBATT     FHARGER       35     VSYS     IC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28         | VLDO1IN   | 1004    | LDO1 input supply                                |

| 31     LICELL     VSNVS     Coin cell input       32     THM     Thermistor connection     Connect thermistor to ground from this pin       33     VBATT     CHARGER     Battery input       35     VSYS     IC core     Main input voltage to PMIC and output of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29         | VLDO1     | LDO1    | LDO1 output                                      |

| 31     LICELL     Coin cell input       32     THM     Thermistor connection<br>Connect thermistor to ground from this pin       33     VBATT     Battery input       35     VSYS     IC core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30         | VSNVS     |         | VSNVS regulator output                           |

| Connect thermistor to ground from this pin       33     Output       34     VBATT       35     VSYS   IC core Connect thermistor to ground from this pin Battery input Battery input Battery input Battery of charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31         | LICELL    | VSNVS   | Coin cell input                                  |

| 33     Battery input       34     Battery input       35     VSYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32         | ТНМ       |         |                                                  |