## National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# DS26LS32MQML Quad Differential Line Receivers

## **General Description**

The DS26LS32 and DS26LS32A are quad differential line receivers designed to meet the RS-422, RS-423 and Federal Standards 1020 and 1030 for balanced and unbalanced digital data transmission.

The DS26LS32 and DS26LS32A have an input sensitivity of 200 mV over the input voltage range of  $\pm 7V$  and the DS26LS33 have an input sensitivity of 500 mV over the input voltage range of  $\pm 15V$ .

The DS26LS32A differ in function from the popular DS26LS32 and DS26LS33 in that input pull-up and pull-down resistors are included which prevent output oscillation on unused channels.

Each version provides an enable and disable function common to all four receivers and features TRI-STATE ® outputs with 8 mA sink capability. Constructed using low power

Schottky processing, these devices are available over the full military and commerical operating temperature ranges.

#### **Features**

- High differential or common-mode input voltage ranges of ±7V on the DS26LS32.

- ±0.2V sensitivity over the input voltage range on the DS26LS32.

- DS26LS32 meet all requirements of RS-422 and RS-423

- 6k minimum input impedance

- 100 mV input hysteresis on the DS26LS32

- Operation from a single 5V supply

- TRI-STATE outputs, with choice of complementary output enables for receiving directly onto a data bus

### **Ordering Information**

| NS Part Number | SMD Part Number | NS Package Number | Package Description        |

|----------------|-----------------|-------------------|----------------------------|

| DS26LS32ME/883 | 5962-7802006Q2A | E20A              | 20LD LEADLESS CHIP CARRIER |

| DS26LS32MJ/883 | 5962-7802006QEA | J16A              | 16LD CERDIP                |

| DS26LS32MW/883 | 5962-7802006QFA | W16A              | 16LD CERPACK               |

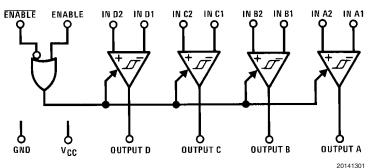

## **Logic Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

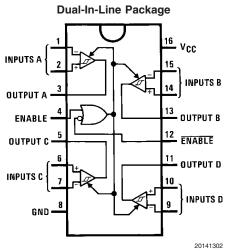

## **Connection Diagrams**

Top View

See NS Package Number J16A or W16A

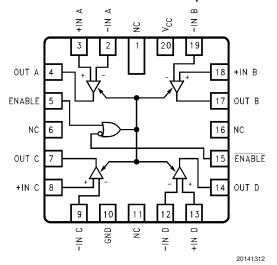

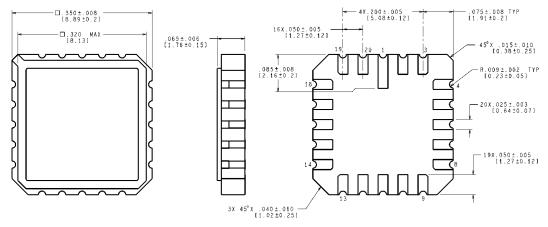

### 20-Lead Ceramic Leadless Chip Carrier

Top View See NS Package Number E20A,

## **Truth Table**

| ENABLE     | ENABLE | Input                     | Output |  |

|------------|--------|---------------------------|--------|--|

| 0          | 1      | 1 X                       |        |  |

| See        |        | $V_{ID} \ge V_{TH} (Max)$ | 1      |  |

| Note Below |        | $V_{ID} \le V_{TH} (Min)$ | 0      |  |

Hi-Z = TRI-STATE®

Note: Input conditions may be any combination not defined for ENABLE and ENABLE .

## **Absolute Maximum Ratings** (Note 1)

Supply Voltage7VCommon-Mode Range±25VDifferential Input Voltage±25VEnable Voltage7VOutput Sink Current50 mA

Maximum Power Dissipation at 25°C (Note 2)

J Package

1666.5 mW

E Package

1875 mW

W Package

967.74 mW

Junction Temperature (T,j)

+150°C

Thermal Resistance, Junction-to-Ambient

$\theta_{\mathsf{JA}}$

J Package 100°C/W E Package 130°C/W W Package 140°C/W

Thermal Resistance, Junction-to-Ambient

$\theta_{JC}$  See MIL-STD-1835 Storage Temperature Range  $-65^{\circ}\text{C}$  to  $+165^{\circ}\text{C}$  Lead Temperature (Soldering, 4 seconds)  $260^{\circ}\text{C}$  ESD Tolerance (Note 3) 500V

# Recommended Operating Conditions

Supply Voltage,  $V_{CC}$  4.5 V to 5.5 V Temperature,  $T_A$  -55°C to +125°C

## **Quality Conformance Inspection**

MIL-STD-883, Method 5005 - Group A

| Subgroup | Description         | Temp ( °C) |  |

|----------|---------------------|------------|--|

| 1        | Static tests at     | +25        |  |

| 2        | Static tests at     | +125       |  |

| 3        | Static tests at     | -55        |  |

| 4        | Dynamic tests at    | +25        |  |

| 5        | Dynamic tests at    | +125       |  |

| 6        | Dynamic tests at    | -55        |  |

| 7        | Functional tests at | +25        |  |

| 8A       | Functional tests at | +125       |  |

| 8B       | Functional tests at | -55        |  |

| 9        | Switching tests at  | +25        |  |

| 10       | Switching tests at  | +125       |  |

| 11       | Switching tests at  | -55        |  |

# **DS26LS32M 883 Electrical Characteristics DC Parameters**

The following conditions apply, unless otherwise specified.  $V_{\rm CC}$  = 5V

| Symbol                | Parameter                          | Conditions                                                                                     | Notes        | Min  | Max  | Unit | Sub-<br>groups |

|-----------------------|------------------------------------|------------------------------------------------------------------------------------------------|--------------|------|------|------|----------------|

|                       | Innut Current                      | $V_{CC} = 5.5V$ , $V_{IN} = 15V$ (Pin under test), other inputs -15V, $\leq V_{IN} \leq +15V$  | (Note 5)     |      | 2.3  | mA   | 1, 2, 3        |

| I <sub>IN</sub>       | Input Current                      | $V_{CC} = 5.5V$ , $V_{IN} = -15V$ (Pin under test), other inputs -15V, $\leq V_{IN} \leq +15V$ | (Note 5)     |      | -2.8 | mA   | 1, 2, 3        |

| I <sub>IL</sub>       | Logical "0" ENABLE Current         | $V_{CC} = 5.5V, V_{IN} = 0.4V$                                                                 | (Note 5)     |      | -360 | uA   | 1, 2, 3        |

| I <sub>IH</sub>       | Logical "1" ENABLE Current         | $V_{CC} = 5.5V, V_{IN} = 2.7V$                                                                 | (Note 5)     |      | 20   | uA   | 1, 2, 3        |

| I <sub>I</sub>        | Logical "1" ENABLE Current         | V <sub>CC</sub> =5.5V, V <sub>IN</sub> = 5.5V                                                  | (Note 5)     |      | 100  | uA   | 1, 2, 3        |

| V <sub>IC</sub>       | Input Clamp Voltage (ENABLE)       | V <sub>CC</sub> = 4.5V, I <sub>IN</sub> = -18mA                                                | (Note 5)     |      | -1.5 | V    | 1, 2, 3        |

| V <sub>OH</sub>       | Logical "1" Output Voltage         | $V_{CC} = 4.5V$ , $I_{OH} = -440uA$ , $\Delta V_{IN} = 1V$ , $V = NABLE = 0.8V$                | (Note 5)     | 2.5  |      | V    | 1, 2, 3        |

| V <sub>OL</sub>       | Logical "0" Output Voltage         | $V_{CC} = 4.5V, I_{OL} = 4mA,$<br>$\Delta V_{IN} = -1V, V \overline{ENABLE} = 0.8V$            | (Note 5)     |      | .4   | V    | 1, 2, 3        |

|                       |                                    | $V_{CC} = 4.5V, I_{OL} = 8mA,$<br>$\Delta V_{IN} = -1V, V \overline{ENABLE} = 0.8V$            | (Note 5)     |      | .45  | V    | 1, 2, 3        |

| I <sub>OS</sub> (MIN) | Output Short Circuit Current       | $V_{CC} = 5.5V, V_{O} = 0V,$<br>$\Delta V_{IN} = 1V$                                           | (Note 5)     | -15  |      | mA   | 1, 2, 3        |

| I <sub>OS</sub> (MAX) | Output Short Circuit Current       | $V_{CC} = 5.5V, V_{O} = 0V,$<br>$\Delta V_{IN} = 1V$                                           | (Note 5)     |      | -85  | mA   | 1, 2, 3        |

| I <sub>cc</sub>       | Supply Current                     | $V_{CC}$ = 5.5V, All $V_{IN}$ = GND,<br>Outputs Disabled                                       | (Note 5)     |      | 70   | mA   | 1, 2, 3        |

|                       | Off-State Output Current           | $V_{CC} = 5.5V, V_{O} = 0.4V$                                                                  | (Note 5)     |      | -20  | uA   | 1, 2, 3        |

| lo                    |                                    | $V_{CC} = 5.5V, V_{O} = 2.4V$                                                                  | (Note 5)     |      | 20   | uA   | 1, 2, 3        |

| V <sub>TH</sub>       | Differential Input Voltage         | $-7V \le V_{CM} \le 7V$                                                                        | (Notes 4, 5) | -0.2 | 0.2  | V    | 1, 2, 3        |

| R <sub>IN</sub>       | Input Resistance                   | -15V ≤ V <sub>CM</sub> ≤ 15V                                                                   | (Note 5)     | 6    |      | kohm | 1, 2, 3        |

| V <sub>IL</sub>       | Logical "0" Input Voltage (ENABLE) | V <sub>CC</sub> = 4.5V                                                                         | (Notes 4, 5) |      | 0.8  | V    | 1, 2, 3        |

| V <sub>IH</sub>       | Logical "1" Input Voltage (ENABLE) | V <sub>CC</sub> = 4.5V                                                                         | (Notes 4, 5) | 2    |      | V    | 1, 2, 3        |

## DS26LS32M 883 Electrical Characteristics (Continued)

## **AC Parameters - Propagation Delay Time**

The following conditions apply, unless otherwise specified.  $V_{\rm CC}$  = 5V

| Symbol               | Parameters             | Conditions                                | Notes    | Min | Max | Unit | Sub-<br>groups |

|----------------------|------------------------|-------------------------------------------|----------|-----|-----|------|----------------|

| t <sub>PLH</sub>     | Propagation Delay Time | C <sub>L</sub> = 15 <sub>P</sub> F        | (Note 6) |     | 30  | nS   | 9,11,          |

| t <sub>PLH</sub>     | Propagation Delay Time | C <sub>L</sub> = 15 <sub>P</sub> F        | (Note 6) |     | 120 | nS   | 10             |

| t <sub>PHL</sub>     | Propagation Delay Time | $C_L = 15_PF$                             | (Note 6) |     | 30  | nS   | 9,11,          |

| t <sub>PHL</sub>     | Propagation Delay Time | C <sub>L</sub> = 15 <sub>P</sub> F        | (Note 6) |     | 120 | nS   | 10             |

|                      |                        | ENABLE C <sub>L</sub> = 5 <sub>P</sub> F  | (Note 6) |     | 34  | nS   | 9              |

| $t_{PLZ}$            | Enable to Output       | ENABLE C <sub>L</sub> = 5 <sub>P</sub> F  | (Note 6) |     | 64  | nS   | 10             |

|                      |                        | ENABLE C <sub>L</sub> = 5 <sub>P</sub> F  | (Note 6) |     | 27  | nS   | 11             |

| t <sub>PHZ</sub> En  | Enable to Output       | ENABLE C <sub>L</sub> = 5 <sub>P</sub> F  | (Note 6) |     | 32  | nS   | 9,11,          |

|                      | Enable to Output       | ENABLE C <sub>L</sub> = 5 <sub>P</sub> F  | (Note 6) |     | 35  | nS   | 10             |

| t <sub>PZL</sub> Ena |                        | ENABLE C <sub>L</sub> = 15 <sub>P</sub> F | (Note 6) |     | 34  | nS   | 9              |

|                      | Enable to Output       | ENABLE C <sub>L</sub> = 15 <sub>P</sub> F | (Note 6) |     | 65  | nS   | 10             |

|                      |                        | ENABLE C <sub>L</sub> = 15 <sub>P</sub> F | (Note 6) |     | 27  | nS   | 11             |

|                      | Frankla to Outout      | ENABLE C <sub>L</sub> = 15 <sub>P</sub> F | (Note 6) |     | 35  | nS   | 9, 11          |

| t <sub>PZH</sub>     | Enable to Output       | ENABLE C <sub>L</sub> = 15 <sub>P</sub> F | (Note 6) |     | 65  | nS   | 10             |

**Note 1:** Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Derate J package 11.11 mW/°C above 25°C; derate E package 12.5 mW/°C above 25°C; derate W Package 6.4516 mW/°C for above 25°C.

Note 3: Human body model, 1.5k $\!\Omega$  in series with 100pF.

Note 4: Parameter tested go-no-go only.

Note 5: For Subgroups 1 and 2, power dissipation must be externally controlled at elevated temperatures.

Note 6: Tested at 25°C, guaranteed but not tested at +125°C & -55°C

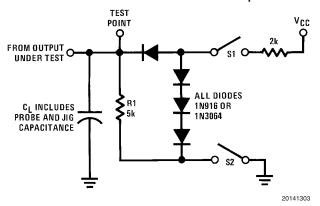

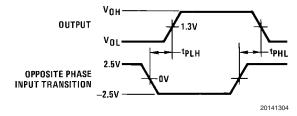

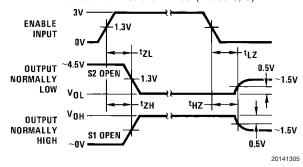

## **AC Test Circuit and Switching Time Waveforms**

### Load Test Circuit for TRI-STATE® Outputs

#### Propagation Delay (Notes 7, 9)

#### Enable and Disable Times (Notes 8, 9)

Note 7: Diagram shown for ENABLE low.

Note 8: S1 and S2 of load circuit are closed except where shown.

**Note 9:** Pulse generator for all pulses: Rate = 1.0 MHz;  $Z_O$  =  $50\Omega$ ;  $t_f \le 6$  ns;  $t_f \le 6.0$  ns.

## **Typical Applications**

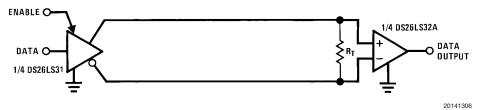

#### Two-Wire Balanced Interface — RS-422

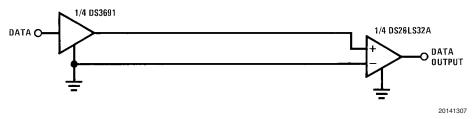

### Single Wire with Driver Ground Reference—RS-423

## **Revision History**

| Date<br>Released | Revision | Section                                                                                                                                                                                                    | Originator | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/20/05         | A        | New Release, Corporate format. Changes made in conversion: Ordering Info. Table, Absolute Ratings, Maximum Operating Conditions, Typo's in QMLV & RH, 883 AC Electrical Characteristics Parameters Column. | R. Malone  | 1 MDS data sheet converted into Corporate data sheet format. <b>Added:</b> SMD reference for 883 NSID's, Juction temp., Thermal Resistance $\theta_{JA}$ and $\theta_{JC}$ . <b>Changed:</b> Maximum Operating Conditions to Recommended Operating Conditions, Enable and Disable Time to Enable to Output. Deleted max limit: 27nS for $t_{PZH}$ and added subgroup 11 to max limit 35nS MDS data sheet MNDS26LS32–X, Rev. 280 will be Archived. |

| 10/05/06         | В        | Ordering Information                                                                                                                                                                                       | R. Malone  | Corrected suffix's in the SMD number. Revision A will be Archived.                                                                                                                                                                                                                                                                                                                                                                                |

## Physical Dimensions inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS INCH VALUES IN [] ARE MILLIMETERS

E20A (Rev F)

#### 20 Lead Ceramic Leadless Chip Carrier (E) NS Package Number E20A

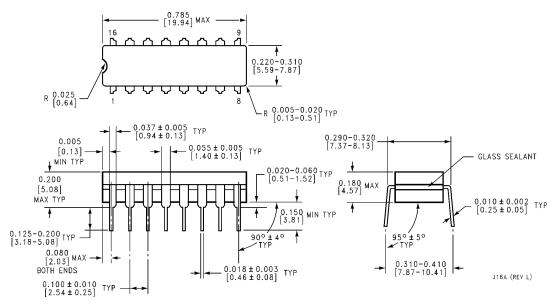

Ceramic Dual-In-Line Package (J) NS Package Number J16A

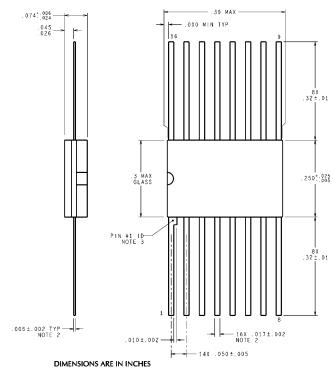

### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16 Lead Ceramic Flatpak (W) NS Package Number W16A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

W16A (Rev T)

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560