# USB97C201 Rev 1.6

# **USB 2.0 ATA/ ATAPI Controller**

#### **FEATURES**

- 2.5 Volt, Low Power Core Operation

- 3.3 Volt I/O with 5V input tolerance

- Complete USB Specification 2.0 Compatibility

- Includes USB 2.0 Transceiver

- A Bi-directional Control, a Bi-directional Interrupt, and a Bi-directional Bulk Endpoint are provided.

- Complete System Solution for interfacing ATA or ATAPI devices to USB 2.0 bus

- Supports USB Mass Storage Compliant Bootable BIOS

- Support for ATAPI Devices:

- CD-ROM

- CD-R

- CD-RW

- DVD

- DVD/R/W

- 8051 8 bit microprocessor

- Provides low speed control functions

- 30 Mhz execution speed at 4 cycles per instruction average

- 768 Bytes of internal SRAM for general purpose scratchpad or program execution while re-flashing external ROM

- Double Buffered Bulk Endpoint

- Bi-directional 512 Byte Buffer for Bulk Endpoint

- 64 Byte RX Control Endpoint Buffer

- 64 Byte TX Control Endpoint Buffer

- 64 Byte TX Interrupt Endpoint Buffer

- 64 Byte RX Interrupt Endpoint Buffer

- External Program Memory Interface

- 64K Byte Code Space

- Flash, SRAM, or EPROM Memory

- On Board 12Mhz Crystal Driver Circuit

- Internal PLL for 480Mhz USB2.0 Sampling, 30Mhz MCU clock, and 60Mhz ATA clock

- Supports firmware upgrade via USB bus if "boot block" Flash program memory is used

- 8 GPIOs for special function use: LED indicators, button inputs, etc.

- Inputs capable of generating interrupts with either edge sensitivity

- One GPIO has automatic ½ sec toggle capability for flashing an LED indicator.

- 100 Pin TQFP Package (14.0 x 14.0 mm footprint)

- 25% smaller body size than other 100 pin TQFP Packages

- 100 Pin QFP Package

### **ORDERING INFORMATION**

Order Number(s):

USB97C201-MN for 100 pin TQFP package

USB97C201-MC for 100 pin QFP package

© STANDARD MICROSYSTEMS CORPORATION (SMSC) 2003

80 Arkay Drive Hauppauge, NY 11788 (631) 435-6000 FAX (631) 273-3123

Standard Microsystems and SMSC are registered trademarks of Standard Microsystems Corporation. Product names and company names are the trademarks of their respective holders. Circuit diagrams utilizing SMSC products are included as a means of illustrating typical applications; consequently complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the semiconductor devices described any licenses under the patent rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT, TORT, NEGLIGENCE OF SMSC OR OTHERS, STRICT LIABILITY, BREACH OF WARRANTY, OR OTHERWISE; WHETHER OR NOT ANY REMEDY IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE; AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **TABLE OF CONTENTS**

| 1.0            | GENERAL DESCRIPTION             | 6   |

|----------------|---------------------------------|-----|

| 2.0            | PIN TABLE                       | 7   |

| 3.0            | PIN CONFIGURATION               | 8   |

| 3.1            | QFP/TQFP 100 Pin                | 8   |

| 4.0            | BLOCK DIAGRAM                   | 9   |

| 5.0            | PIN DESCRIPTIONS                |     |

| 5.1            | BUFFER TYPE DESCRIPTIONS        | .13 |

| 6.0            | FUNCTIONAL BLOCK DESCRIPTIONS   |     |

| 6.1            | MCU                             |     |

| 6.1.1          |                                 |     |

| 6.1.2          |                                 |     |

| 6.1.3<br>6.1.4 |                                 |     |

| 6.2            | SIE Block                       |     |

| 6.2.1          |                                 |     |

| 6.2.2          |                                 |     |

| 6.2.3          |                                 |     |

| 6.2.4          |                                 |     |

|                | IDE Controller Description      |     |

| 6.3.1          |                                 |     |

| 6.3.2          |                                 |     |

| 6.3.3          |                                 |     |

| 6.3.4          |                                 |     |

| 6.3.5          |                                 |     |

| 6.3.6          |                                 |     |

| 6.4            | SRAM Buffers                    |     |

| 6.5            | 8051 Options                    |     |

| 6.6            | Address Multiplexing            |     |

| 6.7            | SRAM Time Multiplexer Operation |     |

| 6.7.1          |                                 |     |

| 6.7.2          | Phase 1 (Ø1)                    | 49  |

| 6.7.3          | Phase 2 (Ø2)                    | 49  |

| 6.7.4          | Phase 3 (Ø3)                    | 50  |

| 6.8            | EP2 SRAM Buffer Operation       | 50  |

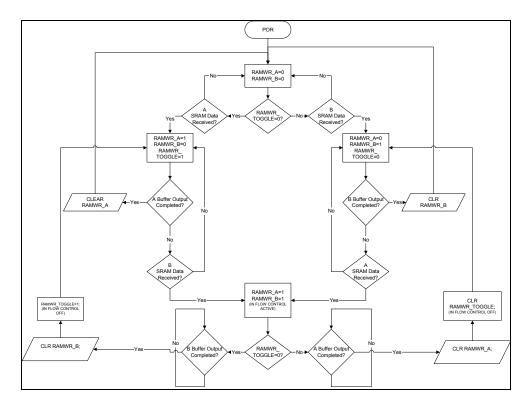

| 6.9            | EP2 Automatic Buffer Operations |     |

| 6.9.1          |                                 |     |

|                | Transmit Buffer Operation       |     |

| 6.9.3          | Automatic Transfer Operation    | 52  |

| 7.0            | DC PARAMETERS                   | .54 |

| 8.0            | AC SPECIFICATIONS               | 56  |

| 8.1            | ATA/ATAPI                       |     |

| 8.2            | USB2.0 Timing                   |     |

|                |                                 |     |

| 9.0            | PACKAGING                       |     |

| 10.0           | USB97C201 REVISIONS             | .59 |

# **TABLES**

| Table 1 - USB97C201 Buffer Type Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Table 2 - MCU Code Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| Table 3 - MCU XData Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Table 4 - MCU Block Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| Table 5 - 8051 Core SFR Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                                               |

| Table 6 - Interrupt 0 Source Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Table 7 - Interrupt 0 Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                               |

| Table 8 - Interrupt 1 Source Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Table 9 - Interrupt 1 Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| Table 10 - Device Revision Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Table 11 - Device Identification Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Table 12 - GPIO Direction Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 13 - GPIO Output Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Table 14 - GPIO Input Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Table 15 – GPIO Interrupt Status Register (INT4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Table 16 – GPIO Interrupt Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| Table 17 - Utility Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Table 18 – SRAM Data Port Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 19 – SRAM Address Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 20 – SRAM Address Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 21 - MCU Clock Source Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 22 - Wakeup Source 1 Register (INT2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| Table 23 - Wakeup Mask 1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Table 24 –USB Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Table 25 – SIE Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Table 26 - USB Bus Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ىدى                                                                              |

| Table 28 – SIE Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Table 29 – SIE Status Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Table 30 – USB Configuration Number Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| Table 30 – 03B Configuration Number Register  Table 31 – Endpoint 0 Receive Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                               |

| Table 32 – Endpoint 0 Transmit Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                               |

| Table 33 – Endpoint 1 Receive Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Table 34 – Endpoint 1 Transmit Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                                               |

| Table 35 – Endpoint 2 Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Table 36 – Endpoint 0 Receive Byte Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Table 37 – Endpoint 0 Transmit Byte Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 38 – Endpoint 1 Receive Byte Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Table 39 – Endpoint 1 Transmit Byte Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 40 – RAM Buffer Write Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| Table 41 – RAM BUFFER WRITE Byte Count Register A2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Table 42 – RAM Buffer Write Byte Count Register B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36                                                                               |

| Table 42 – RAM Buffer Write Byte Count Register B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36<br>36                                                                         |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                                               |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                               |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36<br>36                                                                         |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36<br>36<br>36                                                                   |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36<br>36<br>36                                                                   |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36<br>36<br>36<br>36                                                             |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36<br>36<br>36<br>36<br>36                                                       |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36<br>36<br>36<br>36<br>36<br>37                                                 |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36<br>36<br>36<br>36<br>37<br>37                                                 |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36<br>36<br>36<br>36<br>37<br>37                                                 |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 363636363637373838                                                               |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 363636363737383838                                                               |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3636363636373738383838                                                           |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register Table 44 – RAM Buffer Read Byte Count Register A1  Table 45 – RAM Buffer Read Byte Count Register A2 Register  Table 46 – RAM Buffer Read Byte Count Register B1  Table 47 – RAM Buffer Read Byte Count Register B2 Register  Table 48 – NAK Register (INT5)  Table 49 – NAK Mask Register  Table 50 – USB Error Register  Table 51 – MSB ATA Data Register  Table 52 – LSB ATA Data Register  Table 53 – ATA Transfer Count Register 0  Table 54 – ATA Transfer Count Register 1  Table 55 – ATA Transfer Count Register 2  Table 57 –ATA Control Register                                                                                                                                                                              | 363636363637373838383838                                                         |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36363636373738383838383838                                                       |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register Table 44 – RAM Buffer Read Byte Count Register A1  Table 45 – RAM Buffer Read Byte Count Register A2 Register  Table 46 – RAM Buffer Read Byte Count Register B1  Table 47 – RAM Buffer Read Byte Count Register B2 Register  Table 48 – NAK Register (INT5)  Table 49 – NAK Mask Register  Table 50 – USB Error Register  Table 51 – MSB ATA Data Register  Table 52 – LSB ATA Data Register  Table 53 – ATA Transfer Count Register 0  Table 54 – ATA Transfer Count Register 1  Table 55 – ATA Transfer Count Register 2  Table 56 – ATA Transfer Count Register 3  Table 57 –ATA Control Register  Table 58 –ATA Ultra DMA Timing Register  Table 59 – IDE Timing Register                                                           | 3636363637373838383838383838                                                     |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register Table 44 – RAM Buffer Read Byte Count Register A1 Table 45 – RAM Buffer Read Byte Count Register A2 Register Table 46 – RAM Buffer Read Byte Count Register B1 Table 47 – RAM Buffer Read Byte Count Register B2 Register Table 48 – NAK Register (INT5) Table 49 – NAK Mask Register Table 50 – USB Error Register Table 50 – USB Error Register Table 51 – MSB ATA Data Register Table 52 – LSB ATA Data Register Table 53 – ATA Transfer Count Register 0 Table 54 – ATA Transfer Count Register 1 Table 55 – ATA Transfer Count Register 2 Table 56 – ATA Transfer Count Register 3 Table 57 –ATA Control Register Table 58 –ATA Ultra DMA Timing Register Table 59 – IDE Timing Register Table 60 –ATA Slew Rate Control A Register | 36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>38<br>38<br>38<br>38<br>38<br>38 |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3636363637373838383838383838383838                                               |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36363636373738383838383838383838383838                                           |

| Table 43 – RAM Buffer Write Byte Count Register B2 Register.  Table 44 – RAM Buffer Read Byte Count Register A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

#### 51

# **FIGURES**

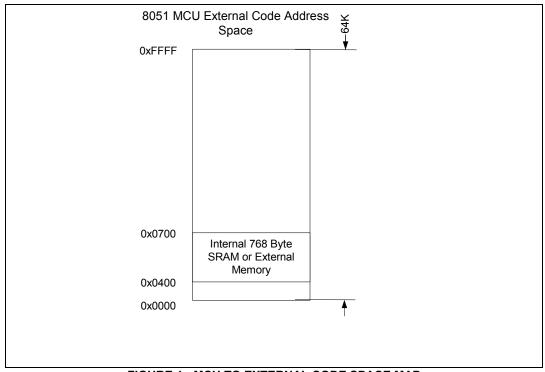

| Figure 1 - MCU to EXTERNAL CODE SPACE MAP    | .14 |

|----------------------------------------------|-----|

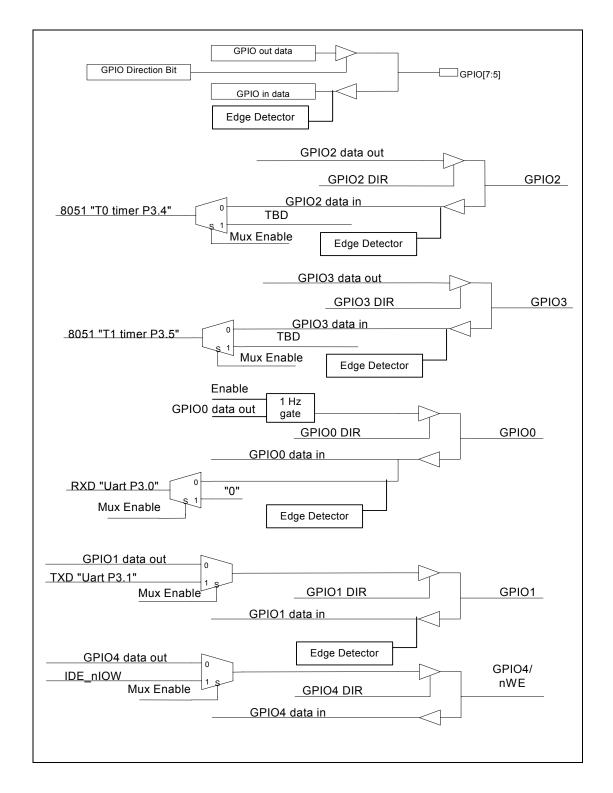

| Figure 2 - GPIO MUXING BLOCK DIAGRAM         | 23  |

| Figure 3 - RECEIVE BUFFER OPERATION          |     |

| Figure 4 - TRANSMIT BUFFER OPERATION         |     |

| Figure 5 - AUTOMATIC DATA TRANSFER OPERATION |     |

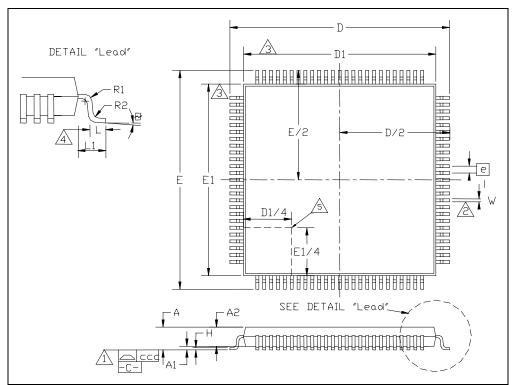

| Figure 6 - 100 PIN TQFP PACKAGE              |     |

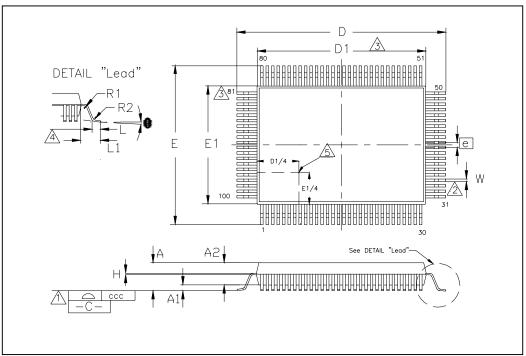

| Figure 7 – 100 PIN OFP PACKAGE               | 58  |

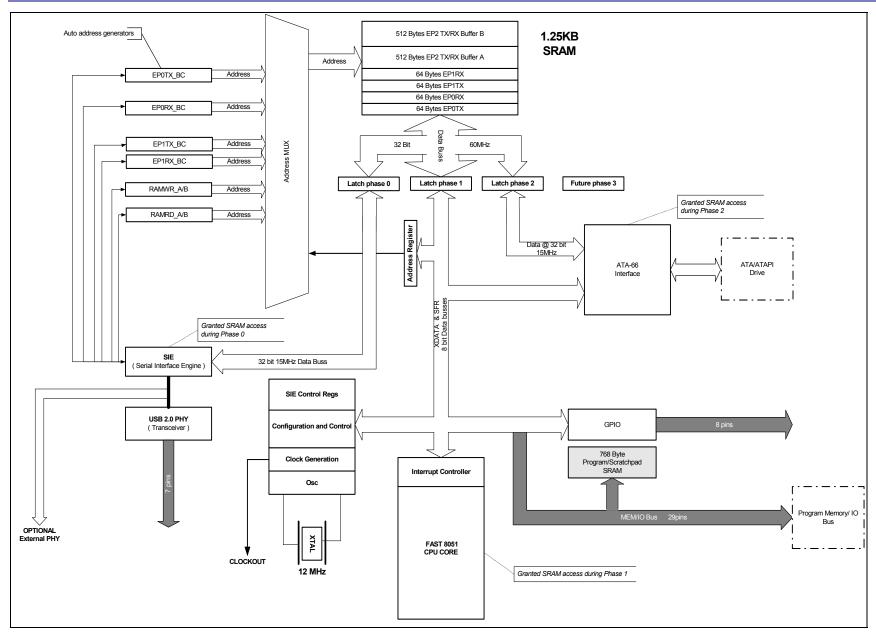

## 1.0 GENERAL DESCRIPTION

The USB97C201 is a USB2.0 Mass Storage Class Peripheral Controller intended for use with standard ATA hard drives and standard ATAPI-5 devices.

The device consists of a USB 2.0 PHY and SIE, buffers, Fast 8051 microprocessor with expanded scratchpad and 768 of program SRAM, and an ATA-66 compatible interface.

Provisions for external Flash Memory up to 64K bytes for program storage is provided.

Internal 768 Bytes of program SRAM are also provided.. This internal SRAM is used for program storage to implement program upgrade via USB download to "boot block" Flash program memory, if desired.

Eight GPIO pins are provided for controlling external power control elements and sensing specialized drive functions. Provisions are made to allow dynamic attach and re-attach to the USB bus to allow hot swap of drives to be implemented.

| DISK DRIVE INTERFACE (27 Pins)            |                 |                 |               |  |

|-------------------------------------------|-----------------|-----------------|---------------|--|

| IDE_D0                                    | IDE_D1          | IDE_D2          | IDE_D3        |  |

| IDE_D4                                    | IDE_D5          | IDE_D6          | IDE_D7        |  |

| IDE_D8                                    | IDE_D9          | IDE_D10         | IDE_D11       |  |

| IDE_D12                                   | IDE_D13         | IDE_D14         | IDE_D15       |  |

| IDE_nIOR                                  | IDE_nIOW        | IDE_IRQ         | IDE_DACK      |  |

| IDE_DRQ                                   | IDE_nCS0        | IDE_nCS1        | IDE_SA0       |  |

| IDE_SA1                                   | IDE_SA2         | IORDY           |               |  |

|                                           | USB INTERFA     | CE (7 Pins)     | _             |  |

| USBD+                                     | USBD-           | LOOPFLTR        | RBIAS         |  |

| RTERM                                     | FS+             | FS-             |               |  |

|                                           | MEMORY/IO INTER | RFACE (28 Pins) |               |  |

| MD0                                       | MD1             | MD2             | MD3           |  |

| MD4                                       | MD5             | MD6             | MD7           |  |

| MA0                                       | MA1             | MA2             | MA3           |  |

| MA4                                       | MA5             | MA6             | MA7           |  |

| MA8                                       | MA9             | MA10            | MA11          |  |

| MA12                                      | MA13            | MA14            | MA15          |  |

| nMRD                                      | nIOR            | nMWR            | nIOW          |  |

| MISC (15 Pins)                            |                 |                 |               |  |

| GPIO0                                     | GPIO1           | GPIO2           | GPIO3         |  |

| GPIO4/nWE                                 | GPIO5           | GPIO6           | GPIO7         |  |

| XTAL1/CLKIN                               | XTAL2           | nRESET          | nTEST/nDBGSTR |  |

| TST_OUT/DBGOUT                            | nTESTEN         | CLKOUT          |               |  |

| POWER, GROUNDS, and NO CONNECTS (23 Pins) |                 |                 |               |  |

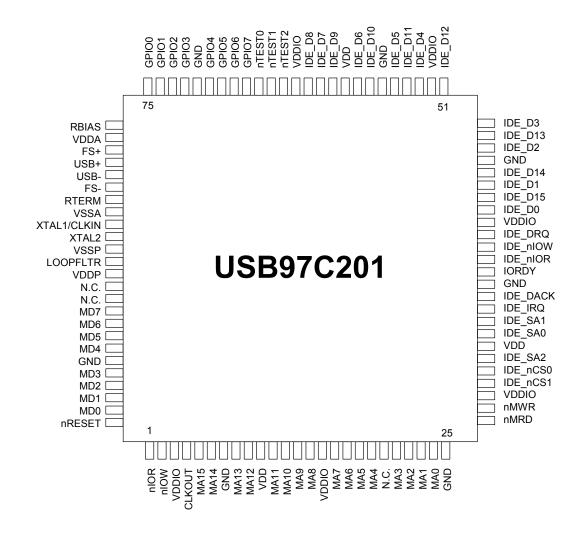

# 3.1 QFP/TQFP 100 Pin

SMSC USB97C201 Page 9 Rev. 11-05-03

| DISK DRIVE INTERFACE      |             |      |                                                                                    |  |

|---------------------------|-------------|------|------------------------------------------------------------------------------------|--|

| IDE DMA<br>Request        | IDE_DRQ     | IS   | This pin is the active high DMA request from the ATA/ATAPI interface.              |  |

| IDE IO Read<br>Strobe     | IDE_nIOR    | O20  | This pin is the active low read signal for the interface.                          |  |

| IDE Register<br>Address 1 | IDE_SA1     | O20  | This pin is the register select address bit 1 signal for the ATA/ATAPI interface.  |  |

| IDE Register<br>Address 0 | IDE_SA0     | O20  | This pin is the register select address bit 0 signal for the ATA/ATAPI interface.  |  |

| IDE Register<br>Address 2 | IDE_SA2     | O20  | This pin is the register select address bit 2 signal for the ATA/ATAPI interface.  |  |

| IDE Data                  | IDE_D15     | IO20 | This pin is the bi-directional data bus bit 15 signal for the ATA/ATAPI interface. |  |

| IDE IO Write<br>Strobe    | IDE_nIOW    | O20  | This pin is active low write signal for the ATA/ATAPI interface.                   |  |

| IDE DMA<br>Acknowledge    | IDE_nDACK   | O20  | This pin is the active low DMA acknowledge signal for the ATA/ATAPI interface.     |  |

| IDE Interrupt<br>Request  | IDE_IRQ     | IS   | This pin is the active high interrupt request signal for the ATA/ATAPI interface.  |  |

| IDE Data                  | IDE_D13     | IO20 | This pin is the bi-directional data bus bit 13 signal for the ATA/ATAPI interface. |  |

| IDE Data                  | IDE_D14     | IO20 | This pin is the bi-directional data bus bit 14 signal for the ATA/ATAPI interface. |  |

| IDE Chip<br>Select 0      | IDE_nCS0    | O20  | This pin is the active low chip select 0 signal for the ATA/ATAPI interface.       |  |

| IDE Chip<br>Select 1 0    | IDE_nCS1    | O20  | This pin is the active low select 1 signal for the ATA/ATAPI interface.            |  |

| IDE Data                  | IDE_D[0:12] | IO20 | These pins are bits 0-12 of the ATA/ATAPI bidirectional data bus.                  |  |

| IO Ready                  | IORDY       | I    | This pin is the active high IORDY signal from the IDE drive.                       |  |

| USB INTERFACE                |              |      |                                                                                                                              |  |

|------------------------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------|--|

| USB Bus<br>Data              | USB-<br>USB+ | IO-U | These pins connect to the USB bus data signals.                                                                              |  |

| USB<br>Transceiver<br>Filter | LOOPFLTR     |      | This pin provides the ability to supplement the internal filtering of the transceiver with an external network, if required. |  |

| USB<br>Transceiver<br>Bias   | RBIAS        |      | A 9.09 Kohm precision resistor is attached from ground to this pin to set the transceiver's internal bias currents.          |  |

| Termination<br>Resistor      | RTERM        |      | A precision 1.5Kohm precision resistor is attached to this pin from a 3.3V supply.                                           |  |

| Full Speed<br>USB Data       | FS-<br>FS+   | IO-U | These pins connect to the USB- and USB+ pins through 31.6 ohm series resistors.                                              |  |

| MEMORY/IO INTERFACE    |          |      |                                                                                                   |  |

|------------------------|----------|------|---------------------------------------------------------------------------------------------------|--|

| Memory Data<br>Bus     | MD[7:0]  | IO12 | These signals are used to transfer data between the internal CPU and the external program memory. |  |

| Memory<br>Address Bus  | MA[15:0] | O12  | These signals address memory locations within the external memory.                                |  |

| Memory Write<br>Strobe | nMWR     | O12  | Program Memory Write; active low                                                                  |  |

| Memory Read<br>Strobe  | nMRD     | O12  | Program Memory Read; active low                                                                   |  |

| IO Read<br>Strobe      | nIOR     | O12  | XDATA space Read; active low                                                                      |  |

| IO Write<br>Strobe     | nIOW     | O12  | XDATA space Write; active low                                                                     |  |

| MISC                                     |                 |                   |                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Crystal<br>Input/External<br>Clock Input | XTAL1/<br>CLKIN | ICLKx             | 12Mhz Crystal or external clock input. This pin can be connected to one terminal of the crystal or can be connected to an external 12Mhz clock when a crystal is not used.                                                                                                                                                                                               |  |

| Crystal Output                           | XTAL2           | OCLKx             | 12Mhz Crystal This is the other terminal of the crystal, or left open when an external clock source is used to drive XTAL1/CLKIN. It may not be used to drive any external circuitry other than the crystal circuit.                                                                                                                                                     |  |

| Clock Output                             | CLKOUT          | O8                | This pin produces a 30Mhz clock signal independent of the processor clock divider. It is held inactive and low whenever the internal processor clock is stopped or is being obtained from the ring oscillator.                                                                                                                                                           |  |

| General<br>Purpose I/O                   | GPIO[0:7]       | IO20              | These general purpose pins may be used either as inputs, edge sensitive interrupt inputs, or outputs. In addition, GPIO0 has the capability of auto-toggling at a 1Hz rate when used as an output.                                                                                                                                                                       |  |

| RESET input                              | nRESET          | IS                | This active low signal is used by the system to reset the chip. The active low pulse should be at least 100ns wide.                                                                                                                                                                                                                                                      |  |

| Test input                               | nTest[0:2}      | IP                | These signals are used for testing the chip. User should normally leave them unconnected. For board testing, all pads except these test inputs are included in an XNOR chain, such that by tying nTEST2 low, nIOR will reflect the toggling of a signal on each pin. Circuit board continuity of the pin solder connections after assembly can be checked in this manner |  |

|                                          | POWE            | R, GROUN          | DS, and NO CONNECTS                                                                                                                                                                                                                                                                                                                                                      |  |

|                                          | VDD             |                   | +2.5V Core power                                                                                                                                                                                                                                                                                                                                                         |  |

|                                          | VDDIO           |                   | +3.3V I/O power                                                                                                                                                                                                                                                                                                                                                          |  |

|                                          | VDDP            | +2.5 Analog power |                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                          | VSSP            |                   | Analog Ground Reference                                                                                                                                                                                                                                                                                                                                                  |  |

|                                          | VDDA            |                   | +3.3V Analog power                                                                                                                                                                                                                                                                                                                                                       |  |

|                                          | VSSA            |                   | Analog Ground Reference                                                                                                                                                                                                                                                                                                                                                  |  |

|                                          | GND             |                   | Ground Reference                                                                                                                                                                                                                                                                                                                                                         |  |