## Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

December 2009

# 24-Bit Ultra-Low Power Serializer / Deserializer Supporting Single and Dual Displays

## **Features**

Ultra-Low Operating Power: ~4mA at 5.44MHz

Supports Dual-Display Implementations with RGB or

Microcontroller Interface

No External Timing Reference Needed

SPI Mode Support

Single Device Operates as a Serializer or Deserializer Direct Support for Motorola®-Style R/W Microcontroller Interface

Direct Support for Intel®-Style /WE, /RE Microcontroller Interface

15MHz Maximum Strobe Frequency

Utilizes Fairchild's Proprietary CTL Serial I/O Technology

Available in BGA and MLP packages

Wide Parallel Supply Voltage Range: 1.60 to 3.0V

Low Power Core Operation: V<sub>DDS/A</sub>=2.5 to 3.0V

Voltage Translation Capability Across Pair with No External Components

High ESD Protection: >15kV IEC 61000 Power-Saving Burst-Mode Operation

## **Applications**

Single or Dual 16/18-Bit RGB Cell Phone Displays

- Single or Dual 16/18-Bit Cell Phone Displays with Microcontroller Interface

- Single or Dual Mobile Display at QVGA or HVGA Resolution

## Description

The FIN324C is a 24-bit serializer / deserializer with dual strobe inputs. The device can be configured as a master or slave device through the master/slave select pin (M/S). This allows for the same device to be used as either a serializer or deserializer, minimizing component types in the system. The dual strobe inputs allow implementation of dual-display systems with a single pair of  $\mu SerDes$ . The FIN324C can accommodate RGB, microcontroller, or SPI mode interfaces. Read and write transactions are supported when operating with a microcontroller interface for one or both displays. Unlike other SerDes solutions, no external timing reference is required for operation.

The FIN324C is designed for ultra-low power operation. Reset (/RES) and standby (/STBY) signals put the device in an ultra-low power state. In standby mode, the outputs of the slave device maintain state, allowing the system to resume operation from the last-known state.

The device utilizes Fairchild's proprietary ultra-low power, low-EMI Current Transfer Logic<sup>™</sup> (CTL) technology. The serial interface disables between transactions to minimize EMI at the serial interface and to conserve power. CMOS parallel output buffers have been implemented with slew rate control to adjust for capacitive loading and to minimize EMI.

## **Related Application Notes**

For additional Information, please visit: http://www.fairchildsemi.com/userdes.

- AN-5058 µSerDes™ Frequently Asked Questions

- AN-5061 µSerDes™ Layout Guidelines

- AN-6047 FIN324C Reset and Standby

# **Ordering Information**

| Order Number | Operating<br>Temperature<br>Range | Package Description                                                                                       | © Eco Status | Packing<br>Method |

|--------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------|--------------|-------------------|

| FIN324CMLX   | -30 to 85°C                       | 40-Terminal Molded Leadless Package (MLP), Quad, JEDEC MO-220, 6mm Square                                 | Green        | Tape & Reel       |

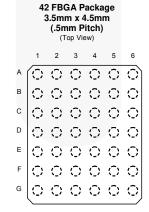

| FIN324CGFX   | -30 to 85°C                       | 42-Ball, Ultra Small Scale Ball Grid Array (USS-BGA),<br>JEDEC MO-195, 3.5 x 4.5mm Wide, 0.5mm Ball Pitch | RoHS         | Tape & Reel       |

For Fairchild's definition of "green" Eco Status, please visit: http://www.fairchildsemi.com/company/green/rohs\_green.html.

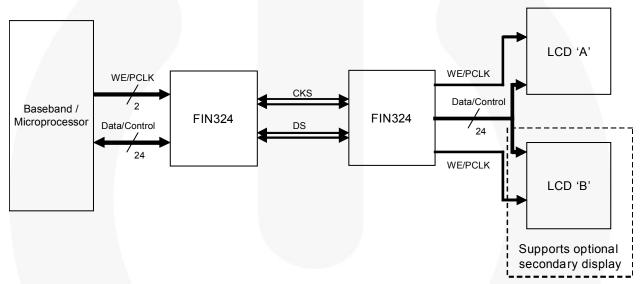

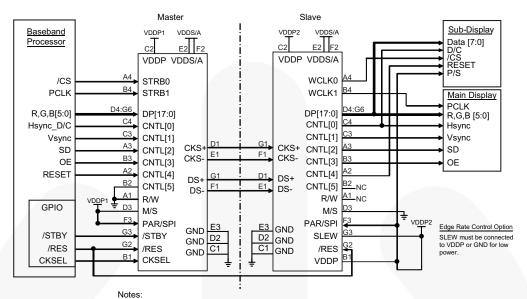

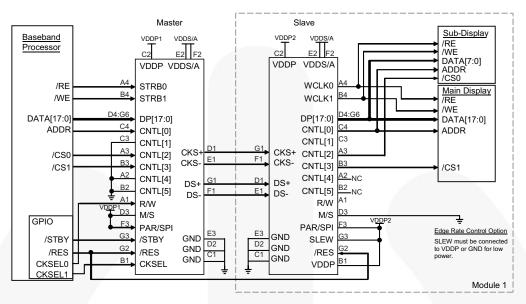

# **Typical Application Diagram**

Figure 1. Typical Application Diagram

## **Pin Definitions**

| Pin                 | I/O Type                   | # Pins | Description of Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M/S                 | CMOS IN                    | 1      | Master/Slave Control Input: The master is tied to the processor. The slave is tied to the display(s). M/S=1 MASTER, M/S=0 SLAVE                                                                                                                                                                                                                                                                                                                                                 |

| /RES                | CMOS IN                    | 1      | Reset and power-down signal /RES=0: Resets and powers down all circuitry /RES=1: Device enabled                                                                                                                                                                                                                                                                                                                                                                                 |

| /STBY               | CMOS IN                    | 1      | Master standby signal /STBY=0: Device powered down /STBY=1: Device enabled                                                                                                                                                                                                                                                                                                                                                                                                      |

| SLEW                | CMOS IN                    | 1      | Slave output slew rate control SLEW=1: Fast edge rate SLEW=0: Slow edge rate                                                                                                                                                                                                                                                                                                                                                                                                    |

| PAR/SPI             | CMOS IN                    | 1      | Parallel / SPI display interface select PAR/SPI=1: Parallel Interface PAR/SPI=0: SPI Interface using STRB0 and WCLK0                                                                                                                                                                                                                                                                                                                                                            |

| CKSEL               | CMOS IN                    | 1      | Master clock source select input. CKSEL=1: STRB1 and WCLK1 Active CKSEL=0: STRB0 and WCLK0 Active                                                                                                                                                                                                                                                                                                                                                                               |

| DP[17:0]            | CMOS I/O                   | 18     | Parallel data I/O. I/O direction controlled by M/S pin and R/W internal state. DP[6] SPI mode SCLK signal pin when PAR/SPI=0 (Slave Only) DP[7] SPI mode SDAT signal pin when PAR/SPI=0(Slave Only)                                                                                                                                                                                                                                                                             |

| CNTL[5:0]           | CMOS I/O                   | 6      | Parallel data I/O. I/O direction controlled by M/S pin M/S=1: Inputs M/S=0: Outputs                                                                                                                                                                                                                                                                                                                                                                                             |

| R/W                 | CMOS I/O                   | 1      | Read / Write input control or output signal. M/S=1: Input M/S=0: Output Functional operation: R/W=1: Read R/W=0: Write                                                                                                                                                                                                                                                                                                                                                          |

| STRB0<br>STRB1      | CMOS IN                    | 2      | Word latch or pixel clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WCLK0<br>WCLK1      | CMOS<br>OUT                | 2      | Word latch or pixel clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SCLK<br>SDAT<br>/CS | CMOS I/O                   | 2      | SPI mode signal pins. The master SCLK input is shared with CNTL[5] when M/S=1 and PARI/SPI=0. The master SDAT input is shared with CNTL[4] when M/S=1 and PARI/SPI=0. The master /CS input is shared with STRB0 when M/S=1 and PAR/SPI=0. The slave SCLK output is shared with DP[6] and CNTL[5] when M/S=0 and PAR/SPI=0. The slave SDAT output is shared with DP[7] and CNTL[4] when M/S=0 and PAR/SPI=0. The slave /CS output is shared with WCLK0 when M/S=0 and PAR/SPI=0. |

| CKS+<br>CKS-        | Differential<br>Serial I/O | 2      | Serial clock differential signal <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DS+<br>DS-          | Differential<br>Serial I/O | 2      | Serial data differential signal <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDP                | Supply                     | 1      | Power supply for parallel I/O and internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDDS                | Supply                     | 1      | Power supply for serial I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDA                | Supply                     | 1      | Power supply for internal bit clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GND                 | Supply                     | 1-3    | Ground Pins: BGA - C1 and D2; E3 is for supplier use only and must be tied to ground. MLP - center pad; Pin 12 is for supplier use only and must be tied to ground.                                                                                                                                                                                                                                                                                                             |

#### Note:

1. Serial I/O signals are swapped on the slave so system traces do not have to cross between master and slave.

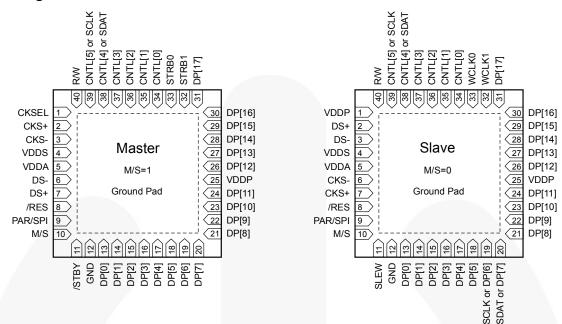

## **Pin Assignments**

Figure 2. MLP Pin Assignments (40 Pins, 6x6mm, .5mm Pitch, Top View)

|   | Master (M/S=1) |                    |         |         |        |        |  |  |  |  |

|---|----------------|--------------------|---------|---------|--------|--------|--|--|--|--|

|   | 1              | 2                  | 3       | 4       | 5      | 6      |  |  |  |  |

| Α | R/W            | CNTL[4]<br>or SDAT | CNTL[2] | STROB0  | DP[17] | DP[16] |  |  |  |  |

| В | CKSEL          | CNTL[5]<br>or SCLK | CNTL[3] | STROB1  | DP[15] | DP[14] |  |  |  |  |

| С | GND            | VDDP               | CNTL[1] | CNTL[0] | DP[13] | DP[12] |  |  |  |  |

| D | CKS+           | GND                | M/S     | DP[11]  | DP[9]  | DP[10] |  |  |  |  |

| Е | CKS-           | VDDS               | GND     | DP[2]   | DP[7]  | DP[8]  |  |  |  |  |

| F | DS-            | VDDA               | PAR/SPI | DP[0]   | DP[4]  | DP[6]  |  |  |  |  |

| G | DS+            | DS+ /RES           |         | DP[1]   | DP[3]  | DP[5]  |  |  |  |  |

| Slave (M/S=0) |      |                    |         |         |                  |                  |  |  |  |  |

|---------------|------|--------------------|---------|---------|------------------|------------------|--|--|--|--|

|               | 1    | 2                  | 3       | 4       | 5                | 6                |  |  |  |  |

| Α             | R/W  | CNTL[4]<br>or SDAT | CNTL[2] | WCLK0   | DP[17]           | DP[16]           |  |  |  |  |

| В             | VDDP | CNTL[5]<br>or SCLK | CNTL[3] | WCLK1   | DP[15]           | DP[14]           |  |  |  |  |

| С             | GND  | VDDP               | CNTL[1] | CNTL[0] | DP[13]           | DP[12]           |  |  |  |  |

| D             | DS+  | GND                | M/S     | DP[11]  | DP[9]            | DP[10]           |  |  |  |  |

| Е             | DS-  | VDDS               | GND     | DP[2]   | DP[7] or<br>SDAT | DP[8]            |  |  |  |  |

| F             | CKS- | VDDA               | PAR/SPI | DP[0]   | DP[4]            | DP[6] or<br>SCLK |  |  |  |  |

| G             | CKS+ | /RES               | SLEW    | DP[1]   | DP[3]            | DP[5]            |  |  |  |  |

Figure 3. BGA Pin Assignments

## **System Control Pins**

(M/S) Master / Slave Selection: A given device can be configured as a master or slave device based on the state of the M/S pin.

Table 1. Master/Slave

| M/S | Configuration |

|-----|---------------|

| 0   | Slave Mode    |

| 1   | Master Mode   |

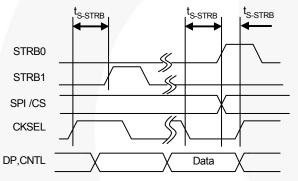

**(PAR/SPI) SPI Mode Selection:** The PAR/SPI signal configures STRB0(WCLK0) for SPI mode write operation. STRB1(WCLK1) always operates in parallel mode. Control signals CNTL[5:0] all pass in SPI mode. In SPI mode, the SCLK signal is used to strobe the serializer. SPI mode supports SPI writes only.

Table 2. Channel 0 PAR/SPI Configuration

| PAR<br>/SPI | M/S=1 MASTER                                          | M/S=0 SLAVE                                                           |

|-------------|-------------------------------------------------------|-----------------------------------------------------------------------|

| 0           | SPI Mode<br>SDAT=CNTL[4]<br>SCLK=CNTL[5]<br>/CS=STRB0 | SPI Mode<br>SDAT=DP[7] & CNTL[4]<br>SCLK=DP[6] & CNTL[5]<br>/CS=WCLK0 |

| 1           | Parallel Mode                                         | Parallel Mode                                                         |

(CKSEL) Strobe Selection Signal: The CKSEL signal exists only on the master device and determines which strobe signal is active. The active strobe signal is selected by CKSEL and PAR/SPI inputs.

Table 3. PAR/SPI

| PAR<br>/SPI | CKSEL | Master<br>Strobe<br>Source | Slave Strobe<br>Source |  |  |  |  |  |

|-------------|-------|----------------------------|------------------------|--|--|--|--|--|

| 0           | 0     | CNTL[5]                    | DP[6] & CNTL[5]        |  |  |  |  |  |

| 0           | 1     | STRB1                      | WCLK1                  |  |  |  |  |  |

| 1           | 0     | STRB0                      | WCLK0                  |  |  |  |  |  |

| 1           | 1     | STRB1                      | WCLK1                  |  |  |  |  |  |

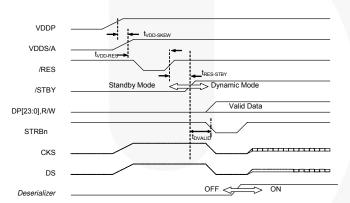

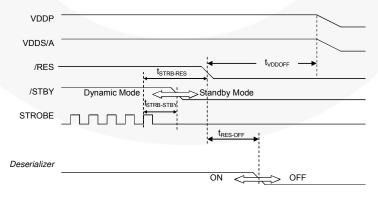

(/RES, /STBY) Reset and Standby Mode Functionality: Reset and standby mode functionality is determined by the state of the /RES and /STBY signals for the master device and the /RES and internal standby-detect signal for the slave device. The /RES control signal has a filter that rejects spurious pulses on /RES.

Table 4. Reset and Standby Modes

|      | , , , , , , , , , , , , , , , , |                   |                                |  |  |  |  |  |

|------|---------------------------------|-------------------|--------------------------------|--|--|--|--|--|

| /RES | /STBY <sup>(2)</sup> Master     |                   | Slave                          |  |  |  |  |  |

| 0    | Х                               | Reset Mode        | Reset Mode                     |  |  |  |  |  |

| 1    | 0                               | Standby<br>Mode   | Standby<br>Mode <sup>(2)</sup> |  |  |  |  |  |

| 1    | 1                               | Operating<br>Mode | Operating<br>Mode              |  |  |  |  |  |

#### Note:

2. The slave device is put into standby mode through control signals sent from the master device.

Table 5. Reset and Standby Mode States

| Pin                      | Master<br>Reset / Standby | Slave<br>Reset | Slave<br>Standby |

|--------------------------|---------------------------|----------------|------------------|

| DP[17:0]                 | Disabled                  | Low            | Last Data        |

| CNTL[5:0]                | Disabled                  | Low            | Last Data        |

| STRB[0:1]<br>(WCLK[0:1]) | Disabled                  | High           | High             |

**(SLEW) Slew Control:** The slew control operates only when in slave mode. This signal changes the edge rate of the DP[17:0], CNTL[5:0], R/W, WCLK1, and WCLK0 signals to optimize edge rate for the load being driven. Master read mode outputs have "slow" edge rates. See the AC Deserializer Specifications table for "slow" and "fast" edge rates.

**Table 6. Slew Rate Control**

| /STBY (SLEW) | Slave M/S=0 |

|--------------|-------------|

| 0            | "Slow"      |

| 1            | "Fast"      |

## **CMOS I/O Signals**

## **System Control Signals**

The system control signals consist of M/S, /RES, /STBY(SLEW), PAR/SPI, and CKSEL. For connectivity flexibility, these signals are over-voltage tolerant to the maximum supply voltage connected to the device. This allows these signals to be tied HIGH to either a  $V_{\rm DDS}$  or  $V_{\rm DDP}$  supply without static current consumption. These signals are all CMOS inputs and should never be allowed to float.

## Parallel I/O Signals

The parallel data port signals consist of the DP[17:0], CNTL[5:0], R/W, and STRB1(0)(WCLK1(0)) signals. These signals have built-in voltage translation, allowing the signals of the master and slave to be connected to different  $V_{\text{DDP}}$  supply voltages.

MLP

Slave

## Serial I/O Signals

## CTL I/O Technology

The serial I/O is implemented using Fairchild's proprietary differential CTL I/O technology. During data transfers, the serial I/O are powered up to a normal operating mode around .5V. Upon completion of a data transfer, the serial I/O goes to a lower power mode around V<sub>DDS</sub>.

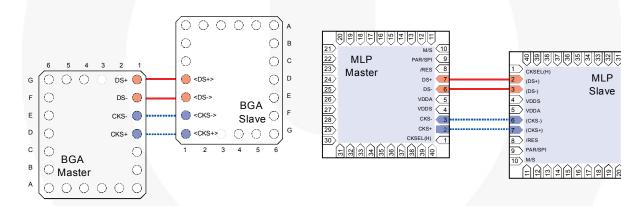

The serial I/O signal traces should not cross between the master and the slave. The pin locations have been designed to eliminate the need to cross traces. See Table 7, Figure 4, and Figure 5.

## **Serial I/O Orientation Logic**

**Table 7. Serial Pin Orientation**

|         | Master (M/S=1) (Pad/Pin #) |      |     |     | S    | lave (M/S=0) | (Pad/Pin # | )   |

|---------|----------------------------|------|-----|-----|------|--------------|------------|-----|

| Package | CKS+                       | CKS- | DS- | DS+ | CKS+ | CKS-         | DS-        | DS+ |

| MLP     | 2                          | 3    | 6   | 7   | 7    | 6            | 3          | 2   |

| BGA     | D1                         | E1   | F1  | G1  | G1   | F1           | E1         | D1  |

Figure 4. **BGA Pair**

Figure 5. **MLP Pair**

## Master/Slave READ Transactions

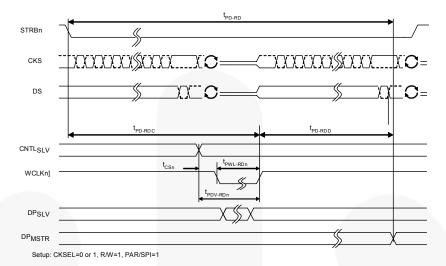

Read transactions have two phases: The Read-Control Phase, where CNTL[5:0], R/W, CKSEL are transmitted to the deserializer; and the Read-Data Phase, where the DP[17:0] signals of the slave are read and transmitted back to the master device. The slave device generates its own strobe signal for latching in the data. Slave data must be valid prior to the WCLKn signal going HIGH.

#### Master Serializer Operation (Read Control Phase)

When the R/W signal is asserted HIGH and the STROBE signal transitions LOW, the Read-Control Phase of the read cycle is initiated. The R/W signal must not transition until the READ cycle completes. For a READ transaction, only eight control signals are captured. The 18 DP bits are ignored during the READ operation. The following sequence must occur for data to be serialized properly:

- 1. CPU selects input strobe source (CKSEL=0 or 1).

- 2. CPU sends signals (R/W=1, CKSEL, CNTL[5:0]).

- 3. CPU sends LOW STROBE signal.

#### Slave Deserializer Operation (Read-Control Phase)

- 1. Captures data from serial transfer.

- 2. Internally decodes that this is a READ transaction.

- Outputs control signals and prepares DP pins to accept data.

- 4. Outputs falling edge of WCLK pulse.

#### Slave Serializer Read Operation (Read-Data Phase)

The slave serializer is enabled on the tail end of the Read-Control Phase of operation. The operation of the serializer is identical to the master serialization except that the strobe signal is generated internally and only the data bits DP[17:0] are captured.

- Display device outputs data onto DP bus on falling edge of WCLK.

- Captures parallel data on generated rising edge of WCLK signal.

- 3. Serializes data stream.

#### Master Deserializer Read Operation (Read-Data Phase):

- 1. Receives valid serial stream.

- 2. Outputs data DP[17:0].

- 3. CPU asserts rising edge of strobe signal to capture data.

### **SPI WRITE transaction**

SPI mode is activated by asserting the PAR/SPI signal low on both the master and slave device. A SPI write is only performed when CKSEL=0. During a SPI transaction, SCLK must be connected to CNTL[5] and is the strobe source for serialization. SDAT is on CNTL[4] and all of the remaining control signals and STRB0 are serialized. STRB0 should be connected to the SPI mode chip select.

On the rising edge of SCLK, all eight control signals (CNTL[5:0], R/W, CKSEL) are captured and serialized. The data signals are not sent. The deserializer captures the serial stream and outputs it to the parallel port.

As shown in Table 2, SDAT and SCLK are output on multiple pins. The DP[7] and DP[6] connections can be used for displays with dual-mode operation and the data pins are multiplexed with the SPI signals. CNTL[5] and CNTL[4] signals can be used when the signals are not multiplexed.

## **Applications Diagrams**

- Write-only Interface

- Unused slave output pin must be NC (No Connection).

- /CS used to strobe sub-display data.

- PCLK used for RGB mode.

- 5. Pin numbers for BGA package.

Figure 6. Dual Display with Parallel RGB Main Display and 6800-Style Microcontroller Sub-Display

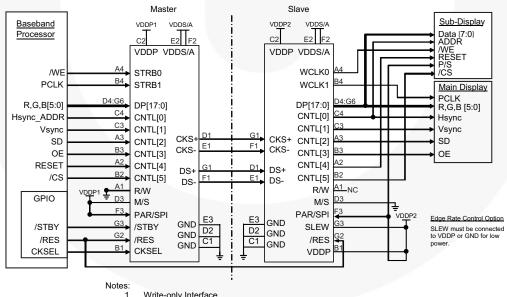

- Write-only Interface.

- Unused slave output pin must be NC (No Connection). 2.

- 3. /WE used to strobe sub-display data

- 4. PCLK used for RGB mode.

- Pin numbers for BGA package.

Figure 7. Dual Display with Parallel RGB Main Display and x86-Style Microcontroller Sub-Display

## **Application Diagrams** (Continued)

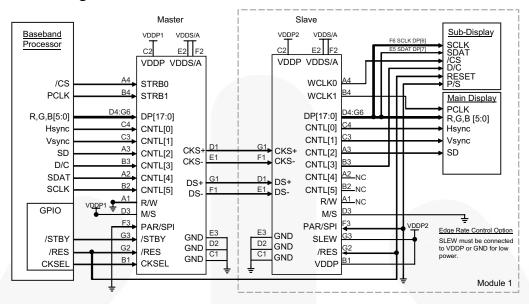

#### Notes:

- 1. Write-only interface (R/W hardwired LOW).

- SPI sub-display interface PAR/SPI=LOW for both master and slave.

- SCLK connected to CNTL[5]; SDAT connected to CNTL[4].

- Shared data pin SDAT; SCLK connections on sub-display.

Unused slave output pin must be NC (No Connection).

- 6. Pin numbers for BGA package.

Figure 8. Dual Display with RGB Main Display and SPI Sub-Display Interface

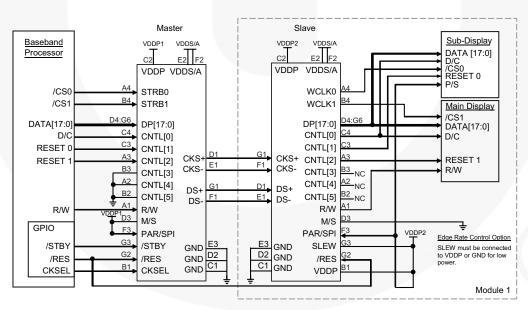

#### Notes:

- R/W interface. R/W signal connected to baseband microprocessor.

- Unused slave output pin must be NC (No Connection).

- 3. PAR/SPI connected HIGH to indicate parallel operation.

- Pin numbers for BGA package.

Figure 9. R/W Dual Display with Parallel Microcontroller Main Display and Sub-Display

## **Application Diagrams** (Continued)

#### Notes

- Dual display R/W Intel® interface.

- Unused slave output pin must be NC (No Connection).

- 3. GPIO signal used to select READ or WRITE functionality. Connected to CKSEL and R/W.

- 4. Displays selected via the chip selects.

- Pin numbers for BGA package.

Figure 10. Dual R/W x86-Style Microcontroller Display Interface

## **Additional Application Information**

**Flex Cabling:** The serial I/O information is transmitted at a high serial rate. Care must be taken implementing this serial I/O flex cable. The following best practices should be used when developing the flex cabling or Flex PCB.

Keep all four differential Serial Wires the same length.

Do not allow noisy signals over or near differential serial wires.

Example: No CMOS traces over differential serial wires.

Use only one ground plane or wire over the differential serial wires. Do not run ground over top and bottom

Design goal of 100-ohms differential characteristic impedance.

Do not place test points on differential serial wires.

Use differential serial wires a minimum of 2cm away from the antenna.

Visit Fairchild's website at <a href="http://www.fairchildsemi.com/products/interface/userdes.html">http://www.fairchildsemi.com/products/interface/userdes.html</a>, contact your sales rep, or contact Fairchild directly at <a href="mailto:interface@fairchildsemi.com">interface@fairchildsemi.com</a> for applications notes or flex guidelines.

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Pa                           | Min.                             | Max. | Unit                  |    |

|------------------|------------------------------|----------------------------------|------|-----------------------|----|

| $V_{DD}$         | Supply Voltage               | -0.5                             | +3.6 | V                     |    |

|                  | All Input/Output Voltage     |                                  | -0.5 | V <sub>DDP</sub> +0.5 | V  |

| T <sub>STG</sub> | Storage Temperature Range    | -65                              | +150 | °C                    |    |

| T <sub>J</sub>   | Maximum Junction Temperatu   |                                  | +150 | °C                    |    |

| TL               | Lead Temperature (Soldering, |                                  | +260 | °C                    |    |

|                  | IEC 61000 Board Level        |                                  |      | 15                    | kV |

| ESD              | Human Body Model,            | All Pins                         |      | 7.5                   | kV |

|                  | JESD22-A114                  | Serial I/0, /RES, PAR/SPI to GND |      | 14.0                  | ٨V |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol                   | Parameter             | Min. | Max.               | Unit |

|--------------------------|-----------------------|------|--------------------|------|

| $V_{DDA}, V_{DDS}^{(3)}$ | Supply Voltage        | 2.5  | 3.0                | V    |

| $V_{DDP}$                | Supply Voltage        | 1.6  | $V_{\text{DDA/S}}$ | V    |

| T <sub>A</sub>           | Operating Temperature | -30  | +85                | °C   |

#### Note

3.  $V_{DDA}$  and  $V_{DDS}$  supplies must be hardwired together to the same power supply.  $V_{DDP}$  must be less than or equal to  $V_{DDA}/V_{DDS}$ .

# **Electrical Specifications**

Values valid for over supply voltage and operating temperature ranges unless otherwise specified.

| Symbol                          | Parameter                             | Test Conditions                                                                                                          |                              | Min.                   | Тур. | Max.                   | Unit |

|---------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|------|------------------------|------|

| DC Paral                        | lel I/O and Serial Characteri         | stics                                                                                                                    |                              |                        |      |                        |      |

| $V_{IH}$                        | Input High Voltage                    |                                                                                                                          |                              | $0.7 \times V_{DDP}$   |      | $V_{DDP}$              | V    |

| $V_{IL}$                        | Input Low Voltage                     |                                                                                                                          |                              | GND                    |      | $0.3 \times V_{DDP}$   | V    |

| $V_{OH}$                        | SLEW=0 I <sub>OH</sub> =-250µA        |                                                                                                                          | A                            | 0.8 x V <sub>DDP</sub> |      |                        | V    |

|                                 | Output High Voltage                   | SLEW=1 I <sub>OH</sub> =-1mA                                                                                             | SLEW=1 I <sub>OH</sub> =-1mA |                        |      |                        | V    |

| V <sub>OL</sub>                 | Output Low Voltage                    | SLEW=0 I <sub>OL</sub> =250µA<br>SLEW=1 I <sub>OL</sub> =1mA                                                             |                              |                        |      | 0.2 x V <sub>DDP</sub> | V    |

|                                 | Output Low Voltage                    |                                                                                                                          |                              |                        |      |                        |      |

| I <sub>IN</sub>                 | Input Current                         |                                                                                                                          |                              | -5                     |      | 5                      | μA   |

| $V_{\text{GO}}$                 | Serial Input Voltage Ground<br>Offset | Slave Relative to Master                                                                                                 |                              |                        | 0    |                        | ٧    |

| Z                               | Serial Transmission Line Imp          | pedance                                                                                                                  |                              | 70                     | 100  | 120                    | Ω    |

| Power Cl                        | naracteristics                        |                                                                                                                          |                              |                        |      |                        | ,    |

| - 4                             |                                       | V <sub>DDA/S</sub> =2.75V,                                                                                               | 5.44MHz                      |                        | 4    |                        |      |

| I <sub>DYN_SER</sub>            | Dynamic Current of Master<br>Device   | M/S=1, V <sub>DDP</sub> =1.8V,                                                                                           | 12.00MHz                     |                        | 7    |                        | mA   |

| 5111_0E.1                       |                                       | /STBY=1, /RES=1                                                                                                          | 15.00MHz                     |                        | 8    |                        |      |

|                                 | Dynamic Current of Slave<br>Device    | V <sub>DDA/S</sub> =2.75V                                                                                                | 5.44MHz                      |                        | 5    |                        |      |

| I <sub>DYN DES</sub>            |                                       | M/S=0 V <sub>DDP</sub> =1.8V,<br>/STBY=1, /RES=1,<br>C <sub>L</sub> =0pF                                                 | 12.00MHz                     |                        | 8    | _                      | mA   |

| -B111_B20                       |                                       |                                                                                                                          | 15.00MHz                     |                        | 10   |                        |      |

| I <sub>BRST_M</sub>             | Burst Standby Current of Master       | V <sub>DDA/S</sub> =2.75V, V <sub>DDP</sub> =1.8V, M/S=1,<br>/STBY=1, /RST=1, No STROBE<br>Signal, C <sub>L</sub> =0pF   |                              |                        | 1.3  |                        | mA   |

| I <sub>BRST_S</sub>             | Burst Standby Current of Slave        | V <sub>DDA/S</sub> =2.75V, V <sub>DDP</sub> =1.8V, M/S=0,<br>/STBY=1, /RST=1, No STROBE<br>Signal, C <sub>L</sub> =0pF   |                              |                        | 1.8  |                        | mA   |

| I <sub>STBY</sub>               | Standby Current                       | Serializer or Deserializer V <sub>DDS/A</sub> =V <sub>DDP</sub> =3.0V, /STBY=0, /RST=1                                   |                              |                        |      | 10                     | μA   |

| I <sub>RES</sub>                | Reset Current                         | Serializer or Deserializer V <sub>DDS/A</sub> =V <sub>DDP</sub> =3.0V, /RST=0                                            |                              |                        |      | 10                     | μA   |

| AC Opera                        | ating Characteristics                 |                                                                                                                          |                              |                        |      | /-                     |      |

| f <sub>WSTRB0</sub>             | Write Strobe Frequency                | CKSEL=0 STRB0                                                                                                            |                              | 0                      |      | 8                      | MHz  |

| f <sub>WSTRB1</sub>             | Write Strobe Frequency                | CKSEL=1 STRB1                                                                                                            |                              | 0                      |      | 15                     | MHz  |

| f <sub>RSTRB</sub>              | Read Strobe Frequency                 |                                                                                                                          |                              | 0                      |      | 2                      | MHz  |

| t <sub>R</sub> , t <sub>F</sub> | Input Edge Rates <sup>(5)</sup>       |                                                                                                                          |                              |                        |      | 40                     | ns   |

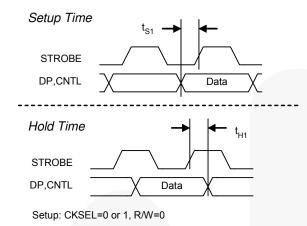

| t <sub>S1</sub>                 | Write Mode Setup Time                 | DP before STRBn ↑, Figure 11                                                                                             |                              | 5                      |      |                        | ns   |

| t <sub>H1</sub>                 | Write Mode Hold Time                  | DP after STRBn ↑, Figure 11                                                                                              |                              | 15                     |      |                        | ns   |

| t <sub>S2</sub>                 | READ Mode Setup Time                  | R/W, CNTL before STRBn ↓ Figure 12                                                                                       |                              | 0                      |      |                        | ns   |

| t <sub>H2</sub>                 | READ Mode Hold Time                   | R/W, CNTL after STRBn ↓<br>Figure 12                                                                                     |                              | 16                     |      |                        | ns   |

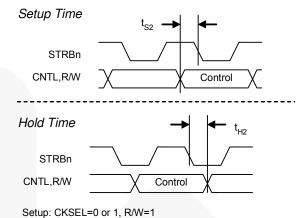

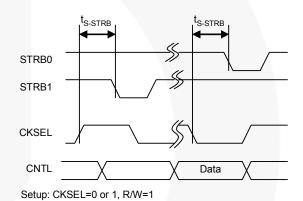

| t <sub>S-STRB</sub>             | CKSEL to STRBn Setup<br>Time          | CKSEL before active edge<br>STRBn <sup>(4)</sup> , CKSEL before SPI /CS,<br>SPI /CS before CKSEL<br>Figure 13, Figure 14 |                              | 50                     |      |                        | ns   |

| Symbol                 | Parameter                                      | Test Conditions                                                                   | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| AC Dese                | rializer Specifications                        | ,                                                                                 |      |      |      |      |

|                        | Output Edge Rates of                           | SLEW=0, CL=5pF 20% to 80% <sup>(5)</sup>                                          | 8    |      | 17   |      |

| $t_{R0}, t_{F0}$       | WCLK0,WCLK1                                    | SLEW=1, C <sub>L</sub> =5pF 20% to 80% <sup>(5)</sup>                             |      |      | 10   | ns   |

| $t_{R1}, t_{F1}$       | Output Edge Rates of R/W, DP[17:0] CNTL[5:0]   | SLEW=0, C <sub>L</sub> =5pF 20% to 80% <sup>(5)</sup>                             | 8    |      | 22   | no   |

|                        |                                                | SLEW=1, C <sub>L</sub> =5pF 20% to 80% <sup>(5)</sup>                             |      |      | 17   | ns   |

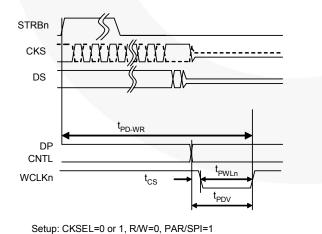

| t <sub>CS</sub>        | CNTL[5:0],R/W to Falling<br>Edge of WCLKn      | M/S=0 <sup>(5)</sup> , C <sub>L</sub> =5pF 50% to 50% <sup>(5)</sup><br>Figure 15 | 0    | 4    |      | ns   |

| $t_{\text{PDV-WR0}}$   | DP, CNTL to WCLK0 ↑                            | PAR/SPI=1 <sup>(5)</sup> , Figure 15                                              | 50   | 60   |      | ns   |

| t <sub>PDV-WR1</sub>   | DP, CNTL to WCLK1 ↑                            | PAR/SPI=1 <sup>(5)</sup> , Figure 15                                              | 18   | 24   |      | ns   |

| t <sub>PDV-RD</sub>    | CNTL to WCLKn ↑                                | PAR/SPI=1 <sup>(5)</sup> , Figure 17                                              | 200  | 224  |      | ns   |

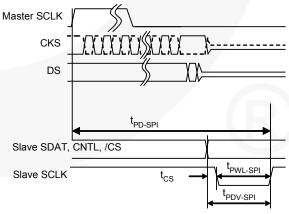

| t <sub>PDV-SPI</sub>   | Data, CNTL to SCLK ↑                           | PAR/SPI=0 <sup>(5)</sup> , Figure 16                                              | 40   | 60   |      | ns   |

| t <sub>PWL-WR0</sub>   | WCLK0 Pulse Width Low;<br>Write Mode           | M/S=0, R/W=0, PAR/SPI=1 <sup>(5,7)</sup><br>Figure 15                             | 50   | 56   |      | ns   |

| t <sub>PWL-WR1</sub>   | WCLK1 Pulse Width Low;<br>Write Mode           | M/S=0, R/W=0, PAR/SPI=1 <sup>(5,7)</sup><br>Figure 15                             | 18   | 20   |      | ns   |

| t <sub>PWL-RD</sub>    | Pulse Width Low of WCLK;<br>Read Mode          | M/S=0, R/W=1, PAR/SPI=1 <sup>(5,7)</sup><br>Figure 17                             | 200  | 220  |      | ns   |

| t <sub>PWL-SPI</sub>   | Pulse Width Low of WCLK;<br>SPI Mode           | M/S=0, R/W=0, PAR/SPI=0 <sup>(5,7)</sup><br>Figure 16                             | 40   | 56   |      | ns   |

| AC Data                | Latencies                                      |                                                                                   |      |      |      |      |

| t <sub>PD-WR0</sub>    | Write Latency                                  | WRITE Mode, CKSEL=0 <sup>(8,9,10)</sup><br>Figure 15                              |      | 147  |      | ns   |

| t <sub>PD-WR1</sub>    | Write Latency                                  | WRITE Mode, CKSEL=1 <sup>(8,9,10)</sup><br>Figure 15                              |      | 111  |      | ns   |

| t <sub>PD-RD</sub>     | Total Read Latency                             | READ Mode <sup>(8,10,11)</sup><br>Figure 17                                       |      | 340  | 480  | ns   |

| t <sub>PD-RDC</sub>    | Read Control Latency                           | READ Mode <sup>(8,10,12)</sup><br>Figure 17                                       |      | 276  |      | ns   |

| t <sub>PD-RDD</sub>    | Read Data Latency                              | READ Mode <sup>(8,10,13)</sup><br>Figure 17                                       |      | 84   |      | ns   |

| t <sub>PD-SPI</sub>    | SPI Write Latency                              | SPI-WRITE Mode <sup>(8,10,14)</sup><br>Figure 16                                  |      | 115  | 4    | ns   |

| AC Oscil               | ator Specifications                            |                                                                                   |      |      |      |      |

| f <sub>OSC</sub>       | Serial Operating Frequency                     |                                                                                   | 240  | 275  | 310  | MHz  |

| t <sub>OSC-STBY</sub>  | Oscillator Stabilization Time<br>After Standby | V <sub>DDA</sub> =V <sub>DDS</sub> =2.75V<br>/RES=1, /STBY ↑ Transition           |      | 15   | 30   | μs   |

| tosc-res               | Oscillator Stabilization Time<br>After Reset   | V <sub>DDA</sub> =V <sub>DDS</sub> =2.75V<br>/STBY=1, /RES ↑ Transition           |      | 30   | 50   | μs   |

| AC Reset               | and Standby Timing                             |                                                                                   |      |      |      |      |

| t <sub>VDD-OFF</sub>   | Power Down Relative to /RES <sup>(15)</sup>    | Figure 19                                                                         | 20   |      |      | μs   |

| t <sub>STRB-RES</sub>  | /RES after last STRBn ↑                        | M/S=1, /STBY=1, R/W=0 <sup>(16)</sup><br>Figure 19                                | 0    |      |      | ns   |

| t <sub>STRB-STBY</sub> | Standby time after last strobe                 | M/S=1, /STBY=1 <sup>(17)</sup><br>Figure 19                                       | 200  |      |      | ns   |

| t <sub>RES-OFF</sub>   | Master/Slave Reset Disable Time                | M/S=1 /STBY=1, /RES=↓<br>Figure 19                                                |      | 15   | 20   | μs   |

| Symbol                | Parameter Test Conditions                                                              |                                            | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|------|

| t <sub>VDD-SKEW</sub> | Allowed Skew between V <sub>DDP</sub> and V <sub>DDA/S</sub> <sup>(18)</sup> Figure 18 |                                            | -80  |      | +∞   | ms   |

| t <sub>VDD-RES</sub>  | Minimum Reset Low Time<br>After V <sub>DD</sub> Stable                                 | M/S=0, /RES= <sup>↑(19)</sup><br>Figure 18 | 20   |      |      | μs   |

| t <sub>RES-STBY</sub> | /STBY Wait Time After<br>/RES ↑                                                        | M/S=1 /RES=1, /STBY=↑<br>Figure 18         | 20   |      |      | μs   |

| t <sub>DVALID</sub>   | /STBY to Active Edge of Strobe                                                         | M/S=0 /RES=1 <sup>(20)</sup><br>Figure 18  | 30   |      |      | μs   |

#### Notes:

- 4. Active edge of strobe is the rising edge for a write transaction and the falling edge for a read transaction.

- Characterized, but not production tested.

- 6. Indirectly tested through serial clock frequency and serial data bit tests.

- Pulse width low WCLKn measurements are measured at 30% of V<sub>DDP</sub>. Measurements apply when SLEW=0 or SLEW=1.

- Minimum times occur with maximum oscillator frequency. Maximum times occur with minimum oscillator frequency.

- 9. Write latency is the sum of the delay through the master serializer and slave deserializer, plus the flight time across the flex cable and I/O propagation delays.

- 10. Assumes propagation delay across the flex cable and through the I/Os of 20ns.

- 11. Total read latency tpd-RD is the sum of the Read-Control Phase latency (tpd-RDC) and the Read-Data Phase latency (tpd-RDD). tpd-RD=tpd-RDC+ tpd-RDD.

- 12. Read-Control latency is the sum of the delay through the master serializer and slave deserializer, plus flex cable flight times and I/O propagation delays.

- 13. Read Data latency is the sum of the delay through the slave serializer and master deserializer, plus flex cable flight times and I/O propagation delays.

- 14. SPI-Write latency is the sum of the delay through the master serializer and slave deserializer, plus the flight time across the flex cable and I/O propagation delays.

- 15. Timing allows the device to completely reset prior to powering down.

- 16. Internal reset filter allows assertion prior to completion of read or write date transfer.

- 17. Timing ensures that last write transaction is complete prior to going into standby.

- 18. V<sub>DDA/S</sub> must power up together. V<sub>DDP</sub> may power-up relative to V<sub>DDA/S</sub> in any order without static power being consumed. Guaranteed by characterization.

- 19. /RES signal should be held low for minimum time specified after supplies go HIGH. It is recommended that /RES be held low during the power supply ramp.

- 20. STRBn must be held off until internal oscillator has stabilized.

## **Typical Performance Characteristics**

Figure 11. Master Write Setup and Hold Time

50tap: 51t5=2 5 5t 1,1111 1

Figure 12.

Setup: CKSEL=0 or 1, R/W=0

Figure 13. CKSEL Write Setup Time

**Master Read Setup and Hold Time**

Figure 14. CKSEL Read Setup Time

Figure 15. Slave Write Mode Timing

Setup: CKSEL=0, R/W=0, PAR/SPI=0, /CS=0

Figure 16. Slave SPI Mode Timing

## **Typical Performance Characteristics** (Continued)

Figure 17. Slave Read Mode Timing

Figure 18. Power-Up Timing

Figure 19. Power-Down Timing

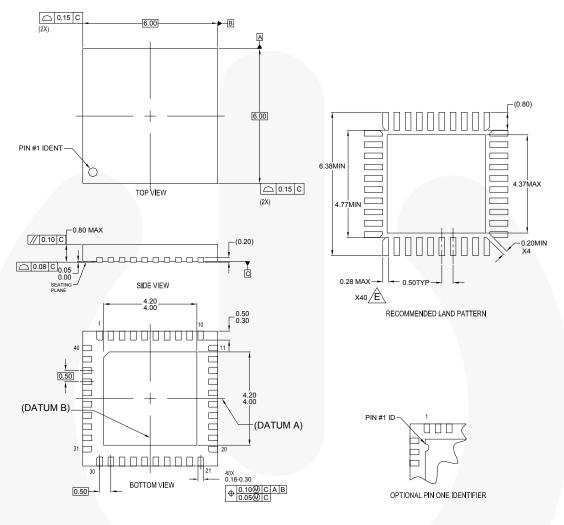

## **Physical Dimensions**

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-220, VARIATION WJJD-2 WITH EXCEPTION THAT THIS IS A SAWN VERSION..

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- D. LAND PATTERN PER IPC SM-782.

- E. WIDTH REDUCED TO AVOID SOLDER BRIDGING.

- F. DIMENSIONS ARE NOT INCLUSIVE OF BURRS, MOLD FLASH, OR TIE BAR PROTRUSIONS.

- G. DRAWING FILENAME: MKT-MLP40Arev3.

## Figure 20. 40-Lead, Molded Leadless Package (MLP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

## Physical Dimensions (Continued) △ 0.10 C 3.50 2X (0.35)(0.5) -△ 0.10 C (0.6)2.5 (0.75)**TERMINAL** $\bigcirc$ A1 CORNER 00000INDEX AREA 000004.50 3.0 0.5 00000 0.5 Ø0.3±0.05 X42 **BOTTOM VIEW** TOP VIEW ⊕ Ø0.15∰ C A B ⊕ Ø0.05∰ C 0.89±0.082 ST (QA CONTROL VALUE) 0.45±0.05 ST 1.00 MAX 0.21±0.04 (ST) // 0.10 C △ 0.08 C (ST) 0.23±0.05 SEATING PLANE 0 NOTES: $\circ$ 0 0 0 A. CONFORMS TO JEDEC REGISTRATION MO-195, 0 0 0 0 B. DIMENSIONS ARE IN MILLIMETERS. LAND PATTERN C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994 RECOMMENDATION D. STATISTICAL TOLERANCING FOR REFERENCE REFER TO MAX DIMENSION FOR QA INSPECTION

Figure 21. 42-Ball, Ball Grid Array (BGA) Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

E. LAND PATTERN RECOMENDATION PER IPC-7351 TABLE14-15

LAND PATTERN NAME PER TABLE 3-15: BGA50P+6X7-42

BGA42ArevB

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ Auto-SPM™ Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT" CTL™

Current Transfer Logic™ DEUXPEED<sup>®</sup> Dual Cool™ EcoSPARK® EfficientMax™ EZSWITCH\*\*\*

Fairchild® Fairchild Semiconductor® FACT Quiet Series™

FACT<sup>®</sup> FAST<sup>®</sup> FastvCore™ FETBench™ FlashVVriter®\* FPS™ F-PFS™ FRFET®

Global Power Resource sM Green FPS™ Green FPS™ e-Series™

Gmax™ **GTOTM** IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™ MicroFET\*\*

MicroPak™ MicroPak2™ MillerDrive™ MotionMax™ Motion-SPM™ OptoHiT™ OPTOLOGIC® OPTOPLANAR® PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™ OFFT

QSTM Quiet Series™ RapidConfigure™ OTM

Saving our world, 1mW/W/kW at a time™ SignalWise™

SmartMax™ SMART START™ SPM® STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT\*-8 SupreMOS™ SyncFET™ Sync-Lock™

SYSTEM ® The Power Franchise® wer TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>e</sup> TINY OPTO\*\* TinyPower™ TinyPVM™ TinyWire™ TriFault Detect™ TRUECURRENT\*\*\* μSerDes™

UHC<sup>6</sup> Ultra FRFET™ UniFET™ **VCXTM** VisualMax\*\*

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HERBIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THERBIN, WHICH COVERS THESE PRODUCTS

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms                                                                                                                                                      |                       |                                                                                                                                                                                                     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Datasheet Identification                                                                                                                                                 | Product Status        | Definition                                                                                                                                                                                          |  |  |

| Advance Information                                                                                                                                                      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary                                                                                                                                                              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed Full Production Datasheet contains final specifications. Fairchild Semiconductor reserves the at any time without notice to improve the design. |                       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                                                                                                                                                                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 146

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hol

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative