# TCM3105DWL, TCM3105JE, TCM3105JL, TCM3105NE, TCM3105NL

### FSK Modem

The TCM3105 is a single-chip asynchronous frequency-shift-keying (FSK) voice-band modem that uses silicon-gate CMOS technology to implement a switched-capacitor architecture. It is pin selectable (TXR1, TXR2, and TRS) for a wide range of transmit/receive baud rates and is compatible with the applicable BELL 202 or CCITT V23 standards. Operation is fully reversible, thereby allowing both forward and backward channels to be used simultaneously.

The transmitter is a programmable frequency synthesizer that provides two output frequencies (on TXA), representing the marks and spaces of the digital signal present on TXD.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

SCTS019C - NOVEMBER 1985 - REVISED MAY 1994

- Single-Chip Frequency-Shift-Keying (FSK) Modem

- Meet Both Bell 202 and CCITT V23 Specifications

- Transmit Modulation at 75, 150, 600, and 1200 Baud

- Receive Demodulation at 5, 75, 150, 600, and 1200 Baud

- Half-Duplex Operation Up to 1200 Baud Transmit and Receive

- Full-Duplex Operation Up to 1200 Baud Transmit and 150 Baud Receive

- On-Chip Group Equalization and Transmit/Receive Filtering

- Carrier-Detect-Level Adjustment and Carrier-Fail Output

- Single 5-V Power Supply

- Low Power Consumption

- Reliable CMOS Silicon-Gate Technology

### description

The TCM3105 is a single-chip asynchronous frequency-shift-keying (FSK) voice-band modem that uses silicon-gate CMOS technology to implement a switched-capacitor architecture. It is pin selectable (TXR1, TXR2, and TRS) for a wide range of transmit/receive baud rates and is compatible with the applicable BELL 202 or CCITT V23 standards. Operation is fully reversible, thereby allowing both forward and backward channels to be used simultaneously.

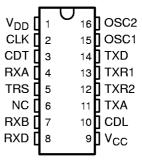

### J OR N PACKAGE (TOP VIEW)

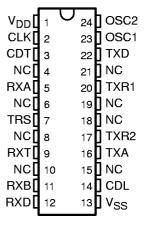

# DW PACKAGE (TOP VIEW)

NC - No internal connection

D package are available taped and reeled. Add the R suffix to device type (e.g., YCM3105DWLR).

The transmitter is a programmable frequency synthesizer that provides two output frequencies (on TXA), representing the marks and spaces of the digital signal present on TXD.

The receive section is responsible for the demodulation of the analog signal appearing at the RXA input and is based on the principle of frequency-to-voltage conversion. This section contains a group delay equalizer (to correct phase distortion), automatic gain control, carrier-detect-level adjustment, and bias-distortion adjustment, thereby optimizing performance and giving the lowest possible bit error rate.

Carrier-detect information is given to the system by means of the carrier-detect circuits, which set a flag on the CDT output if the level of received in-band energy falls below a value set on the CDL input for a specified minimum duration.

The TCM3105JE and TCM3105NE are characterized for operation from -40°C to 85°C. The TCM3105DWL, TCM3105JL, and TCM3105NL are characterized for operation from 0°C to 70°C.

Caution. These devices have limited built-in protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# TCM3105DWL, TCM3105JE, TCM3105JL TCM3105NE, TCM3105NL FSK MODEM SCTS019C - NOVEMBER 1985 - REVISED MAY 1994

### **Terminal Functions**

| TERMINAL        |                                |           |                                                                                                                                                                                                                                                  |  |  |  |  |  |

|-----------------|--------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME            | NO.                            |           | DESCRIPTION                                                                                                                                                                                                                                      |  |  |  |  |  |

| NAME            | DW                             | J OR N    |                                                                                                                                                                                                                                                  |  |  |  |  |  |

| CDL             | 14                             | 10        | Carrier-detect-level adjust for external adjustment of carrier-detect threshold                                                                                                                                                                  |  |  |  |  |  |

| CDT             | 3                              | 3         | Carrier-detect output. A low-level output indicates carrier failure                                                                                                                                                                              |  |  |  |  |  |

| CLK             | 2                              | 2         | Output for a continuous clock signal at 16 times the highest selected (transmit or receive) bit rate                                                                                                                                             |  |  |  |  |  |

| NC              | 4, 6, 8, 10,<br>15, 18, 19, 21 | 6         | No internal connection                                                                                                                                                                                                                           |  |  |  |  |  |

| OSC1,<br>OSC2   | 23,<br>24                      | 15,<br>16 | Oscillator connections. The crystal (typically 4.4336 MHz) is connected to OSC1 AND OSC2. If an external clock is used, OSC2 is left open and the clock is connected to OSC1.                                                                    |  |  |  |  |  |

| RXA             | 5                              | 4         | Receive analog input to which the received line signal must be ac coupled                                                                                                                                                                        |  |  |  |  |  |

| RXB             | 11                             | 7         | Receive bias adjust for external adjustment of the decision threshold of the comparator to minimize bias distortion                                                                                                                              |  |  |  |  |  |

| RXD             | 12                             | 8         | Receiver digital output for the demodulated received data in positive logic. The high logic level is a mark and the low logic level is a space.                                                                                                  |  |  |  |  |  |

| RXT             | 9                              | _         | Receive test access. Output of limiter is available on RXT. (DW only)                                                                                                                                                                            |  |  |  |  |  |

| TRS             | 7                              | 5         | Transmit/receive standard select input, which with TXR1 and TXR2, sets the standard bit rates and mark/space frequencies                                                                                                                         |  |  |  |  |  |

| TXA             | 16                             | 11        | Transmit analog output for the modulation signal, which must be ac coupled                                                                                                                                                                       |  |  |  |  |  |

| TXD             | 22                             | 14        | Transmit digital input for data to the transmitter in positive logic. The high logic level is a mark, and the low logic level is a space. The data can be accepted at any speed from zero to the selected speed and may be totally asynchronous. |  |  |  |  |  |

| TXR1            | 20                             | 13        | Bit-rate select 1 input which along with TXR2 and TRS, sets the bit rates and mark/space frequencies                                                                                                                                             |  |  |  |  |  |

| TXR2            | 17                             | 12        | Bit rate select 2 input, which along with TXR1 and TRS, sets the bit rates and mark/space frequencies                                                                                                                                            |  |  |  |  |  |

| $V_{DD}$        | 1                              | 1         | Positive supply voltage                                                                                                                                                                                                                          |  |  |  |  |  |

| V <sub>SS</sub> | 13                             | 9         | Most negative supply voltage (normally ground); connected to substrate                                                                                                                                                                           |  |  |  |  |  |

### functional block diagram

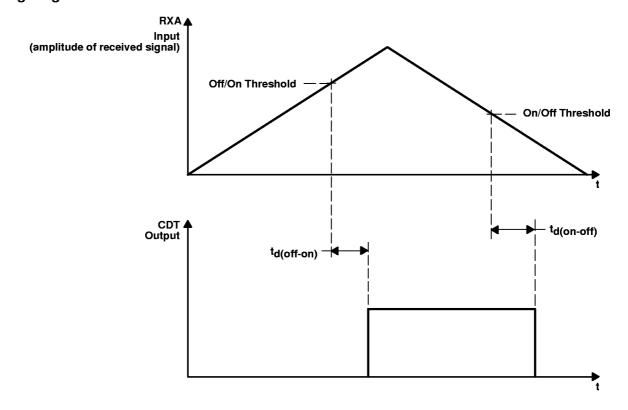

### timing diagram

### TCM3105DWL, TCM3105JE, TCM3105JL TCM3105NE, TCM3105NL FSK MODEM

SCTS019C - NOVEMBER 1985 - REVISED MAY 1994

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| oply voltage range, V <sub>DD</sub> (see Note 1)                         | 0.3 V to 10 V            |

|--------------------------------------------------------------------------|--------------------------|

| ut voltage range, V <sub>I</sub> (any input)                             | 0.3 V to V <sub>DD</sub> |

| erating free-air temperature range, TA: TCM3105DWL, TCM3105JL,TCM31      | 105NL −10°C to 70°C      |

| TCM3105JE, TCM3105NE                                                     | 55°C to 85°C             |

| rage temperature range:                                                  | 55°C to 150°C            |

| nd temperature 1,6 mm (1/16 inch) from case for 10 seconds: DW or N pack | kage 260°C               |

| nd temperature 1.6 mm (1/16 inch) from case for 10 seconds: J package    | 300°C                    |

NOTE 1: Voltage values are with respect to VSS.

### recommended operating conditions

|                                               |        | TCM3105JE<br>TCM3105NE |          |        | TCM3105DWL<br>TCM3105JL<br>TCM3105NL |          |     |

|-----------------------------------------------|--------|------------------------|----------|--------|--------------------------------------|----------|-----|

|                                               | MIN    | NOM                    | MAX      | MIN    | NOM                                  | MAX      |     |

| Supply voltage, V <sub>DD</sub>               | 4      | 5                      | 5.5      | 4      | 5                                    | 5.5      | ٧   |

| High-level input voltage, V <sub>IH</sub>     | 2      |                        | $V_{DD}$ | 2      |                                      | $V_{DD}$ | ٧   |

| Low-level input voltage, V <sub>IL</sub>      | 0      |                        | 0.8      | 0      |                                      | 0.8      | ٧   |

| Analog input level, peak to peak (ac coupled) |        | 0.3                    | 0.78     |        | 0.3                                  | 0.78     | V   |

| Clock frequency, f <sub>clock</sub>           | 4.4334 | 4.4336                 | 4.4338   | 4.4334 | 4.4336                               | 4.4338   | MHz |

| Analog load impedance at TXA                  | 50     |                        |          | 50     |                                      |          | kΩ  |

| Operating free-air temperature range, TA      | -40    |                        | 85       | 0      |                                      | 70       | °C  |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|     | PARAMETER                                    | TEST CONDITIONS         |                                       | TCM3105JE<br>TCM3105NE            |                 |                    | TCM3105DWL<br>TCM3105JL<br>TCM3105NL |                 |                    | UNIT     |     |

|-----|----------------------------------------------|-------------------------|---------------------------------------|-----------------------------------|-----------------|--------------------|--------------------------------------|-----------------|--------------------|----------|-----|

|     |                                              |                         |                                       |                                   | MIN             | TYP                | MAX                                  | MIN             | TYP                | MAX      |     |

| VOH | High-level output<br>voltage                 | RXD, CDT,<br>CLK        | I <sub>OH</sub> = -100 μ              | A                                 | 2.4             |                    | $V_{DD}$                             | 2.4             |                    | $V_{DD}$ | ٧   |

| VOL | Low-level output voltage                     | RXD, CDT,<br>CLK        | I <sub>OL</sub> = 1.6 mA              |                                   | V <sub>SS</sub> |                    | 0.4                                  | V <sub>SS</sub> |                    | 0.4      | ٧   |

|     |                                              |                         | V <sub>DD</sub> = 4 V                 |                                   |                 | 1.55               |                                      |                 | 1.55               |          |     |

|     | Analog output voltage<br>level, peak to peak | TXA                     | V <sub>DD</sub> = 5 V                 | $R_L = 50 kΩ$ ,<br>$R_L = 100 pF$ | 1.4             | 1.9                | 2.3                                  | 1.4             | 1.9                | 2.3      | V   |

|     | ievei, peak to peak                          |                         | $V_{DD} = 5.5 V$                      |                                   |                 | 2.1                |                                      |                 | 2.1                |          |     |

|     | Adjust voltage                               | RXB                     | V== 5.V                               |                                   | 2.3             | 2.7                | 3.1                                  | 2.3             | 2.7                | 3.1      | V   |

|     | Adjust voltage                               | CDL                     | V <sub>DD</sub> = 5 V                 |                                   | 2.8             | 3.3                | 3.9                                  | 2.8             | 3.3                | 3.9      | V   |

|     | Analog output dc offset                      | TXA                     |                                       |                                   |                 | V <sub>DD</sub> /2 |                                      |                 | V <sub>DD</sub> /2 |          | ٧   |

|     | Digital input current                        | TXD, TRS,<br>TRX1, TRX2 | V <sub>I</sub> = 0 to V <sub>DD</sub> |                                   |                 |                    | ±1                                   |                 |                    | ±1       | μА  |

|     | Analog input current                         | RXA                     |                                       |                                   |                 |                    | ±15                                  |                 |                    | ±15      | μА  |

|     | Bias input current                           | RXB, CDL                | V <sub>I</sub> = 3 V                  |                                   |                 |                    | ±150                                 |                 |                    | ±150     | μА  |

|     |                                              |                         | V <sub>DD</sub> = 4 V                 |                                   |                 | 3                  | 6                                    |                 | 3                  | 5        |     |

| IDD | Supply current                               | urrent                  |                                       |                                   |                 | 5                  | 10                                   |                 | 5                  | 8        | mA  |

|     |                                              |                         | V <sub>DD</sub> = 5.5 V               |                                   |                 | 8                  | 16                                   |                 | 8                  | 12       |     |

| Ci  | Input capacitance, all inpu                  | uts                     | f = 1 MHz                             |                                   |                 | 10                 |                                      |                 | 10                 |          | pF  |

| Со  | Output capacitance, all in                   | f = 1 MHz               |                                       |                                   | 10              |                    |                                      | 10              |                    | pF       |     |

|     | Phase jitter                                 |                         |                                       |                                   |                 |                    | 200                                  |                 |                    | 200      | μs  |

|     | Bias distortion‡                             |                         |                                       |                                   |                 | ±15%               |                                      |                 | ±15%               |          |     |

|     | Carrier-detect threshold,                    |                         |                                       | -45.5                             |                 | -43                | -45.5                                |                 | -43                | dBm      |     |

|     | Carrier-detect threshold,                    |                         |                                       | -48                               |                 | -45.5              | -48                                  |                 | -45.5              | dBm      |     |

|     | Carrier-detect hysteresis                    |                         |                                       |                                   | 2.5             | 2.8                |                                      | 2.5             | 2.8                |          | dBm |

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                  | TEST CONDITIONS                 | TCM3105JE<br>TCM3105NE |     |     | TCM3105DWL<br>TCM3105JL<br>TCM3105NL |     |     | UNIT |

|------------------------|------------------------------------------------------------|---------------------------------|------------------------|-----|-----|--------------------------------------|-----|-----|------|

|                        |                                                            |                                 | MIN                    | TYP | MAX | MIN                                  | TYP | MAX |      |

| <sup>t</sup> d(off-on) | Carrier detect off to an delay time                        | RX = 600 or 1200 b/s            | 12                     |     | 25  | 12                                   |     | 25  | ms   |

|                        | Carrier-detect off-to-on delay time                        | RX = 5, 75, or 150 b/s          | 48                     |     | 80  | 48                                   |     | 80  |      |

| <sup>†</sup> d(on-off) | 0 : 1 : 1 : 1 : 1 : 1                                      | RX = 600 or 1200 b/s            | 12                     |     | 20  | 12                                   |     | 20  |      |

|                        | Carrier-detect on-to-off delay time                        | RX = 5, 75, or 150 b/s          | 48                     |     | 75  | 48                                   |     | 75  | ms   |

|                        | Transmit frequency deviation from assignment (see Table 1) | f <sub>clock</sub> = 4.4336 MHz |                        | ±1  |     |                                      | ±1  |     | Hz   |

$<sup>\</sup>uparrow$  All typical are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>‡</sup> Bias distortion is the departure from a 50% duty cycle when a series of alternating mark and space tones is received.

$<sup>\</sup>$  This is the threshold with the CDL input properly adjusted.

SCTS019C - NOVEMBER 1985 - REVISED MAY 1994

### **PRINCIPLES OF OPERATION**

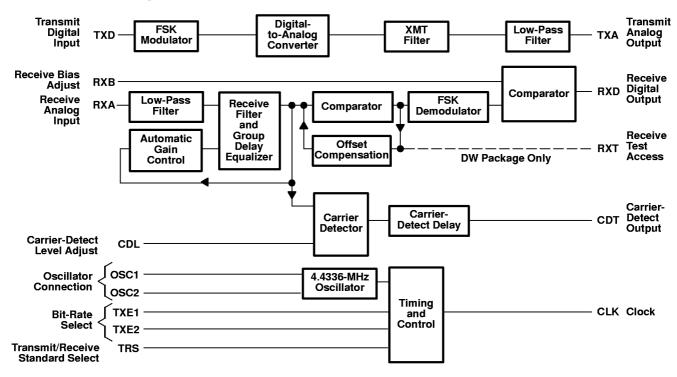

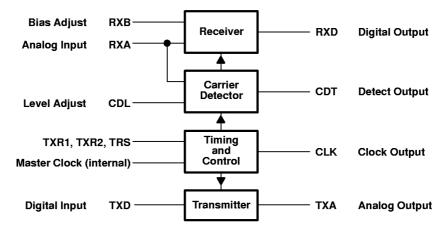

The TCM3105 FSK modem is made up of four functional circuits. The circuits are the transmitter, the receiver, a carrier detector, and control and timing (see Figure 1).

Figure 1. TCM3105 System Partitioning

### transmitter

The transmitter comprises a phase-coherent FSK modulator, a transmit filter, and a transmit amplifier. The modulator is a programmable frequency synthesizer that drives the output frequencies by variable division of the oscillator frequency (4.4336 MHz). The division ratio is set by the states of the transmit/receive standard input (TRS), the bit-rate select inputs (TXR1 and TXR2), and the digital data input (TXD).

A switched-capacitor low-pass filter limits the harmonics and noise outside the transmit band, and the characteristics of this filter are set by the frequency-select inputs as previously described. The harmonics introduced by the transmit filter clock are removed by a continuous low-pass filter.

The transmitter output level varies with power supply voltage and so must be compensated in the 2-wire to 4-wire converter to give a constant output level to the line.

### receiver

A continuous low-pass antialiasing filter is followed by the receiver amplifier, which automatically controls the gain to give a constant output level from the receiver filter. The receiver filter limits the bandwidth of the signal presented to the demodulator reducing out-of-band interference and has very high rejection of the transmit channel frequencies. These are typically present at much higher levels than the received signal.

The group delay equalizer is a switched-capacitor network that compensates the delay introduced by the receiver filter and the network. The output from the equalizer is then limited to give an FSK modulated squarewave that is presented to the demodulator.

The demodulator is an edge-triggered multivibrator that triggers off positive- and negative-going edges. The output of the demodulator is a stream of constant-length pulses at a frequency that is double the frequency of the limited input signal. The dc component of this signal is proportional to the received frequency and is extracted by a switched-capacitor, low-pass, post-demodulator filter.

The variation of dc level with received frequency is presented to a comparator that slices at a level externally fixed by the RXB bias-adjustment pin. This voltage depends on received bit rate and internal offsets. The comparator output is then the received data at RXD.

### TCM3105DWL, TCM3105JE, TCM3105JL TCM3105NE, TCM3105NL FSK MODEM

SCTS019C - NOVEMBER 1985 - REVISED MAY 1994

### carrier detect

The carrier-detect circuits comprise an energy detector and digital delay. The energy detector compares the total signal level at the output of the receive filter to an externally set threshold level on the CDL input. The comparator has a 2.5-dB hysteresis and a delay to allow for momentary signal loss and to prevent oscillation. The output detector is available on CDT where a high level indicates that a carrier is present. The data output is clamped to a mark condition when the carrier-detect output switches off at the end of transmission.

### control and timing

An on-chip oscillator runs from an external 4.4336-MHz crystal connected between OSC1 and OSC2 or an external signal driving OSC1. A clock signal equal to 16 times the highest selected bit rate (transmit or receive) is available on the CLK output.

The single-supply rail means that all analog functions are referenced to an internally generated reference. All analog inputs and outputs must be ac coupled.

### transmit and receive modes

The various modes of operation of the TCM3105 are given in Table 1. The data convention is that a logic high is a mark and a logic low is a space.

# TCM3105DWL, TCM3105JE, TCM3105JL TCM3105NE, TCM3105NL FSK MODEM

SCTS019C - NOVEMBER 1985 - REVISED MAY 1994

**Table 1. Modes of Operation**

| STANDARD   | TRS        | TXR1     | TXR2     | TRANSMITTED<br>BAUD RATE | RECEIVED<br>BAUD RATE | TRANSMIT<br>FREQUENCY<br>ASSIGNMENTS<br>(Hz) | RECEIVE<br>FREQUENCY<br>ASSIGNMENTS<br>(Hz) | CLK<br>FREQUENCY<br>(kHz) |

|------------|------------|----------|----------|--------------------------|-----------------------|----------------------------------------------|---------------------------------------------|---------------------------|

|            | L          | L        | L        | 1200                     | 1200                  | M 1300<br>S 2100                             | M 1300<br>S 2100                            | 19.11                     |

|            | Н          | L        | L        | 1200                     | 75                    | M 1300<br>S 2100                             | M 390<br>S 450                              | 19.11                     |

|            | L          | L        | Н        | 600                      | 75                    | M 1300<br>S 1700                             | M 390<br>S 450                              | 9.56                      |

| CCITT V.23 | Н          | L        | Н        | 600                      | 600                   | M 1300<br>S 1700                             | M 1300<br>S 1700                            | 9.56                      |

|            | L          | Н        | L        | 75                       | 1200                  | M 390<br>S 450                               | M 1300<br>S 2100                            | 19.11                     |

|            | Н          | Н        | L        | 75                       | 600                   | M 390<br>S 450                               | M 1300<br>S 1700                            | 9.56                      |

|            | L          | Н        | Н        | 75                       | 75                    | M 390<br>S 450                               | M 390<br>S 450                              | 1.19                      |

|            | CLK        | L        | L        | 1200                     | 1200                  | M 1200<br>S 2200                             | M 1200<br>S 2200                            | 19.11                     |

|            | CLK/8      | L        | Н        | 1200                     | 150                   | M 1200<br>S 2200                             | M 387<br>S 487                              | 19.11                     |

|            | CLK/8      | L        | Н        | 1200                     | 5                     | M 1200<br>S 2200                             | M 387<br>S 0                                | 19.11                     |

| BELL 202   | CLK        | Н        | L        | 150                      | 1200                  | M 387<br>S 487                               | M 1200<br>S 2200                            | 19.11                     |

|            | CLK        | Н        | Н        | 150                      | 150                   | M 387<br>S 487                               | M 387<br>S 487                              | 2.39                      |

|            | CLK†<br>H† | н†<br>н† | L†<br>H† | 5                        | 1200                  | M 387<br>S 0                                 | M 1200<br>S 2200                            | 19.11                     |

|            | Н          | Н        | Н        | Transmit<br>Disabled     | 1200                  | Transmit<br>Disabled                         | M 1200<br>S 2200                            | 19.11                     |

H = high level, L = low level

<sup>†</sup> In these modes, the modulation is controlled by TRS and TXR2. TXD is tied high.

### **APPLICATION INFORMATION**

Pin numbers shown are for the J and N packages.

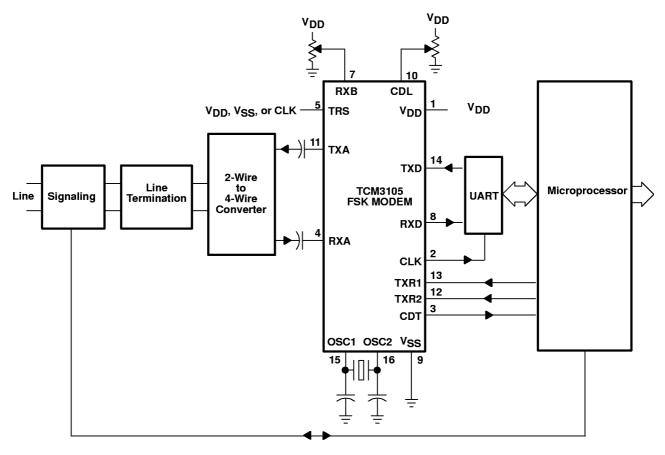

Figure 2. Typical System Configuration

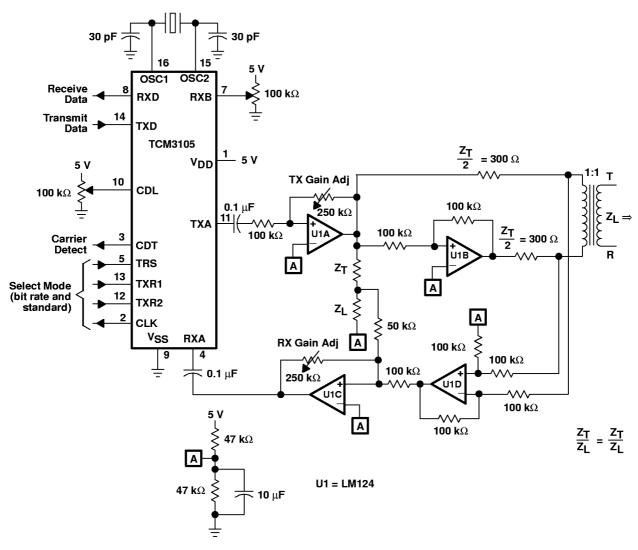

### **APPLICATION INFORMATION**

Pin numbers shown are for the J and N packages.

Figure 3. Telephone Line Interface Circuit

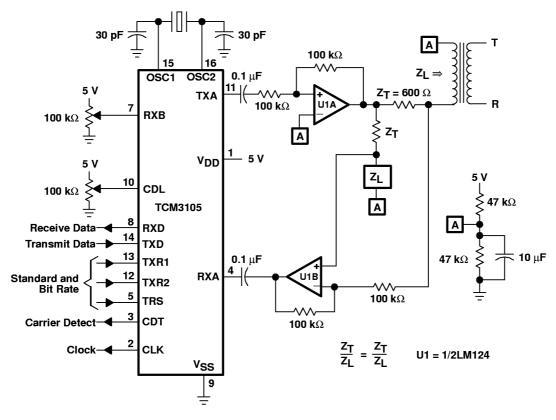

### **APPLICATION INFORMATION**

Figure 4. Simplified Telephone Line Interface Circuit