CMOS 128 Word (CDP68HC68R1) and 256 Word (CDP68HC68R2) by 8-Bit Static RAMs

January 1991

#

- Input Data and clock buffers Gated Off with Chip Enable

- Automatic Sequencing for Fast Multiple Byte Accesses

- Low Minimum Data Retention Voltage ......2V

- Wide Operating Temperature Range: -40°C to +85°C

#### Pinout

# Description

The CDP68HC68R1 and CDP68HC68R2 are 128 word and 256 word by 8-bit static random access memories, respectively. The memories are intended for use in systems utilizing a synchronous serial three wire (clock, data in, and data out) interface where minimum package size, interconnect wiring, low power, and simplicity of use are desirable. These parts will interface directly with CDP68HC05D2, CDP68HC05C4, and CDP68HC05C8 microcomputers (providing the CPHA bit in the microcomputer's SPI Control Register is set equal to 1). The

CDP68HC68R1 and CDP68HC68R2 are also compatible with general purpose microcomputers, including the CDP1804A and CDP6805 family, by utilizing I/O bits for the SPI (Serial Peripheral Interface) bus. Other industry microcomputers such as the 80C51 can also interface to these serial RAMs.

The CDP68HC68R1 and CDP68HC68R2 are supplied in 8 lead plastic Mini DIP packages. (E suffix).

#### TRUTH TABLE

|                       | SIGNAL |        |                     |                   |                                                         |  |  |  |  |

|-----------------------|--------|--------|---------------------|-------------------|---------------------------------------------------------|--|--|--|--|

| MODE                  | CE     | ss     | SCK                 | MOSI              | MISO                                                    |  |  |  |  |

| Disabled and<br>Reset | L<br>X | X<br>H | Input<br>Disabled   | Input<br>Disabled | High Z                                                  |  |  |  |  |

| Read or<br>Write      | н      | L      | CPOL = 0, CPOL = 1, | Data Bit<br>Latch | High Z During Write,<br>Current Data Bit<br>During Read |  |  |  |  |

| Shift                 | н      | L      | CPOL = 0,           | х                 | Next Data Bit                                           |  |  |  |  |

NOTE: MISO remains at a High Z until 8 bits of data are ready to be shifted out during a Read and it remains at a High Z during the entire Write cycle.

The CPHA bit must be set = 1 in the Serial Peripheral control register of 6805 microcomputers in order to communicate with these devices.

### MAXIMUM RATINGS, Absolute-Maximum Values:

|                                       | DC SUPPLY-VOLTAGE RANGE, (VDD):                                        |

|---------------------------------------|------------------------------------------------------------------------|

| 0.5 to +7 V                           |                                                                        |

|                                       | INPUT VOLTAGE RANGE, ALL INPUTS                                        |

| ±10 mA                                | DC INPUT CURRENT, ANY ONE INPUT                                        |

|                                       | POWER DISSIPATION PER PACKAGE (PD):                                    |

| 500 mW                                | For T <sub>A</sub> =-40 to +60°C (PACKAGE TYPE E)                      |

| Derate Linearly at 12 mW/°C to 200 mW | For T <sub>A</sub> =+60 to +85° C (PACKAGE TYPE E)                     |

|                                       | DEVICE DISSIPATION PER OUTPUT TRANSISTOR                               |

| 100 mW                                | For TA=FULL PACKAGE-TEMPERATURE RANGE                                  |

|                                       | OPERATING-TEMPERATURE RANGE (TA):                                      |

| 40° to +85°C                          | PACKAGE TYPE E                                                         |

| 65 to +150°C                          | STORAGE TEMPERATURE RANGE (Tatg)                                       |

|                                       | LEAD TEMPERATURE (DURING SOLDERING):                                   |

| +265°C                                | At distance 1/16 $\pm$ 1/32 in. (1.59 0.79 mm) from case for 10 s max. |

|                                       |                                                                        |

### OPERATING CONDITIONS at TA = -40° to +85°C

For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

|                             |                 | LII                 | T                    |            |

|-----------------------------|-----------------|---------------------|----------------------|------------|

| CHARACTERISTIC              | ALL             | UNITS               |                      |            |

|                             | Ī               | MIN.                | MAX.                 | 1          |

| DC Operating Voltage Range  |                 | 3                   | 5.5                  |            |

| Input Voltage Range         | V <sub>IH</sub> | 0.7 V <sub>DD</sub> | V <sub>DD</sub> +0.3 | ] v        |

|                             | VIL             | -0.3                | 0.2 V <sub>bD</sub>  | 1          |

| Serial Clock Frequency      | fsck            |                     |                      |            |

| V <sub>DD</sub> =3 <u>V</u> |                 | _                   | 1.05                 | MHz        |

| V <sub>DD</sub> =4.5 V      |                 | _                   | 2.1                  | ]   V   12 |

# STATIC ELECTRICAL CHARACTERISTICS at TA = -40 to +85°C, $V_{DD}$ = 3.3 V $\pm 10\%$ , Except as Noted

|                                              | <u> </u>                                             | LIMITS         |             |     |      |             |      |    |

|----------------------------------------------|------------------------------------------------------|----------------|-------------|-----|------|-------------|------|----|

| CHARACTERISTIC                               | CONDITIONS                                           | CD             | CDP68HC68R1 |     |      | CDP68HC68R2 |      |    |

|                                              |                                                      | MIN. TYP. MAX. |             |     | MIN. | TYP.        | MAX. | 1  |

| Standby Device Current                       |                                                      |                | 1           | 15  | _    | 1           | 50   | μΑ |

| Output Voltage High Level<br>V <sub>он</sub> | I <sub>OH</sub> =-0.4 mA, V <sub>DD</sub> =3 V       | 2.7            | _           | _   | 2.7  |             | _    | v  |

| Output Voltage Low Level Vol                 | I <sub>OL</sub> =0.4 mA, V <sub>DD</sub> =3 V        |                | _           | 0.3 | _    | _           | 0.3  | *  |

| Input Leakage Current, I <sub>IN</sub>       | _                                                    |                | *           | ±1  | _    | *           | ±1   |    |

| 3-State Output<br>Leakage Current, lout      |                                                      | _              | _           | ±10 | _    | _           | ±10  | μΑ |

| Operating Device Current IOPER#              | V <sub>IN</sub> =V <sub>IL</sub> ,V <sub>IH</sub>    | _              | 5           | 10  | _    | 5           | 10   | mA |

| Input Capacitance, C <sub>IN</sub>           | V <sub>IN</sub> =0 V, f=1 MHz, T <sub>A</sub> =25° C | _              | 4           | 6   | _    | 4           | 6    | pF |

<sup>•</sup>Typical values are for T<sub>A</sub> = 25°C and nominal V<sub>DD</sub>.

<sup>#</sup>Outputs open circuited; cycle time = Min. t<sub>cycle</sub>, duty = 100%.

<sup>\*</sup>Typical input current values (high and low) for pins 1, 5, 6, 7, approximately 100 nA due to presence of feedback transistor.

Pin 6 is an exception - I<sub>in</sub>(high) typically 1 nA.

#### STATIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = -40 to +85 $^{\circ}$ C, V<sub>DD</sub> = 5 V $\pm$ 10%, Except as Noted

|                                         |                                                     |             |      | LIM  | ITS  |       |      |    |

|-----------------------------------------|-----------------------------------------------------|-------------|------|------|------|-------|------|----|

| CHARACTERISTIC                          | CONDITIONS                                          | CDP68HC68R1 |      |      | CD   | UNITS |      |    |

|                                         | 1                                                   | MIN.        | TYP. | MAX. | MIN. | TYP.  | MAX. | 1  |

| Standby Device Current                  | _                                                   | _           | 1    | 15   | _    | 1     | 50   | μΑ |

| Output Voltage High Level               | I <sub>OH</sub> =-1.6 mA, V <sub>DD</sub> =4.5 V    | 3.7         | _    | _    | 3.7  | _     | _    |    |

| Output Voltage Low Level Vol            | 1 <sub>0L</sub> =1.6 mA, V <sub>DD</sub> =4.5 V     | _           | _    | 0.4  | _    | -     | 0.4  |    |

| Output Voltage High Level<br>Voн        | I <sub>OH</sub> ≤10 μA, V <sub>DD</sub> =4.5 V      | 4.4         | _    | _    | 4.4  | _     | -    | ]  |

| Output Voltage Low Level Vol            | I <sub>OL</sub> ≤10 μA, V <sub>DD</sub> =4.5 V      | _           | -    | 0.1  | _    | -     | 0.1  |    |

| Input Leakage Current, IIN              | _                                                   |             | *    | ±1   | _    | *     | ±1   | Ī  |

| 3-State Output<br>Leakage Current, Iout | _                                                   |             | -    | ±10  | _    | _     | ±10  | μΑ |

| Operating Device Current lopes#         | V <sub>IN</sub> =V <sub>IL</sub> ,V <sub>IH</sub>   | _           | 5    | 10   | _    | 5     | 10   | mA |

| Input Capacitance, CIN                  | V <sub>IN</sub> =0 V, f=1 MHz, T <sub>A</sub> =25°C | _           | 4    | 6    |      | 4     | 6    | pF |

Typical values are for T<sub>A</sub> = 25°C and nominal V<sub>DD</sub>.

#### **PIN SIGNAL DESCRIPTION**

**SCK (Serial Clock Input)\*** - This input causes serial data to be latched from the MOSI input and shifted out on the MISO output.

MOSI (Master Out/Slave In)\* - Data bytes are shifted in at this pin most significant bit (MSB) first.

MISO (Master In/Slave Out)\* - Data bytes are shifted out at this pin most significant bit (MSB) first.

SS (Slave Select)\* - A negative chip select input. A high level at this input holds the serial interface logic in a reset state.

CE (Chip Enable)\*\* - A positive chip enable input. A low level at this input holds the serial interface logic in a reset state.

CE · SS - This is a logical function of CE and  $\overline{SS}$  used throughout this data sheet to simplify diagrams. CE · SS = 1 when pin 5 is low and pin 6 is high. CE · SS = 0 at all other times.

#### **FUNCTIONAL DESCRIPTION**

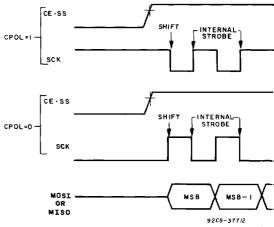

The Serial Peripheral Interface (SPI) utilized by the CDP68HC68R1 and CDP68HC68R2, is a serial synchronous bus for address and data transfers. The clock, which is generated by the microcomputer, is active only during address and data transfers. In systems using the CDP68HC05C4, CDP68HC05C8 or CDP68HC05D2, the inactive clock polarity is determined by the CPOL bit in the microcomputer's control register. A unique feature of the CDP68HC68R1 and CDP68HC68R2 is that they automatically determine the level of the inactive clock by sampling SCK when CE • SS becomes active (see Fig. 1). Input data (MOSI) is latched internally on the Internal Strobe edge and output data (MISO) is shifted out on the

Shift edge, as defined by Fig. 1. There is one clock for each data bit transferred (address as well as data bits are transferred in groups of 8).

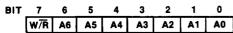

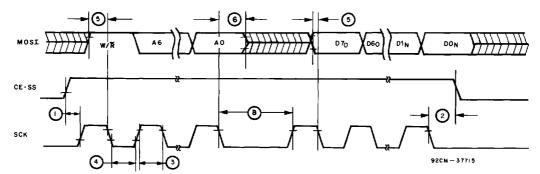

#### ADDRESS AND DATA FORMAT

The address and data bytes are shifted MSB first into the serial data input (MOSI) and out of the serial data output (MISO). The Address/Control byte (see Fig. 2b) contains a Write/Read bit and a 7-bit address. Any transfer of data requires an Address/Control byte to specify a RAM location, followed by one or more bytes of data. Data is transferred out of MISO for a Read and into MOSI for a Write. Address/Control bytes are recognizable because they are the first byte transferred following a valid CE · SS (except for Page select bytes, see PAGE SELECTION). To transmit a new address, CE · SS must first go false and then true again.

Fig. 1 - Serial RAM clock (SCK) as a function of MCU clock polarity (CPOL).

<sup>#</sup>Outputs open circuited; cycle time = Min. t<sub>cycle</sub>, duty = 100%.

<sup>\*</sup>Typical input current values (high and low) for pins 1, 5, 6, 7, approximately 100 nA due to presence of feedback transistor.

Pin 6 is an exception - l<sub>in</sub>(high) typically 1 nA.

<sup>\*</sup>These inputs will retain their previous state if the line driving them goes into a HIGH-Z state.

<sup>\*\*</sup>The CE input has an internal pull-down device—if the input is driven to a low state before going to a HIGH Z.

#### a. Page/Device Byte (CDP68HC68R2 Only)

| BIT | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|-----|---|---|---|---|---|---|---|----|

|     | X | Х | X | Х | Х | X | X | A7 |

b. Address/Control Byte

A0-A6 The seven least significant RAM address bits, sufficient to address 128 bytes.

W/R Read or Write data transfer control bit.

W/R = 0 initiates one or more memory read cycles. W/R = 1 initiates one or more memory write cycles.

#### c. Data Byte

Fig. 2 - Serial byte format.

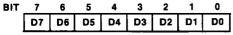

#### PAGE SELECTION (CDP68HC68R2 Only)

For the CDP68HC68R2, a Page/Device byte is sent from the microcomputer before the Address/Control byte. Because the Address/Control byte is limited to 128 addresses, the CDP68HC68R2 is divided into two 128-byte pages. A page select is accomplished by enabling the CDP68HC68R2, transmitting the Page/Device Select byte (see Fig. 2a), and finally disabling the device prior to any more data transfers. The Page/Device byte is recognizable because it is the only time that a single byte is transferred to the RAM before CE-SS is disabled (see Fig. 3). The page select is latched and remains until changed or is incremented during a burst transfer (see next section).

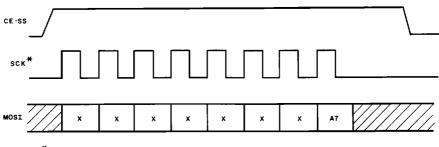

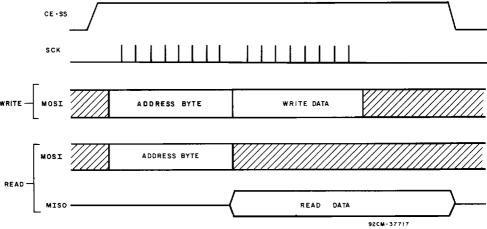

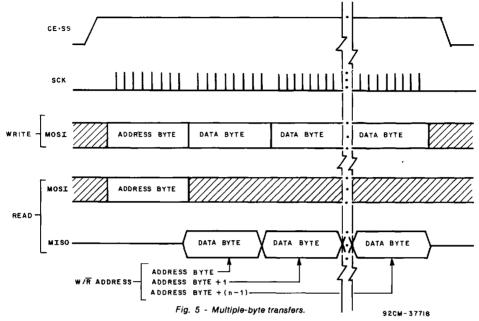

#### **ADDRESS AND DATA**

Data transfers can occur one byte at a time (Fig. 4) or in a multi-byte burst mode (Fig. 5). After the chip is enabled, an address word is sent to select one of the 128 bytes (on the selected page) and specify the type of operation (i.e., Read or Write). For a single byte Read or Write (Fig. 4), one byte is transferred to or from the location specified in the Address/Control byte; the device is then disabled. Additional reading or writing requires re-enabling the RAM and providing a new Address/Control byte. If the RAM is not disabled, additional bytes can be read or written in a burst mode (Fig. 5). Each Read or Write cycle causes the latched

SCK CAN BE EITHER POLARITY.

92CM-37713

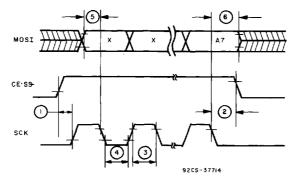

Fig. 3 - Page/Device Select byte transfer waveforms.

Fig. 4 - Single-byte transfer.

RAM address to automatically increment. Incrementing continues after each transfer until the device is disabled. After incrementing to 7FH on the CDP68HC68R1 or to FFH on the CDP68HC68R2, the address will recycle to 00H and

continue. Note that incrementing past 7FH on the CDP-68HC68R2 causes the address to go to location 80H (i.e., location 00H of page 1). The programmer must take care to keep track when crossing page boundaries.

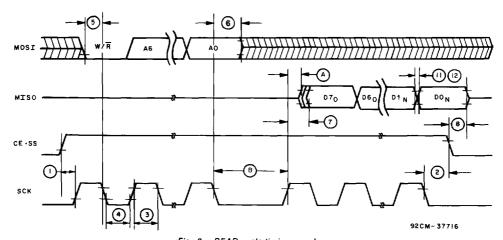

DYNAMIC ELECTRICAL CHARACTERISTICS - BUS TIMING V<sub>DD</sub>  $\pm$ 10%, VsS = 0 V dc, T<sub>A</sub> = -40° to +85° C, C<sub>L</sub> = 200 pF. See Figs. 6, 7 and 8.

| IDENT. |                                   |                   | LIMI                   | 4 1  |      |      |       |

|--------|-----------------------------------|-------------------|------------------------|------|------|------|-------|

| NUMBER | CHARACTERISTIC                    |                   | V <sub>DD</sub> =3.3 V |      |      |      | UNITS |

|        |                                   |                   | Min.                   | Max. | Min. | Max. |       |

| ①      | Chip Enable Set-Up Time           | tevov             | 200                    | _    | 100  | _    |       |

| 2      | Chip Enable after Clock Hold Time | t <sub>CVEX</sub> | 250                    |      | 125  | _    |       |

| 3      | Clock Width High                  | twн               | 400                    | _    | 200  | _    |       |

| 4      | Clock Width Low                   | twL               | 400                    |      | 200  | -    |       |

| 5      | Data In to Clock Set-Up Time      | tovov             | 200                    | _    | 100  | _    |       |

| 6      | Data In after Clock Hold Time     | tovex             | 200                    | _    | 100  | _    | ns    |

| 7      | Clock to Data Propagation Delay   | tovov             | _                      | 200  | _    | 100  |       |

| 8      | Chip Disable to Output High Z     | t <sub>EXQZ</sub> | _                      | 200  | _    | 100  |       |

| 11)    | Output Rise Time                  | tr                | _                      | 200  |      | 100  |       |

| 12     | Output Fall Time                  | tı                | -                      | 200  | _    | 100  |       |

| A      | Clock to Data Out Active          | tovax             | _                      | 200  | _    | 100  |       |

| В      | Clock Recovery Time               | trec              | 200                    | -    | 200  | _    |       |

Fig. 6 - Page/Device byte timing waveforms.

Fig. 7 - WRITE cycle timing waveforms.

Fig. 8 - READ cycle timing waveforms.

# DATA RETENTION CHARACTERISTICS at TA = -40° to +85° C

|                                  | TEST               | LIM                                            | ITS   |      |    |

|----------------------------------|--------------------|------------------------------------------------|-------|------|----|

| CHARACTERISTIC                   | CONDITIONS         | ALL T                                          | UNITS |      |    |

|                                  |                    |                                                | MIN.  | MAX. | 1  |

| Minimum Data Retention Voltage   | V <sub>DR</sub>    | CS≥V <sub>DD</sub> -0.2 V                      | 2     |      | V  |

| Data Retention Quiescent Current | l <sub>oo</sub> DR | V <sub>DD</sub> = 2 V,<br>CE = V <sub>SS</sub> | _     | 1    | μΑ |