# Encore! 32™ Series Microcontroller (Z32AN)

**High Performance ARM9 SoC Data Sheet**

DS0200-003

WARNING: DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2009 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Encore!  $32^{\text{TM}}$  is a trademark of Zilog, Inc. ARM® and Thumb® are registered trademarks of ARM Limited in the European Union and other countries. All other product or service names are the property of their respective owners.

# **Revision History**

Each instance in the revision history reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date               | Revision Level | Description                | Page Number         |

|--------------------|----------------|----------------------------|---------------------|

| August 2008        | 001            | Original issue             | All                 |

| September 23, 2008 | 002            | Updated part numbers       | Chapter 23          |

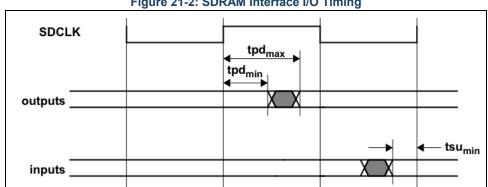

| February 25, 2009  | 003            | Updated AC Characteristics | Chapter 21, pg. 179 |

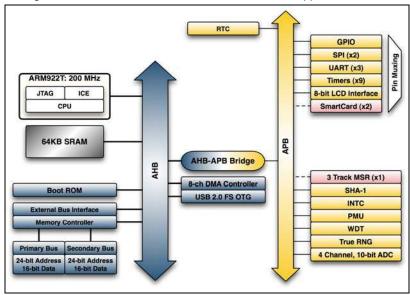

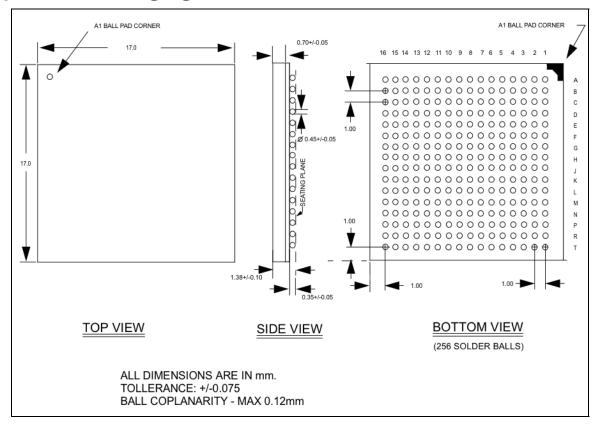

The Z32AN Series is a highly integrated System-on-Chip (SoC) based on the ARM922T core. Available in a 256-BGA package, the Z32AN Series provides a rich set of features on a single chip and enables designers to lower manufacturing costs and reduce time-to-market for embedded applications.

#### • 200 MHz ARM922T Core

- o 32/16-bit RISC Core (ARMv4T)

- o 16-bit Thumb Instruction Capable

- o 8k/8k I/D Caches

- o MMU supporting Linux and Windows CE

- JTAG Embedded ICE Support

### 64 KB Embedded zero-wait-state-SRAM

- Vectored Interrupt Controller

- FIPS-180-2 compliant SHA-1 Hash Generator

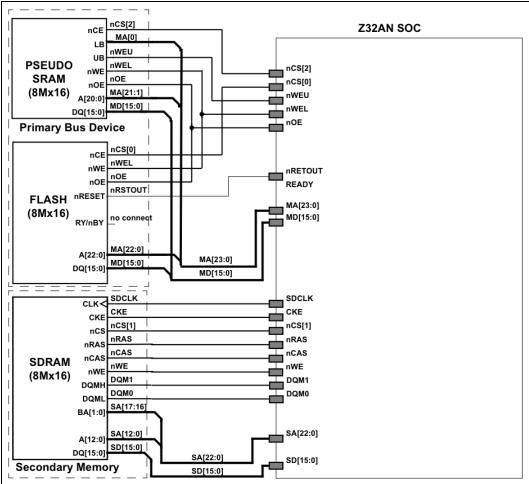

#### Dual External Bus Interface

- o 24-bit address, 16-bit data

- o SDRAM in 16-512 MB configurations

- o 10 chip selects

- External DMA support

#### Power Management Unit

- o 14-40 MHz oscillator and PLL

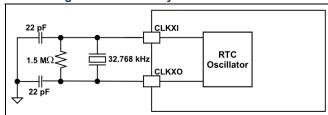

- o 32.768 kHz Oscillator for RTC

- o Clock disable per peripheral

- o 3 Modes: Active, Idle, and Battery-Backup

- Wake from idle capability

### 9 Timer/Counters

- o Five 32-bit cascadable

- o Four 16-bit with PWM Operation

- o Counter, PWM, Capture and Compare Modes

- 4 Dedicated I/Os

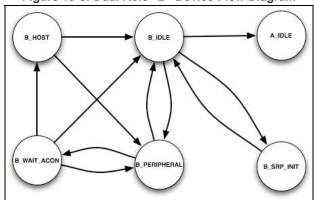

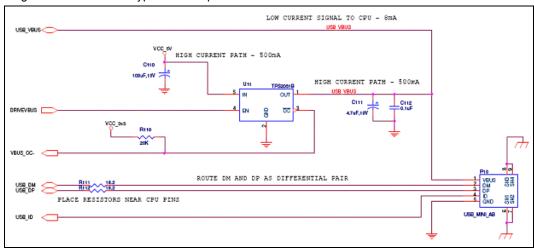

#### USB 2.0 full speed OTG

- o 16 endpoints

- Dedicated DMA

#### 3 UARTs

- o 1 x 8-wire Interface

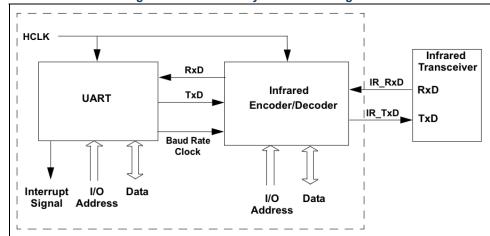

- o 2 x 4-wire Interface (1 shared with IrDA endec)

### 2 SmartCard Interface Controllers (Optional)

Interfaces directly to ON Semiconductor (NCN6001) SmartCard Controller

### Magnetic Card Reader (Optional)

- Support for ISO 7811-3 and 7811-6 Compliance

- o Direct Interface to Magnetic Head

- Simultaneous Three Track Reading

### • 8 independent DMA Channels

- SmartCard, MCR, UARTs, SPIs, LCD, external peripherals and Mem-to-Mem

- Up to 16 MB transfer capability

### • Voltage: Dual 1.8V and 3.3V supplies

- Embedded boot ROM w/external boot option

- NIST 800-22 compliant Random Number Generator

#### Display Controller Interface

- Directly Compatible with popular LCD Displays, Text or Graphic Modes

- o Interface to 4/8-bit Data, 3 Control, 1 Contrast

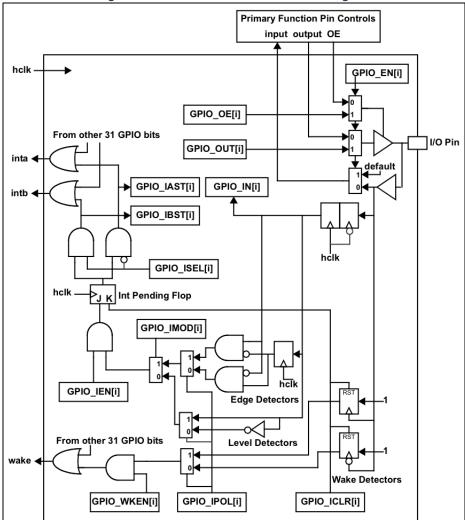

### Up to 76 General Purpose I/Os

- o 16 dedicated (with open drain capability)

- All Configurable as Edge/Level Interrupts

- Full Input/Output/Tri-state Control

- GPIO Wake capability

#### 4-channel, 10-bit SAR ADC, 45 kSps

- Real Time Clock

- Watchdog Timer

- 2 Dedicated SPI Interfaces

- 3.3V I/Os w/5V tolerant I/O for UART and SPI

Page ii

• 256 BGA Package. Boundary scan capable

# **Table of Contents**

| Chap | ter 1: Pin Description                                    | 1    |

|------|-----------------------------------------------------------|------|

| 1.1  | System Pins                                               | 1    |

|      | External Bus Interface                                    |      |

| 1.3  | Secondary External Bus Interface                          |      |

| 1.4  | External DMA Interface                                    |      |

| 1.5  | Timer/Counter                                             |      |

| 1.6  | RTC                                                       | 2    |

| 1.7  | UARTs                                                     | 2    |

|      | 1.7.1 UARTO                                               | 2    |

|      | 1.7.2 UART1                                               | 2    |

|      | 1.7.3 UART2                                               | 3    |

| 1.8  | SPI                                                       |      |

|      | 1.8.1 Port 0                                              | 3    |

|      | 1.8.2 Port 1                                              |      |

| 1.9  | USB Interface                                             |      |

| 1.10 | ) SmartCard Interface                                     |      |

|      | 1.10.1 Port 0                                             |      |

|      | 1.10.2 Port 1                                             |      |

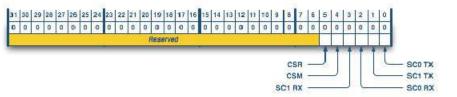

|      | 1.10.3 SmartCard SPI Interface                            |      |

|      | LCD Display Interface                                     |      |

|      | 2 Dedicated General Purpose I/O                           |      |

|      | 3 ADC                                                     |      |

|      | 4 Magnetic Card Reader                                    |      |

|      | 5 JTAG                                                    |      |

|      | S Power                                                   |      |

| 1.17 | 7 Pin Assignments, 256 BGA Package                        | 6    |

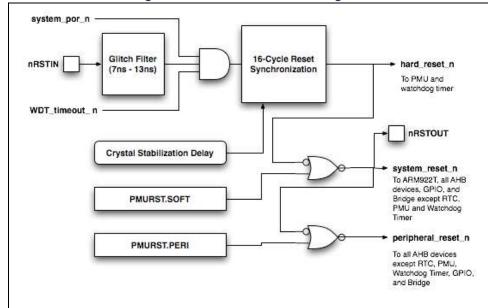

| Chan | ter 2: Reset                                              | 7    |

| •    |                                                           |      |

| 2.1  | System Reset                                              |      |

|      | Hard Reset                                                |      |

| 2.3  | Peripheral Reset                                          | /    |

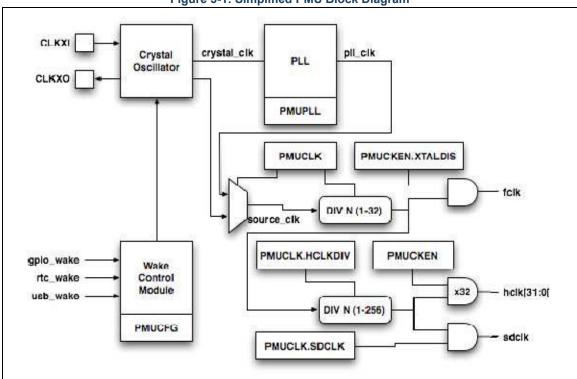

| Chan | ter 3: System Clocks and Power Management                 | ۶    |

|      |                                                           |      |

| 3.1  | Power Modes                                               |      |

|      | 3.1.1 HALT - ARM922 Wait for Interrupt                    |      |

|      | 3.1.1 IDLE                                                |      |

|      |                                                           |      |

| 2.0  | 3.1.3 Battery Back Up                                     |      |

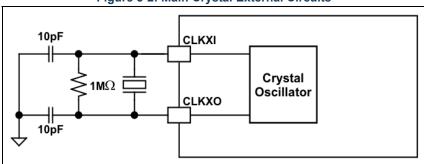

|      | Main Oscillator External Circuits                         |      |

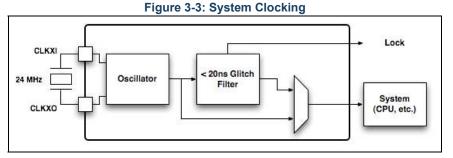

| 3.4  | System Clocking Notes                                     | •••• |

|      | PMU Registers: (Base → FFFFE000h)                         |      |

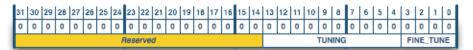

| 3.3  | 3.5.1 Offset 000h: PMUPLL – PMU PLL Register              | 11   |

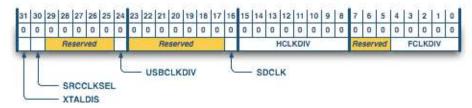

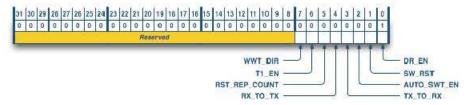

|      | 3.5.2 Offset 000th: PMUCLK – PMU Clock Control Register   | 17   |

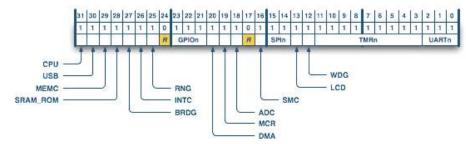

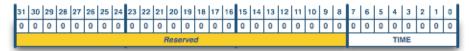

|      | 3.5.3 Offset 008h: PMUCKEN – PMU Clock Enable Register    |      |

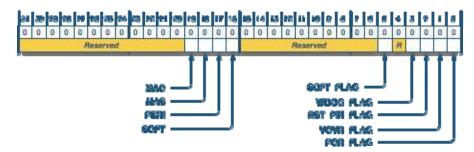

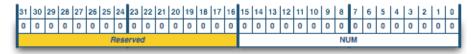

|      | 3.5.4 Offset 00Ch: PMURESET – PMU Reset Register          |      |

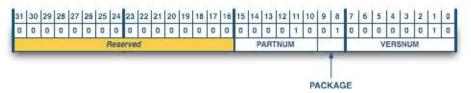

|      | 3.5.5 Offset 014h: PMUID – PMU ID Register                |      |

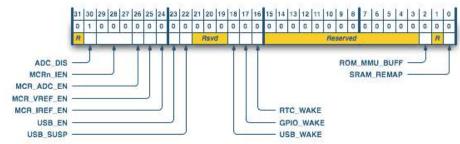

|      | 3.5.6 Offset 01Ch: PMUCFG – PMU Configuration Register    | 14   |

|      | 0.5.0 Offset of Cit. I Moci O Timo Configuration Register | 10   |

| Chap | ter 4: ARM922TCore and Embedded ICE                       | 16   |

|      |                                                           | . •  |

| Chap | ter 5: Memory Organization                                | 17   |

| 5.1  | Memory Map                                                | 17   |

|      | , ,                                                       |      |

| 5.2  | Accesses                                                                  | 18 |

|------|---------------------------------------------------------------------------|----|

| 5.3  | Restricted / Reserved Addresses                                           | 18 |

| 5.4  | ROM/SRAM Remapping                                                        |    |

| 5.5  | Internal SRAM                                                             |    |

|      | 5.5.1 Clock Disable                                                       |    |

|      | 5.5.2 Zeroization                                                         |    |

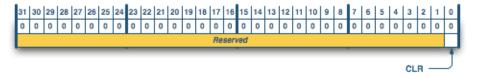

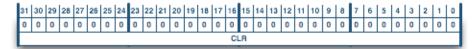

|      | 5.5.3 Address FFFF8068h: INT_SRAM_CLR – Internal SRAM Clear Register      |    |

| 5.6  | Internal ROM and Boot Program                                             |    |

|      | 5.6.1 Boot locations                                                      |    |

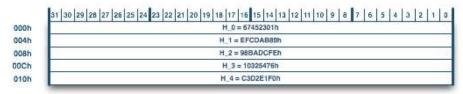

|      | 5.6.2 External Memory Image Format                                        |    |

|      | 5.6.3 Boot Sequence                                                       |    |

|      | 5.6.4 Boot ROM MMU Table                                                  | ∠( |

| Chap | ter 6: Interrupt Controller (INTC)                                        | 21 |

| 6.1  | Interrupt Channels and Sources                                            |    |

| 6.2  | Interrupt Priority                                                        |    |

| 6.3  | Configuring the Interrupt Controller                                      |    |

| 6.4  | ISR Invocation                                                            |    |

| 6.5  | ISR Return from Interrupt                                                 |    |

| 6.6  | Interrupt Nesting                                                         |    |

| 6.7  | Interrupt Latching                                                        |    |

| 6.8  | Registers: Base → FFFFF000h                                               |    |

|      | 6.8.1 Offset 000h: INTC_EN – Interrupt Controller Enable Register         |    |

|      | 6.8.2 Offset 004h: INTC_ESET – Interrupt Controller Enable Set Register   |    |

|      | 6.8.3 Offset 008h: INTC_ECLR – Interrupt Controller Enable Clear Register |    |

|      | 6.8.4 Offset 00Ch: INTC_DFLT – Default Vector Register                    |    |

|      | 6.8.5 Offset 010h: INTC_ISTA – Interrupt Status Register                  | 24 |

|      | 6.8.6 Offset 014h: INTC_RSTA – Raw Interrupt Status Register              |    |

|      | 6.8.7 Offset 018h: INTC_IDBG – IRQ Processor Debug Register               |    |

|      | 6.8.8 Offset 01Ch: INTC_FDBG – FIQ Processor Debug Register               | 25 |

|      | 6.8.9 Offset 020h: INTC_SWINT – Software Interrupt Register               | 25 |

|      | 6.8.10 Offset 024h: INTC_SWINT_SET – Software Interrupt Set Register      |    |

|      | 6.8.11 Offset 028h: INTC_SWINT_CLR – Software Interrupt Clear Register    |    |

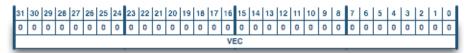

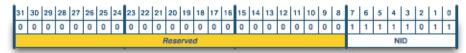

|      | 6.8.12 INTC_VECN – Channel N Vector Register                              |    |

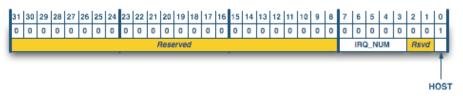

|      | 6.8.13 INTC_CFGN – Channel N Configuration Register                       |    |

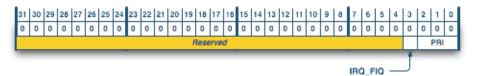

|      | 6.8.14 Offset F00h: INTC_IVEC – IRQ Vector Register                       |    |

|      | 6.8.15 Offset F04h: INTC_FVEC – FIQ Vector Register                       |    |

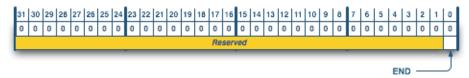

|      | 6.8.16 Offset F08h: INTC_IEND – IRQ End-of-Interrupt Register             |    |

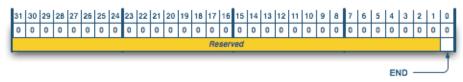

|      | 6.8.17 Offset F0Ch: INTC_FEND – FIQ End-of-Interrupt Register             | 28 |

| Chap | ter 7: External Bus Interface (田I)                                        | 29 |

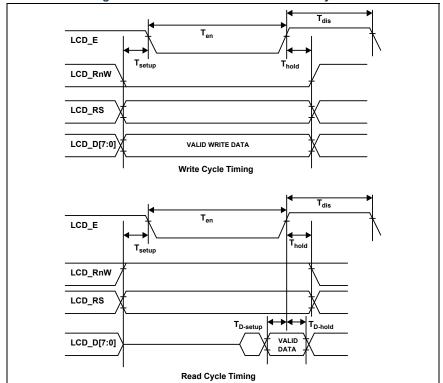

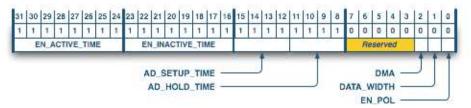

| 7.1  | Asynchronous Memory Controller                                            |    |

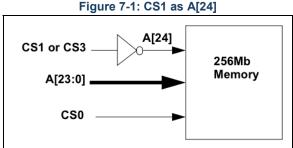

| 7.1  | 7.1.1 Programmable Features                                               |    |

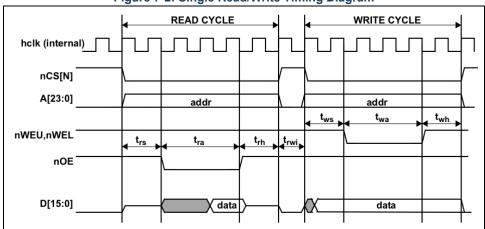

|      | 7.1.2 Asynchronous Single Read and Write Transactions                     |    |

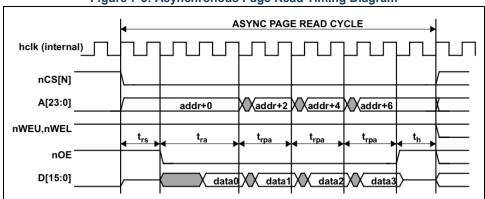

|      | 7.1.3 Asynchronous Page Read Transactions                                 |    |

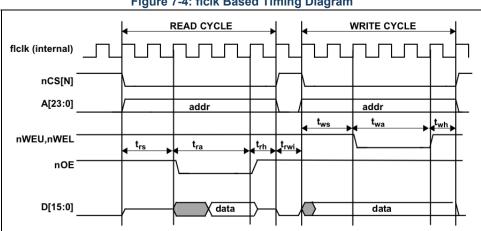

|      | 7.1.4 Clock Divided Transactions                                          |    |

| 7.2  | SDRAM Controller                                                          |    |

|      | 7.2.1 Operation                                                           |    |

|      | 7.2.2 Address Mapping                                                     |    |

|      | 7.2.3 Supported Configurations                                            |    |

|      | 7.2.4 SDRAM Performance                                                   |    |

|      | 7.2.5 Open Bank Policy                                                    |    |

|      | 7.2.6 Power Saving Modes                                                  |    |

|      | 7.2.7 Pin Multiplexing                                                    |    |

|      | 7.2.8 Programmer's Guide                                                  | 36 |

| 7.3  | - 1 9                                                                     |    |

| 7.4  | Registers (Base → FFFF8000h)                                              | 4  |

| Chap              | er 8: DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 8.1               | Channel Arbitration and Bursts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49      |

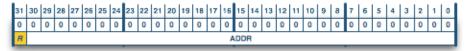

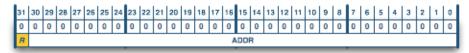

| 8.2               | DMA Source and Destination Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

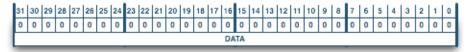

| 8.3               | Data Movement from the DMA FIFO to the Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| 8.4               | Memory Buffer Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| 8.5               | Count-to-Zero Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| 8.6               | Chaining Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

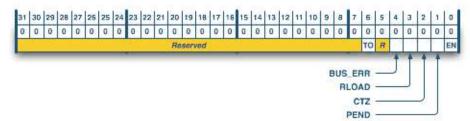

| 8.7               | DMA Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 8.8               | Channel Time-outs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| 8.9               | Register Accesses Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|                   | Memory-to-Memory DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

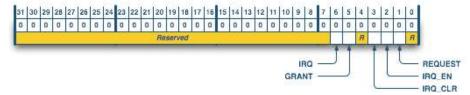

|                   | External DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

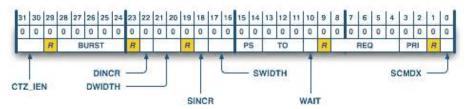

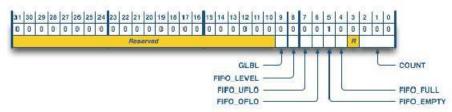

|                   | Registers (Base → FFFF4000h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| 0.12              | 8.12.1 Global Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

|                   | 8.12.2 Per-Channel Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| Chap              | er 9: Magnetic Card Reader (MCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

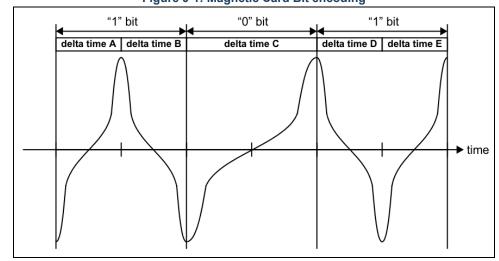

| 9.1               | Magnetic Card Reading Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60      |

| 9.2               | Direct Mode Operation of MCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61      |

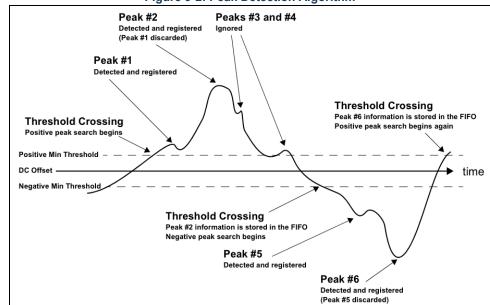

|                   | 9.2.1 Peak Detection Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61      |

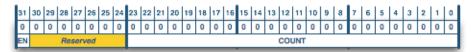

|                   | 9.2.2 Stored Peak Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|                   | 9.2.3 Peak Detection Timer and Time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62      |

|                   | 9.2.4 Card Time-out and Track Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62      |

|                   | 9.2.5 Dynamic Minimum Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62      |

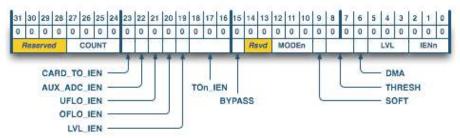

|                   | 9.2.6 MCR Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62      |

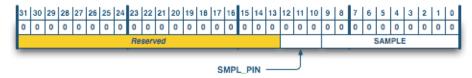

|                   | 9.2.7 Acquiring Raw ADC Samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63      |

|                   | 9.2.8 Programming Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63      |

|                   | 9.2.9 Card Time-out and Track Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 64      |

| 9.3               | Registers (Base → FFFF3000h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64      |

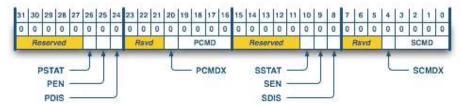

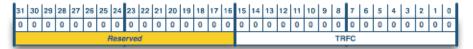

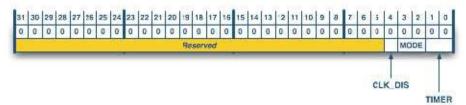

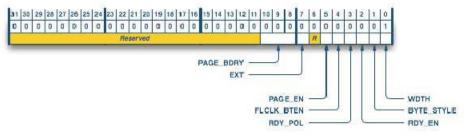

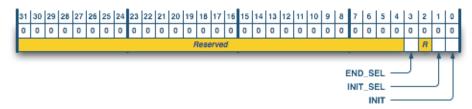

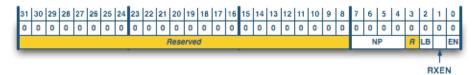

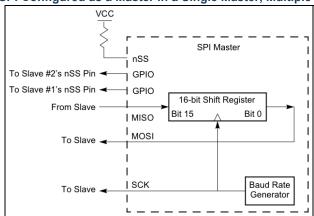

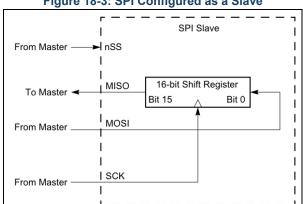

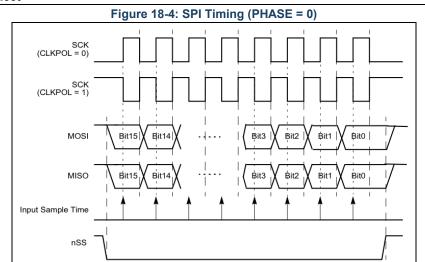

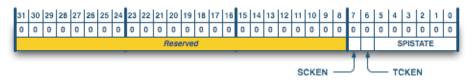

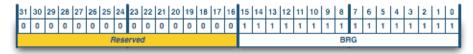

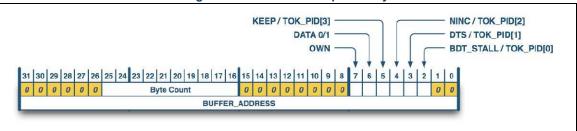

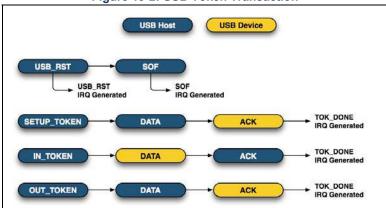

|                   | 9.3.1 Offset 000h: MCR_CTRL – MCR Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |