# **SX1441**

# Ultra Low Power Bluetooth® V1.2 Soc for Wireless Headset and Data Applications with DSP Capabilities

## **GENERAL DESCRIPTION**

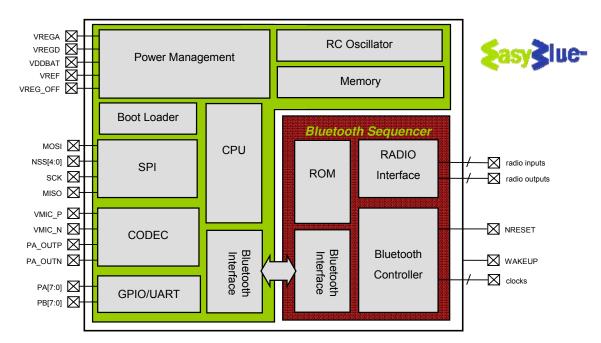

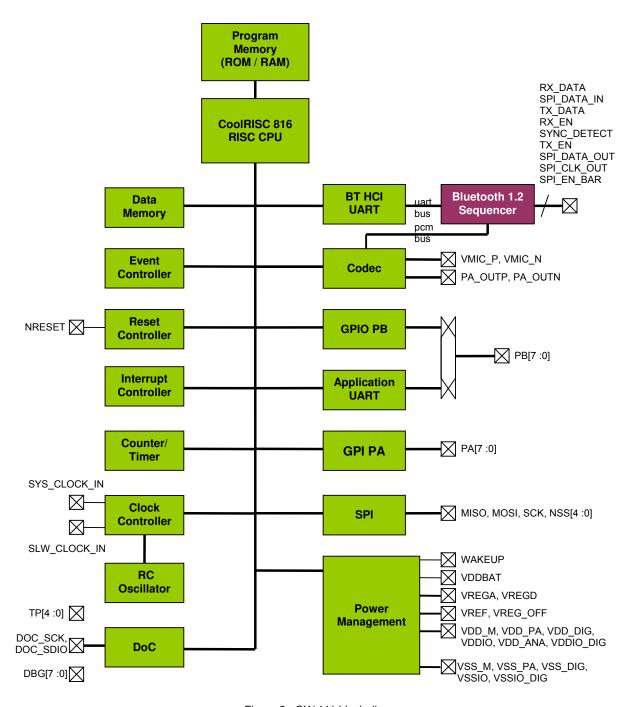

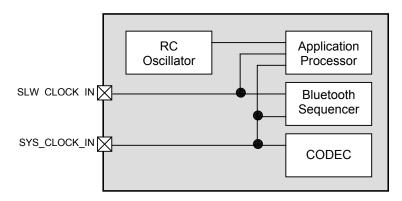

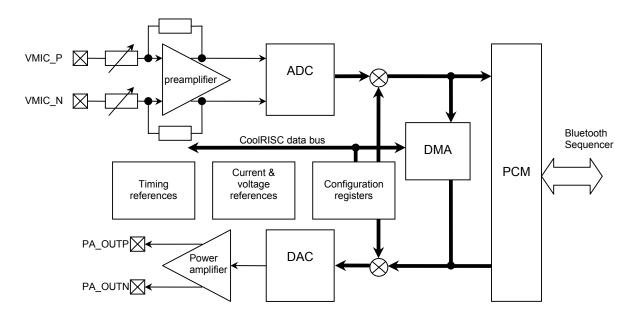

The SX1441 is a Bluetooth System-on-Chip based on the Semtech Bluetooth Sequencer, which includes a fully programmable 8-bit application microcontroller, a high speed UART, SPI interface, RC oscillator, power management unit, and an on-chip voice CODEC with DMA interface. The purpose of the SX1441 is to offer a very high level of integration requiring a minimum of external components to build complete voice and data applications whilst maintaining design flexibility.

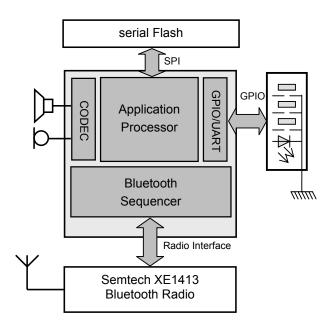

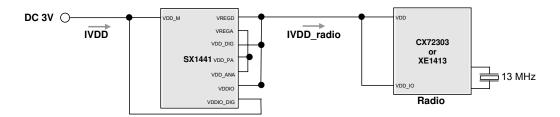

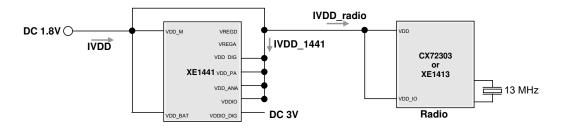

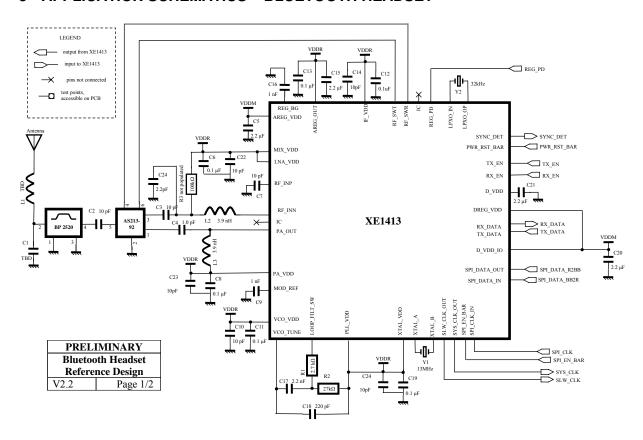

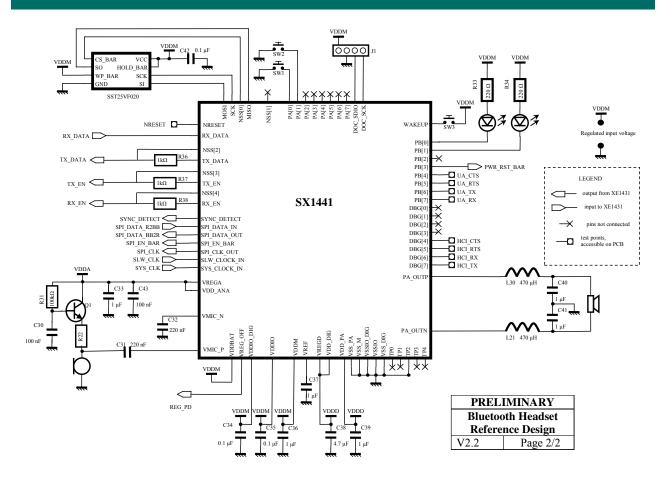

This product has been designed for ultra low power consumption and low cost solutions. By combining the SX1441 with a low power 2.4 GHz radio device such as the XE1413, from Semtech, an ultra low power Bluetooth wireless headset consuming less than 23mW @1.8V (HV3) can be built.

#### **APPLICATIONS**

- · Bluetooth wireless headset

- Handsfree kit

- VoIP, VoRF

- Cable replacement

- Computer accessories

## **KEY PRODUCT FEATURES**

- Ultra low power single-chip Bluetooth SoC, fully Bluetooth rev 1.2 compliant. Supports AFH, Fast Connect and eSCO

- Fully integrated Bluetooth protocol stack up to the HCI, compliant to revision 1.2

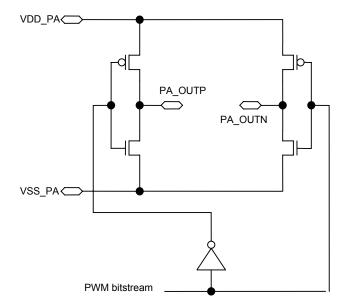

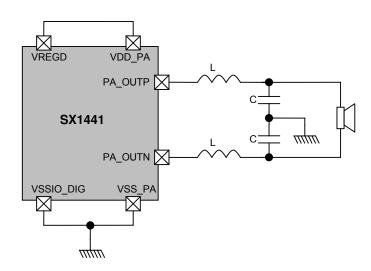

- On-chip 16-bit audio linear Codec with DMA interface, preamplifier and audio power amplifier

- Minimum of external components required

- Small form factor

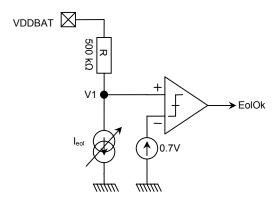

- On-chip battery level detector

- High speed general purpose UART

- Supports simultaneously one SCO and up to three ACL channels

- On-chip MCU and ROM/SRAM memory

- Ni-MH or Li-ion polymer rechargeable battery operation. Supply voltage range 1.8V to 3.6V

- Ultra low power consumption

- Supports CX72303 and XE1413 BT 1.2 radios

#### ORDERING INFORMATION

| Part Number     | Description                 |

|-----------------|-----------------------------|

| SX1441IO77TR LF | Bluetooth SoC for voice and |

|                 | data applications           |

## **Table of Contents**

| 1 | App            | olication Information – SX1441-based System Level Block Diagram | 5  |

|---|----------------|-----------------------------------------------------------------|----|

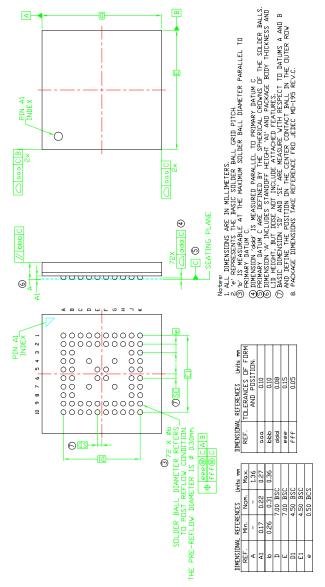

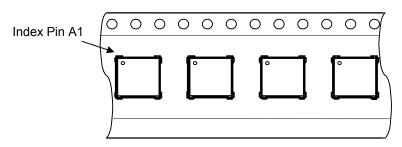

| 2 | SX             | 1441 Pinout                                                     | 6  |

|   | 2.1            | Pin description                                                 |    |

| 3 |                | tailed Functional Description                                   |    |

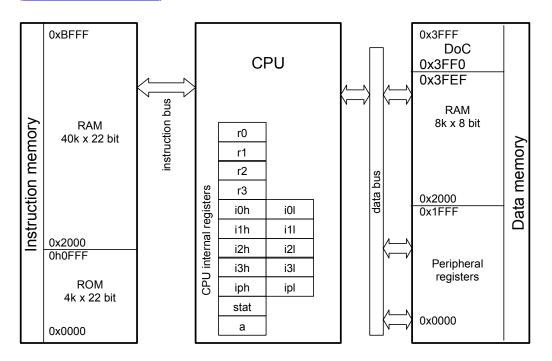

| J | 3.1            | Block Diagram                                                   |    |

|   | 3.2            | Host Processor system                                           |    |

|   | 3.2.1          |                                                                 |    |

|   | 3.2.2          |                                                                 |    |

|   | 3.2.3          |                                                                 |    |

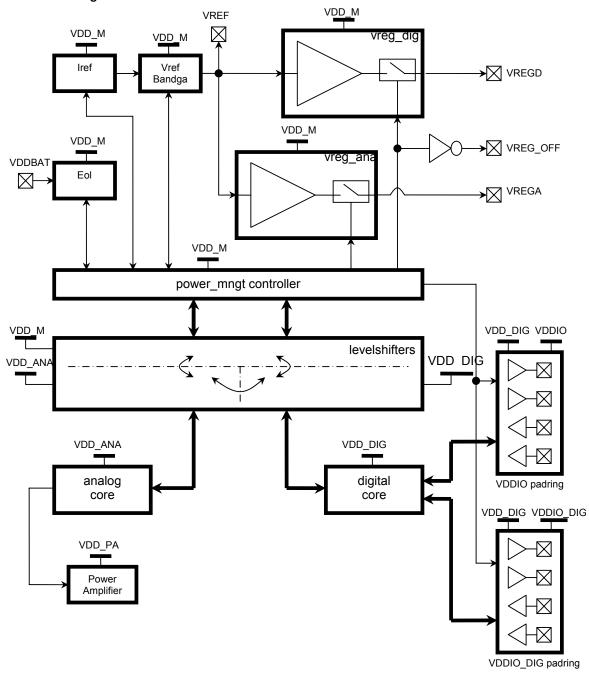

|   | 3.3            | Power Management Unit                                           | 12 |

|   | 3.3.1          |                                                                 |    |

|   | 3.3.2          |                                                                 |    |

|   | 3.3.3          |                                                                 |    |

|   | 3.3.4<br>3.3.5 |                                                                 |    |

|   | 3.3.6          |                                                                 |    |

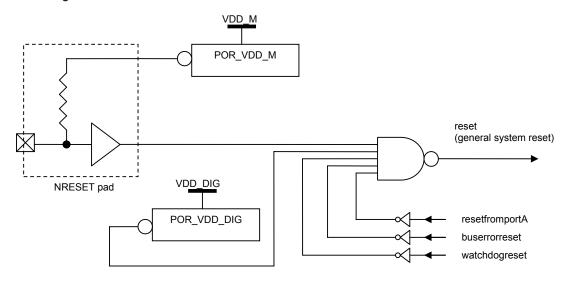

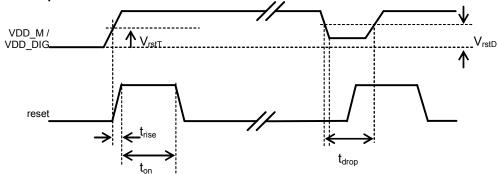

|   | 3.4            | Reset controller                                                |    |

|   | 3.4.1          |                                                                 |    |

|   | 3.4.2          |                                                                 |    |

|   | 3.4.3          |                                                                 |    |

|   | 3.4.4          |                                                                 |    |

|   | 3.4.5<br>3.4.6 |                                                                 |    |

|   |                | · · · · · · · · · · · · · · · · · · ·                           |    |

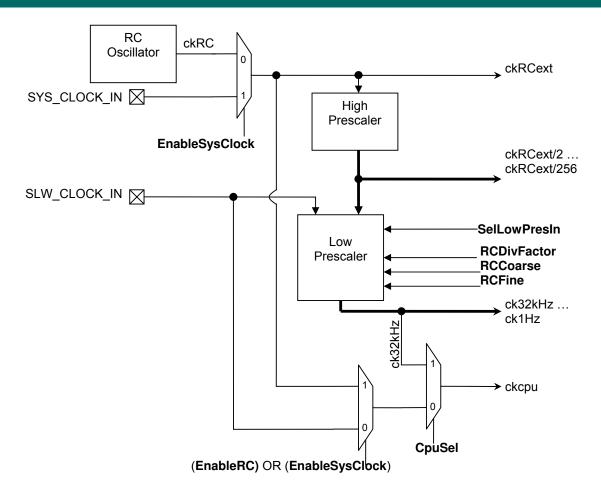

|   | 3.5<br>3.5.1   | Clock Distribution Unit                                         |    |

|   | 3.5.2          |                                                                 |    |

|   | 3.5.3          |                                                                 |    |

|   | 3.5.4          | SLOW_CLOCK_IN                                                   | 20 |

|   | 3.5.5          |                                                                 |    |

|   | 3.5.6<br>3.5.7 |                                                                 |    |

|   | 3.5.8          | <b>0</b> , 1                                                    |    |

|   | 3.5.9          |                                                                 |    |

|   | 3.6            | Interrupt controller                                            |    |

|   | 3.6.1          | ·                                                               |    |

|   | 3.6.2          | Register map                                                    | 27 |

|   | 3.6.3          | ·                                                               |    |

|   | 3.7            | Event controller                                                | 30 |

|   |                | Features                                                        |    |

|   | 3.7.2<br>3.7.3 | - J                                                             |    |

|   |                | ·                                                               |    |

|   | 3.8<br>3.8.1   | Digital input port PA[7:0]Features                              |    |

|   | 3.8.2          |                                                                 |    |

|   | 3.8.3          | - J                                                             |    |

|   | 3.8.4          | Debounce mode                                                   | 33 |

|   | 3.8.5          |                                                                 |    |

|   | 3.8.6          |                                                                 |    |

|   | 3.8.7<br>3.8.8 |                                                                 |    |

|   | 3.8.9          |                                                                 |    |

|   | 3.9            | Digital input/output port PB[7:0]                               |    |

|   | 3.9.1          |                                                                 |    |

|   |                |                                                                 |    |

|   | 3.9.2  | Register map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.9.3  | Multiplexing PB with other peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36 |

|   | 3.9.4  | Port B digital capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   |        | Counters/Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.10.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

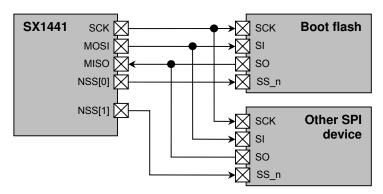

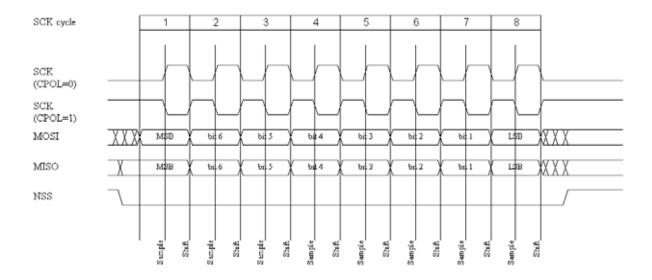

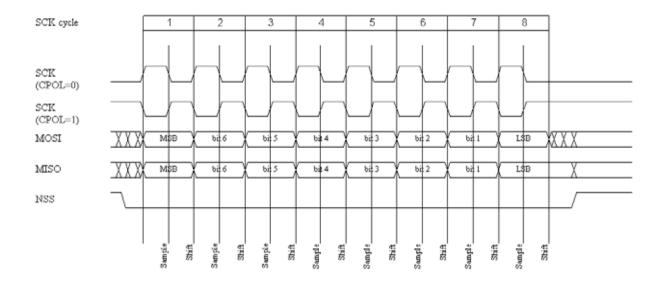

|   | 3.11   | Serial Peripheral Interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|   | 3.11.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.11.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.11.3 | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|   | 3.11.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.11.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

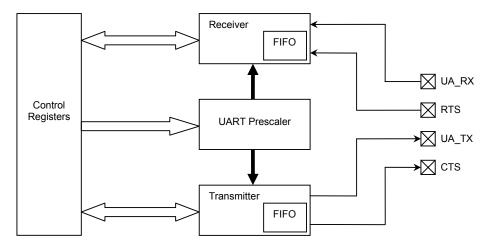

|   | 3.12   | Application UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|   | 3.12.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.12.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.12.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

|   | 3.12.4 | and the state of t |    |

|   | 3.12.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.12.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.12.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.12.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.12.9 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

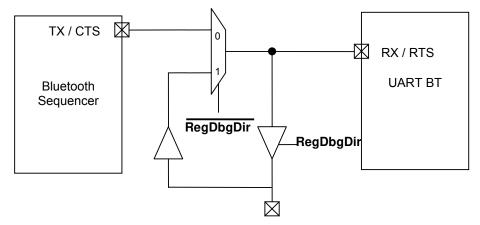

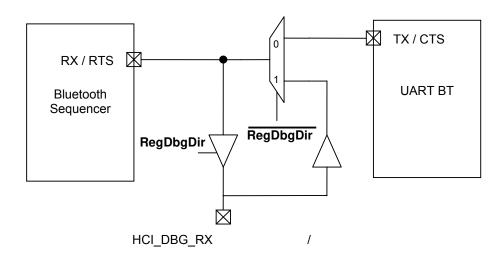

|   | 3.13   | Bluetooth Sequencer Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|   | 3.13.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.13.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.13.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.13.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.13.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59 |

|   | 3.13.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |